# Upgrading to the 68HCI2 I6-bit microcontroller (I)

# an introduction

By Oliver Thamm

The application of microcontrollers on the other side of the 8-bit boundary often seems like a closed book. Here we show that it can actually be fairly easy to start working with such microcontrollers — it's not even necessary to be an accomplished 'HCII programmer!

Circuits using microcontrollers are very flexible, and they enjoy a correspondingly high level of popularity. The Motorola 68HC11 family has for years been one of the favourites for hobby applications. These 8-bit microcontrollers have an easily understood internal structure and can be readily programmed via an RS232 link. The HC11 fan club has grown over the years, and the number of published designs has also increased (see Literature). However, these days the HC11 has become somewhat technically obsolescent. New application areas demand controllers that are more flexible and that have more processing power. Motorola, the manufacturer of the HC11, finally decided to make a radical change in their manufacturing technology, which however could not easily be carried out with the HC11 types. The result was the 68HC812A4, the first member of the new, powerful HC12 family.

Many HC11 users do not realise that they can easily change over to

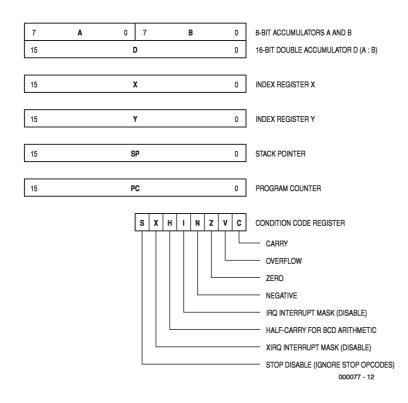

Figure 1. HC12 CPU registers.

## **HCI2 Operating Modes**

The HC12 can work in several different operating modes that are selected via pins MODA and MODB. The levels on these pins are read in by the processor on the rising edge of the reset signal, to determine the operating mode. Normally, the BKGD pin must maintain a steady High level at this moment. The following operating modes, which are the most important, are frequently encountered in HC12 circuits.

#### Normal Single Chip Mode (MODA=L, MODB=L)

The HC12 operates without an external bus interface, using only the internal memory (RAM, EEPROM and Flash EEPROM if available). The bus leads that are thereby made free are made available as general-purpose I/O leads.

#### Normal Expanded Wide Mode (MODA=H, MODB=H)

The HC812A4 operates with a 16-bit-wide external bus interface. Ports A and B provide the address bus, while the data bus is found at ports C and D. Bus control is provided by the signals ECLK, R/W and /LSTRB (port E). The HC12 generates up to seven chip select signals on port F, as necessary. In addition, it is possible to use Memory Banking to drive memory regions beyond the 64-kB boundary. Up to six leads of port G are responsible for this.

#### Normal Expanded Narrow Mode (MODA=H, MODB=L)

In this mode, the HC812A4 behaves the same as in the Expanded Wide mode, except that the data bus is only eight bits wide (Port C). The MCU automatically splits every 16-bit access into two sequential 8-bit accesses.

#### Special Single Chip Mode (MODA=L, MODB=L)

This mode is specially provided for putting the IC into operation with the Background Debug Interface Mode interface. When the reset signal is released, the connected BCM pod must hold the BKGD lead Low for a short time. The HC12 system and the pod subsequently communicate via this lead. The CPU does not start with processing an application program, as usual, but initially executes only BDM instructions. In this software-development operating mode, the restrictions on the use of some of the control registers are relaxed, since some of the protective provisions of the MCU are disabled. the faster HC12. This is because the new models have inherited the complete HC11 programming model. That means that the structure of the CPU registers (see **Figure 1**), the assembler instructions and the addressing modes have remained the same. Programmers will thus find it very easy to change to the new family, since existing source code only has to be retranslated. If you're only starting, rather than switching over, you can still enjoy certain advantages. In brief, the HC12 masters an important balancing act, combining high performance with a relatively low level of complexity.

#### **Practical circuits**

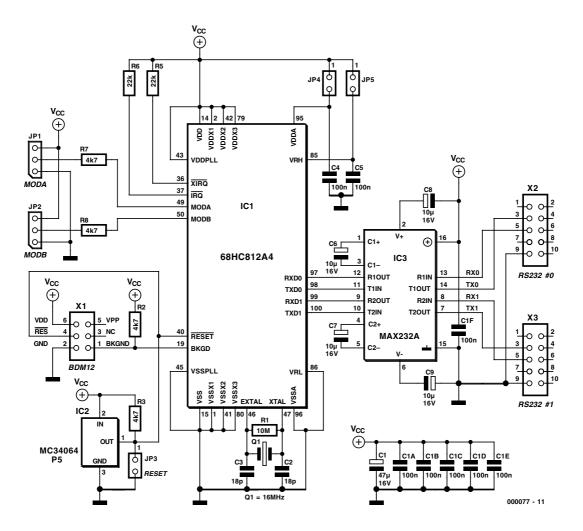

Enough of the introductory remarks, now it's time to look at a circuit diagram for the HC12. **Figure 2** shows an HC812A4 IC and the external circuitry that the microcontroller needs to run. Is that all it takes? Yes, indeed, and this is one of the main advantages of this microcontroller unit (MCU) – almost all the important components are integrated into the controller.

IC3 is the well-proven Maxim TTL/RS232 signal-level converter. The HC812A4 has two asynchronous serial interfaces, which are internally designated SCI0 and SCI1. Their operation is mutually independent, and they easily manage a data rate of 38,400 baud with the clock crystal used here. A second serial interface has been on the wish list of a lot of HC11 users for a long time. Now you finally have all the resources you need, for example to exchange messages with the application program via the first channel while sending debugging data via the second channel. The two connectors X2 and X3 are implemented as pin headers, to which oneto-one crimped flatcables can be connected, with 9-pin sub-D connectors (also crimped) at the PC end.

#### A quick tour of the MCU

The clock is generated using the usual combination of a quartz crystal, a pair of ceramic capacitors and a resistor. HC11 users will recognise the circuit, but in this case a 16-Mhz crystal provides the time standard. Compared to standard HC11 types, this provides four times the internal processing speed (8 MHz E clock).

In order to reliably reset the CPU when the circuit is switched on (or restarted), an external reset IC is prescribed. In our circuit, this service is provided by IC2, an MC34064P5. In addition, it is possible to connect a manual reset pushbutton via jumper JP3.

Jumpers JP4 and JP5 are normally closed

Figure 2. The circuit diagram of the HCA812A4 component set corresponds to that of the HC12 Welcome Kit.

(installed), so that the operating voltage (Vcc, +5 V) is applied to the power supply and reference voltage inputs of the integrated A/D converter. These inputs can be fed from external voltages by removing the jumpers, for example if it is necessary to use a more precise reference voltage.

#### **Mode selection**

Two additional jumpers are needed to set the operating mode of the HC12. JP1 is connected to the MODA pin, and JP2 to the MODB pin. The manner in which these signals affect the behaviour of the HC12 is explained in the 'HC12 Operating Modes' box. In our case, both jumpers are set to the 1–2 positions and thus select the Single Chip operating mode. Single Chip mode does not mean that there are not any other ICs on the board. Instead, in this mode the HC12 disables all bus signals for external memory ICs. The ports that are made free as a consequence can be used as general-purpose I/O lines, and this means a gain of up to 40 lines!

The internal EEPROM serves as the program store. With a size of 4 kB, it is larger than the internal program store of the HC11. In addition, there is 1 kB of RAM for variable data. Since the instruction set of the HC12 is very efficient, it is possible to store a fairly sizeable program in the internal memory. Some examples will be provided in the second part of this article, in the December 2000 issue.

#### In the background

Apart from a few blocking capacitors and pull-up resistors, we would be finished with the description of the schematic diagram, except for the six-pin connector X1. Only two 'real' signals are tied to this connector, namely /RES and BKGD. The signal /RES is an extension of the MCU /RESET signal, while BKGD is connected directly to the microcontroller. The built-in debugging function of

the microcontroller works via this lead, which is the interface for the Background Debug Mode (BDM). As the name indicates, the BDM interface is used for more than just downloading software into the RAM or EEPROM. The BKGD pin also provides a 'back door' to the microcontroller, which allows any desired memory addresses to be read and written, ranging from the RAM and EEPROM to the IC control registers. This means that, via this pin and BDM, you can start and stop application programs as desired, set breakpoints, run software in singlestep mode and read or modify the contents of the processor registers. The most important details of BDM12 operation are explained in the box 'How does BDM work?'.

This all sounds like we have a complete hardware emulator on board. Normally, you can expect to pay the cost of a small car for such a piece of equipment, but the HC12 includes the most important features of such a debugging aid at no extra charge. This sounds almost too good to be true, and in fact there is a fly in the ointment.

The connection to a PC that is used for developing and downloading the software is not entirely without problems. The BDM interface is simply too fast to work with a normal serial or parallel PC interface. This means that you need a bit of hardware and software to act as an interpreter between the PC and the HC12. This is called a BDM pod, and it is not particularly suitable for DIY construction. Fortunately, there are alternative solutions, such as the NoICE debugger, that will not soak up the annual budget of an ambitious HC12 developer in one blow. A large collection of links relating to BDM and the general subject of HC12 microcontrollers can be found on the author's HC12 Internet site at http://hc12web.de.

#### I/O leads

It's a fortunate person who has enough I/O heads to connect all of his LCDs, pushbuttons, lamps and relays. With an HC812A4, you won't find your self in a predicament quite so quickly, at least if it is working in Single Chip mode. More than 80 I/O connections are available to the user, each of which can be addressed as an input and/or output. With regard to the internal pull-up resistors, there are several configuration options. A substantial number of input signals (roughly one third) can function as interrupt triggers.

#### **28** Pins $\times$ **4**

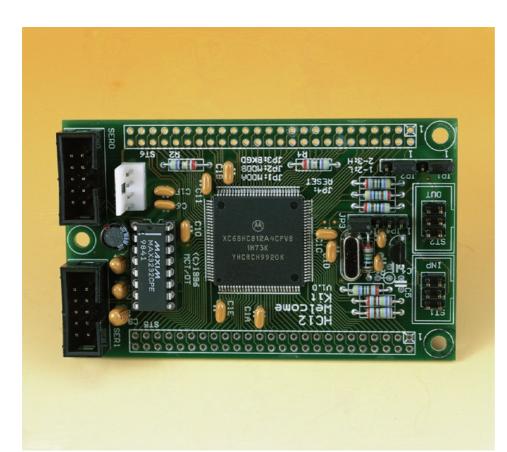

If you're already getting curious and would like to take a closer look at the HC12, you have basically two options for getting started quickly. The first option is to obtain the microcontroller IC and mount it in a socket on a universal printed circuit board. The relatively few external connections will not present that much of a problem. However, the catch is that it is very difficult to manually solder the IC, so that a socket must be used – and suitable sockets for the 112-pin OFP package of the HC812A4 are expensive and hard to come by. In fact, they are so expensive that it is worth taking a look at the second option. This consists of a pre-assembled controller module, as shown in the photograph. It not only includes the peripheral circuitry shown in **Figure 2**, but also makes all processor signals available on lateral pin strips, where they can be easily accessed (even using non-professional means).

The German firm *Elektronikladen* (see <u>http://www.elektronikladen.de</u> on the Internet) offers such modules in credit-card format under the designation 'HC12 Welcome Kit' (see <u>http://elektronikladen.de/kit12.html</u>) The MCU is soldered directly to the circuit board in an SMD production step, without a socket. This makes the whole thing affordable, and for around £75 you receive a complete starter kit, including a monitor program for easy downloading of application programs via the serial interface.

(000077-1)

Part 2 will discuss the programming of the internal functional modules of the HC12 and the tools that are needed for this.

Literature: 68HC11 emulator, Elektor Electronics February 1997.

### **How does BDM work?**

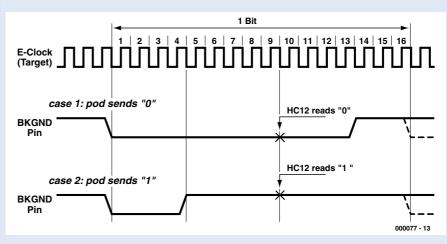

The Background Debug Mode (BDM) interface of the HC12 is basically supported by a single lead (BKGD) of the microcontroller. In the idle state, this lead is held High by a pull-up resistor. A special asynchronous serial protocol is used for communications. The underlying clock is based on the clock speed of the HC12. For example, if a 16-MHz crystal is used, the basic time unit of the BCM system is 125 ns.

The timing diagram shows how an individual bit is transferred. This requires 16 clock cycles, which means that it takes 2  $\mu$ s to transfer one bit at 125 ns per clock, and a full byte thus takes 16  $\mu$ s. A typical BDM command sequence consists of five bytes, and thus takes around 80  $\mu$ s. In practice, you can expect to see around 5 to 10 thousand BDM instructions per second – and that's already pretty fast.

A BDM instruction consists of a command byte and any necessary parameters. For example, the instruction sequence for a 16-bit write access to address \$0800/I appears as follows:

C8 08 00 1A 2F

The individual components of the message have the following meanings:

\$C8 BDM command 'WRITE\_WORD' \$0800 address \$1A2F data word

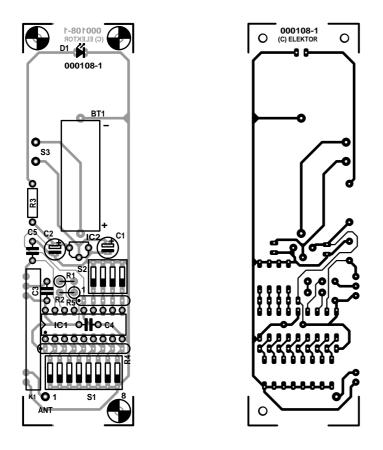

# Learning RC5 Control Decoder

# build a low-cost remote volume control

By Jason Vincent-Newson

jasreb@bigfoot.com

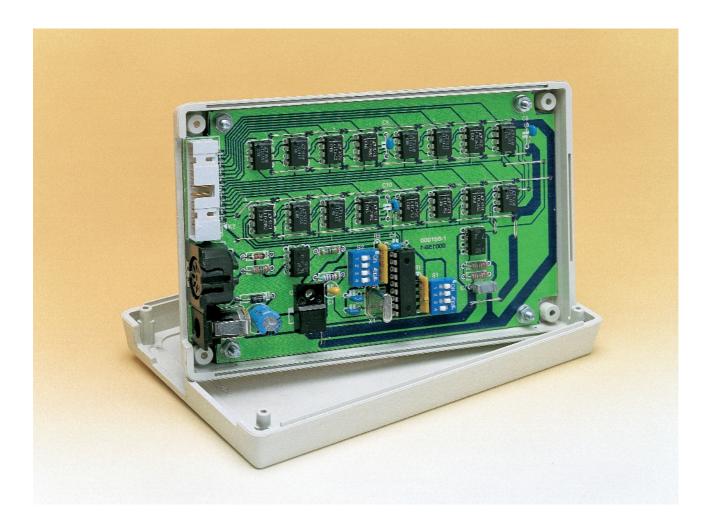

The unit described is intended to be used with any Philips RC5 remote control to enable up/down remote control of a motor driven potentiometer.

A special feature of the design is that it is truly universal in that it can be programmed to respond to any two specific keys on any Philips RC5 compatible remote control.

This is achieved simply by shorting two

pins on the unit during power-up. The unit will then indicate PROG mode by flashing the relevant LEDs, and learn the system address and volume UP/DOWN commands as they are pressed on the chosen remote control. The resulting information is stored in non-volatile memory for retention after power-down.

The unit can be reprogrammed at any time in the same way.

A power opamp motor driver is included to directly drive any conventional 5-V motor driven pot.

The PCB is fitted with a 10-way pinheader connector to allow easy design into new or existing equipment. The pins give access to the 3pin IR sensor, motor wires and the PROG jumper so that these can be sited remotely if required.

#### **Circuit Description**

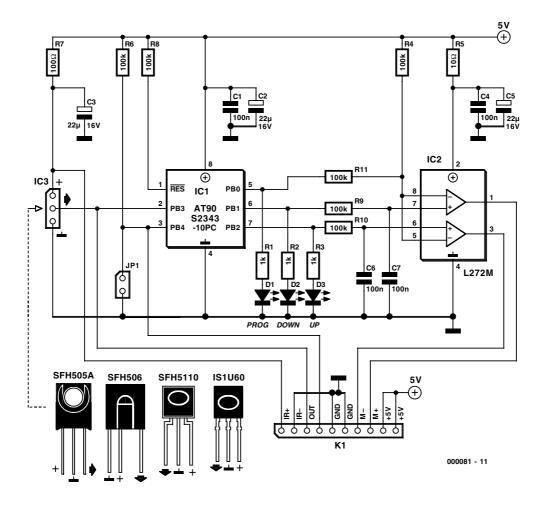

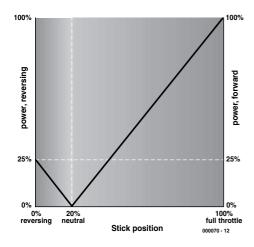

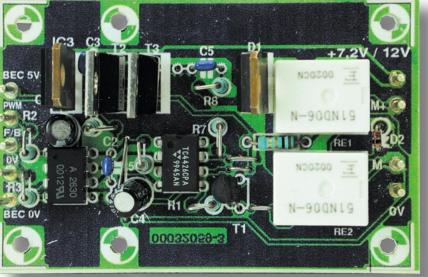

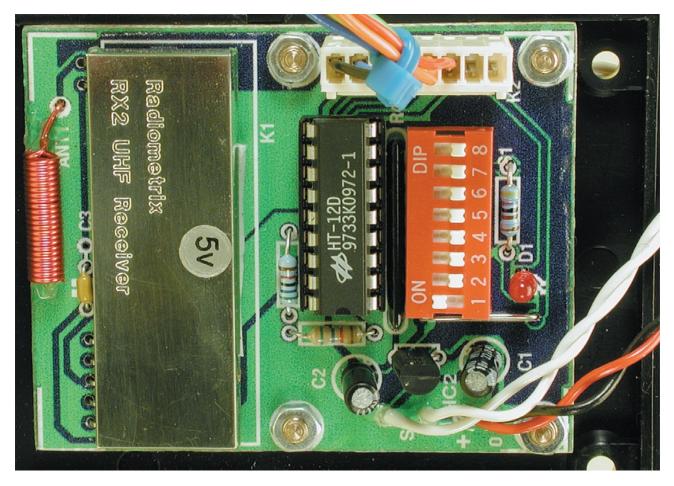

As you can see in **Figure 1**, the circuit is very simple and consists of three sections: an infrared (IR) receiver/demodulator type IS1U60 (IC3), an 8-pin AVR microcontroller AT90S2343 (IC1) and a power opamp

Figure 1. Circuit diagram of the Learning RC5 Decoder. The L272M power opamp drives a 5-V stepper motor.

motor driver L272(IC2).

The IR receiver/demodulator receives the modulated RC5 data stream and provides a demodulated 5-V digital output for processing by the microcontroller. If you can not get hold of the Sharp IS1U60, the Siemens near-equivalents SFH505A, SFH506 or SFH5110 may be used instead. These IR decoders are not pin compatible hence their pinouts are shown in the circuit diagram. Although the SFH505A is now 'obsolete' according to Siemens, you may still manage to get your hands on one.

The microcontroller used is an AVR AT90S2343 8-pin device. This tiny device includes 2k of Flash program memory and 128 bytes of nonvolatile EEPROM user memory. An internal oscillator runs at 1 MHz and the efficient design of the processor enables processing approaching 1 MIPs. The microcontroller is available ready-programmed through our

1/2001

#### Readers Services.

The processor has five I/O pins, all of which are used in the present design:

- PB3 is used as the RC5 data input, active Low.

- PB4 reads the PROG jumper (PROG mode selected when Low).

- PB1 and PB2 are the UP/DOWN outputs to drive the L272 motor driver (the UP/DOWN indicator LEDs are also driven via these pins).

- PB0 doubles as the motor enable output (when Low) and the PROG mode indicator (when High).

The L272 motor driver operates in the following way:

The two -inputs are tied together and connected to a potential divider R4-R11 that sets the voltage of these pins to approx. 2.5 V when the enable output (PB0) is Low. In this mode, taking input pin 7 High and the corresponding input pin 6 Low will drive the separate outputs of the L272M High and Low respectively. Reversing the input pins (6 High, 7 Low) will reverse the outputs hence reversing the direction of the motor.

If the PROG output (PB0) is HIGH the opamp is disabled because the -pins (8 and 5) are pulled to +5 V, making it impossible to turn On either half of the opamp.

The 10- $\Omega$  and 100- $\Omega$  resistors and the

## DIY AT90S Microcontroller

Those of you with access to an AT90S programmer will be pleased to know that the source code (Bascom AVR Basic) and the Hex file for the microcontroller used in this project are available from the Free Downloads section of our website at <u>http://www.elektor-electronics.co.uk</u>. Look for file **# 000081-11.exe** under the December 2000 items. corresponding supply filter capacitors serve to filter out any supply noise present on the 5-V rail.

The quiescent supply current of the unit is negligible and the operating current is determined by the current drawn by the motor used.

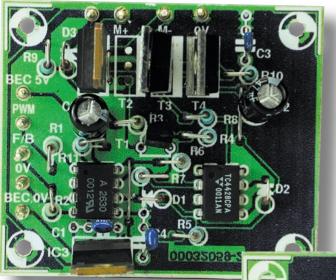

#### Construction

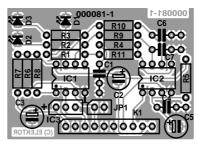

The unit is constructed on a small singlesided PCB as shown in **Figure 2**. IC2 may be either soldered directly or fitted in a DIL socket as preferred, but the microcontroller (IC1) should be fitted in a socket.

If it is intended to use the board as a standalone control, a straight pin header can be fitted in position K1 and the power supply and motor connections made directly to the pins. The IR sensor may be connected with flying wires to enable it to be sited remotely.

If it is intended to incorporate the unit into an existing piece of equipment then the pin header can be plugged into a suitable female connector (socket).

#### Operation

The unit is extremely easy to set up and operate. On power-up the unit will first check the PROG jumper and if set will enter PROG mode:

#### PROG mode

The red (PROG) LED will light and the Down LED (D2) will flash to indicate that the Volume Down key on the remote must be pressed. Once the command (and remote control system address) have been correctly received the Down LED will stop flashing and the UP LED with start to flash. The Volume Up key is now pressed on the remote and once correctly received the red PROG LED will go out and the unit will enter NORMAL mode:

#### NORMAL mode

In this mode the unit continuously monitors the IR sensor and if it detects the programmed volume Up/Down commands will drive the motor (+/-) outputs in the appropriate direction. If the key is held down the motor will continue to turn until it is released.

On power-up (assuming the PROG jumper is not set) the unit will look to see if there is valid data stored in the non-volatile memory for the stored commands. If none is found (i.e. the first time the unit is powered up, or if the data has been lost for some reason) the unit will automatically enter PROG mode as described above.

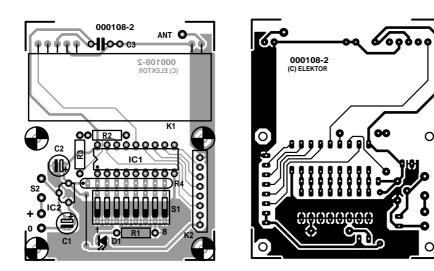

Figure 2. Copper track layout and component mounting plan of the small PCB designed for the control (board available ready-made through Readers Services).

#### **COMPONENTS LIST**

**Resistors:** R1,R2,R3 =  $1k\Omega$ R4,R6,R8-R11 =  $100k\Omega$ R5 =  $10\Omega$ R7 =  $100\Omega$

**Capacitors:** C1,C4,C6,C7 = 100nFC2,C3,C5 =  $22\mu F$  I6V radial

Semiconductors: DI,D2,D3 = low current LED ICI = AT90S2343-10PC, Publishers

#### order code: **000081-41** IC2 = L272M

#### Miscellaneous:

- JPI = 2-pin pinheader with jumper. KI = 10-way SIL pin header for

- board edge mounting.

- IC3 (not on board) 36 kHz centre frequency IR receiver/demodulator, e.g., IS1U60 (Sharp) SFH506-36, SFH5110-36, SFH5110 (Siemens).

- PCB, Publishers order code **000081**-

- Disk, project source code and Hex file, order code 000081-11

Figure 3. Compare your work against this working prototype of the Learning RC5 Decoder.

(000081-1)

# Universal Mobile Telephone Service

# Part 2: Third generation mobile technology

By G. Kleine

The introduction of Third Generation mobile phones will offer vastly increased data capacity ensuring the proliferation of mobile Internet use and new multimedia uses.

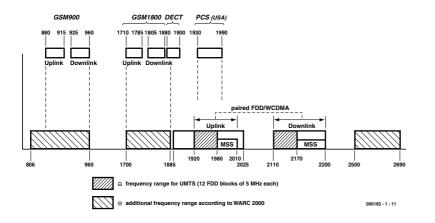

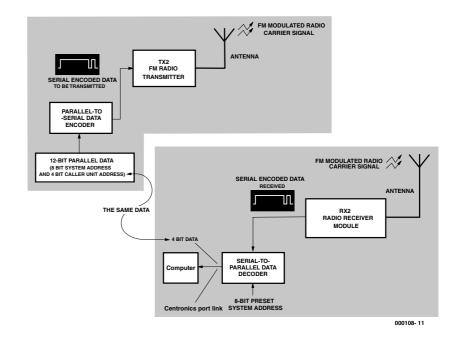

To ensure that global roaming would be possible for third generation mobile phones the World Radiocommunications Conference (WRC) in 1992 defined the operating frequencies for UMTS to be 1885 MHz to 2025 MHz (uplink) and 2110 MHz to 2200 MHz (downlink). Uplink is defined as information passing from the subscriber to the base station while downlink is information passing from the base station to the subscriber. **Figure 1** shows UMTS frequency allocation. The upper band of these frequencies

is reserved for future Mobile Satellite Service (MSS). The core frequencies for Frequency Division Duplexing (FDD) with W-CDMA modulation are 1920 MHz to 1980 MHz for the uplink and 2110 MHz to 2170 MHz for the downlink. These maintain a duplex distance of 190 MHz between the uplink and downlink. FDD is favoured by Nokia and Ericsson and provides identical capacity for the uplink and downlink channels. Cur-

rent GSM systems use FDD with respect to the uplink and downlink capacity. An alternative to FDD is the Time Division Duplexing (TDD) System that has been standardised by Bosch, Siemens and Alcatel. A major advantage of this standard is the use of non-paired frequency bands thereby allowing unsymmetrical channel capacity between the uplink and downlink channels. This is much more suited to the 'bursty' nature of TCP/IP data exchange that occurs when accessing Internet information. In this case uplink data could consist of little more than a web page address which results in a downlink data flow of many pages of data. For FDD a Duplex bandpass filter with relatively sharp cut off characteristics is used to prevent coupling of send and receive data. With TDD equipment it is necessary to strictly control the synchronisation between the base stations so that adjacent cells can function correctly together and that the entire network can operate synchronously.

The two UMTS frequency ranges each 60 MHz wide split into 12 channels each with a 5 MHz bandwidth are at the moment available for use in European countries and in the majority of Asian countries. In the USA the situation is not quite so clear. The USA currently uses the

Figure 1.UMTS frequency allocation.

1.9 GHz band for its second generation phone network called Personal Communications System or PCS. The plan here is to free-up some of these frequencies for UMTS use in the coming year.

It is also anticipated by the WRC-2000 that the 806 MHz to 960 MHz band will be used for UMTS when the current GSM era comes to a close. The 1710 MHz to 1885 MHz will also become available when the DCS 1800 service comes to an end. Apart from these frequencies there is also a part of the spectrum which is currently used by DECT cordless phones. Lastly 2500 MHz to 2690 MHz is also eventually anticipated to be used for future capacity increase of the UMTS network in.

#### **UMTS frequency licences**

The allocation of these highly desirable 5 MHz frquency pairs has been handled differently in different countries. In Spain, Norway and Sweden for example, these licences have been distributed on a practically cost free basis whereas in most other countries they have been auctioned off to the highest bidder. Here in the U.K. five licences were available and four of these went to the big hitters

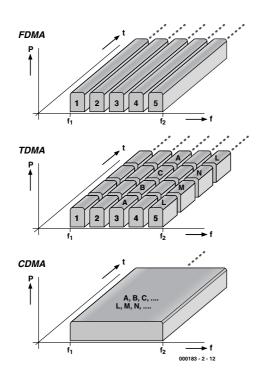

Figure 2. FDMA, TDMA and CDMA access methods.

in the mobile phone world: Vodafone, BT3G, one2one (owned by Deutsch Telecom) and Orange (owned by Vodafone but currently on the transfer list). The fifth licence was awarded to TIW, a relative newcomer comprising Canada Telesystem International and Hutchison Whampoa of Hong Kong. The U.K. auction for 3G licences raised £22.48 Billion for the Government.

More details of the licencing can be found in UMTS forums on the Internet.

#### A refined modulation method

The classical methods of providing multiple communication channels by using FDMA and TDMA were described in part 1 of this article in the previous issue of *Elektor Electronics*. Figure 2 shows diagrammatically how the channel is subdivided in frequency and time when either FDMA or TDMA is used. Another method that we have not looked at yet is also shown. UMTS will use a Code Division Multiple Access (CDMA) method. CDMA allows all users to send simultaneously using the same frequency. At first glance this may seem a very poor method: If everyone is using the same frequency how is it possible to select just one transmitted signal at the receiver? A simple filter would attenuate all channels equally because they are all sending on the same frequency. The key to this method is that each transmit and receive channel is assigned a unique code or 'Pseudo Noise' (PN) sequence. Transmitted data is combined with this sequence before transmission. At the receiver, we detect what just seems like noise from these many transmitters all sending together however when this received 'noise' is passed through a correlator which uses the same code sequence as the transmitter, the original transmitted signal is magically recovered.

This concept may be difficult to grasp but as an analogy imagine that you are having a conversation with a friend in a lift. The lift stops and two people enter conversing in Japanese, next two people enter conversing in Russian. If we assume (crucially) that everyone in the lift can only understand their own language then you can see that these three conversations can occur simultaneously without any mix-up of information. Somewhere deep in your brain the equivalence of correlating the sounds at your ears with the code sequences of the English language is occurring.

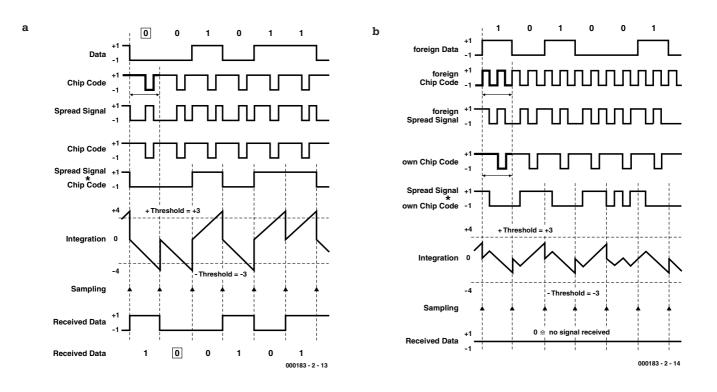

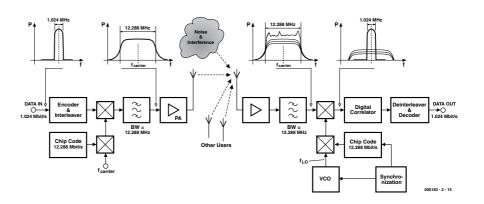

The process of spreading can be seen as sacrificing a narrow bandwidth signal for a signal that can operate in a high noise environment and is more immune to noise. A simplified example is given here in **Figure 3**.

# **GENERAL**INTEREST

Figure 3. The principle of CDMA communication. a) Reception of the desired signal b) Reception of an unwanted signal.

Encoding of the transmission signal and reception of the desired signal with the correct Chip sequence is shown in **Figure 3a**. The Chip sequence data rate is four times the actual data rate in this example. Processing gain is a measure of by how much the bandwidth of the data signal is increased by the spreading process. It is defined as the ratio of the chip rate to the data rate. Each input data bit is multiplied by a four bit long chip sequence. A high is +1, a low is -1 and no signal is 0. The resultant transmitted data signal after multiplication with the spreading signal has a bandwidth of four times the data rate.

By signal reception the input data integrator is initially at set to zero. The integrator amplitude is given by the processing gain for the system. The sample time of the waveform occurs at the end of each integration period. The sampling threshold is here set to +3 and -3. At the output of this process we have recovered the actual data stream which was input to the transmitter with an additional time delay.

Figure 3b shows the same process but this time with an unwanted signal with an unknown chip sequence. The first two lines show the unwanted data signal and its chip sequence. Line three is the spread signal. As before line four is the chip sequence used by the receiver here we are using the same chip sequence as in Figure 3a. The next line shows the product of the above two lines and this is input to the integrator. We can see that at no point during the integration process does the signal step above or below the +3and -3 threshold so the output remains at zero. Zero indicates that no signal has been detected. From this we can see that the chip sequence should be carefully chosen so that it has a sharp auto-correlation peak i.e. that it does not allow any other unwanted code to be mistaken for the desired code. Crosscorrelation between two chosen chip sequences should be as small as possible (optimally zero).

#### The Wideband variant

Originally CDMA was used in a military environment and employed a relatively narrow signal bandwidth of 100 kHz. UMTS signals require a bandwidth of 5 MHz in order to support a data rate of 2 Mbit/s and a chip rate of 4,096 Mbit/s. The correspondance of the chip rate to the data rate is relatively small (2 Mbit/s or 2 MHz) yielding a relatively small processing gain. This low processing gain means that when several subscribers are sending on the same frequency it is crucial that each received signal must reach the receiver with approximately equal signal strength in order that the integration process at the receiver functions correctly (see The near/far problem of W-CDMA). Good quality receivers must be employed in the base stations and in the mobile handsets along with transmitter stages with good linearity otherwise intermodulation products will have adverse effects on the signal quality.

# A W-CDMA communication system

A simplified block diagram of a W-CDMA communications system is shown in Figure 4. This example uses a data stream of 1,024 Mbits/s and is passed through an encoder and interleaver. The interleaver provides error protection by shifting bit positions so that the effects of interference bursts are distributed throughout the data stream and can be corrected once the signal is deinterleaved at the receiver. The resultant data stream is now multiplied by the chip sequence (12.288 MB/s in this example). This processing is equivalent to performing an XOR

## **GENERAL**INTEREST

operation between the data and the spreading code (also known as 'chipping'). A bandpass filter limits the signal bandwidth to that of the chip rate. The original bandwidth of 1,024 MHz is spread to 12,288 MHz and the processing gain is 12.

The signal is now passed through the power amp (PA), to the antenna. As the signal travels through the ether to the receiving antenna it is subject to interference and noise. It also mixes with transmissions from other mobiles using the same frequency. The resulting noise-like signal is picked up by the receiver antenna, amplified by the input amplifier (LNA) and filtered through the chip rate bandwidth filter. The signal is now passed to the correlator this will mix the signal with a locally generated chip sequence that must be synchronised with the transmitter chip sequence. At the output of the correlator the actual transmitted data stream is reconstituted. Now after the de-interleaving and decoding the DATA OUT signal will correspond to the original DATA IN signal at the input.

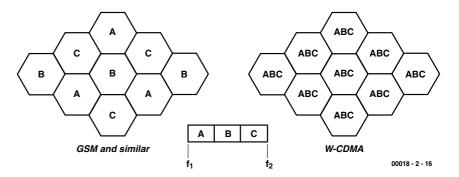

**Figure 5** shows the comparison between the present day radio cell structure compared to the radio cells that will be used in the W-CDMA system. Uplink and downlink capacity can be adjusted according to needs.

# The near/far problem of W-CDMA

The principle that many subscribers in the same cell can use the same frequency relies on the necessity that each signal arriving at the base station must have approximately equal signal strength so that the decorrelation process can function correctly. This applies to the mobile 5 km away from the base station as well as the user just across the road from the base station. This is the so called near/far problem and going back to our analogy, it is equivalent to some people in the lift shouting, this is sure to upset everyone else's ability to carry on their conversation.

Unwanted signals cannot be removed with filters because they are using the same frequency as the desired signal. The method used in W-CDMA is for the base station to

Figure 4. W-CDMA Communication system.

dynamically control the power output of each mobile so that the received signal strength at the base station from each mobile is equal. The output power of a UMTS mobile will need to be adjustable over a range of 70 dB i.e. 1:10 million! The power amplifier must also be capable of a switching speed of 1500 gain steps per second. In contrast current GSM mobiles only need to alter power output a few steps per second.

#### The future looks bright

Many companies are currently cooperating to develop UMTS base stations and prototypes of UMTS handsets. Key players in the production of net equipment and base stations are Ericsson (Sweden) and Nokia (Finland). Both companies have collaborated closely with research facilities and institutions to produce the first prototype of a UMTS system. Nokia has also won many contracts in China and Ericsson is collaborating with Vodafone to provide pilot implementation of a UMTS system in the UK.

Alcatel and Fujitsu are jointly working on development of GPRS, EDGE and UMTS technology and are in the process of promoting this on a bus tour of Europe demonstrating the principles and possibilities of new UMTS technology. Many companies are already producing dedicated UMTS chipsets. Infineon Technologies of Austria have a purpose built UMTS development centre This facility goes under the name of Danube Integrated Circuit Engineering (DICE) and it has already in April 2000 delivered the first UMTS chip for the Japanese market. Toshiba Corporation have also set up a small Telecommunications Research Laboratory in Bristol with the aim of developing UMTS chipsets.

As for the implementation timescale for UMTS it is anticipated that by 2001 we can expect the first field trials of a UMTS network and by the end of 2002 the system should be partially implemented leading to total coverage by 2005.

By 2010 GSM will probably still have many users, especially using GPRS and EDGE enhancements.

(000183-2)

Figure 5. Radio cells and frequency use

# PC Serial Peripheral Design (5)

# Analogue measurements

By B. Kainka

So far in this series we have used the PC only with digital signals: switching, monitoring and counting. Now we turn to the analogue domain: our programs will understand not just 'yes' and 'no', but 'larger' and 'smaller'.

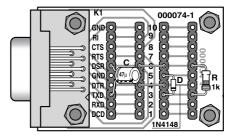

Figure 1. Charging and discharging a capacitor

If a voltage is applied to a serial port input, it will be read as either a logic Low (0) or a logic High (1). The PC cannot determine the actual voltage present. Likewise, if a resistor is con-

Figure 2. Charge/discharge curves and definition of the time constant T

nected between an output that has been set high and an input, there are only two possible results: either the resistor is sufficiently small that a clear logic one is read at the input, or it is not. If more precision is required, a new approach is needed.

#### **Charging and discharging**

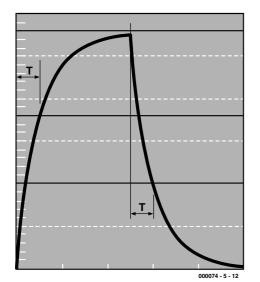

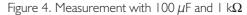

If computers are good at one thing, it is counting. We can use this to measure time: a program simply counts the seconds (or milliseconds) that pass until a certain event happens, for example when an input changes state. If we can convert an analogue quantity such as a resistance into a time period, then it will be easy to measure it with a computer. In this example, we can use an RC network. **Figure 1** shows a capacitor C charged and discharged through a resistor R. A time constant *T* is associated with an RC network:

#### T = RC.

Here *T* is the time taken for the voltage across the capacitor to reach 63.2 % (=1-1/e) of its final value. This can be derived from the exponential charging characteristic, shown in **Figure 2**. We shall not go into the details of the physics here: it is enough to know that the time taken to charge to a given voltage is directly proportional to the capacitance and to the value of the resistor.

For a 100  $\mu {\rm F}$  capacitor and a 1 k $\Omega$  resistor we have:

$T = 1000 \ \Omega \times 0.0001 \ F = 0.1 \ s = 100 \ ms$

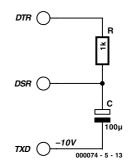

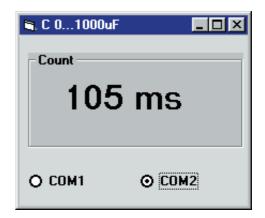

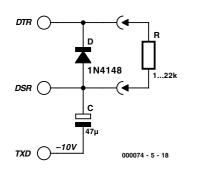

A doubling of the resistance leads to a doubling of the charging time. The same goes for a doubling of the capacitance. So, we can measure the charging time and deduce the value of either one of the resistor or the capacitor, if the value of the other is known. All that is needed is a program that replaces the switch in Figure 1. Figure 3 shows a simple circuit where the capacitor is connected not to ground but to the TXD output. There is a good reason for this: if an electrolytic capacitor is used, it must never be charged with the wrong polarity, and this is guaranteed as long as TXD remains at -10 V.

The circuit charges and discharges the capacitor via DTR and uses the DSR signal as an input to determine when the set voltage is reached. The threshold voltage will be around 1.5 V. Comparing this with the overall voltage range of -10 V to +10 V, we see that the threshold is about 11.5 V/20 V = 0.575 = 57.5 % of the final voltage. This is not too far from our value of 63.2 % given above for the time constant. In any case, the error factor introduced is constant and can be compensated for later. There are other sources of error, which we discuss below.

# **BEGINNERS**COURSE

```

Listing I. Measuring the time constant in milliseconds

```

```

Private Sub Form_Load()

i = OPENCOM("COM2,1200,N,8,1")

If i = 0 Then

i = OPENCOM("COM1,1200,N,8,1")

Option1.Value = True

End If

If i = 0 Then MsgBox ("COM Interface Error")

TXD 0

RTS 0

DTR 0

Counter1 = 0

Timer1.Interval = 2000

End Sub

Private Sub Form Unload(Cancel As Integer)

CLOSECOM

End Sub

Private Sub Timer1 Timer()

DTR 1

TIMEINIT

While (DSR() = 0) And (TIMEREAD() < 1501)

DoEvents

Wend

Label1.Caption = Str$(TIMEREAD()) + " ms"

DTR 0

End Sub

```

#### **Counting time**

The time measurement takes place in a 'while' loop as shown in Listing 1. The loop runs until either DSR becomes set or the count reaches 1.5 seconds (timeout). The measurement loop includes the command DoEvents: this allows Windows to process other events that may be occurring in the system. During measurements the user can still use the mouse and other applications, and indeed stop the program itself. This is reassuring for the user, especially when bugs in the program cause it to function incorrectly. In general it is always necessary, when programming loops, to consider how the loop can be forced to terminate. Otherwise if the program gets into an infinite loop the PC will need to be reset, either by switching it off and on again, or by using the familiar Ctrl-Alt-Del chord. Adding DoEvents call makes the loop safe; but this has a cost in timing accuracy, adding an uncertainty of around 1 to 3 milliseconds to the measured time.

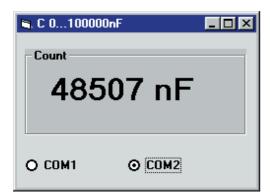

#### $\mu \mathbf{F} \mathbf{not} \mathbf{ms}$

If the units 'ms' in the window in Figure 4 are replaced by ' $\mu$ F', the value shown is not too far off the true

one. As we said above, a 100  $\mu F$  capacitor and a 1 k $\Omega$  resistor give a time constant of 100 ms. Similarly, with a 10  $\mu F$  capacitor we have a time constant of 10 ms. This can be tested by trying various capacitors from the junk box. Often there will be quite a large discrepancy between the value measured and the value printed on the capacitor: this is down to the large tolerance (as much as 50 %) quoted for electrolytics. The capacitance of an electrolytic often changes if it is stored for a long time.

The measurements are less accurate for very large electrolytic capacitors, with values of say around 1000  $\mu$ F. The indicated value will be too small. The reason for this lies in the program: the charged capacitor must be discharged, which also requires time. Our program uses a timer with a period of two seconds: one second is used for charging the capacitor up to the input threshold voltage; the remaining second, however, is not enough to discharge the capacitor completely. The next charge therefore takes less time. There is a simple solution: a diode can be used to accelerate the discharge cycle. Figure 5 shows the circuit diagram, and Figure 6 shows how it can be constructed. With this modification to the circuit we can

Figure 5. Improved capacitance measurement circuit

000074 - 5 - 16

Figure 6. Construction details.

# **BEGINNERS**COURSE

Figure 7. Capacitance display in nF

Figure 8. Circuit 1 with 10 k $\Omega$  potentiometer.

Figure 10. Charging time plotted against charging resistance

```

Listing 2. Modifications for program Cmeas2.frm

Private Sub Timer1_Timer()

F = 1.19

DTR 1

REALTIME (True)

TIMEINITUS

While (DSR() = 0) And (TIMEREADUS() < 1500000)

Wend

T = TIMEREADUS() * F

REALTIME (False)

T = Int(T)

Label1.Caption = Str$(T) + " nF"

DTR 0

End Sub</pre>

```

#### Listing 3. Measuring the time constant in microseconds

```

Private Sub Timer1_Timer()

DTR 1

REALTIME (True)

TIMEINITUS

While (DSR() = 0) And (TIMEREADUS() < 1500000)

Wend

t = TIMEREADUS()

REALTIME (False)

Label1.Caption = Str$(t) + " us"

DTR 0

End Sub</pre>

```

#### Listing 4. Determining the charging resistance

```

Private Sub Timer1_Timer()

DTR 1

REALTIME (True)

TIMEINITUS

While (DSR() = 0) And (TIMEREADUS() < 1500000)

Wend

T = TIMEREADUS()

T = T * 1.000000001

R = 2200 + 7800 * (T - 76300) / (294600 - 76300)

REALTIME (False)

R = Int(R)

Label1.Caption = Str$(R) + " Ohm"

DTR 0

End Sub</pre>

```

reliably measure capacitors up to about 1500  $\mu$ F. Larger values are possible if more time is allowed by making the appropriate changes to the program. The timeout value in the measurement routine and the overall timer period must both be increased, so that the program waits long enough for the measurement to be completed.

What about capacitors smaller than 1  $\mu$ F? In principle the charging resistor could be increased. However, a problem then arises: the impedance of the DSP input (around 3 k $\Omega$ ) introduces measurement errors that get more and more severe as the value of the charging resistor is

increased. This problem could for example be overcome using an operational amplifier with a high input impedance, but this is outside the scope of this series.

#### Software enhancements

It is much more interesting to try to get around these limitations in software. In particular it is possible to use a timer with a resolution of one microsecond. This increases the resolution of the capacitance measurement one thousandfold, allowing measurements in nanofarads (**Figure 7**). Library PORT.DLL provides functions TIMEINITUS and

# **BEGINNERS**COURSE

TIMEREADUS for this purpose, where 'US' stands for microseconds ( $\mu$ s). These functions are used in **Listing 2**.

When we consider making measurements in microseconds, we must look at the effect of Windows on the timing accuracy. In principle other process running in parallel can interrupt the measurement program and cause large inaccuracies. This can be prevented by raising the priority of the measurement task, for which a special function is provided in PORT.DLL. Using REALTIME (True) we can obtain greater reliability. It is essential to set REALTIME (False) after the measurement has been taken. The exact accuracy achieved depends on the PC: with a 200 MHz Pentium MMX we measured variations of about 50  $\mu$ s in the measured value; with a faster PC this may be reduced. If the same experiment is carried out in Delphi, the timing accuracy is about 20 times better. The method is described in the Elektor Electronics book 'PC Interfaces under Windows', to be published soon). It is nonetheless impressive that an interpreted language such as Visual Basic can achieve such timing accuracy.

Alongside these changes to the program, we can also improve the basic accuracy of the measurements. We have already seen two sources of error in the simple equation t/ms = $C/\mu F$ , namely the threshold voltage being slightly too low and the input impedance of the DSR signal. There is a third source of error: the DTR output does not switch exactly between -10 V and +10 V, but has an internal resistance of roughly 430  $\Omega$ . The charging resistance is therefore in effect about 1430  $\Omega$ . Further, this internal resistance is non-linearly dependent on the current. The TXD output also has an internal resistance, making the voltage on the capacitor slightly higher than expected. The effects are too complicated to be analysed mathematically, and so we take the course preferred by experienced engineers in the face of a complicated calculation: test; measure; calibrate. All the errors can be condensed into a single correction factor F which can be determined with a calibration measurement. For this we require a capacitor whose

1/2001

value is accurately known (or which can be accurately measured). Then the correction factor can be adjusted until the reading is correct. On the author's PC the value of F was found to be 1.19; this value can of course be used on any PC, but there will be individual variations from machine to machine which can only be compensated for by determining the correct value of F in each case.

#### **Resistance measurement**

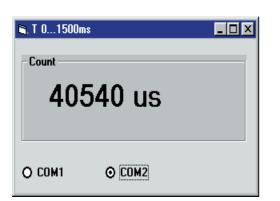

We can measure resistance using the same method; this is similar to the way that potentiometers are read by PC games cards. The circuit for measuring resistance is shown in **Figure 8** and is essentially the same as the capacitance-measuring circuit. Here, however, we use a fixed capacitor and work with various resistor values.

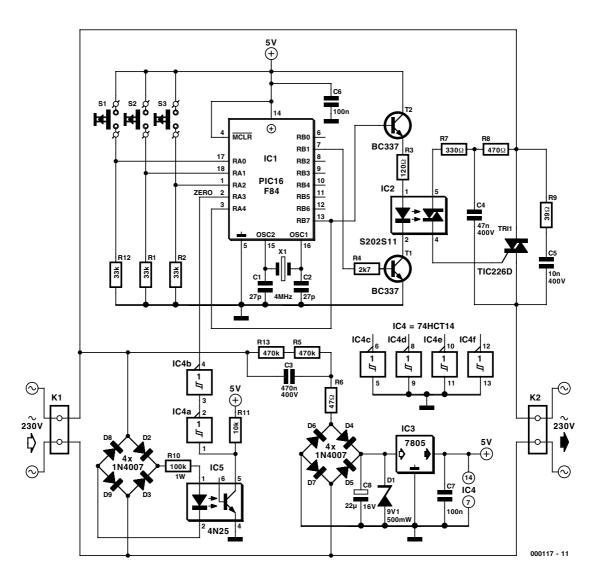

To test this circuit we use the program (**Listing 3**) which measures the charging time to the highest accuracy. We use again the technique described above for measuring small capacitors: REALTIME (True) gives us good timing accuracy. **Figure 9** shows how the results appear on the screen.

The circuit can be tested using metal film resistors with a tolerance of 1 %. Measurements with an accurate ohmmeter indicate that in general the tolerance of such resistors is rather better. A set of tests using  $C=47 \,\mu\text{F}$  gave the following results:

| $\mathbf{R}/\mathbf{k}\Omega$ | T/ms  |

|-------------------------------|-------|

| 0                             | 33.7  |

| 0.1                           | 34    |

| 0.22                          | 34.5  |

| 0.56                          | 37.9  |

| I                             | 45.5  |

| 2.2                           | 76.3  |

| 4.7                           | 147.5 |

| 6.8                           | 204.9 |

| 8.2                           | 245.9 |

| 10                            | 294.6 |

| 15                            | 433.7 |

| 22                            | 661.2 |

From the numbers alone a strong linear dependency can be seen. An exact determination of the linearity is possible using a graph: an analysis using Excel produced the curve shown in **Figure 10**. It can be seen that linearity is good between around 2.2 k $\Omega$  and 10 k $\Omega$ .

Figure 11. Measurement using a 15 k $\Omega$  resistor.

The reasons for deviation from the ideal linear curve are the same as were found in measuring capacitance. With very small charging resistances we get an error due to the non-linear internal resistance of the DTR output driver; with large resistances (say around 22 k $\Omega$ ) the low impedance of the DSR input causes error.

The data obtained can be converted into an explicit equation which will let us calculate a resistance with high accuracy. **Listing 4** shows the measurement routine for resistance. The calculation in question reads:

R = 2200 + 7800 \* (T - 76300) / (294600 - 76300)

Using this formula we can obtain a measurement accuracy of around 1 % in the range 1.5 k $\Omega$  to 15 k $\Omega$ . It should be borne in mind. however, that this function, specific to a particular PC, will not give the same accuracy on a different machine. The various measurements and calculations must be carried out afresh for each PC. It is sufficient to measure the charging times for two resistors, say 2.2 k $\Omega$  and 10 k $\Omega$  and substitute these in the formula. Failing this, it is possible simply to consider where the greatest sources of error lie: in this case our attention turns immediately to the electrolytic capacitor. Electrolytics often have a capacitance very different from the value printed on them, which has a significant effect on the charging time for a given resistance. If a suitable correction factor is inserted in the line

#### T = T \* 1.000000001

then this error will be compensated for, and reasonably usable results (see **Figure 11**) can be obtained. A correction factor of greater than or less than one will be required according to whether the capacitor has a value lower or higher than nominal.

(00074-5)

29

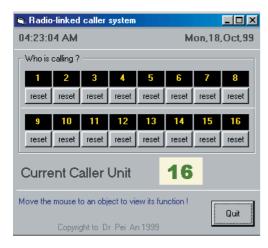

# Microprocessor Controlled Light Dimmer

# with pushbutton control

Design by P. Staelens

This easy to construct light dimmer is controlled by a PIC controller and can handle a maximum current of 6 A. Three pushbuttons ensure extremely user-friendly operation.

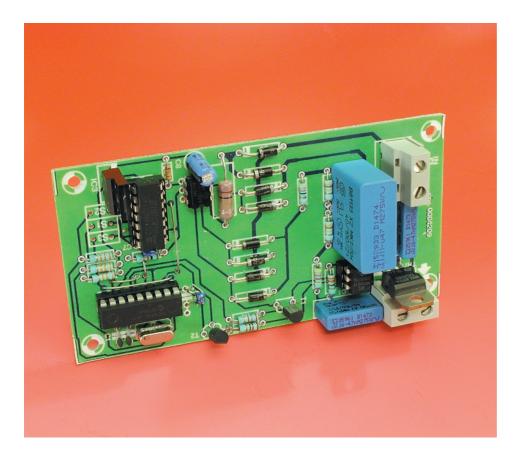

The light dimmer described here can be split into two parts. The light dimmer proper follows the familiar recipe. It is an analogue circuit, which uses a triac for phase control of the mains voltage. This is hardly a surprise. A little more striking is the fact that this dimmer circuit is not controlled with a simple potentiometer but with a programmed PIC16F84 processor. The processor is operated with the aid of three pushbuttons: a combined on/off button, an up and a down button.

#### **Usage Instructions**

The microprocessor is programmed in such a way that the dimmer will be in the 'off' position when first powered up, while at the same time the control circuit starts off in the

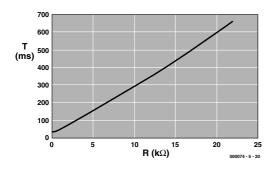

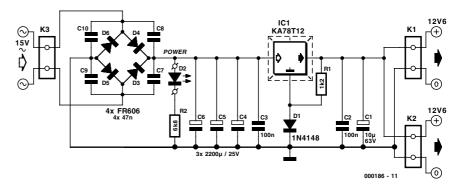

Figure 1. The classic triac light dimmer is driven from a programmed PIC16F84 processor.

'fully open' position. Pushing the on/off button activates the dimmer, only then will current be supplied to the attached lamp. However, it is also possible to adjust the control circuit before the dimmer is activated; in other words, it makes no difference whether the dimmer is activated or not.

#### Operation

The dimmer schematic is shown in **Figure 1**. It is immediately obvious that the amount of hardware required is quite small. The various functional blocks will be easily recognised by most of you. At top centre is the PIC-processor, to its right is the triac circuit, at bottom left is the zero-crossing detector and at bottom right is the power supply.

The **processor circuit** is a textbook example and requires no further explanation. The three input pushbuttons are connected to RA0, RA1 and RA2, while the triac circuit is driven from RB1 and RB7. The connection that has been drawn between RB7 and RA4 is now actually superfluous. Initially, the software used this connection to sense if the dimmer was on or off. Later on this was changed to enable the processor to keep track if this itself.

Now to the **triac circuit**. This is also a textbook example, with the exception that the triac (TRI1) is driven by a triac-driver (IC2). This provides separation between the low voltage and the high voltage circuitry. This is required because ground of the 5 V power supply has a different potential with respect to the high voltage circuit. T1 and T2 control the triac driver. These two transistors together perform an AND-function. The drive signal is applied only when both transistors conduct (RB1 and RB7 high). Snubber network R9/C5 protects the triac from inductive loads.

In order to determine the exact trigger point, a zero-crossing detector is indispensable. IC5 (optocoupler 4N25) is the most important part in this sub-circuit. A separate bridge rectifier drives the light source in the optocoupler. This is because the other bridge rectifier does not provide phase information of the mains, due to the presence of C3. The 100 Hz voltage applied to the input of IC5 causes the transistor in the optocoupler to block briefly at every zero crossing of the mains voltage. As a consequence, at every zero crossing there is a short 5-V pulse at the collector of this transistor. This signal is applied to the processor via the double Schmitt-trigger IC4a/IC4b. This makes it possible for the software to synchronise itself to the mains.

Finally, the power supply. As can be observed, the required 5 V supply voltage is derived directly from the mains, without the use of a transformer. 'AC resistor' C3 reduces the mains voltage to an acceptable level. This reduced voltage is rectified by a bridge rectifier (D4-D7) and regulated by a 7805. Diode D1 prevents the input voltage of IC3 from exceeding safe limits. Two 100 nF capacitors are used for power supply decoupling.

Because a 5 V power supply appears harmless, we would like to stress that this voltage in this instance is everything but safe! The reason is that this power supply is not electrically isolated from the mains. Be very careful!

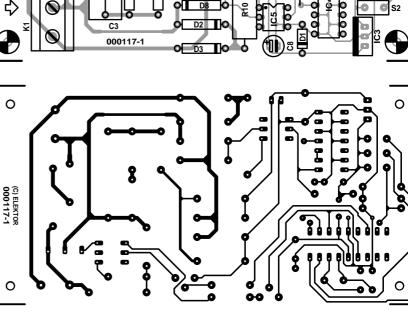

#### Construction

Figure 2 depicts the layout for the PCB designed for the project. The construction of the light dimmer is a relatively simple task, because the number of components required is very modest, and the PCB and programmed PIC are available from the Elektor Electronics Readers Services (the source code files as well, for that matter).

We again urge all prospective constructors to take the utmost caution. The entire circuit is directly connected to the mains! Despite the presence of an optical triac driver and an optocoupler, the entire low voltage circuit is not electrically isolated from the mains. Keep this in mind while testing and making measurements on this circuit.

Another important practical matter is that for C3, C4 and C5, Class-X2 capacitors must be used. These are short-circuit proof and are guaranteed never to cause a short circuit in the event that they develop a defect. If you intend to fit the circuit into a typical enclosure, it may be better to mount voltage regulator IC3 horizontally. This can be achieved by bending IC3 over the top of IC4; do not trim the leads too short, otherwise this will not be possible.

Because of the compact dimensions of the PCB, finding a suitable enclosure should not be an issue. Use plastic screws and standoffs to fasten the PCB, in order to maintain the required insulation spacing between mains voltage and parts that may be touched. Our prototype was built into a plastic case from Bopla. The PCB fitted nicely, but it was necessary to shorten the internal stand-offs by some 3 mm for the cover to be fitted properly.

(000117-1)

Semiconductors: D1 = zener diode 9.1V 500mW D2-D9 = IN4007TI, T2 = BC337Tril = TIC226DICI = PICI6F84-04, programmed, order code 000117-41 (see Readers Services page) IC2 = MOC302IIC3 = 7805IC4 = 74HCT14IC5 = 4N25

#### **Miscellaneous:**

SI,S2,S3 = pushbutton with make contact, safety Class 2 XI =4 MHz quartz crystal KI,K2 = 2-way PCB terminal block, lead pitch 7.5 mm Case: e.g. Bopla (Conrad-Electronics order code 52 22 52-11) PCB, order code 000117-1 (see Readers Services page) Project disk (PIC source code files), order code 000117-11

**]**0-6

ici.

oolloc

0 R3

0 D7

D6

0 05 10

Тю́

Figure 2. The PCB has everything clearly arranged and is compact. Keep in mind that the entire circuit is connected to the mains!

#### **COMPONENTS LIST**

C) ELEKTOR -211000

> **Resistors:**  $RI,R2,RI2 = 33 k\Omega$  $R3 = 120 \Omega$  $R4 = 2k\Omega7$  $R5,R13 = 470 k\Omega$  $R6 = 47 \Omega$  $R7 = 330 \Omega$  $R8 = 470 \Omega$  $R9 = 39 \Omega$  $RI0 = I00 k\Omega I W$  $R|I = 10 k\Omega$

#### **Capacitors:**

$CI, C2 = 27 \, pF$  $C3 = 0.47 \mu F 400 V (Class X2)$ C4 = 47 nF 400 V (Class X2) C5 = 10 nF 400 V (Class X2) C6.C7= 100 nF  $C8 = 22 \,\mu\text{F}$  I 6 V radial

# **Stand-Alone MP3 Players**

# a new lease of life for the old PC

By H. Baggen

MP3 players are now in the shops in assorted colours and varieties, with different price tags, from small Walkman-like players using solid-state memories to full-blown CD players for use in the living room.

Cramming a CD-R with MP3 files is an excellent way of ensuring many hours of listening pleasure. But the real joy is, of course, found in playing home-burned CDs on a home-made MP3 CD player.

MP3 music files are compressed in such a way that they are easily transferred via a relatively slow medium like the Internet. Not surprisingly, MP3 gained its popularity entirely from the Internet. Thanks to the excellent sound quality offered by MP3 files, this particular file format has also become popular on equipment other than the PC. The arrival of portable stand-alone MP3 players gave the format a considerable boost. However, because the memory cards used in these players are relatively expensive and limited in respect of storage capacity, a new phenomenon has emerged: the MP3 CD. A home-burned CD-R of less than a pound each has enough capacity for 10 hours worth of MP3 files. Although off-the-shelf players (both portable and more residential ones) are now available for these CDs, it is, of course, more fun to build one yourself. Surprisingly, that is easily achieved with some old computer parts.

So what's needed to build my own player for MP3 CDs? The answer is: an old motherboard with at least a Pentium 100 or 133, a computer power supply, a CD-ROM drive, a sound card and (optionally) an old hard disk. On the Internet we came across several websites describing the construction of a stand-alone MP3 player from not

1/2001

much more than the above components.

The first example to be mentioned here is **mpMan** from Mirko Roller. Mirko built an MP3 CD player based on an old Pentium-100 motherboard. He employs a 2-line LCD as a display. At the time of writing (mid-November 2000) Mirko was busy developing a boot image for the CD, which allows а bootable MP3 CD to burned that's he capable of starting the system at poweron. A floppy disk or hard disk drive is then

superfluous. The source code for this project is available from Mirko's website.

The aim of the Spanish project dubbed MP3Case Car Stereo Player is to bring MP3 music into your car. The project was started in 1998 and employs a souped up Pentium-133. The system is built in a separate case, and WinAmp is used as the MP3 program. Even a remote control is catered for. Although fairly extensive construction notes and a parts list are available, not everything is to be had in English. If you are really interested in this design, we reckon there's no way to avoid brushing up your Spanish or seek the help of a translator.

Though Andie's MP3 CD Player

Index / Indice nting C English/Inglés Montando e GreenGrou Castellano/Spanish Take a look at the Working Ha Making of/Hazlo tú Los conectores de A closer look vista del m A Whole view of the MP3Case Car Stered mpleta del

> Project is also based on 'scrap' PC components, he manages to cram it all into a case of the size of regular CD player with a height of just 7 cm. The case then contains a CD-ROM drive as well as a 20-GB hard disk drive which easily holds up to 340 hours worth of music. A nice detail of this design is that it incorporates a webserver, allowing the user to compile and edit playlists using a web browser.

> > (015005-1)

- O ×

mpMan - Build your own MP3 player: http://www.dvz.fh-koeln.de/~bn520/mp3.html MP3Case Car Stereo Player: http://members.nbci.com/\_XMCM/mpcase/ english.htm Andie's MP3-CD-Player Project:

http://homepages.compuserve.de/asdevel/ mp3-cd-player.htm

3 🕂 2 🖻 🛎 📽 🖏 🏶

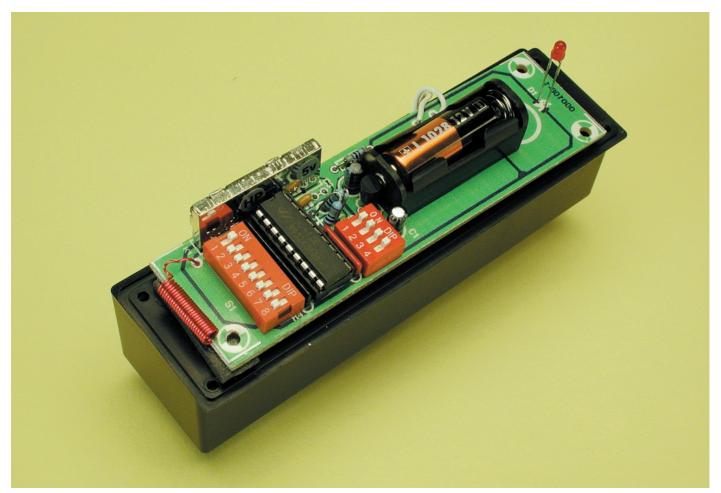

# Emulator for 27C256 EPROM

# with RS232 control

Design by B. Legrand and D. Mautaulon

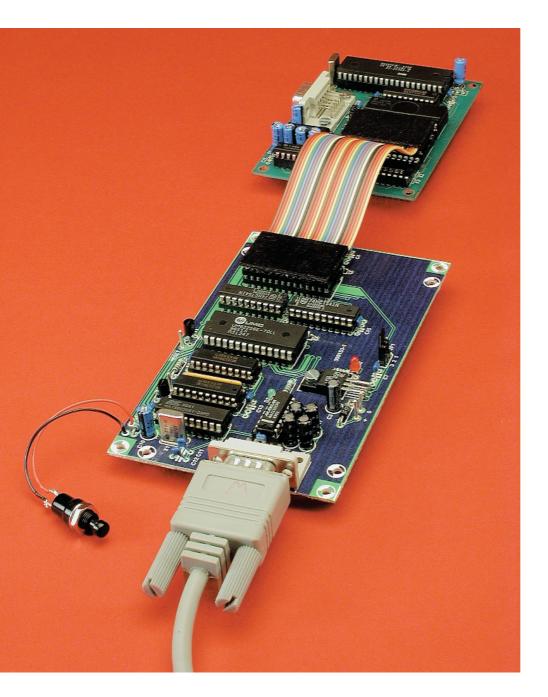

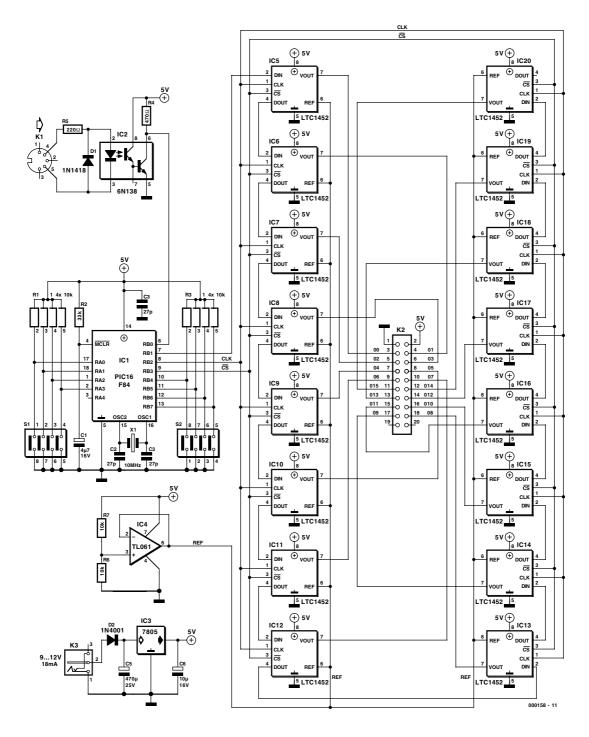

Going through our archives we discovered that it's been almost ten years since we published an EPROM emulator. The version we propose in this article should meet today's demands of hobbyists wishing to debug microconsystems troller based on an EPROM. We have chosen the 27C256 because it is cheap and currently the most widely used EPROM the in hobby area.

# MICROPROCESSOR

## Technical features

- Emulates the most widely used EPROM type 27C256

- RS232 controlled

- Employs HyperTerminal for data transfer between PC and EPROM simulator.

- Recognizes industry-standard

IntelHex format

- May be adapted to suit 27C64 and 27C128 by modifying circuit around pins 26 and 27. Support for 27C512 also possible with some hardware and software modifications.

An EPROM emulator is a development tool designed to facilitate code debugging and code writing jobs on circuits incorporating an EPROM (electrically erasable read only memory). An EPROM, as most of you will know, can not be reprogrammed before its previous contents has been erased through exposure to a certain amount of ultraviolet (UV) light. So, even for the smallest modification to the code in your EPROM, you need to do a complete eraseand-reprogram cycle, which is tedious and costly given the time lost and the price of an UV eraser box.

An EPROM emulator obviates these problems by allowing you to debug, rewrite and download code as many times as you like, until the desired system operation is achieved, all without having to erase a single EPROM. Having extensively tested the target program, you need to program an EPROM just once yet rest assured that it will work as planned.

Meanwhile, in this day and age of Flash reprogrammable and ISP (insystem programmable) devices, it is fair to reflect on the advantages, if any, of an EPROM emulator. Also, one can not fail to recognise the trend towards ever larger memory capacities.

Despite the above trends, there is still a fair number of circuits based

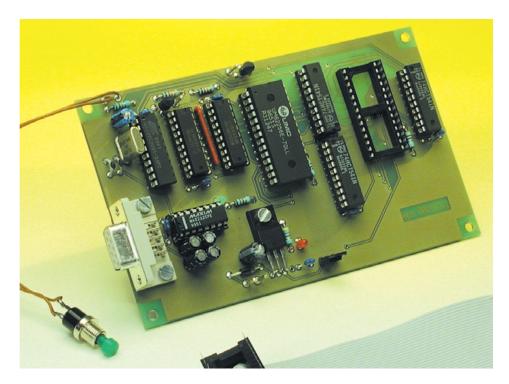

Figure 1. Block diagram of the 27C256 EPROM emulator, with the Atmel microcontroller clearly at the hub of things.

on microcontrollers running code from an external EPROM. These controllers include devices from the 8051 series, the 68HC11 and 80C5xx. It is precisely in this area where the present emulator will be highly valued.

#### **Principle of operation**

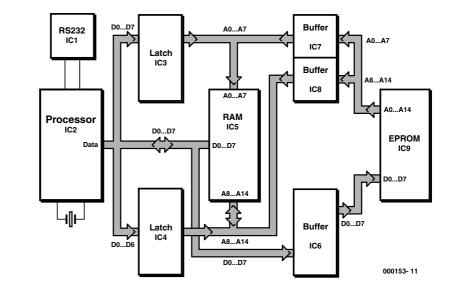

The block diagram shown in **Figure 1** is classic and typical for this type of application.

The underlying principle of an EPROM emulator is that it replaces 'dead' memory like ROM or EPROM by 'live' memory (RAM) with double (two-port) access. The RAM is flanked by two latches and supported by a microcontroller.

As in any EPROM emulator that's any good, the heart of the circuit is a RAM device (here, IC5) which essentially replaces the (E)PROM of the target (or 'host') system. The RAM is surrounded by latches (IC3 and IC4) and buffers (IC6, IC7 and IC8). The exact function of these components will be discussed a bit further on.

The distinctive feature of the present EPROM emulator (as compared with traditional designs) is the presence of a microcontroller (IC2). This component looks after the control of the latches and the RAM, and also handles the correct reception (from the PC) and processing of the object code to be transferred to the target system. Here, an Atmel 89AT2051 microcontroller is used. The main reason for choosing this device is that it offers on-chip serial I/O as well as EPROM to store the firmware that handles the code reception and control of the emulator.

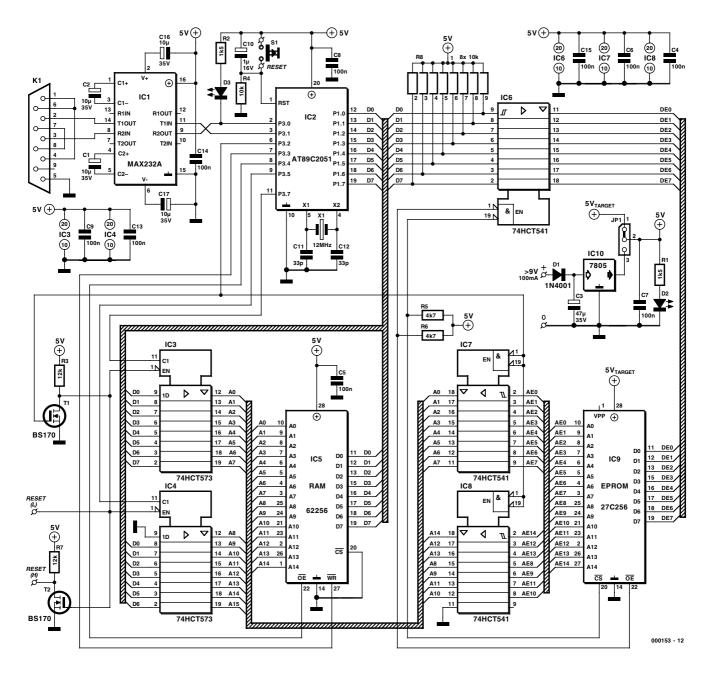

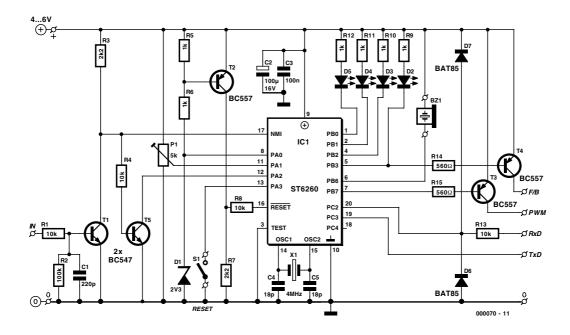

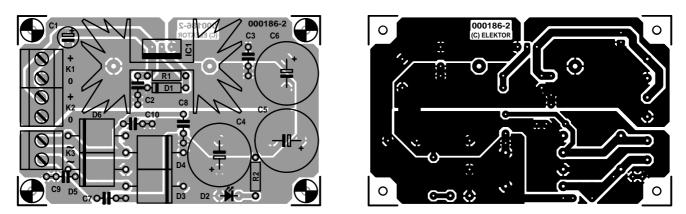

#### **Practical circuit**

By and large, the circuit diagram shown in **Figure 2** follows the general structure of the block diagram. In fact, all building blocks discussed above are fairly easy to find back in the schematic.

IC1, a MAX232, handles the classic function of converting the  $\pm$ 10-V signal levels on the RS232 lines to logic levels (+5 V/0 V), in two directions. The MAX232 allows the microcontroller in the circuit to communicate with the PC via the RS232 port. Although many PCs these days are capable of handling serial signals with a swing of 5 V, simply omitting the MAX232 would require the RxD and TxD signals to be inverted!

IC2 is the microcontroller type AT89C2051. It controls latches IC3 and IC4 as well as buffers IC6, IC7 and IC8. These integrated circuits ensure the correct interfacing with RAM IC5. In this context, 'correct' means that the RAM may be accessed by either the microcontroller or the external (i.e., target) circuit, but never at the same time.

The RAM in fact emulates (mimics) the (E)PROM which has been removed form the target circuit. When the target circuit has access to the RAM, it will behave as if a system (E)PROM was installed, hence the term 'emulator'. To be able to pull off this trick, the RAM requires two peripheral devices. From

# **MICRO**PROCESSOR

Figure 2. Circuit diagram of the 27C256 EPROM emulator.

one side, the emulator electronics enables the object code under test to be written into the RAM, while from the other side the external (host) system can access the RAM to read code which the host microcontroller will eventually execute.

Latches IC3 and IC4 connect the host system address lines to the RAM. Depending on commands received from the microcontroller, these ICs transfer the data on the internal databus, D0-D7. Each of the latch enable inputs is controlled by an individual I/O line of the central processor. This configuration allows the processor to control the RAM address bus. Once the target program is stored in RAM, the two latches go into highimpedance mode to avoid contention problems when the system switches to emulation mode, i.e., with the RAM effectively connected into the target system.

Buffers IC6, IC7 and IC8 ensure the quasi-connection of the RAM address and datalines to the external (host) circuit.

#### **Power supply**

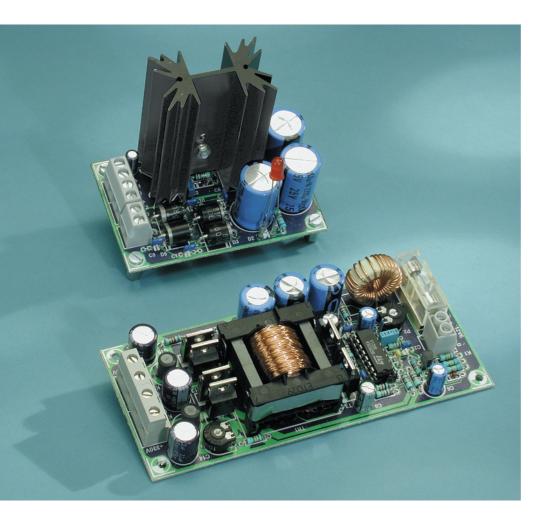

The 27C256 EPROM emulator may be powered in two ways. The first, which we will treat as the 'standard' method, consists of powering the circuit by means of a mains adapter.

The on-board power supply consists of a three-pin voltage regulator type 7805 (IC10) in a classic configuration. This component provides the +5-V regulated supply voltage to the emulator circuitry. Because only 100 mA or so of output current is required, the 7805 has an undemanding job in this circuit. Diode D1 protects the circuit against reverse polarised input voltages. LED D2 acts as a power on/off indicator.

The second method consists of powering the emulator from the target (host) system, which will be possible in most cases because +5 volts will be present for the digital circuitry around the (E)PROM. If you envisage using this method all the time, you may omit components IC10, diode D1 and capacitor C3 from the emulator circuit.

Jumper JP1 (located near the voltage regulator) allows you to select between internal and external powering.

#### The serial link

The communication between the PC and the emulator consists of twoway traffic via the RS232 port, for which suitable circuitry and cable lines have to be present.

On the emulator board, the RS232 interface consists of a MAX232 (IC1)

in its standard application circuit with four pump capacitors. Sure, we could have used the SMA version of the MAX232 and enclosed the complete serial interface in a sub-D connector case for easy connection the PC. However, to keep construction as easy as possible we decided to fit all the parts that make up the interface on the emulator board. This choice also enables an off the shelf serial cable to be used.

A note about the RS232 link this should consist of a **standard** RS232 cable, i.e., not one with 'crossed wires' (also known as null/zero-modem cable).

#### How it works

The operation of the EPROM emula-

tor may be divided into two phases: (1) loading the RAM, and (2) simulating an (E)PROM in the target system.

For the first task, the PC transmits, via its serial port, the hexadecimal code to be stored in the pseudo EPROM. For the second function, if the target system is to gain access to the code, it is necessary for the microcontroller to pull its port line P3.2 logic Low to actuate 3-state drivers IC7 and IC8. Two FETs, T1 and T2, keep the host system in the reset state.

Let's see how this works in more detail. At power-on, the microcontroller, IC2, prepares all circuitry for data to be written into the RAM. This is done by pulling all lines of port P3 to logic High, with the exception of P3.5 and P3.7.

For the microcontroller to get control over the RAM it has to pull port line P3.2 to logic High.

#### **COMPONENTS LIST**

#### **Resistors:**

$R1,R2 = 1k\Omega5$   $R3,R7 = 12k\Omega$   $R4 = 10k\Omega$   $R5,R6 = 4k\Omega7$  $R8 = 10k\Omega$  8-way SIL array

#### **Capacitors:**

C1,C2,C16,C17 = 10µF 35V C3 =47µF 35V C4-C9,C13-C15 = 100nF C10 = 1µF 16V C11,C12 =33pF

#### Semiconductors:

DI = IN4001 D2,D3 = high efficiency LED TI,T2 = BS170 IC1 = MAX232 (Maxim) IC2 = AT89C2051 (Atmel), programmed, order code **000153-41** IC3,IC4 = 74HCT573 IC5 = 62256 (RAM) IC6,IC7,IC8 = 74HCT541 IC9 = EPROM being emulated IC10 = 7805

**Miscellaneous:**

KI=9-way sub-D socket (female), PCB mount

PCI-PC4= solder pin

JPI= 3-way SIL pinheader with jumper

SI= pushbutton, I make contact

XI=I2MHz quartz crystal

PCB, order code 000153-I (see Readers Services page)

Disk, project software, order code 000153-II (see Readers Services page)

Elektor Electronics

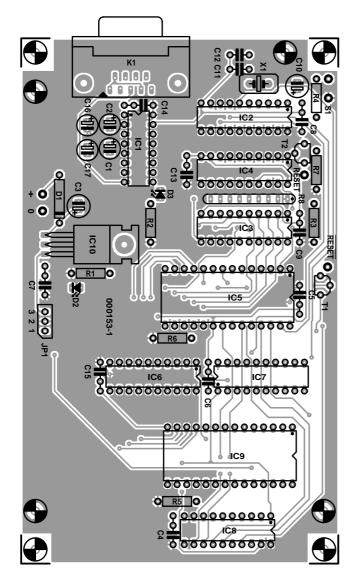

Figure 3b. Copper track layout of the circuit board designed for the 27C256 EPROM emulator. This board is double-sided and through-plated.

To be able to load the RAM, port P1 is supplied with the high address of the first databyte. Next, the 3-state driver IC4 is opened and closed again by means of port line P3.5 in order to block this address.

The above sequence is repeated for the low address, this time with the aid of port line P3.7 controlling another 3-state driver, IC3.

Port line P3.2 of the AT89S2015 microcontroller is programmed to switch the outputs of buffers IC6, IC7 and IC8 to high-impedance (tri-state), which is necessary to ward off all disturbances caused by the external electronics from the RAM during the write process.

The same signal is also inverted by the combination T1-R3. The inverted control signal serves to actuate IC3 and IC4 in such a way that the RAM address lines are properly driven. The control signal on P3.2 is put to the disposal of the target circuit by a pair of solder pins, RESET(L) and RESET(H). One of these signals may be used to keep the target

system in the reset state while the RAM is being filed with object code.

Once the complete object code file has landed in the RAM, the microcontroller in the emulator produces a message on the RS232 port.

The PC has to send the object code file in IntelHex format, via its RS232 port. The processor on the emulator board looks after the correct reception of the file (LED D3 will light while data is being received from the PC), and arranges for each databyte to be written into the RAM at the proper location. This is achieved by IC2 copying address lines A0-A7 on to port P1 and when done producing a pulse on P3.7. Latch IC3 copies this word. The same process is repeated with address group A8-A13. The data transferred by these addresses are latched in IC4 when a pulse appears on port line P3.5. Finally, the actual databyte is copied on to P1, followed by a Low pulse produced on port line P3.3. The latter drives the write ( $\overline{WR}$ ) input of the RAM. When a falling pulse edge appears at this input, the RAM transfers the dataword on port P1 to the specified address.

The same procedure is followed for the transfer of all datawords that make up the object code.

Once the complete IntelHex file has been received, the central processor switches the circuit to simulation mode. More specifically, the RAM is switched to read mode by pulling port line P3.3 Low and enabling the RAM output drivers by pulling  $\overline{OE}$  (output enable) Low. This is achieved by controlling P3.4.

Pulling P3.3 logic Low also

enables the outputs of buffers IC7 and IC8, plus it switches the latch outputs to high-Z (tri-state) by means of the  $\overline{\text{EN}}$  (enable) inputs.

In addition to these important functions, the P3.3 signal disables the two RESET outputs of the circuit. With one the two RESET outputs suitably connected to the target circuit, this will be automatically held in its reset state while the RAM is being loaded with the object code file. Once the RAM is filled, the target circuit is automatically re-initialised (very handy if the target circuit does not have a dedicated reset button or similar).

Port line P3.4 drives the RAM in such a way that the memory chip constantly places data on the internal databus.

To prevent the RAM from supplying data on the external databus, the two enable inputs of buffer IC6 are connected to  $\overline{OE}$  (output enable ) and  $\overline{CS}$  (chip select) lines of the external electronics. This approach guarantees the correct transfer of data from the RAM to the external databus whenever the target system addresses the EPROM simulator.

If new data has to be written into the RAM, you have to press the RESET button to start the file loading process.

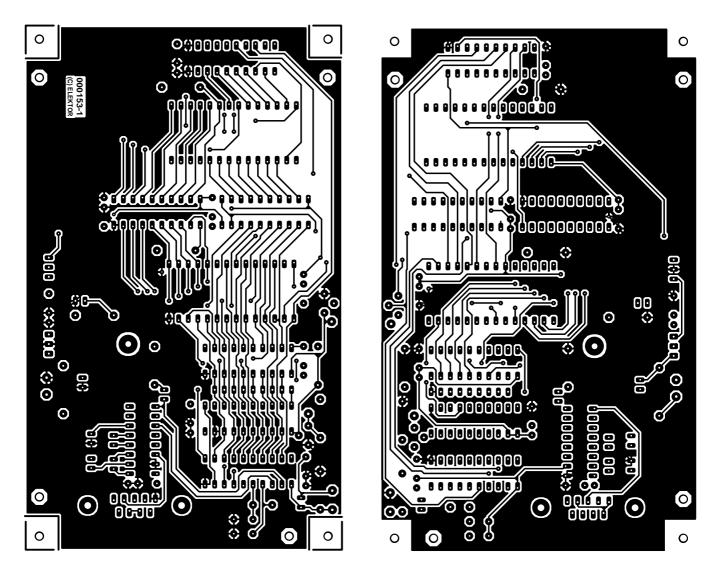

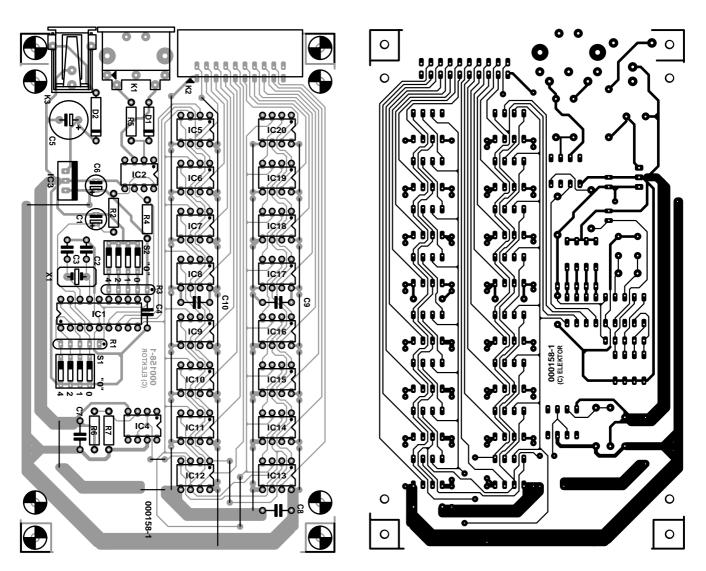

#### Building the EPROM Emulator

As evidenced by the introductory photograph with this article, it would have been possible to make the emulator board even more compact, for example, by 'moving' the MAX232 serial interface to the serial connector casing. As discussed above, this option was not followed to ensure that everyone can build the present circuit from regular size components.

The copper track layout and component mounting plan of the emulator board are given in **Figure 3**. Fitting the parts on the board should not cause problems and a spot-on working construction, we feel, should be within the capacity of most of our readers. The board being doublesided and through-plated, it does not have a single wire link, which otherwise is the most frequently forgotten 'component'!

Figure 4. Finished prototype of 27C256 EPROM emulator.

As customary with this type of project, it is best to start with the low-profile components like resistors, capacitors and transistors. Pay attention to the orientation of SIL resistor array R8, of which the pin with the dot (indicating the common connection) should be at the edge of the board. To cut costs, you may fit only three (high quality) IC sockets, one for the processor, one for the RAM and one for flatcable between the emulator and the EPROM in the target circuit. Note that IC7 is fitted the other way around as compared with the other ICs on the board (except IC1 and IC10).

Give the circuit a thorough check, including a supply voltage check on all ICs, before fitting the processor and the RAM into their sockets. LED D2 will light to indicate the presence of the supply voltage.

#### The software

The program stored in the Atmel microcontroller has been written to allow the Windows HyperTerminal communications utility to talk to the EPROM emulator.

The code transfer from the PC to the emulator is via a serial connection running at 4,800 bit/s.

The emulator recognises Intel

Hexadecimal (a.k.a. IntelHex) which is a widely used format for object code file transfer between PCs and programmers. HyperTerminal is part and parcel of Windows 95 and 98 so everyone running Windows on his/her PC should have it (you'll find it under Programs  $\rightarrow$  Accessories  $\rightarrow$  Communications). The IntelHex file is transferred using the ASCII transmission mode (and not, as you may have expected, a protocol like Kermit or Zmodem).

The communication parameters are set to 4800 bits/s, 8 Databits, No parity, 1 Stop bit (4800,N,8,1)

In HyperTerminal, select the function 'Send Textfile'.

It is also possible to use DOS for the communication between the PC and the emulator. **DOS users** may use this command line:

COPY INTEL.HEX COM1:

Linux users will typically employ

Cat INTEL.HEX \dev\xxx

Where xxx is the port to which the EPROM emulator is connected.

(000153-1)

#### For further reading:

EPROM Emulator II, B.C. Zschocke and N. Breidohr, Elektor Electronics July/August and September 1992.

1/2001

# GBPB — GameBoy Prototyping Board

# A development aid for the GameBoy

Design by L. Lemmens

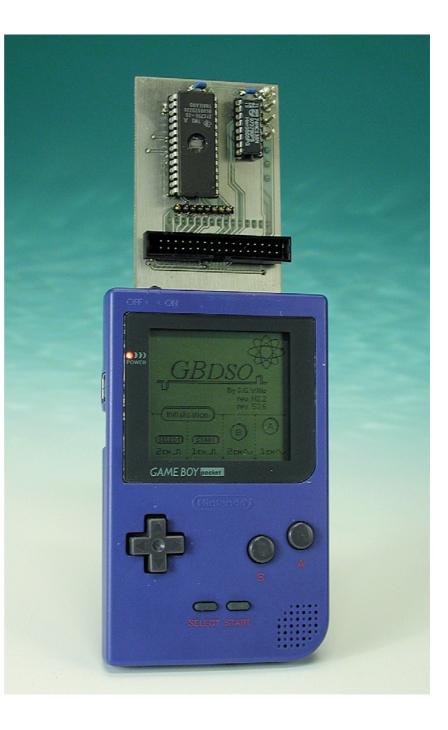

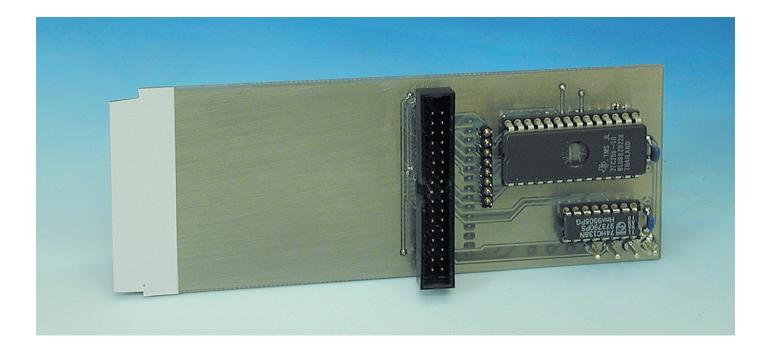

In previous editions we proved beyond doubt that Nintendo the GameBoy is perfectly suitable for more serious tasks than playing games. The sampling oscilloscope described in the October and November 2000 prime issues was а example. In the December 2000 issue, we published a follow-up article on GameBoy **Development Tools. This** month it's time to offer help in the hardware department.

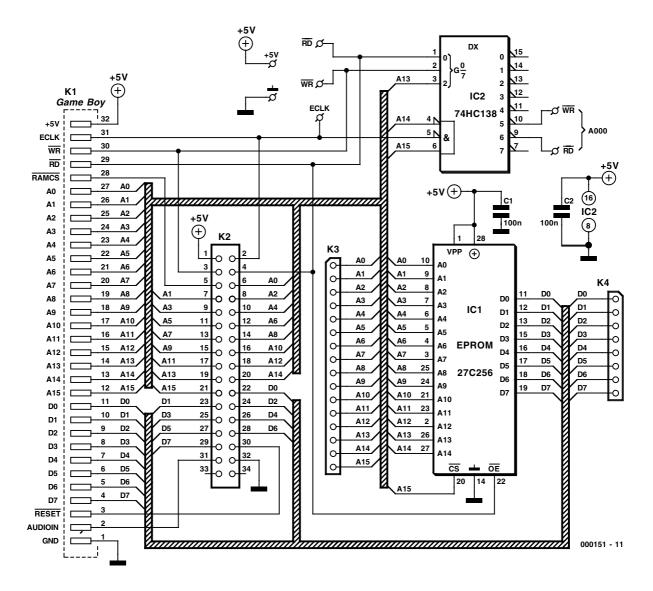

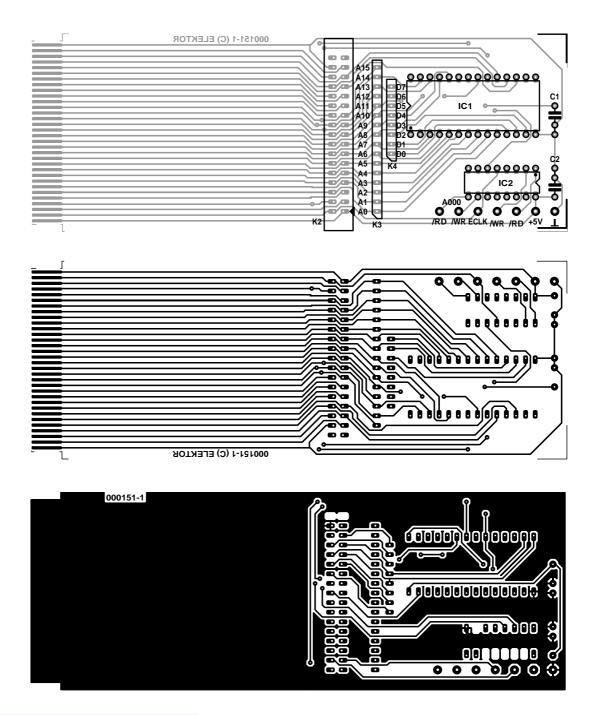

Figure 1. Circuit diagram of the GameBoy Prototyping Board (GBPB)

In the December 2000 issue of *Elektor Electronics* we supplied pointers to a variety of GameBoy emulators that allow software for this extremely popular 'games console' to be tested on a PC. Emulators are fine tools for projects consisting of software only. However, the moment extra hardware has to be linked to the GameBoy, two problems occur: the connector for the (game) cartridge is a Nintendo proprietary design and to make matters worse it is hidden deep in the GameBoy case.

These problems with the card edge connector do not appear when a PCB is designed and etched straight away for the prototype of the circuit you have in mind. Still, because a large part of the cartridge board is hidden by the GameBoy

1/2001

case, it will be hard, if not impossible, to do any measurements on the new board. Sure, it is possible to open the GameBoy case by removing the screws that hold the rear panel. That way you have access to the cartridge board, at least for measurements. However, opening the Game-Boy case is a far cry from the ideal solution because the screws are difficult to remove with an ordinary screwdriver. Moreover, opening the GameBoy case voids the product warranty you may have, and without the rear panel there is no battery case! The most annoying problem is, however, that the prototype is at the rear side of the GameBoy, while the display and controls are located on the front (now who did that design?).

#### A helper board

All of the problems mentioned above are avoided by our prototyping board of which the circuit diagram is shown in **Figure 1**, and the PCB design, in **Figure 2**.