# THE ELECTRONICS & COMPUTER MAGAZINE OCTOBER 1999

£ 2.85

C TOPICS: • FPGAs in theory and practice • use software to test servo motors build your own active SCSI terminator •

poor man's

shortwave radio

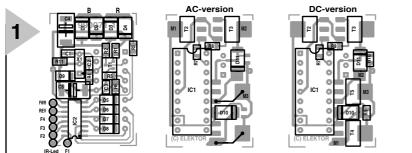

**EEDTs-Pro** locomotive decoder

baitiery charge/refresh station Intelligent & feature-packed

BASIC Stamp course part 2

Elektor Electronics Volume 25 ISSN 0268/4519

October 1999

Number 281 CONTENTS

NFORMATIVE ARTICLES

36 Controller Area Network (CAN) In this second and penultimate part we look at transmission protocols

22

# CONSTRUCTION PROJECTS

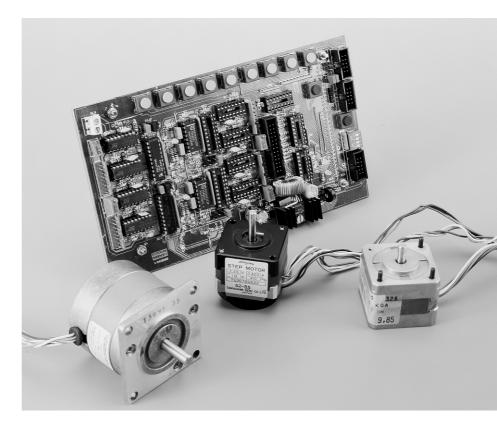

#### 14 Stepper motor control (2)

Description of a microcontrollerpowered stepper motor driver card.

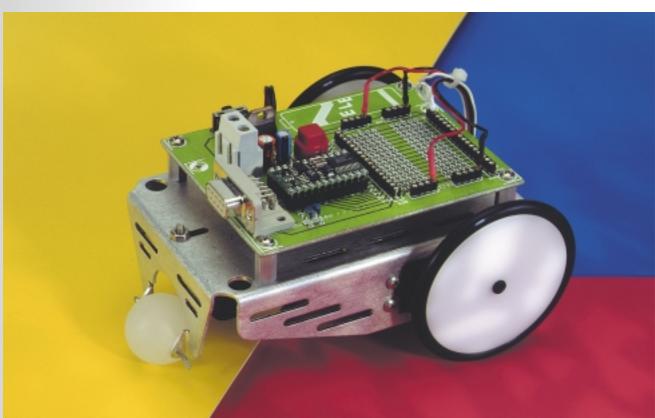

#### 28 BASIC Stamp programming course (2)

This month we tackle the construction of BoE-Bot, a Stamp-powered robotic vehicle.

#### 42 Poor man's shortwave radio

Small, effective and sensitive, all with just two ICs!

#### **Battery charge/refresh** station (1)

Meet our intelligent charge/refresh station for NiCd and NiMH cells and battery packs.

#### 50 EEDTS Pro Super Loco decoder Small, well yes of course, but also compatible with several systems for model train control.

## MISCELLANEOUS

- **New Products** 32

- 56 **Electronics on-line:** watching movies on the PC

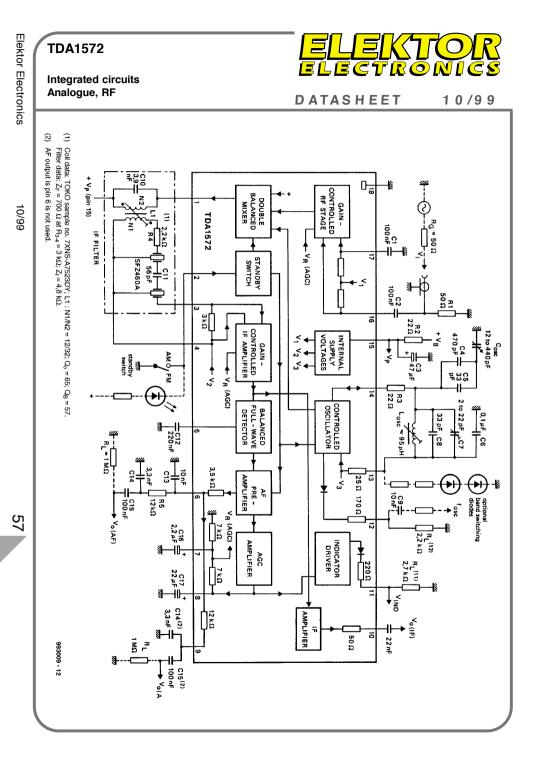

- Datasheets: TDA1572 57

- 59 **Readers Services**

- **Sneak Preview** 66

- Index of Advertisers 66

## THIS MONTH IN PC TOPICS:

- Atmel FPGA design course (1) >

- When Electronics was young (8)

- Build your own active SCSI terminator

- **Corrections & Updates**

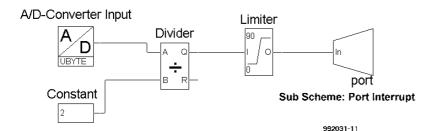

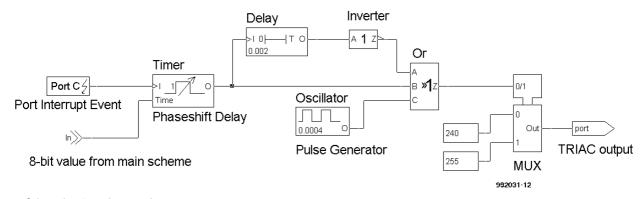

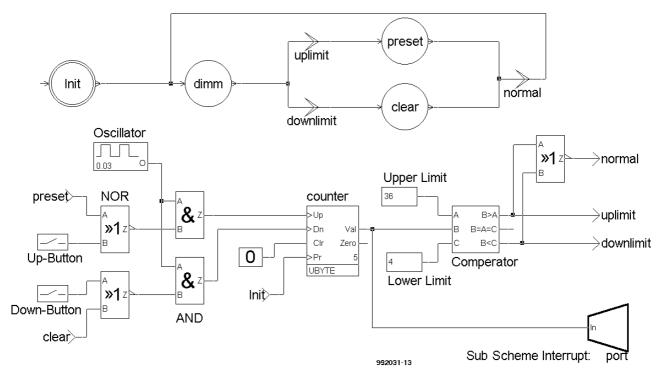

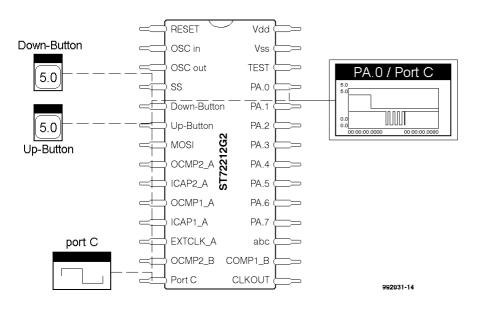

- ST-REALIZER > for ST6 and ST7 microcontrollers

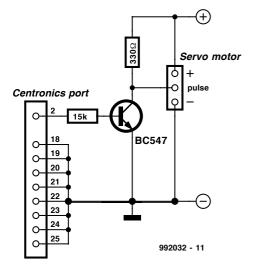

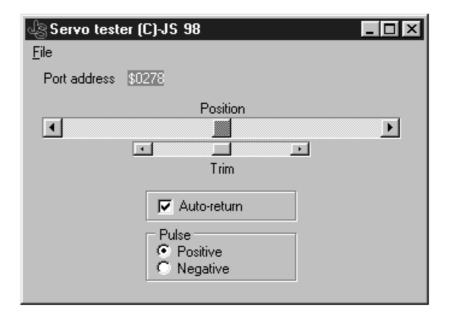

- Minimal servo tester

- Windows 98 Tips & Tricks

MICROPROCESSORS

# stepper motor control

## part 2: SMC, a 80C166-powered driver for 4 motors

Over the past few years, we've witnessed a significant increase in the use of stepper motors. This result is largely due to technological advances and refinements achieved by the semiconductor industry, which currently offers a galaxy of integrated circuits, drivers and power stages specifically developed for the control of stepper motors. The number of ready-made controls complete with power drivers has also seen a remarkable increase.

### Main features

- ♦ 4 power drivers, each having 2 bipolar output pairs for 0.5A or 1.2A phase winding current (PBL3717/PBL3717/2N)

- Current adjusted digitally in 3 steps, or analogue via presets

- Current reduction at no motor action

- Cut-off time 35 μs

- Full and half-step operation, other modes available by reprogramming system GALs.

- LED indicators for clock and direction

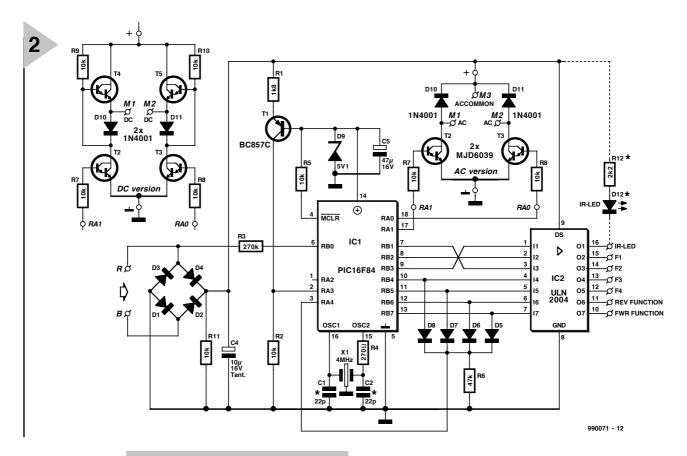

- 4 optocoupler inputs for zeropoint sensors or contacts

- ♦ 8 optocoupler inputs for position sensors or contacts

- 2 serial interfaces

- 10 pushbuttons for manual control

- 1 reset pushbutton

- Power supply 12-40VDC, approx. 2.0A or 4.8A

Design by K. H. Domnick

The key advantage of using stepper motors is the ability to control motor speed and spindle position without the need for a closed control circuit. Drivers and power stages for stepper motors determine the amount of current and the direction of the current sent through the stepper motor windings. For spindle movement, the direction signal has to be complemented with a variable-frequency clock signal. For accurate positioning of the motor spindle, all pulses have to be counted and tallied. Clearly these functions challenge us to use a powerful microcontroller system like the 80C166 board described in the March & April 1999 issues of Elektor Electronics.

The Stepper Motor Control (SMC)

described in this article is the perfect mechanical end electrical companion to the 80C166 Evaluation System. The 80C166 employs tailor-made software to generate all the necessary signals for up to four power drivers on the motor control board, and also handles all information supplied by the available optocoupler inputs, the keyboard and the serial interface.

The construction, dimensions and mechanical assembly details of the 80C166 board and the SMC board are such that they can be housed together under a 42-TE wide front panel in a 19inch case. The power supply is a simple one, turning the mains voltage into 12 to 40 volts d.c. (unregulated). Of course, the output current of the PSU should be adequate for the power drivers and stepper motors you want to use. A step-down voltage converter forms the 5-volt power supply for the HCMOS logic on the motor board.

The 80C166 board may also be used to provide clock signals to other step-

per motor drivers, power stages and direction inputs. This however does require an additional regulated supply voltage of 5 V/300 mA for the board. Because all inputs and outputs are designed for

TTL levels, level converters may be necessary where the board is connected to power drivers or sensors. Pushbuttons and a serial interface on the other hand may be directly connected.

Pushbuttons (Halt/Go) are provided to allow manual control of the stepper motors. As soon as the control becomes complex, however, you'll soon find that the necessary control signals have to be created with the aid of a PC.

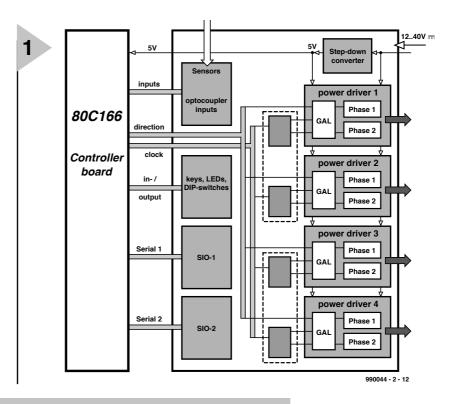

#### THE HARDWARE IN DETAIL

The block diagram of the SMC (stepper motor control) is given in Figure 1. Each of the four (identical) power drivers consists of two stepper motor ICs type PBL3717 or PBL3717/2, a programmed GAL type 16V8 and one half of a re-triggerable monostable multivibrator type 74HC123. The output of the HC123 goes inactive when no clock signal is detected for 35-50 ms. This signal may be used to reduce the motor current when the spindle is not moving. The GAL, or rather its contents, determines the step order and current distribution through the windings its outputs eventually lead to the two stepper motor ICs. These components, in turn, use just a handful of external components to generate the phase currents for the stepper motor windings. Their outputs toggle (change polarity) as a function of the TTL level applied to pin 8 (PH). Two other TTL inputs, pin 9 and pin 7 (IO and I1) set up a comparator threshold of about 420 mV,

Figure 1. Block diagram of the stepper motor control. The program is hidden in blocks SIO1 and SIO2. The 80C166 microcontroller board supplies the necessary direction and clock information.

250 mV, 80 mV or 0 mV. When a coil current starts to flow, the resulting volt-

control inputs on the PBL3717 have to be held low with this method.

Three jumpers at the GAL inputs enable different step modes to be selected:

| Jumper | GAL Pin | Function           | open            | closed         |

|--------|---------|--------------------|-----------------|----------------|

| 1      | 7       | Step mode          | Full step       | Half step      |

| 2      | 8       | Phase current      | 60%             | 100%           |

| 3      | 9       | (Stand by)         | (with Stand-by) | (w/o Stand-by) |

|        |         | Stationary current | 60%             | 100%           |

age drop across the 1- $\Omega$  resistor (Rx1/Rx5) at pin 16 is applied to input pin 10 of the comparator. When this voltage exceeds the set level, the comparator cuts off the current. After a 'cut-off' time of about 35  $\mu$ s (determined by Rx3/Rx7 and Cx2/Cx4), the current flow is established again, and the process starts again.

The power stage will only supply enough current required to either build up or maintain the magnetic field in the phase winding. This is done because the high inductive coil reactance drops to the much lower ohmic resistance of the coil once the magnetic field has been established. Alternatively, this current may be adjusted with the aid of a potentiometer. The bias level set up by voltage dividers Rx4/Rx8 and Rx2/Rx6 is applied to the comparator input where it is effectively added to the voltage drop across the 1- $\Omega$  sense resistor that enables the comparator to cut the motor current. The disadvantage of this arrangement is that it is no longer possible to control the current distribution across the phase windings because all current

Other modes are possible by changing the GAL contents.

For zeropoint searching (spindle 'home' calibration) four optocoupler inputs are available for sensors or contact-less switches with a 'make' function. During a zeropoint search, the stepper motor first turns in the direction of a sensor. When this is actuated, the motor is halted for about 0.2 s. Next, the spindle is turned into the opposite direction until the sensor switches off again. The locating of the zeropoint is acknowledged, and the current motor position is defined as 'zero' or 'home'. When a stepper motor is connected up, you should take into account that the spindle will turn in the direction of the sensor during the zeropoint search.

The activation of one of the other 8 optocoupler inputs is reported individually. In this way, it is possible to detect certain states or when a certain position is reached.

The pushbuttons on the SMC front panel allow the stepper motors to be controlled by hand, as well as parameters to be entered. The preferred

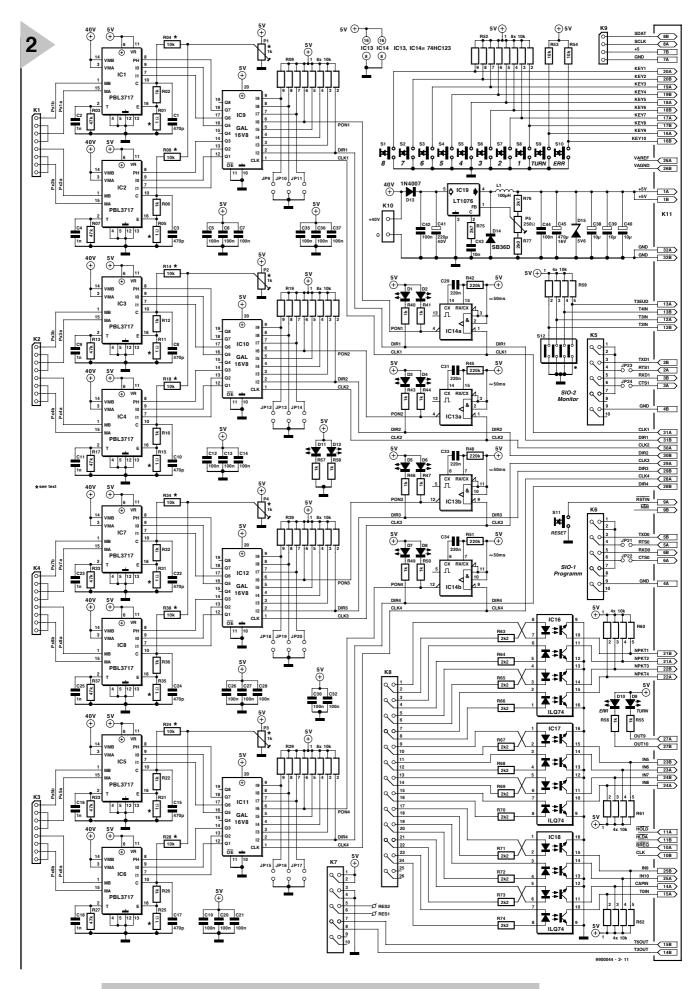

*Figure 2. Complete circuit diagram of the stepper motor control (SMC). Individual circuit functions are clearly identifiable.*

## Connector pinouts

| Function           | Label        | Pin  | (X1) |   | Pin | (X1) | Label        | Function           |  |

|--------------------|--------------|------|------|---|-----|------|--------------|--------------------|--|

| + 5V pwr supply    | + 5V         | 1bc  | 1    |   | 2   | 1a   | + 5V         | + 5V pwr supply    |  |

| O SIO 2 TxD Mon    | P3.8 / TXD1  | 2bc  | 3    |   | 4   | 2a   | P1.12        | O SIO 2 RTS        |  |

| I SIO 2 RxD Mon    | P3.9 / RXD1  | 3bc  | 5    |   | 6   | За   | P2.12/CC12IO | I SIO 2 CTS        |  |

| GND SIO 2          | GND          | 4bc  | 7    |   | 8   | 4a   | GND          | GND SIO 1          |  |

| O SIO 1 TxD Prog   | P3.10 / TXD0 | 5bc  | 9    |   | 10  | 5a   | P1.11        | O SIO 1 RTS        |  |

| E SIO 1 RxD Prog   | P3.11 / RXD0 | 6bc  | 11   |   | 12  | 6a   | P2.11/CC11IO | I SIO 1 CTS        |  |

| + 5V Serial        | + 5V         | 7bc  | 13   |   | 14  | 7a   | GND          | GND Serial         |  |

| I/O Serial Data    | P1.10        | 8bc  | 15   |   | 16  | 8a   | P2.10/CC10IO | I/O Serial Clock   |  |

| l (not used)       | NMI#         | 9bc  | 17   |   | 18  | 9a   | RSTIN#       | l Reset key        |  |

| O 4                | P3.15 / CLK  | 10bc | 19   |   | 20  | 10a  | P2.13/BREQ#  | 01                 |  |

| 02                 | P2.14/HLDA#  | 11bc | 21   |   | 22  | 11a  | P2.15/HOLD#  | 03                 |  |

| I DIP switch Bit 4 | P3.7 / T2IN  | 12bc | 23   |   | 24  | 12a  | P3.6 / T3IN  | I DIP switch Bit 3 |  |

| I DIP switch Bit 2 | P3.5 / T4IN  | 13bc | 25   |   | 26  | 13a  | P3.4 / T3EUD | I DIP switch Bit 1 |  |

| O Output T3        | P3.3 / T3OUT | 14bc | 27   |   | 28  | 14a  | P3.2 / CAPIN | l Pos. Sensor 7    |  |

| O Output T6        | P3.1 / T6OUT | 15bc | 29   |   | 30  | 15a  | P3.0 / TOIN  | l Pos. Sensor 8    |  |

| l Key 10 (Cntrl)   | P2.9 / CC9IO | 16bc | 31   |   | 32  | 16a  | P2.8 / CC8IO | I Key 9 (control)  |  |

| l Key 8 (1)        | P2.7 / CC7IO | 17bc | 33   |   | 34  | 17a  | P2.6 / CC6IO | l Key 7 (2)        |  |

| l Key 6 (3)        | P2.5 / CC5IO | 18bc | 35   |   | 36  | 18a  | P2.4 / CC4IO | l Key 5 (4)        |  |

| l Key 4 (5)        | P2.3 / CC3IO | 19bc | 37   |   | 38  | 19a  | P2.2 / CC2IO | l Key 3 (6)        |  |

| l Key 2 (7)        | P2.1 / CC1IO | 20bc | 39   |   | 40  | 20a  | P2.0 / CC0IO | l Key 1 (8)        |  |

| I Motor zero SM-1  | P5.0 / AN0   | 21bc | 41   |   | 42  | 21a  | P5.1 / AN1   | I Motor zero SM-2  |  |

| I Motor zero SM-3  | P5.2 / AN2   | 22bc | 43   |   | 44  | 22a  | P5.3 / AN3   | I Motor zero SM-4  |  |

| l Pos. Sensor 1    | P5.4 / AN4   | 23bc | 45   |   | 46  | 23a  | P5.5 / AN5   | l Pos. Sensor 2    |  |

| l Pos. Sensor 3    | P5.6 / AN6   | 24bc | 47   |   | 48  | 24a  | P5.7 / AN7   | l Pos. Sensor 4    |  |

| l Pos. Sensor 5    | P5.8 / AN8   | 25bc | 49   |   | 50  | 25a  | P5.9 / AN9   | l Pos. Sensor 6    |  |

| GND                | VAGND        | 26bc | 51   |   | 52  | 26a  | VAREF        | + 5V               |  |

| O LED Cntrl        | P1.9         | 27bc | 53   |   | 54  | 27a  | P1.8         | A LED control      |  |

| O Direction SM-4   | P1.7         | 28bc | 55   | ] | 56  | 28a  | P1.6         | O Clock SM-4       |  |

| O Direction SM-3   | P1.5         | 29bc | 57   |   | 58  | 29a  | P1.4         | O Clock SM-3       |  |

| O Direction SM-2   | P1.3         | 30bc | 59   | ] | 60  | 30a  | P1.2         | O Clock SM-2       |  |

| O Direction SM-1   | P1.1         | 31bc | 61   | ] | 62  | 31a  | P1.0         | O Clock SM-1       |  |

| GND pwr supply     | GND          | 32bc | 63   | 1 | 64  | 32a  | GND          | GND pwr supply     |  |

| Function                | Name                   | Pin       | Pin (X2) |   | Pin (X2) |   | Name         | Function        |

|-------------------------|------------------------|-----------|----------|---|----------|---|--------------|-----------------|

| + 5V pwr supply         | + 5V                   | 1         | 1        |   | 2        | 6 | + 5V         | + 5V pwr supply |

| GND pwr supply          | GND                    | 2         | 3        |   | 4        | 7 | GND          | GND pwr supply  |

| Spare 2                 | Res 2                  | 3         | 5        |   | 6        | 8 | Res 1        | Spare 1         |

| Output T6               | P3.1 / T6OUT           | 4         | 7        | ] | 8        | 9 | P3.3 / T3OUT | Output T3       |

|                         |                        | 5         | 9        | 1 | 10       |   | -            |                 |

| (X2 is not normally use | ed and provided for ex | tensions) | •        |   |          |   |              |                 |

Function Pin (X3) Name Function Name Pin (X3) DTR / DSR0 1 1 2 6 DTR / DSR0 Output TxD1 Prog P3.10 / TXD0 2 3 4 7 P1.11 Output RTS1 Input RxD1 Prog P3.11 / RXD0 З 5 6 8 P2.11 / CC11IO Input CTS1 GND DTR / DSR0 4 7 8 9 GND pwr supply GND pwr supply GND 5 9 10

| Function        | Name        | Pin | Pin (X4) |   | Pin (X4) |   | Name           | Function       |

|-----------------|-------------|-----|----------|---|----------|---|----------------|----------------|

|                 | DTR / DSR1  | 1   | 1        |   | 2        | 6 | DTR / DSR1     |                |

| Output TxD2 Mon | P3.8 / TXD1 | 2   | 3        |   | 4        | 7 | P1.12          | Output RTS2    |

| Input RxD2 Mon  | P3.9 / RXD1 | 3   | 5        |   | 6        | 8 | P2.12 / CC12IO | Input CTS2     |

|                 | DTR / DSR1  | 4   | 7        | ] | 8        | 9 | GND            | GND pwr supply |

| GND pwr supply  | GND         | 5   | 9        |   | 10       |   | -              |                |

\_

method of parameter inputting and control is however by means of the PC and its serial interface. The SMC is capable of reading parameters and commands via its serial input. The serial link is also used to return information to the PC.

#### WITH A HOT NEEDLE...

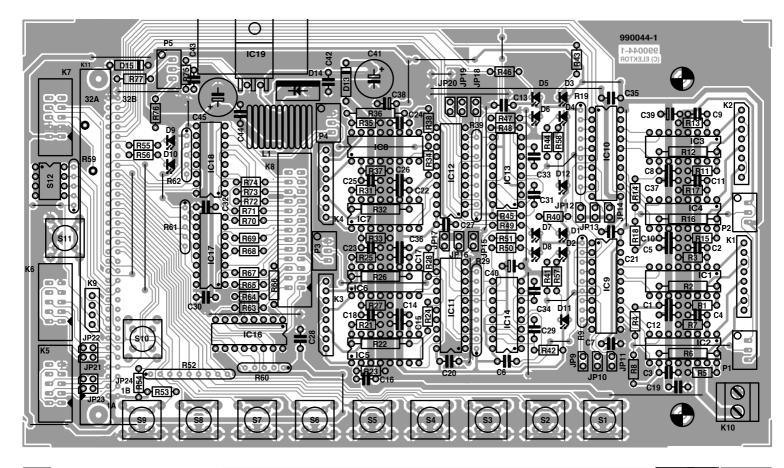

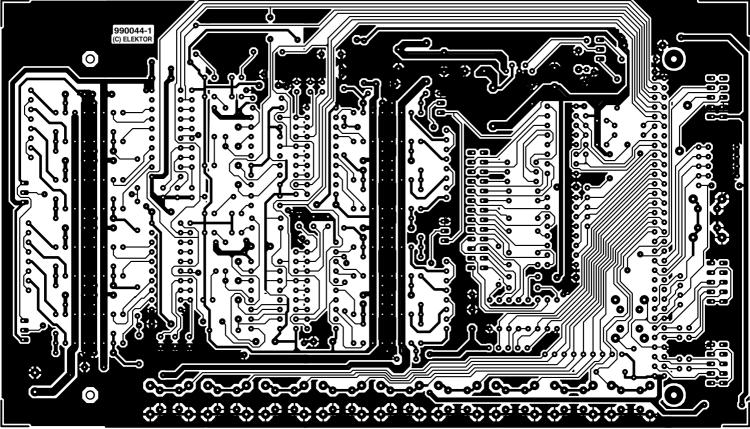

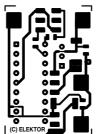

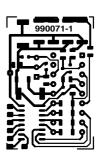

To build up the stepper motor control board you will need solder tin with a diameter of not more than 1 mm. The solder iron should have a fine bit and a tip temperature of about 340 degrees Figure 3. Copper track layout and component mounting plan of the single-sided PCB designed for the SMC. Mechanically it is a perfect match to the 80C166 controller board.

#### **COMPONENTS LIST**

#### **Resistors:**

$R1,R5,R11,R15,R21,R25,R31,R35 = 1\Omega$ (1W for 1.2-A version) R2,R6,R12,R16,R22,R26,R32,R36,R40, R41,R43,R44,R46,R47,R49,R50,  $R55-R58 = 1k\Omega$ R3, R7, R13, R17, R23, R27, R33,  $R37 = 47k\Omega$ R4,R8,R14,R18,R24,R28,R34,R38,R53,  $R54 = 10k\Omega$ R9,R19,R29,R39,R52 = 8×-way 10kΩ SIL arrav R10,R20,R30 = not used  $R42, R45, R48, R51 = 220 k\Omega$ R59-R62 = 4-way  $10k\Omega$  SIL array  $R63-R74 = 2k\Omega^2$  $R75, R76 = 2k\Omega7$  $R77 = 2k\Omega 0$ P1-P4 =  $1k\Omega$  multiturn preset, vertical, (top adjustment)  $P5 = 250\Omega$  multiturn preset, vertical, (top adjustment) Capacitors: C1,C3,C8,C10,C15,C17,C22,C24 = 470pF C2,C4,C9,C11,C16,C18,C23,C25 = 1nF

C5,C6,C7,C12,C13,C14,C19,C20,C21, C26,C27,C28,C30,C32,C35,C36,C37, C42,C44 = 100nF C29,C31,C33,C34 = 220nF  $C38,C39,C40 = 10\mu F 16V$  tantalum C41 = 220µF 40V C43 = 10nF  $C45 = 470 \mu F \, 16V$

Celsius. The wire jumpers being the 'components' with the lowest profile, they are first bent to shape, fitted and soldered. Next come the resistors, IC sockets, capacitors and so on, until all components are fitted except the integrated circuits, the pushbuttons and the LEDs. The step-down regulator IC is a tall component that has to be fitted flat on the board. Carefully insert its pins into the holes in the board, secure a small heatsink to it, and then solder the pins.

The connection to the 80C166 board is made via a 20-mm long pinheader at the solder side of the board. To make sure it fits correctly, insert the pinheader in the socket on the 80C166 board and secure the SMC board on top using fours PCB spacers with a height of 20 mm. Next, fix the pinheader by soldering its corner pins and two centrally located pins. Finally you remove the controller board again and solder the remaining pins on the pinheader.

Next, concentrate on the pushbuttons and the LEDs. The pushbuttons are fitted with their caps mounted on them, and the LEDs, with spacers. Now mount the front panel on to the SMC board using four 15-mm high PCB spacers. The layout and drilling template of the front panel will be

$L1 = 100\mu H 1A$ , max. dia. 15mm Semiconductors: D1-D8,D10 = LED, red D9 = LED, yellow D11,D12 = LED, green D13 = 1N4007 D14 = SB360 or SB550 (Schottky diode, 3A) D15 = 5V6 1W zener diode IC1-IC8 = PBL3717A or PBL3717/2N

(ST-Microelectronics) IC9-IC12 = GAL16V8 (order code 996524-1-a+b, 2 pcs) IC13,IC14 = 74HC123 IC15 = not used IC16,IC7,IC18 = ILQ74 IC19 = LT1076 CT

#### Miscellaneous:

Inductors:

JP1-JP8 = not used JP9-JP24 = jumper K1-K4 = 8-way PCB plug (Conrad Electronics o/n 741256) K5,K6,K7 = 10-way boxheader K8 = 26-way boxheader K9 = 4-way SIL header K10 = 2-way PCB terminal block K11 = 64-way pinheader S1-S11 = pushbutton, 1 make contact (ITT/Schadow PVA10AH2) S12 = 4-way DIP-switch Heatsink for voltage regulator PCB, order code 990044-1 Disk (source code files), order code 996031-1 On 80C166 board: H-EPROM = order code 996525-1 L-EPROM = order code 996525-2

given in next month's instalment. Check that no components are squashed between the board and the front panel! Once the LEDs and the pushbuttons are seated in their respective holes, their connecting terminals may be soldered.

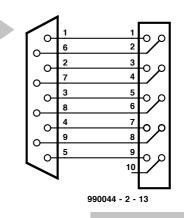

A cable adapter is needed to enable the SMC to communicate with the outside world. It consists of piece of flatcable, an IDC-style 10-way pinheader and a 9-way sub-D

also for flatcable mounting. Its 'schematic' is given in Figure 4.

Figure 4. A DIY cable adaptor.

The pinheader and the sub-D connector are aligned on the flatcable ends, clamped secure in a vise and then pressed on to the cable by slowly closing the vise. Do not forget the strain relief for the flatcable. On the pinheader, an arrow marks pin 1. Unused wires at either end of the cable may be cut off. A 26/25-way way cable adaptor for the inputs is made in the same way.

Having read this instalment you have roughly a month to build the electronics. Next time, we will again tackle practical matters like taking the SMC in use and operating it. Faultfinding will also be discussed, as well as the operation of the system software developed by the author.

(990044-2)

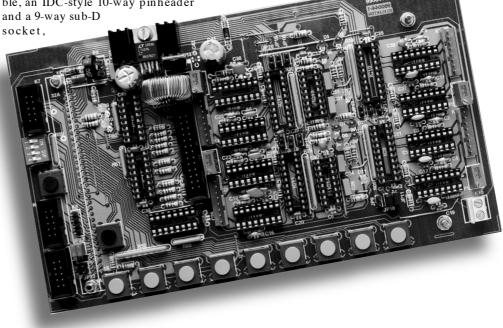

Figure 5. Completed prototype of the SMC board. Compare this carefully with your own work!

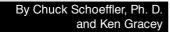

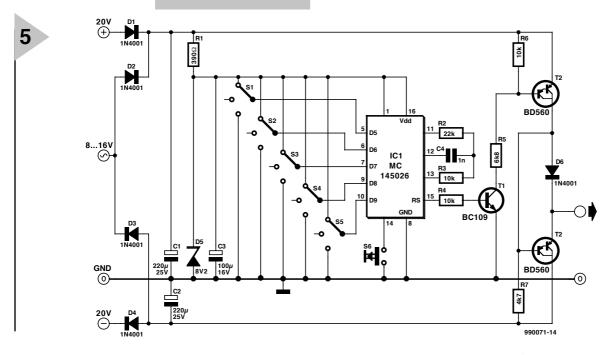

# BATTERY CHARGERS battery battery charge/refresh station (1)

## automatic charging at up to 3 A

This microprocessor controlled charger is suitable for Nickel-Cadmium (NiCd) as well as Nickel-Metal-Hydride (NiMH) batteries and battery packs. The charger is capable of topping up 1 to 10 cells using a charging current of up to 3 A. The end of the charging process is automatically detected, as is the adaptation of the charging current when

the full actually available capacity is reached. Thanks to a special pulsedriven charging process, discharging is not required before the battery is connected. In addition to the charging function, automatically followed by trickle charging, the station also features a charge/discharge cycle mode and a refresh mode for 'tired' or 'presumed dead' batteries.

> To get things straight from the onset: this charge/refresh station is not suitable for batteries consisting of 'small' cells like, for example, button cells, AAA cells or 9-V PP3-style batteries. The smallest cell size that may be used is the 'Mignon' style battery capable of 'fast' charging. In plain words, **do not**

use the station with batteries having a capacity of less than 700 mAh (at a discharge rate of C/3). By contrast, there is virtually no upper limit as to what the station van handle: sub-C, Baby, Mono and even larger cell sizes are okay as long as they are Nickel-Cadmium (NiCd) or Nickel-Metal-Hydride

Design by N. Bechtloff & G. Brenner (Conrad Technology Center, CTC)

### Features

- Selection between NiCd and NiMH, 1 up to 10 cells

- microprocessor control using intelligent charging algorithm

- Sense circuits for charging current, charging voltage, charge density and temperature

- Reliable protection against overcharging guarantees long battery life

- ◆ Charging current automatically adapted to cell capacity (from mignon-size > 700 mAh at C/3)

- Pre-discharging not required, battery is always charged to 100% of currently available capacity.

- Automatic switch-off at end of charging cycle

- Maximum charging current 3 A effective (8 A peak)

- Maximum discharging current: 1.5 A effective

- Three charging modes:

- 1. Charge (1 charge period for 100% charge)

- 2. Cycle (charge, discharge, charge)

- 3. Refresh (up to six cycles)

- ♦ With 4 or more cells, charging data are stored and re-used after mains interruption

- Storage and readout of charging and discharging capacity

- ♦ LC display readout

- Single-switch control for mode selection and data display

(NiMH) types. Because of its operating principle, this charge/refresh station is not suitable for lead-acid or Lithium-Ion (Li-Ion) cells or battery packs.

#### **PRINCIPLES** OF OPERATION

Fast charging of rechargeable batteries generally follows this simple rule: the higher the charging current, the shorter the charging time given a certain battery capacity (expressed in Ah or mAh). You, the user of the battery, of course want to be sure that the battery is charged in the shortest possible time, yet always be confident that the battery is reliably topped up and not damaged in any way by a fast charging process. On the contrary: the charging process should also guarantee optimum use of the battery capacity at the longest possible battery life. Furthermore, we would like the charging process to be as simple as possible, allowing the battery to be connected without having to discharge it first and independent of the charge still contained in the battery. In other words: connect the battery to the charger, switch on the charger and leave it to do its work. After a short time, the battery should be charged to its full capacity, 100 per cent, not more, not less.

Those of you who have ever had a the pleasure of studying the charging process of batteries with at least one Nickel electrode (NiCd or NiMH) will confirm that it is hard to satisfy all conditions mentioned above. On the one hand, charging at relatively high currents is good to make the most of the available capacity and at the same time combat the very annoying 'memory' effect of NiCd batteries. On the other hand, it requires the battery to be fully discharged, and precautions should be taken to make sure the battery is *never* over-charged with a high current. The first condition is normally satisfied by a simple discharging cycle. Two methods are often used together to meet the second condition:

#### 1. controlled charging time

The charging current is removed after the time calculated to fully top up the battery. This however requires certainty about the initial amount of charge in the battery, which is simple to ascertain by discharging it completely. Secondly, the battery capacity has to be known and set by the user. Apart from having to adjust the charger, the user often has a problem in that the battery at hand may not have the specified capacity any more. A further point to keep in mind is that the charging efficiency is by no means constant. Instead, it depends on many factors including the amount of current in relation to the battery capacity and the cell temperature. By itself, the 'controlled charge time' method is therefore too inaccurate to achieve full charging of he battery while ensuring that overcharging does not occur.

#### 2. controlled charge voltage

When the 'full charge' point is reached, charging current is increasingly not accepted by the battery but instead turned into heat. The resulting cell temperature increase causes the charging voltage to stop rising, then stabilise at a certain level, and finally even drop a little at the onset of overcharging. This drop may serve as an indication to initiate the switching off of the charging current. The advantage of this so-

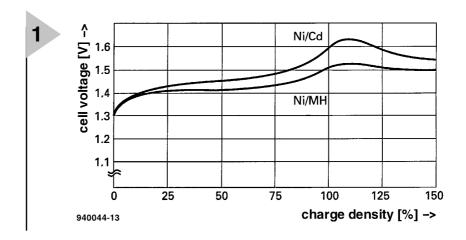

Figure 1. Typical charging voltage curves for NiCd and NiMH cells at 20 °C and 1CA (1-hour charge).

called delta-U ( $\Delta$ U) switch-off method is that it works independently of the initial battery state, and only evaluates the actually measured battery capacity. In practice, however, it is not easy to determine the exact switch-off instant with 100% certainty just by monitoring the charging voltage curve. Because the relevant voltage changes are often in the millivolts range, there is a real risk of the evaluating circuit responding to noise and disconnecting the battery too early. Moreover, the voltage curve as a function of charge condition may not be the same with all batteries, although these are of the same age and type. The main complicating factor is however the fact that the voltage drop is not always as clear as we would like it to be (or it does not occur at all). That is why designing a *reliable*  $\Delta U$  switchoff control is often likened to sorcery. Mainly because of the required 'intelligence', a microcontroller is then called for, besides clever design techniques and, most of all, lots of experience in this field.

THE DESIGN CONCEPT The battery charge/refresh station works without charge-time limiting and discharging before charging. This means that partly discharged batteries may also be topped up. To prevent partial charging from reducing the battery capacity as a result of the dreaded memory effect, charging takes place with very strong current pulses of up to 8 A. The effective charging current is adapted to the charging behaviour of the relevant battery by varying the pulsewidth. The maximum effective charging current is 3 A. The charging current setting is achieved depending on the voltage response. With a small battery, the terminal voltage rises faster than with a large one, so the charging current is reduced accordingly to match the smaller battery capacity (or battery condition, if applicable). Because the present circuit is a fast charger by any standard, the minimum charging current is a respectable 1 A. That is why the station should only be connected to batteries with a nominal capacity of not less than 700 mAh, and suitable for rapid charging. However, the 'overshoot' effect may still occur at the start of a charging session, in particular with small batteries (mignon cells) or batteries suffering from reduced capacity. Because of the high initial current, the battery temperature rises so quickly that the charging voltage drops a little after an initially 'steep' increase. In a normal delta-U charger, that would mean a premature end to the charging process. Not so with the present charger, because its internal microcontroller not only monitors the charge response, but also records the amount of energy already

transferred to the battery. Based on this information, the charger does not cut the charging current just like that. Instead, the battery is first discharged for about 9 seconds to 'sense' its internal resistance. If nothing untoward is detected, the charging continues at a reduced charging current. Likewise, the station ensures that the charging process is terminated in accordance with the actually loaded amount of energy. After passing the peak in the charging voltage (typical curves are shown in Figure 1), a small battery is quickly shut down. By contrast, larger batteries are given some more charging current because it takes longer for them to reach full charge (100% of nominal capacity).

A further problem arises when no clear voltage drop can be detected after the charging voltage peak. Depending on the battery make, size and condition, that is a reality to be taken into account. A regular delta-U control then fails to switch off the charging current, causing the battery to be overcharged at a high current, and turning the charger into an effective 'battery killer'. With the present charger, however, the switch-off routine is already activated when the charging voltage no longer rises. Even if the charging voltage stagnates, the charging process continues for a while (depending on the amount of energy already transferred) before the battery is disconnected. This switch-off routine - which adapts itself to the battery - allows the maximum capacity to be reached with any battery, and at the same time prevent overcharging under all conditions.

Starting at 1.8 A, the microcontroller also adapts the discharging current to the response of the battery at hand. By increasing the pauses in between discharging pulses, the effective discharging current is automatically reduced from about 1.5 A down to 0.5 A as the battery capacity drops also.

#### PRACTICAL REALISATION

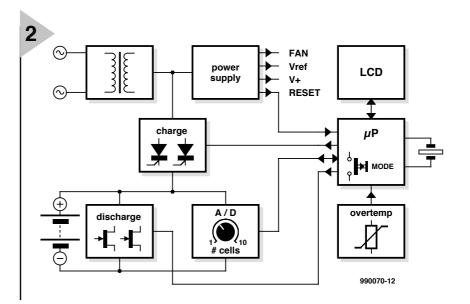

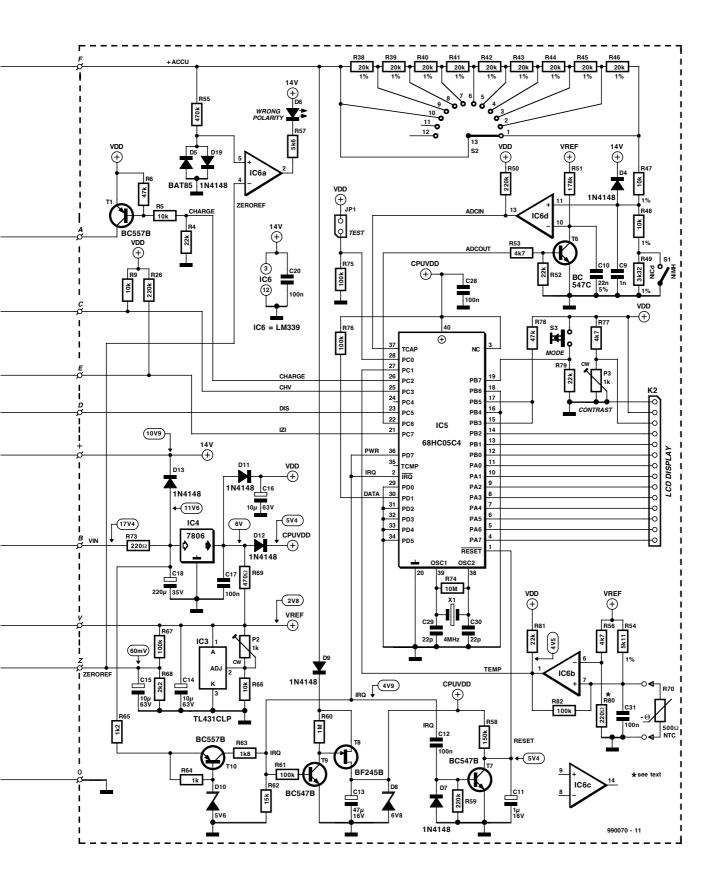

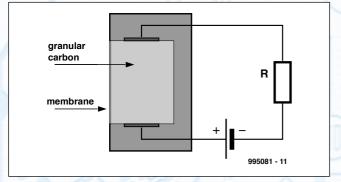

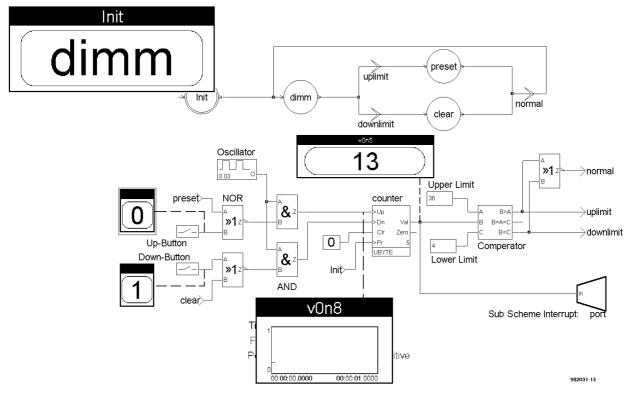

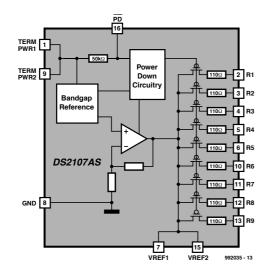

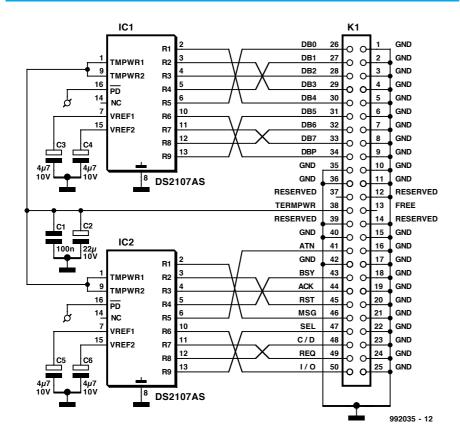

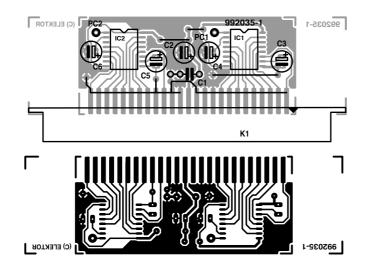

The block diagram shown in Figure 2 provides an overview of the relatively complex circuit. The actual circuit diagram is given in Figure 3. The charging current for the batteries is supplied directly by the secondary winding on the mains transformer. The amount of current is determined by the microcontroller in combination with a halfphase control based on thyristors. A MOSFET is used to discharge batteries in 'cycle' and 'alive' (refresh) mode. Using an A-D converter the microcontroller continuously monitors the charging current as well as the charging voltage. In addition, a temperature signal is processed, where either the battery temperature or the charger temperature may be measured. Manual control is by means of a rotary switch for the number of cells and a mode switch for the menu-driven selection of the charger mode. Results and selections appear on an LC display. The NiCd/NiMH cell type selection switch is not shown in the block diagram.

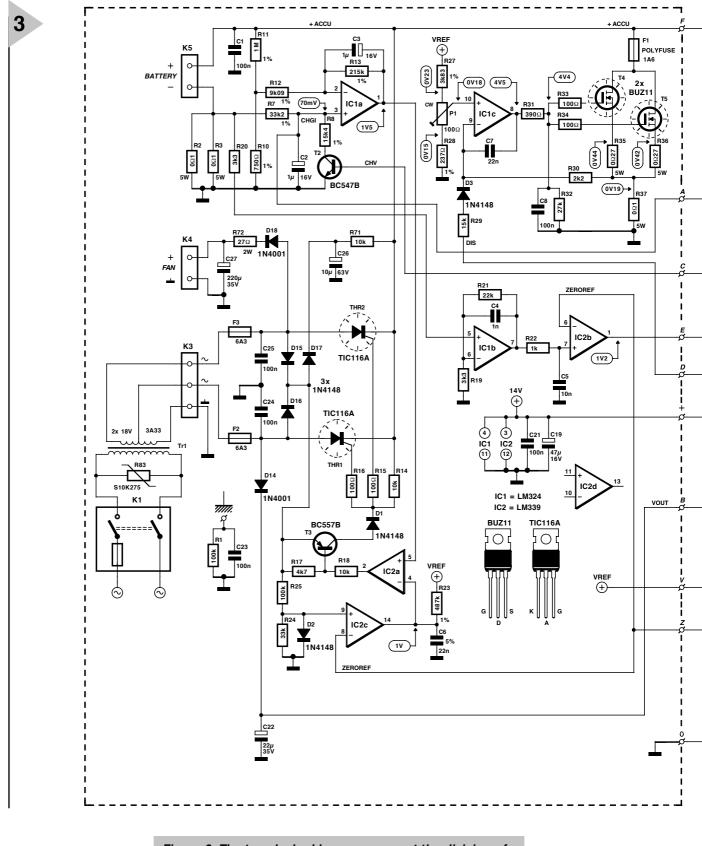

You may not be able to spot all of the above functions at first blush in the circuit diagram — finding it all takes a bit of study. The dashed lines indicate the division of the parts between two sub-boards. The left-hand section goes to the smaller board, the right-hand section, to the large board.

#### Charging circuit

The centre tap of the mains transformer being connected to ground, thyristors THR1 and THR2 act as a fullwave rectifier under microprocessor control. Because the charging current is adjusted by way of phase angle control, very high pulse currents of up to 8 A may be applied to the battery or cell. The battery charging current is measured by means of the voltage drop developed across sense resistors R2 and R3. After averaging by R7-C2, the measured voltage is amplified by IC1a and then compared with a mainssynhronous sawtooth voltage generated by IC2c. The sawtooth level depends on the reference voltage VREF and may therefore be adjusted using P2 (at the reference source, IC3). As soon as the voltage derived from the charging current and available at the output of IC1a exceeds the sawtooth voltage, T3 is switched off via IC2a, preventing the thyristor from being triggered. The phase angle control operates by itself with just these three opamps, with the microcontroller switching it all on and off via transistor T1. When the controller drives T1 via the CHARGE line, the transistor will conduct and pull the voltage on C2 to about 5 V. This voltage is interpreted as a very high charging current by the three opamps. This subcircuit responds by not activating the thyristors, which remain off. Once the controller reenables the triggering circuit, the voltage on C2 (5 V) drops slowly so that the current control starts off smoothly from zero. Also, the controller is able to switch between 100% charging current (3 A effective) and 33% (1 A effective) via the CHV line. When the controller switches on T2 via the CHV line, R8 is connected into circuit and R7 forms a voltage divider.

#### **Discharging circuit**

Batteries are discharged by passing their current through MOSFETs T4 and T5. This, too, is an autonomous subcircuit which is simply switched on and off by the microcontroller. Resistors R35 and R36 ensure equal distribution of the discharging current between the two FETs. The full discharging current flowing through R37, this resistor supplies the voltage that enables opamp IC1 to monitor the amount of current. The opamp compares the measured voltage with a reference level set with preset P1. Here, too, the controller is able to switch it all on and off by means of a voltage level. When the DIS line is pulled to 5 V, this high voltage reaches the opamp's measurement input via R29 and D3. This level is taken to mean a high discharging current, and causes the opamp to switch off the discharging circuit. As in the charging control, the switching off is gradual thanks to timing element C7 in the opamp feedback circuit. For security's sake, the discharging circuit includes a Polyfuse, which is a kind of super-PTC. In the inactive ('cold') state, this component represents a very small resistance in the region of a few tenths of an ohm. If the nominal current is exceeded, the internal resistance of the Polyfuse rises as a result of the higher temperature. When the current drops again, the fuse returns to its low-resistance state once it has cooled down. The advantage: a 'self-healing' ability; the disadvantage: much slower response than a conventional wire fuse.

#### A-D converter

This is built in quasi-discrete fashion with opamp IC6d acting as a simple single-slope converter. Initially, T6 is driven hard by the microcontroller so that the voltage across C10 is (almost) zero. When a measurement is required, the controller first switches off T6, allowing C10 to be charged via R51 by a stable reference voltage. As soon as this comparison voltage is equal to the (scaled-down) battery voltage applied to the other opamp input, the output of IC6d toggles. The time between the enabling of the capacitor charging until the toggling of IC6d is measured by the microcontroller, and the resulting value enables it to compute the measured current. The absolute accuracy of the measurement is not terribly important because we're looking at capturing a measurement value during a period of several hours, rather than an absolute value over a longer period.

To enable NiMH batteries or cells to be charged, switch S1 modifies the composition of voltage divider at the converter input. The result is that the A-D converter is made slightly more sensitive to enable it to reliably follow the smaller voltage changes in the charging voltage curve (as compared with NiCd, see the curves in Figure 1).

The charging voltage measurement always takes place at the same instant after a charging current pulse, that is,

Figure 2. Block diagram of the battery charge/refresh station. The charging current flows directly from the transformer secondary inti the battery.

at an almost 'current-less' point in time. In this way, the (considerable) voltage loss caused by contact resistance and wires is avoided, and the actual battery terminal voltage is reliably measured. The measurement occurs just after the zero crossing, with the controller receiving a signal from IC2b telling it if the current is large or very small. This is achieved by IC2b weighing the current measurement signal (amplified by IC1b) against a very small direct voltage. In the circuit diagram, this is labelled 'ZEROREF'.

#### Battery/cell polarity

The battery or cell polarity is checked by means of IC6a comparing with ZEROREF. When the battery is connected the wrong way around, LED D6 lights.

#### **Temperature guard**

This function consists of a simple circuit around IC6b monitoring the voltage produced by a measurement bridge based on NTC R70. If the measured temperature exceeds the threshold set by bridge resistor R80, the opamp output drops low and causes the microcontroller to interrupt the relevant process (charging or discharging). Once the temperature has dropped below the threshold level, the process is continued. If, however, the temperature guard is activated three times in succession, the process is terminated.

#### **Power supply**

This is relatively complex sub-circuit. D18 and R72 supply the ventilator supply voltage (depending on the type used).

- D15 and D16 generate an auxiliary voltage to ensure proper triggering of the thyristors. When no battery is connected, D17 and R71 apply a high direct voltage across the battery connector K5, to enable the microcontroller to detect, via the A-D converter, whether or not a battery is connected.

- D14 carries the current for the voltage regulators, to wit

- IC4 followed by diodes D11 and D12 for the two 5-V supply lines CPU-VDD (microcontroller) and VDD (remaining 5-V electronics).

- Via R69, IC3 is connected to the 6 V at the output of IC4, and so generates the reference voltage VREF (typ. 2.8 V) adjusted with P2.

- ZEROREF (typ. 60 mV) is derived from VREF via R67 and R68. Its function is to aid the zero-crossing detection of the mains transformer voltage. Note however that ZEROREF always has to exceed the maximum offset voltage of the opamps used in the circuit.

#### MPU backup voltage

The backup supply voltage for the microcontroller to work from during a mains outage (or when the station is briefly switched off) comes from the external battery rather than from an internal power source. Of course, this will only work as long as the battery voltage is high enough. To ensure the guaranteed switchover to emergency supply by the external battery, the voltage at the input of voltage regulator IC4 is sensed via T10 and D10. As long as this voltage is higher than 6 V, tran-

Figure 3. The two dashed boxes represent the division of the circuit in two sub-boards.

sistor T9 conducts, while T8 is held switched off so that it has no effect on the controller's supply voltage (CPU-VDD). However, as soon the level drops below 6 V, FET T8 starts to conduct, thereby passing the battery voltage to the microcontroller. In this setup, D8 ensures that a maximum level of 6.8 V can not be exceeded. As long as the battery powers the controller, all values and settings remain safely stored. In this way, a charging or discharging process continues where it left off after the mains voltage disappeared, as if nothing had happened.

The return of the mains voltage is

detected via C12 and R7. If the voltage rises again, T7 is shortly opened by C12, causing C11 to discharge across the transistor and so generate a reset for the microcontroller. Next, the reset line returns to logic high, and the controller starts from a defined state. Via its IRQ pin, the controller is informed

that a battery voltage is available but no supply voltage.

The LCD contrast is adjusted with preset P3. If you look closely at the circuit you may note that some opamp outputs are connected directly to microcontroller input lines, despite the 14-V opamp supply voltage. The microcontroller however can not normally handle more than its supply voltage (max. 5.4 V) at its inputs. That is why type LM339 opamps are used — these are marked by open-collector outputs which are tied to VDD by pull-up resistors. Controller port lines PB3 through PB7 determine the internal settings (the scale factors) stored in the micro-controller.

(990070-1)

Continued next month

27

# **BASIC St a mp** programming course (2)

## Part 2: building the BOE-Bot

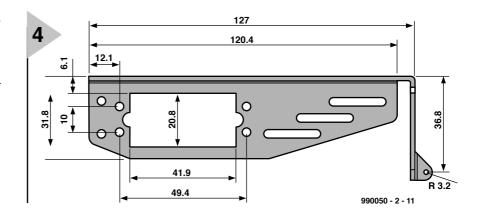

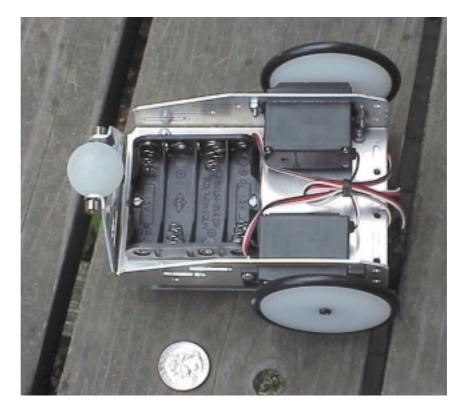

#### ASSEMBLING A ROBOT CHASSIS

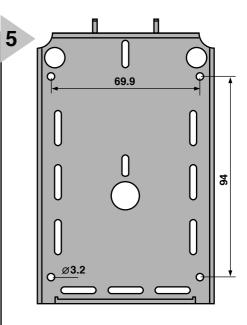

The robot chassis needs to accommodate two servos for drivetrain, a battery pack, and have a prototype development area (the Board of Education). We're using a custom aluminum chassis that you can purchase (from Parallax Stamp dealers, *Ed.*), but we're providing dimensioned drawings so you can build your own from aluminum or plastic. In fact, you can download dimensioned Autocad \*.dwg and \*.dxf drawings for your own customization. These drawings may be edited to your specific needs and are available from *http://www.stampsinclass.com* **Figures 4 and 5** show the top and side dimensions of the BOE-Bot chassis.

#### ASSEMBLY OF THE BOE-BOT

Construction of the BOE-BOT platform consists of five parts:

- 1. Modifying the Futaba servos for full rotation.

- 2. Calibrating the servo.

- 3. Mounting the servos on the robotics platform and attaching the wheels.

- 4. Attaching the tail wheel and battery holder.

Robot vehicle with Elektor Electronics version of BOE installed on top.

5. Mounting the BOE and connecting the servos to the controller.

#### Modifying the Futaba servo for continuous rotation

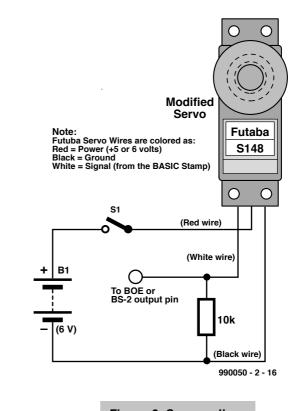

The BOE-Bot uses two modified Futaba S-148 servos. The S-148 provides low cost, easy-to-modify gear motors that let the platform move around. The servos are easily modified to let them rotate 360 degrees. When you purchase most hobby servos they are usually set up to move about 90 total. The servos respond to a pulse width modulation signal (PWM) that you send to it using the BASIC Stamp. This is accomplished using the PULSOUT command.

Modifying the Futaba S-148 servos takes only a few minutes (or less if

you've done them before), is painless, only requires a Phillips screwdriver, a file or sandpaper, and a little careful disassembly. This modification can be reversed at a later date to make the servo operate like it was intended if you save the small plastic drive plate (we're going to remove it) or purchase the replacement gear set at a hobby shop.

The Futaba servos have a round control horn attached to the main output shaft and secured in place with a Phillips screw.

Turn the servo horn with your fingers until it stops. Turn it clockwise and counter-clockwise till the shaft stops to see how the servo will operate. We need to

change it so that the control horn will rotate all the way around and not stop. When you're done playing, take the screw out and wiggle the control horn off the main output gear shaft. The gear shaft has splines on it, so you will have to apply upward pressure and then wiggle it off. Look at the bottom of the Futaba servo and find the four Phillips head screws on the bottom of the case because you will need to remove those in addition to the one Phillips screw that was holding the control horn on the main output gear.

Carefully remove the four Phillips screws from the bottom of the servo. The bottom plate of the servo will come off at this point so look at the control circuitry. You won't need to do any soldering unless you break a wire off or something else.

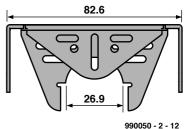

Hold your finger on the output gear shaft and press down (the one that the control horn was on) and carefully pry and wiggle the top of the servo case up and remove it. Work slowly so the gears all stay in place on their shafts. **Figure 6** shows a drawing of the servo case and gear names.

The final gear is the one you are going to modify. It's also the one you held down with your finger. You'll need to remove the 3<sup>rd</sup> gear in order to

Figure 4. Chassis dimensioned (mm), viewpoint from side (no scale).

access the final gear. Looking at the top of the final gear you'll see a plastic stop tab that

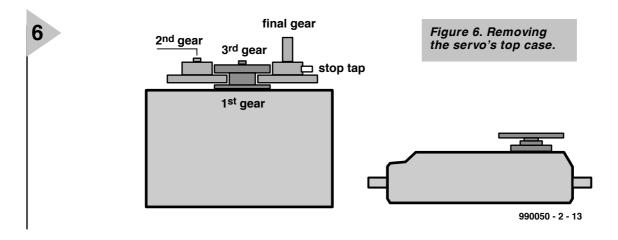

we need to file off to make the servo turn completely around when we issue commands. File, sand or cut the stop tab on the main output gear until it is gone (don't sand into the gear teeth). The tab is shown in **Figure 7**.

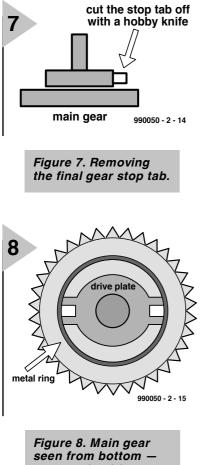

Turn the final gear over and look at the bottom. You will see a metal ring pressed into the plastic, and you need to pry that out with a small screwdriver, your fingernail or a paper clip. Remove the potentiometer drive plate. You might want to save this plastic part if you ever want to convert the servo back to its normal mode of operation. Insert the metal ring back into the main gear. **Figure 8** shows the bottom of the main gear.

#### Calibrating the servos

Before assembling the servo back together you should check the calibration of the servo and make it stop moving when the BASIC Stamp sends a PULSOUT command of 750. At this point get out your BASIC Stamp or BOE and enter the appropriate program listed in **Listing 1**. You will need to connect your BASIC Stamp to an IBM PC, enter the source code in the editor and download. The BASIC Stamp software editor is available for free download from Figure 5. Chassis dimensioned (mm), viewpoint from top and rear (no scale).

10/99

9

seen from bottom – remove the drive plate.

#### http://www.parallaxinc.com

The servo calibration schematic is shown in **Figure 9**.

If you are not using the BOE for the servo calibration you must use a separate 5 or 6 VDC source of power to operate the servos. If you do not you're liable to burn out the regulator on the BASIC Stamp. The BOE uses a lowdropout regulator and it can drive the servos from its output. When using a 6-volt power supply connect the servo power and ground directly to the battery terminals. If you connect the servos directly to voltages higher than 5 or 6 VDC you may notice that they don't operate correctly under program control and you might damage them. If you damage the servos, it's usually just the servo control board that has something wrong with it and you can remove that and still use the servo as a high torque gear motor. They are still useable for robotics but you won't be able to use the PULSOUT command to make them turn clockwise and counter-clockwise anymore.

Load your calibration program into the BASIC Stamp and see if the servo gears are turning. If they are then you will need to adjust the potentiometer (pot) shaft underneath the main gear until everything stops moving. Once you have stopped all motion then you

Figure 9. Servo calibration schematic.

### Listing 1. Servo calibration code

'Program for calibrating servo to its center using BS-2 'C. Schoeffler, University of Idaho

center: 'establishes a name for this calibration routine pulsout 15, 750 'sends a pulse of 1.5 milliseconds to the servo pause 20 'delay between pulses is 10 ms to 20 ms goto center

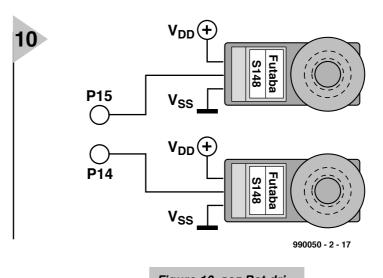

Figure 10. BOE-Bot drivetrain schematic.

can unplug the servo and put it back together.

Check the servo again before putting all the screws back in to see if the servo is indeed stopped when you sent it the test program. The servo case parts should go back together smoothly and when put together you should just barely be able to see where the case part joins together.

### Mounting the servos on the robotics platform

When you're done modifying and testing the servos you can install them on your robot chassis and connect them to the BASIC Stamp. Figure 10 shows the completed servo schematic interfacing to the BASIC Stamp. Futaba wires are easy to identify. Red is positive 5 or 6 VDC, black is the negative wire, and the white wire is the signal wire. The BOE-Bot is configured to just plug and unplug the battery power supply so you don't need a switch. After you have installed the servos in the BOE-BOT base, attach the wheels and secure them with a Phillips screw that is normally used to secure the control horn on the servo.

### Attaching the tail wheel and battery holder

If you are using the chassis design we featured, mount the tail wheel using a steel wire or cotter pin. We used a 25.4 mm polyethylene ball for the tail wheel. Drill a hole through the tail wheel. **Figure 10** shows how the battery holder is mounted under the BOE-Bot base. Mount the battery holder and solder some wires to the terminals so you can bring the 6 VDC up to the top of the BOE-BOT. If you aren't using this metal chassis then consider doublesided tape or Velcro.

#### Mounting the Board of Education

Mount the BOE on the robot chassis using machine screws and standoffs. Using aluminum 1/2-inch (12 mm) standoffs with machine screws works well. Again, you could even use double-sided tape, but be sure that the BOE doesn't short-circuit with the robot chassis.

#### CONCLUSION

Now that you've got a robotic platform based on the BASIC Stamp, it's time to prepare for learning simple I/O control.

Next month we'll start with BASIC programming and proceed to implement a sensor.

(990050-2)

Figure 12. Contents of the robot kit supplied by Parallax Stamp dealers. The metal chassis is to be made available as a separate item.

## Internet

<u>http://www.parallaxinc.com</u> – BASIC Stamp Manual Version 1.9, BASIC Stamp DOS and Windows Editor, program examples. International distribution sources.

<u>http://www.stampsinclass.com</u> —BoE documentation, Robotics curriculum, BoE-Bot \*.dxf and \*.dwg drawing formats, discussion group for educational uses of BASIC Stamp.

<u>chucks@turbonet.com</u> — creator of the BoE-Bot and author of this series. Technical assistance.

<u>kgracey@parallaxinc.com</u> — co-author of this article. Technical assistance and questions about the educational program.

http://www.milinst.demon.co.uk – UK distributor of Parallax BASIC Stamp.

# controller area network (CAN)

# *intelligent, decentralized data communications Part 2*

The first part of this article described the history, standardization, and the basic setup of the Controller Area Network (CAN) developed by the **Robert Bosch** Company in Germany. In this second part, the attention is

focused on the data transmission protocol that determines the capabilities and reliability of this automotive digital data system.

#### INTRODUCTION

As already stated in Part 1, CAN is a serial asynchronous communication protocol that connects sensors and actuators of electronic control stations in cars. Among its many functions is a digital data link. It is an asynchronous system because each station (also called 'node') synchronizes to messages of other stations on the leading edge of the first message bit and on subsequent leading edges throughout the rest of the message. The ability of any station to synchronize to another station is determined by the maximum differences in oscillator frequencies. Other factors are, for instance, bit duration,

message duration and composition, and handshaking.

The most important parts of the network are the *physical layer*, comprising the topology of the network and the link to the bus, and the *data link layer*, which lays down how the data transmission medium is accessed, how a message is constructed (address, data, control and protection against errors) and how the data transmission protocol is structured.

#### IN PRACTICE

The exchange of messages between two network stations may take place in two basically different ways: station-

By B vom Berg & P Groppe

oriented and messageoriented.

### Station-oriented exchange

In this mode, the sender addresses the receiver simply by means of the receiver address, for instance: 'Station 25 is sending a message to station 37'. In this way, a virtual link between the sender and receiver is established via the bus.

The transmitted packet of data therefore contains the address of the receiver station and that of the sending station. All other stations connected to the bus ignore the packet since it is not addressed to them.

The receiving station evaluates the message and normally acknowledges its receipt. In case of an error during the data transmission (no acknowledgment from the receiver), the sender repeats the message.

#### Message-oriented exchange

In this mode, the sender adds to the message an unambiguous identifier and sends the message and identifier via the bus, for instance: 'Station A is sending a voltage measurement with identifier 978'. In this mode, the addresses of the sender and receiver are not included.

Such a message is clearly intended for several receivers connected to the bus under the motto: 'Take from the bus what you need' (broadcast principle). The various receive stations must determine, on the basis of their programming, whether the message is relevant to them or not.

#### Flow of communications

The flow of communications between the individual stations connected to the CAN bus takes place in the form of a broadcast of event-controlled, prioritized (through-numbered) messages or frames (communication messages).

#### Dominant and recessive bus/bit states

The actual data transmission via the data transmission medium does not take place, as usual, in the form of '1s' and '0s', but by dominant and recessive bits. Recessive typifies a bus state that may be overwritten by a dominant bus state. So, when a station connected

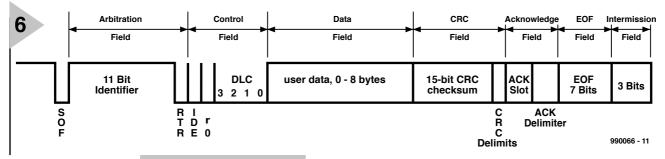

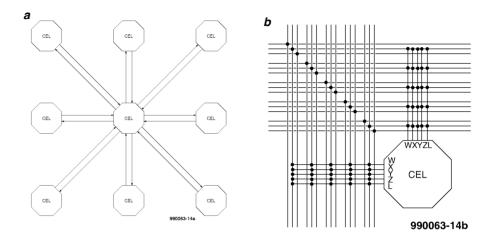

Figure 6. Composition of a data frame (standard frame format – Specification CAN 20A).

to the bus sends a recessive bit and another station at the same time sends a

dominant bit, the dominant bit takes priority over the recessive bit, that is, the dominant state is accepted by the entire bus. The assignment of logic states to the bus is generally so that a logic 0 repretransmitteds a dominant state, and a logic 1, a recessive state.

These arrangements constitute one of the foundations of the CAN specification and will be elaborated on later.

#### Data packets

The network uses four kinds of data packets, normally called frames, to exchange data on the bus: data frame; remote frame; error frame; and overload frame.

#### Data frame

The data frame is used by the stations to send their data in line with their programming. The composition of a typical data frame, which consists of a single field, is shown in **Figure 6**. This is a standard frame format according to Specification CAN 20A. The meaning of the various terms in the figure is as follows.

**SOF**. This is the start-of-frame bit, which is always dominant (0). All stations connected to the bus synchronize their internal receive stages to the trailing edge of this bit.

**Arbitration field**. This field, which is 12 bits long, contains the data for accessing the bus.

11-bit identifier. This section contains the identifier (ID) of the transmitted frames. The 11 bits allow up to  $2^{11}$ = 2048 different identifiers to be constructed, of which only 2032 are freely available: the remaining 16 are reserved for certain special functions. This means that a single controller area network can process 2032 different messages (measurement values, switch positions, light functions, and so on). Although this seems a fairly large number, in many applications it is not enough. Therefore, an Extended Frame Format with 29 identifier bits (CAN 20B) has been formulated. In this,  $2^{29}$ = 536 870 912 frames can be handled.

**RTR** (Remote Transmission Request) bit. This bit, which is always dominant (0), enables a station to address and send messages to another specified station. This is of great value when certain data are urgently needed to be processed (more about this later).

**Control field**. This 6-bit long section contains the information as to how a data frame is composed.

**IDE** (Identifier Extension) bit. This bit indicates whether a standard-format frame with an 11-bit identifier (IDE = dominant = 0), or an extended-format frame with a 29-bit identifier (IDE = recessive = 1) is being transmitted.

**r0** (Reserve bit 0). This dominant bit is transmitted as a spare bit for future expansion specifications.

**DLC** (Data Length Code). This 4-bit long section indicates how many data bytes are being transmitted successively in a data field. The CAN Specification allows data field lengths of 0–8 bytes, that is, a single data frame may transmit not more than eight data bytes.

**Data field**. This 8-bit long section contains the data bytes (0–8) to be transmitted.

CRC field. The 16-bit long CRC field contains additional information for protecting the data being transmitted against interference. For this purpose, the sender station constructs, according to specific rules, a 15-bit CRC check sum from the preceding data and sends this, together with the frames. The receiver station calculates a similar check sum according to the same rules and compares this with the transmitted check sum. If the two sums are identical (the normal case), data transmission can commence. If the sums are not identical, an error handling procedure is initiated. The CRC field is limited by a CRC delimiter bit which is always transmitted recessively.

Acknowledge field. The 2-bit long acknowledge field serves to transmission acknowledgments of correctly received data frames.

ACK slot. This 1-bit long section is transmitted as a recessive bit and may, therefore, be overwritten by a dominant bit transmitted by another station connected to the bus. It allows receive stations to send an acknowledgement of a correctly received data frame. The acknowledgment bit is dominant and is transmitted by each and every relevant station upon error-free reception of messages. Since it is dominant, it overwrites the recessive bit sent by the transmitting station. Thus, if the transmitting station receives a dominant bit during the ACK slot window, instead of its own transmitted recessive bit, it 'knows' that at least one station has received the message.

The ACK slot window is restricted by a recessively transmitted ACK Delimiter bit.

**EOF** (End Of Frame) **field**. This field consists of seven recessive bits and serves to terminate the data frame.

Before the next data frame can be transmitted, the receive stations need a short intermission to enable them to process, or at least store, the received data. The intermission is arranged by a recessive 3-bit intermission field ending the data frame.

Owing to lack of space, the Extended Frame Format cannot be discussed; its principles are, however, the same as those discussed for the Standard Frame Format.

#### AVOIDANCE OF CONFLICT

Since all stations connected to the Controller Area Network bus, two questions arise:

- \* What happens when several stations want to send a message at the same time?

- \* How is it decided which station can start and which stations must wait their turn?

Clearly, these matters may give rise to conflicts and to avoid those there is a special bus access procedure which must be obeyed by all stations when they want to send a message. In this, an important role is played by the dominant and recessive bits in the Arbitration Field.

Basically, each sender 'hears' its own transmission to the bus: it sends a bit, receives it back and compares the two. If they are identical, transmission of the message is allowed. If, however, the two bits are dissimilar, there is a problem. As explained earlier, a recessive bit (1) can be overwritten by a dominant bit (0).

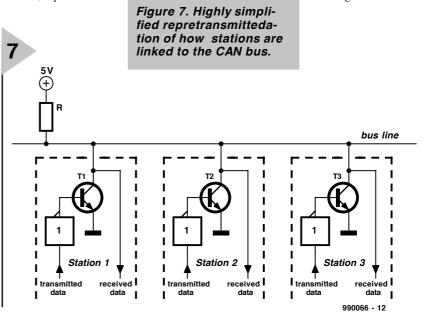

Figure 7 gives a highly simplified repretransmittedation of some linking stages of the bus. Basically, these are open-collector output stages that are arranged as wired-AND gates. With reference to station 1, a recessively transmitted bit (1) ensures that transistor  $T_1$  remains cut off. This means that the recessive level is pretransmitted at the bus. After this bit has been transmitted, station 1 reads the bus status and recognizes the bit it has transmitted. If then a dominant bit (0) is transmitted,  $T_1$  comes on ing back, station 1 notices that its recessive bit has been overwritten, which means that it has lost access to the bus to at least one other station. Station 1 then assumes the receive mode (but tries to send its message at a later time again). Stations 2 and 3 continue as before.

At time j, station 3 sends a recessive bit that is promptly overwritten by the dominant level transmitted by station 2. This is noticed by station 3, which thereupon also assumes the receive mode (and, like station 1, tries to send its message at a later time again). Station 2 is the 'victor' and can send its

message without fur-

and switches the bus line to earth. The bus line is then dominant (0). Again, station 1 reads back the bit it transmitted.

Considering the three stages, if one of them sends a dominant bit, the busline becomes dominant (0) and the other stations read this level.

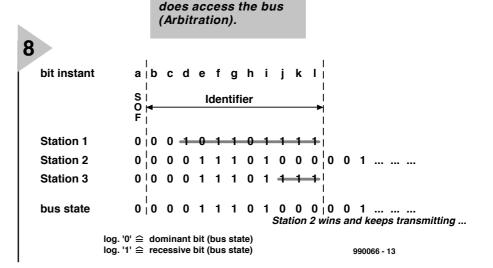

An example will show how the bus access procedure takes place. Assume that the stations in Figure 2 are all ready to transmit their data frames with three different identifiers:

Station 1: identifier 367 Station 2: identifier 232 Station 3: identifier 239.

All three start with the arbitration (bus access) phase by transmitting a SOF bit (see Figure 8). This is a dominant bit, and each station reads back its own (correct) bit from the bus. Then, the identifiers are transmitted. Up to time b, all stations send a dominant bit and all is well. At time c, there is still no problem. At time d, station 1 sends a recessive bit, but stations 2 and 3 continue with a dominant bit. When read-

ther hindrance to the bus.

A closer look at the identifiers shows that it is the station with the smallest identifier that gains access to the bus first: it has the highest send priority. In other words: the identifier also automatically contains the message priority. A message with identifier 0 will always be the first to be received by the stations connected to the bus, since it has the highest priority. A message with identifier 2032 has a long wait since it has the lowest priority.

#### **Remote Request Frame**

The remote request frame is an important one in the network. Assume that station D connected to the CAN bus transmits three temperature measurement data every five minutes with Identifier 598. This means that the data field contains three bytes. These messages are received and processed by other stations.

However, station G urgently needs the actual temperature measurement and cannot in any circumstances wait for five minutes. It has the facility, therefore, to request the measurements directly from station D, that is, it can bypass the data transmission cycle. To do so, it sends a so-called Remote Request Frame, which is composed similar to a Data Frame (Figure 6), but with some small differences:

- The identifier of the station to whom the request is transmitted (here, 598) is entered in the identifier field.

- In the DLC field, the number of useful bytes contained in the requested message (here, 3) is entered.

- The Remote Transmission Request (RTR) which is dominant (0) in the Data Frame is made and transmitted recessively (1). This is a typical identification of a station that requests data direct from another specific station.

- There is no data field in the Remote Request Frame: the DLC field is followed immediately by the CRC field. In other words, the Remote Request Frame is composed like a Data Frame but with 0 bytes of data.

The transmitted Remote Request Frame functions as follows. All stations connected to the bus receive the frame and recognize by the set RTR bits that a station has requested specific data from another station. Station D recognizes that the identifier in the Remote Request Frame is the same as its own identifier and immediately sends its response in the form of a Data Frame with the requested data.

#### ERROR DETECTION AND REMEDIES

One of the most striking properties of the Controller Area Network concept is its uncanny capability of detecting a multitude of errors during the data transmission and react to them accordingly. It has a Hamming Distance (also called signal distance) of 6. The signal distance between two binary words of the same length is the number of the corresponding bit positions in which the two words have different bit values. For instance, the signal distance between 11011010 and 10000110 is four, since the 3rd, 4th, 5th, and 7th bits (counting from the left) are different.

In a CAN data are transmitted permanently at a transmission rate of 500 kbit/s. Every 0.7 s a one-bit error is caused by external interference. The network operates eight hours a day, 365 days a year. The built-in protection against errors in a CAN guarantees that in 1000 years of operation only one error will not be detected. Errors can and do, of course, occur, but once they are known, they can be remedied. Only unknown errors can cause false measurements to be processed.

#### DETECTION OF TRANSMISSION ERRORS

In a CAN, several means are used simultaneously to detect errors.

#### Bit error detection

Each and every station receives its own transmission back. If, therefore, after the arbitration phase, a station is the only one that sends a message to the bus and it receives back a different bus status than it transmitted, it is clear that an error has occurred on the bus. The station then shifts its operation to an error treatment routine (see later).

#### Stuffbit error detection

The CAN specification states clearly that when in a data frame more than five bits of the same value are transmitted in sequence (for

instance, seven times a 0 in a field), each and

#### Acknowledgment error detection

In the description of the frame format (see Figure 6) mention was made of the ACK slot bit, which is transmitted by a station as a recessive bit. All stations that have received the previous frame correctly overwrite this bit with a dominant bit. The sender detects this and 'knows' that at least one station has received its data correctly.

If the sender detects that its ACK slot bit is not overwritten, it 'knows' that not one station has received its message correctly. It then shifts its operation to an error treatment routine (see later).

#### Format error detection

In this, use is made of the fact that the network format has several fields that must always have a fixed content: the

> CRC delimiter, the Acknowledgment Delimiter, and the EOF

Figure 8. Diagram-

matic repretransmitte-

dation of how a station

every group of five bits is followed by a complementary bit (here, a 1, of course). This introduced bit, which, of course, contains no information whatever, is called a stuffbit. At the receive end, these bits are removed from the data stream, so that only the original message is processed.

The stuffbits may readily be used for error checking. If the receiver detects more than five sequential bits of the same value in a frame (but not in the EOF field), it is clear that this cannot be right and that an error in the data transmission has occurred which has inverted one or more bits. The receiver then shifts its operation to an error treatment routine (see later).

#### CRC error detection

This consists, as already described, of an evaluation of the CRC check sum at the receiver. When the received and calculated check sums are dissimilar, the receiver shifts its operation to an error treatment routine (see later). field are always composed of recessive bits. If a dominant bit is detected, this can have been caused only by a data transmission error. Here also, operation is shifted to an error treatment routine (see later).

#### ERROR TREATMENT

The error treatment routine in response to a data transmission error takes two forms.

In the first place, frames in which an error has been detected are immediately rejected by the relevant station and not processed. Secondly, if any station within the system detects an error, it immediately transmits an error frame that consists of six dominant bits (= error flag) and an error delimiter of eight recessive bits. The result of this is that all recessive bits on the bus are overwritten, so that six dominant bits remain. This is, however, a contravention of the stuffbit rule that not more than five sequential bits may have the same value.

All other stations connected to the bus detect this error condition and treat the frame just transmitted as faulty, reject it and also send out an error frame. In other words, a station that detects an error purposely mutilates the entire transmitted frame so that all other stations connected to the bus receive a faulty frame. This means that an error local to a station is immediately communicated to all other stations. The motto of the network is that all stations receive correct data that can be processed as required, or all stations receive faulty data that are rejected. The original sender detects, of course, that the frame it transmitted is mutilated, adjust its message and resends it after a short while.

#### ERROR INSIDE A STATION

What happens when a station itself becomes defect, is damaged, operates with an inaccurate transmission rate, or is the only station that gets interference? Such a station would permanently send out error frame and so disable the entire network. The CAN concept has adequate protection against such an occurrence, but space prohibits describing this in this article.

#### Table 3.

|                                       | 0411204      | 0/11/200        |  |

|---------------------------------------|--------------|-----------------|--|

|                                       |              |                 |  |

| Maximum number of identifiers         | 211          | 2 <sup>29</sup> |  |

| Number of stations (nodes)            | 32           | 32              |  |

| Data transfer rate                    | 5–125 kbit/s | 5–1000 kbit/s   |  |

| Number of permissible bytes per frame | 0–8          | 0–8             |  |

| Maximum length of a frame             | 117 bits     | 13 bits         |  |

| Maximum bus expansion                 | see text     | see text        |  |

|                                       |              |                 |  |

CAN 20A

CAN 20B

Table 3. Comparison of CAN 20A (standard frame format) and CAN 20B (extended frame format).

#### SUMMARY

The specifications of the two CAN versions, CAN 20A (standard frame format) and CAN 20B (extended frame format) are compared in Table 3.

Although the Controller Area Network is a powerful and highly reliable system for data communications, the reader and prospective user may well ask how it can be turned into a practical application. There are dominant and recessive bits, an 11-bit identifier, a 15-bit CRC check sum, a 1-bit delimiter, a 7-bit EOF field, a 6-bit error frame, and many more. None of this resembles the 8-bit or 16-bit data structure of the microcontroller.

So how is it possible to program according to the network protocol? Here, the future constructor need not worry. There is a plethora of readymade, inexpensive building blocks available for the network. It is this support by IC manufacturers for the CAN that has made the network so popular in such a short time.

The next instalment will deal with these building blocks, with the programming according to the CAN protocol and with practical application of the network.

[990066]

#### **C** O N S T R U C T I O N GUIDELINES

Elektor Electronics (Publishing) does not provide parts and components other than PCBS, fornt panel foils and software on diskette or IC (not necessarily for all projects). Components are usually available form a number of retailers – see the adverts in the magazine.

Large and small values of components are indicated by means of one of the following prefixes :

| $E(exa) = 10^{18}$   | a (atto) = $10^{-18}$            |

|----------------------|----------------------------------|

| $P(peta) = 10^{15}$  | $f(femto) = 10^{-15}$            |

| T (tera) = $10^{12}$ | $p(pico) = 10^{-12}$             |

| $G (giga) = 10^9$    | $n (nano) = 10^{-9}$             |

| $M (mega) = 10^{6}$  | $\mu$ (micro) = 10 <sup>-6</sup> |

| $k (kilo) = 10^3$    | $m (milli) = 10^{-3}$            |

| h (hecto) = $10^2$   | $c (centi) = 10^{-2}$            |

| da (deca) = $10^1$   | d (deci) = $10^{-1}$             |

In some circuit diagrams, to avoid confusion, but contrary to IEC and BS recommandations, the value of components is given by substituting the relevant prefix for the decimal point. For example,  $3k9 = 3.9 k\Omega$  $4\mu7 = 4.7 \,\mu\text{F}$

Unless otherwise indicated, the tolerance of resistors is  $\pm$  5% and their rating is  $\frac{1}{2}-\frac{1}{2}$  watt. The working voltage of capacitors is  $\geq 50$  V.

In populating a PCB, always start with the smallest passive components, that is, wire bridges, resistors and small capacitors; and then IC sockets, relays, electrolytic and other large capacitors, and connectors. Vulnerable semiconductors and ICS should be done last.

Soldering. Use a 15-30 W soldering iron with a fine tip and tin with a resin core (60/40) Insert the terminals of components in the board, bend them slightly, cut them short, and solder: wait 1-2 seconds for the tin to flow smoothly and remove the iron. Do not overheat, particularly when soldering ICS and semiconductors. Unsoldering is best done with a suction iron or special unsoldering braid.

Faultfinding. If the circuit does not work, carefully compare the populated board with the published component layout and parts list. Are all the components in the correct position? Has correct polarity been observed? Have the powerlines been reversed? Are all solder joints sound? Have any wire bridges been forgotten?

If voltage levels have been given on the circuit diagram, do those measured on the board match them – note that deviations up to  $\pm 10\%$ from the specified values are acceptable.

Possible corrections to published projects are published from time to time in this magazine. Also, the readers letters column often contains useful comments/additions to the published projects.

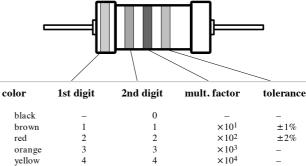

The value of a resistor is indicated by a colour code as follows.

| brown  | 1 | 1 | $\times 10^{1}$  | ±1%   |

|--------|---|---|------------------|-------|

| red    | 2 | 2 | $\times 10^{2}$  | ±2%   |

| orange | 3 | 3 | $\times 10^{3}$  | -     |

| yellow | 4 | 4 | $\times 10^4$    | -     |

| green  | 5 | 5 | ×10 <sup>5</sup> | ±0,5% |

| blue   | 6 | 6 | $\times 10^{6}$  | _     |

| violet | 7 | 7 | -                | -     |

| grey   | 8 | 8 | -                | -     |

| white  | 9 | 9 | -                | -     |

| gold   | - | - | $\times 10^{-1}$ | ±5%   |

| silver | _ | - | $\times 10^{-2}$ | ±10%  |

| none   | - | - | -                | ±20%  |

Examples

brown-red-brown-gold =  $120 \Omega$ , 5% yellow-violet-orange-gold =  $47 \text{ k}\Omega$ , 5%

# poor man's short-wave radio small but effective

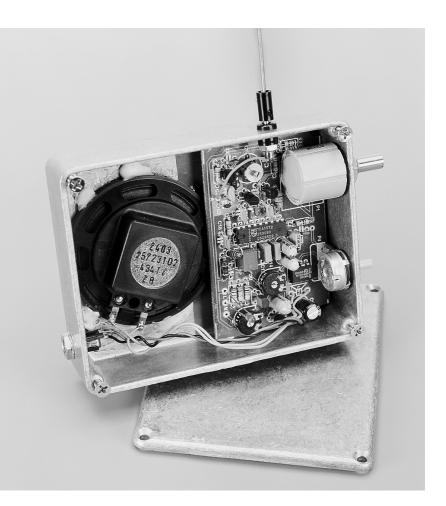

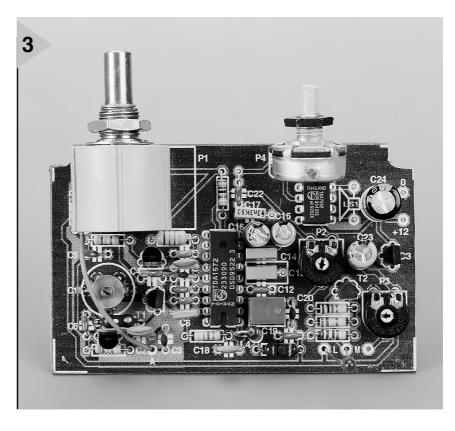

The design described in this article is one of those with immediate appeal. It is easy to build, very compact, and offers exceedingly good performance. Even with only a short whip antenna, it receives a myriad of broadcasting stations at good strength.

### Some parameters

| ٠ | Frequency range                | approx. 5.5-12.5 MHz   |

|---|--------------------------------|------------------------|

|   | (25 m, 31 m, 41                | m, and 49 m bands)     |

| ٠ | Sensitivity (6 dB signal-to-ne | oise) approx. 1 μV     |

| ٠ | AGC range                      | 86 dB                  |

| ٠ | Intermediate frequency         | 455 kHz                |

| ٠ | Audio power output             | 1 watt into 8 $\Omega$ |

| ٠ | Quiescent current drain        | about 50 mA            |

| ٠ | Supply voltage                 | 12–15 V                |

|   |                                |                        |

Anyone with only the slightest interest in radio-frequency engineering will immediately be captivated by the tiny receiver described here. It is constructed on a printed-circuit board

a small loudspeaker at the output. Nevertheless, it receives broadcasting stations from all over the world: the Voice of America; Radio Moscow; Radio Prague, not forgetting the BBC World Service when you're on holiday. And all that with a minimum of controls. **FOUR BANDS IN ONE**

#### The receiver is designed for operation over a single range containing the 25 m, 31 m, 41 m, and 49 m, short-wavebands. There is therefore no need for a band selector. It is tuned with the aid of

measuring  $8.5 \times 5$  cm  $(3.4 \times 2 \text{ in})$  and consists of only a handful of components, a whip antenna at the input and

Design by G Baars PE1GIC

varactors (also called voltage-controlled capacitors or voltage-variable capacitors – see inset) and a multi-turn potentiometer. The latter ensures that in spite of the very wide range, tuning is accurate and comfortable. The tuning indicator may be a light-emitting diode (LED) or moving-coil  $\mu$ A-meter.

The receiver is designed for the reception of amplitude-modulated (AM) signals only, since that is the universal mode of operation by broadcasting stations in the short-wave bands. The intermediate frequency (IF) bandwidth is 6 kHz, which ensures good audio reproduction.

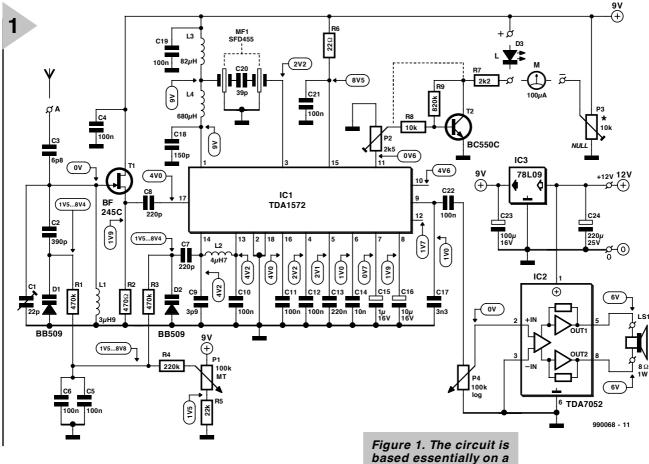

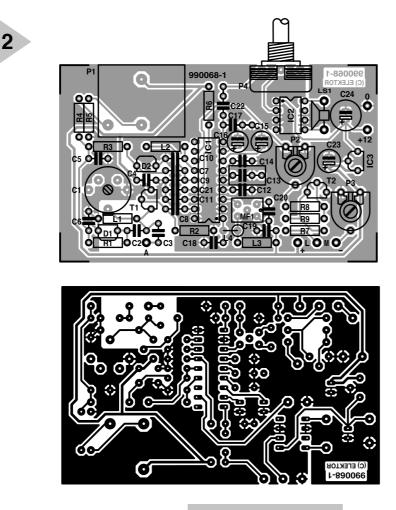

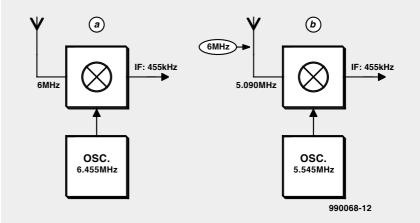

#### TWO INTEGRATED CIRCUITS