March 1995 £ 2·45

THE INTERNATIONAL ELECTRONICS MAGAZINE

ALAKIO:

# **DSP FUNCTION GENERATOR** Stepper motor ICs

Wideband active loop antenna

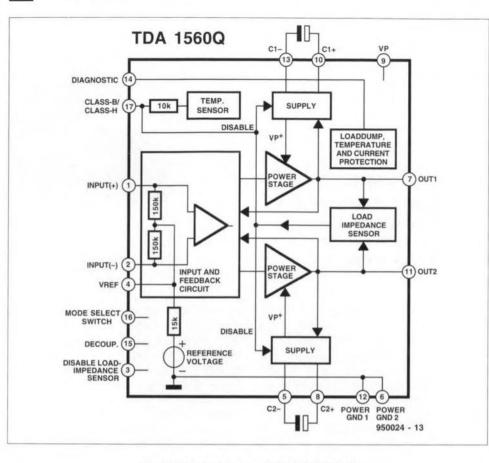

TDA1560@r a 30 W audio amplifier for cars

Long-life night light Telephone-con

bellovinoo-enongeleT mains switch

#### In next month's issue

- FOCUS ON: MICROCONTROLLER DEVELOPMENT SYSTEMS

- Chip cards .

- Sun blind control .

- Stepper motor control

- Electronic barometer

- Simple function generator

- Bat detector

- . and others for your continued interest.

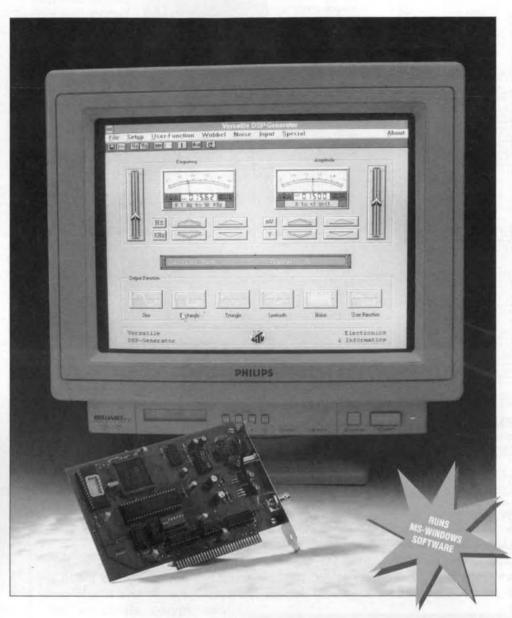

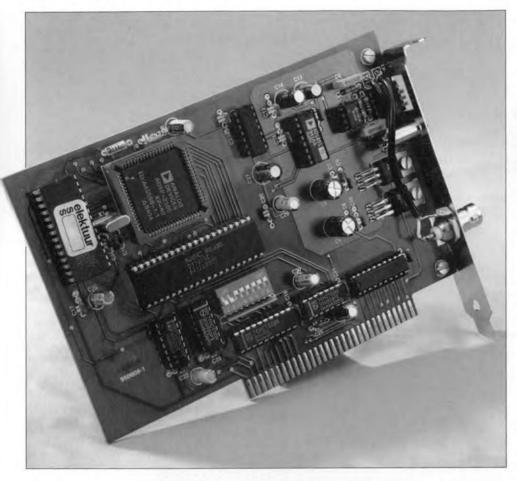

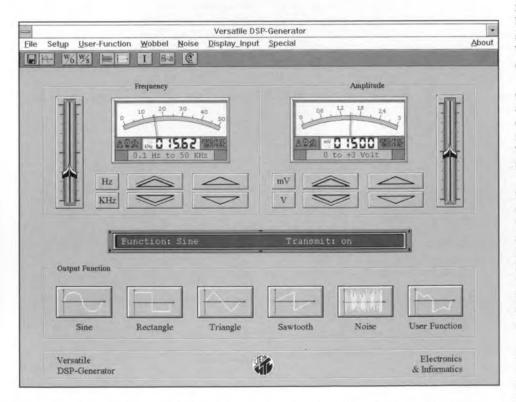

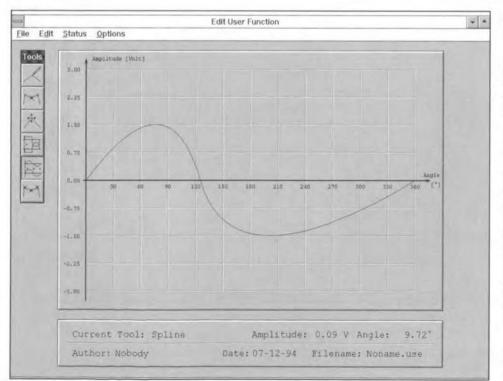

#### Front cover

No electronics workshop or laboratory is complete without a function generator. The one described on p.42 is an insertion card for PCs and controlled entirely by software. The heart of the generator is a digital signal processor (see also p. 24) from Analog Devices. The card is controlled by a DOS or a Windows program supplied on disk (see p.70). The Windows version even allows you to create your own waveshapes.

Copyright © 1995 Elektuur

## CONTENTS

#### APPLICATION NOTE

28 LMD 18245 3 A, 55 V stepper motor driver A National Semiconductor Application

#### AUDIO & HI-FI

5

PROJECT: 30 W a.f. amplifier for cars Design by T. Giesberts

#### COMPONENTS

24 Digital signal processors By L. Lemmens

#### GENERAL INTEREST

- 16 FOCUS ON: CD ROM standards and applications By our editorial staff 32 **PROJECT**: Long-life night light

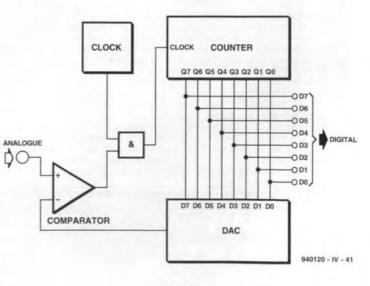

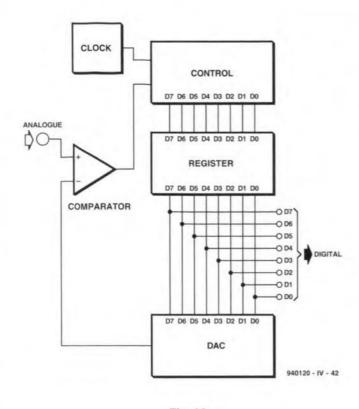

- Design by H. Bonekamp 52 COURSE: The digital solution

- Part 4: Analogue to digital By Owen Bishop 58

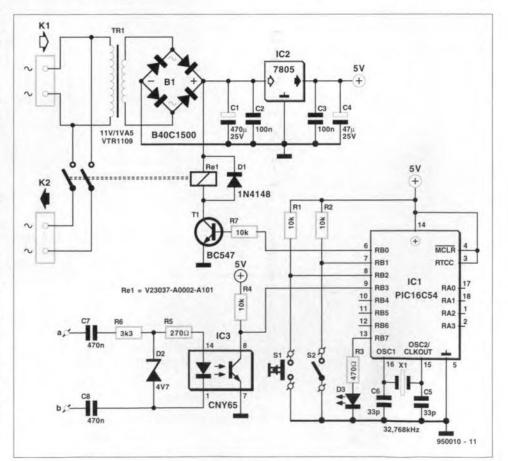

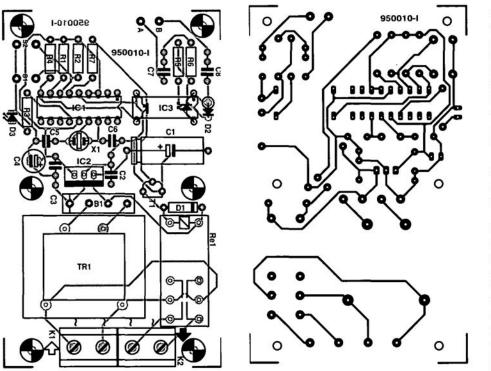

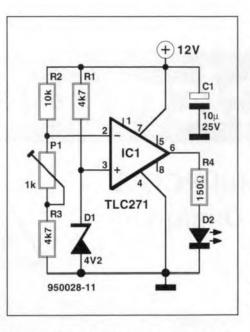

- **PROJECT**: Telephone-controlled mains switch Design by H. Kiprowski 62

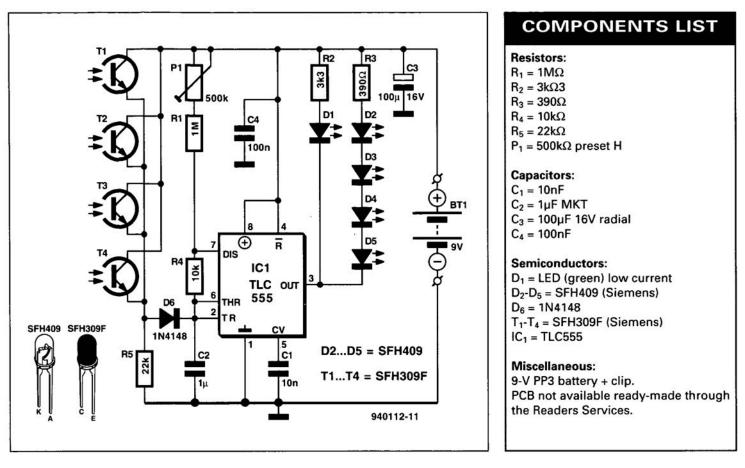

- **PROJECT:** Electronic fireflies Design by H. Bonekamp

- PROJECT: Mock car alarm 66 Design by L. Lemmens

#### RADIO, TV AND COMMUNICATION

10 **PROJECT**: Wideband active loop antenna Design by J. Barendrecht

#### **TEST & MEASUREMENTS**

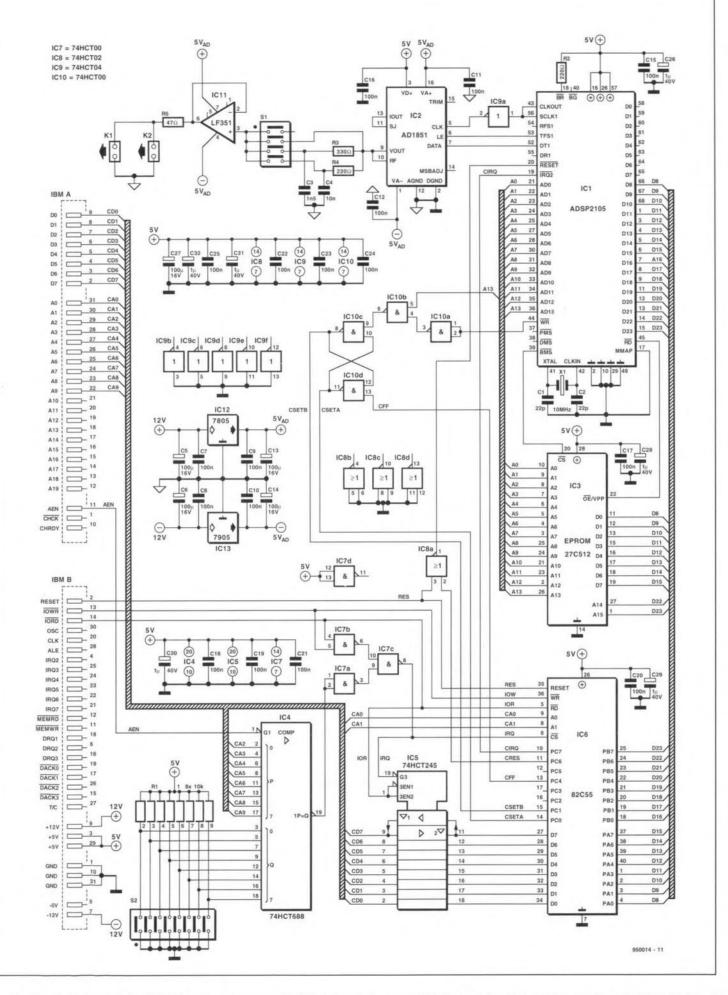

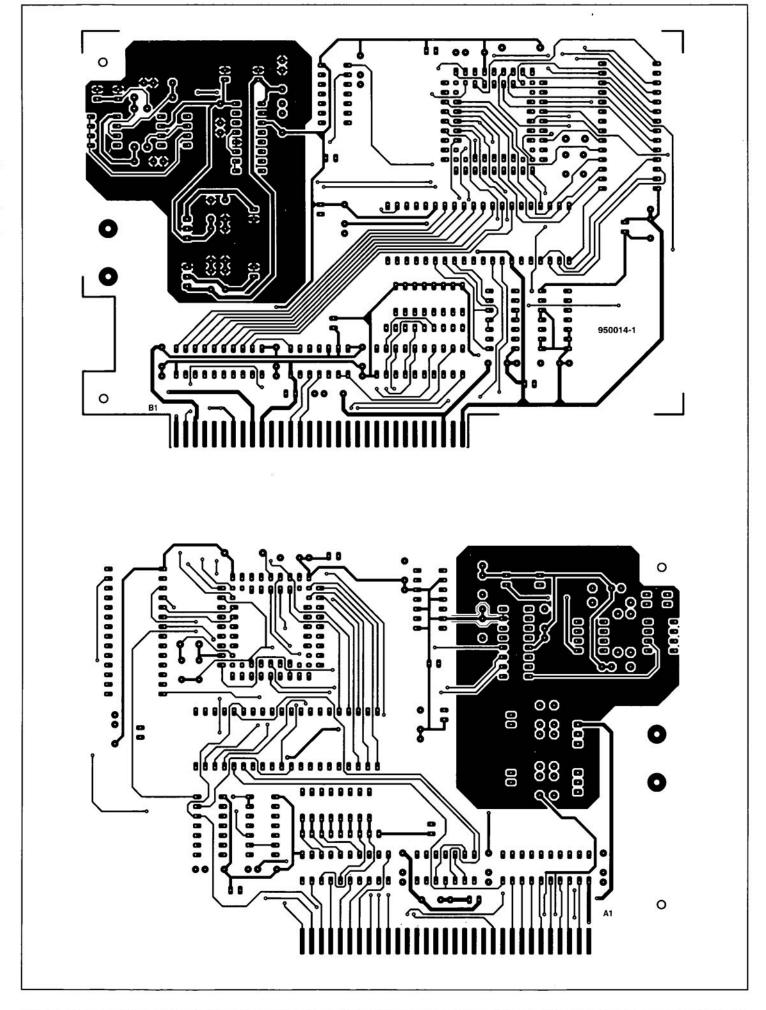

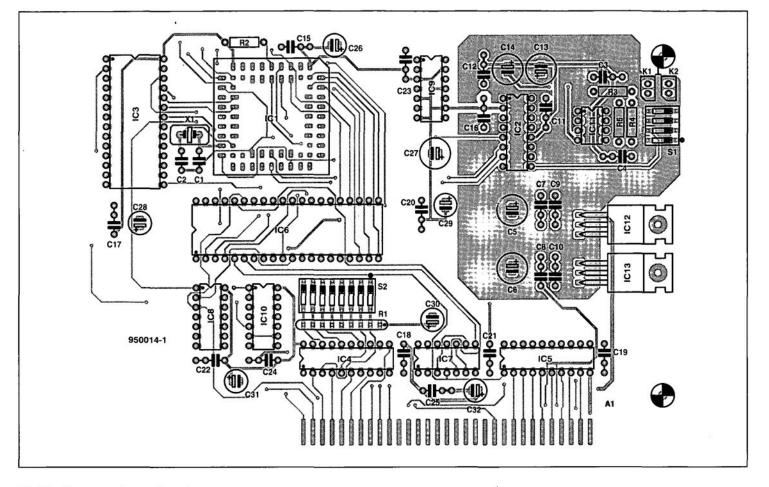

42 **PROJECT:** DSP function generator Design by P. Hackl, M. Haidinger, R. Leeb and F. Reithuber

#### **MISCELLANEOUS INFORMATION**

| 73 | Book availability & prices |

|----|----------------------------|

| 74 | Buyers' guide              |

| 68 | CeBIT95                    |

| 74 | Index of advertisers       |

| 68 | New Books                  |

| 38 | Product overview           |

| 70 | Readers' services          |

| 73 | Switchboard                |

| 72 | Terms of Business          |

March 1995 Volume 21 Number 231 ISSN 0268/4519

30 W a.f. amplifier for cars - p. 5

Wideband active loop antenna p. 10

CD ROM standards and applications - p. 16

Electronic fireflies - p. 62

Elektor Electronics is published monthly, except in August, by Elektor Electronics (Publishing). P.O. Box 1414, Dorchester, Dorset DT2 8YH, England. The magazine is available from newsagents, bookshops, and electronics retail outlets, or on subscription at an annual (1994/95) post paid price of £28-00 in the United Kingdom; air speeded: £35-00 in Europe, £44-00 in Africa, the Middle East and South America; £46-00 in Australia, New Zealand and the Far East; and \$US 59.00 in the USA and Canada. Second Class Postage paid at Rahway N.J. Postmaster: please send address corrections to Elektor Electronics, c/o Mercury Airfreight International Inc., 2323 Randolph Avenue, Avenel, New Jersey, N.J. 07001.

### **30 W AF AMPLIFIER FOR CARS**

#### **Design by T. Giesberts**

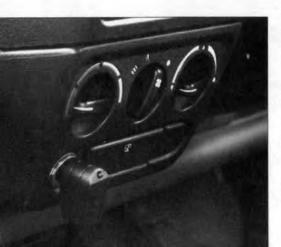

The power that can be obtained from a standard car radio amplifier operating from a 12 V car battery is 5–6 W, which (for many listeners) is not really enough for satisfactory hi-fi reproduction. It is, of course, possible to boost the 12 V supply with a power inverter, but that is fairly expensive and not always acceptable. Now, a Philips IC enables audio power of about 30 W to be obtained from a 12 V car battery.

Tntil not so long ago, the Class B output stages of a standard car radio could not deliver more than 2× 5–6  $W_{rms}$  into 4  $\Omega$  loudspeakers. More was not possible with a single supply line of 12 V. Most modern car radios use bridge amplifiers to boost the output to 12-16 W. Often, each of the four loudspeakers has its own dedicated amplifier. Many car manufacturers do not like the use of power inverters to raise the on-board voltage out of fear that these can cause (embarrassing or even dangerous) interference with the remainder of the electronic systems in the car (of which there can be many). There is also the problem of heat generation in the output stages, which may necessitate forced cooling.

#### **Class H**

Electronics manufacturers have been researching ways and means of obtaining adequate output power without the use of a power inverter, and Philips have come up with the TDA1560Q.

Output amplifiers can be arranged in a number of different configurations, of which most audio enthusiasts only know Class A and Class B. A different one that provides fairly high output power with relatively low dissipation is Class G. In this configuration, use is made of two supply voltages: a fairly low one that is constantly available and a much higher one that becomes available only when the the voltage swing of the output stages can not be sustained by the low supply voltage.

Since in cars only one supply voltage is available, Philips engineers have devised a pseudo Class G configuration in which a number of electrolytic capacitors are charged by the battery voltage. During brief voltage peaks in the output signal, semiconductor switches connect these capacitors in series with the 12 V line so that the supply voltage to the amplifier is temporarily doubled. Since this is a further development of the Class G technique, it is named Class H. The (temporary) 24 V supply to the amplifier enables (theoretically) a power of 80 W to be delivered into 4  $\Omega$  or 40 W into 8  $\Omega$ .

A simplified diagram of a Class H

Power bandwidth (-3 dB)

output amplifier is shown in **Fig. 1**. It contains two principal circuits: the first is a Class B amplifier,  $T_1-T_4$ , which is loaded by  $R_1$ , and the second raises the internal supply voltage. The second circuit uses two external capacitors,  $C_1$  and  $C_2$ , which serve as supply buffers.

Since a music signal consists only

| Brief                               | fechnical Data                           |

|-------------------------------------|------------------------------------------|

| Class H operation                   |                                          |

| Low dissipation with music signals  |                                          |

| Extensive protection circuits (outp | ut current; temperature; load impedance) |

| Supply voltage                      | 12 V nominal                             |

| Quiescent current                   | 100 mA                                   |

| Output power                        |                                          |

| (1  kHz sinusoidal, THD = 0.5%)     | 30 W r.m.s. into 8 Ω                     |

| (music signal)                      | 40 W into 8 Ω                            |

| THD + noise (1 W into 8 $\Omega$ )  | <<0.01% (1 kHz)                          |

|                                     | <<0.05% (20 Hz to 20 kHz)                |

| THD + noise (20 W into $8 \Omega$ ) | <<0.06% (1 kHz)                          |

|                                     | <<0.2% (20 Hz to 20 kHz)                 |

|                                     |                                          |

V3

LIFT/ RECHARGE CONTROL

LIFT/ RECHARGE CONTROL

V3

V4

T

V1

T1

T7

T6

C2

V4

T

V1

T1

T7

T6

C2

T4

T

V1

T2

T4

T4

T4

T5

V2

T2

T4

T4

T5

V1

T2

T4

T4

T5

5 Hz to 100 kHz

Fig. 1. Diagram of a basic Class H amplifier.

5

Fig. 2. Block diagram of the TDA1560Q

for a small part of high level components, the supply voltage needs to be raised for a small part of the time only.

Because the supply voltage is raised for short periods of time only, the average dissipated power will be only slightly higher than that of an amplifier without a voltage-raising circuit, in spite of the fact that the peak output power is appreciably higher.

Capacitors  $C_1$  and  $C_2$  are charged through current sources  $T_7$  and  $T_8$  to a voltage which is nearly equal to the supply voltage,  $E_1$ . When either voltage V<sub>1</sub> (or V<sub>2</sub>) rises and T<sub>1</sub> (or T<sub>3</sub>) approaches the saturation voltage, the lift control circuit detects this. Lift transistors T<sub>5</sub> and T<sub>6</sub> then conduct, so that the charged capacitors are switched between the collector of T<sub>1</sub> (or T<sub>3</sub>) and supply voltage E<sub>1</sub>. Diodes D<sub>1</sub> and D<sub>2</sub> prevent the capacitors being discharged via the battery. Voltage V<sub>1</sub> (or V<sub>2</sub>) can increase to nearly twice the supply voltage. The lift/recharge control circuit ensures that T<sub>5</sub> and T<sub>7</sub>, and T<sub>6</sub> and T<sub>8</sub>, can not conduct simultaneously.

#### Inside the TDA1560Q

A block diagram of the TDA1560Q is shown in **Fig. 2**. A differential input stage in the input and feedback circuit is connected to pins 1 and 2. Because of this stage, the IC is highly insensitive to common-mode interference. The input impedance is  $300 \text{ k}\Omega$ , so that for a good low-frequency response even small input capacitors are sufficient.

The input and feedback circuit contains circuitry that controls the supply circuits and the power stages.

The control circuitry monitors the input signal and anticipates saturation of the output transistors. As soon as this happens, the supply voltage is raised. Because the input signal is monitored, it is possible to control the lift voltage. To keep the dissipation at a minimum, the supply voltage is raised only to a level where the output will stay below the clipping level.

A current limiter protects the out-

#### Produced and published by ELEKTOR ELECTRONICS (Publishing)

Editor: Len Seymour Technical Editor: Jan Buiting

Editorial & Administrative Offices: P.O. Box 1414 DORCHESTER DT2 8YH England Telephone: (01305) 250 995 (*National*) or +44 1305 250 995 (*International*) Fax: (01305) 250 996 (*National*) or +44 1305 250 996 (*International*)

U.K. Advertising Office: 3 Crescent Terrace CHELTENHAM GL50 3PE Telephone: (01242) 510 760 Fax: (01242) 226 626

International Advertising Office: Elektuur BV P.O. Box 75 6190 AB BEEK The Netherlands Telephone: +31 46 38 94 44 Fax: +31 46 37 01 61

Subscriptions: World Wide Subscription Service Ltd. Unit 4, Gibbs Reed Farm Pashley Road TICEHURST TN5 7HE **Telephone:** (01580) 200 657 (*National*) or +44 1580 200 657 (*International*) **Fax:** (01580) 200 616 (*National*)

or +44 1580 200 616 (International)

#### Head Office

P.O. Box 75 6190 AB BEEK The Netherlands Telephone: +31 46 38 94 44 Telex: 56617 (elekt nl) Fax: +31 46 37 01 61 Managing Director: Johan H. Boermann Deputy Managing Director:

Menno M.J. Landman Editor-in-Chief/Publisher: Pierre E.L. Kersemakers Commercial Manager: Karel van Noordenne

Distribution: SEYMOUR 1270 London Road LONDON SW164DH

Printed in the Netherlands by NDB, Zoeterwoude Overseas editions: FRANCE Elektor sarl Les Trois Tilleuls B.P. 59; 59850 NIEPPE Editor: G.C.P. Raedersdorf

#### GERMANY Elektor Verlag GmbH Süsterfeld Straße 25 5100 AACHEN

5100 AACHEN Editor: E.J.A. Krempelsauer

GREECE Elektor EPE Karaiskaki 14 16673 Voula—ATHENA Editor: E. Xanthoulis

#### INDIA

Elektor Electronics PVT Ltd Chhotani Building 52C, Proctor Road, Grant Road (E) BOMBAY 400 007 Editor: C.R. Chandarana

ISRAEL Elektorcal P O Box 41096 TEL AVIV 61410 Publisher: M. Avraham NETHERLANDS

Elektuur BV Peter Treckpoelstraat 2–4 6191 VK BEEK Editor: P.H.M. Baggen

#### POLAND

Elektor Elektronik 02–777 Warszawa 130 Skrytka Pocztowa 271 Editor: W. Marciniak

#### PORTUGAL

Ferreira & Bento Lda. R.D. Estefáni, 32-1° 1000 LISBOA Editor: F. Ferreira de Almeida

#### SPAIN

Resistor Electronica Aplicada SA P. de la Castellana, 212–4° Izda 28046 MADRID Editor: Agustin Gonzales Buelta

SWEDEN Electronic Press AB

Box 5505 14105 HUDDINGE Editor: Bill Cedrum put stages against being short-circuited to ground or to the supply line. In general, whenever the current drawn exceeds a level of 5.5 A, the output and the power stages are switched off. The protection circuit monitors at short intervals whether the short-circuit has been removed. If so, the output stages are reactuated. This arrangement limits the dissipation in the power stages during shortcircuits to a minimum.

There is a dual temperature protection. The first switches off the voltage doublers when the temperature of their cases rises above 120 °C. The amplifier can then operate in Class B only. The second protection uses sensors located close to the output and switching transistors. If these sensors measure a temperature higher than 165 °C, the base current of the associated transistor is lowered.

There is also a circuit that monitors the load impedance. After the amplifier has been switched on, the d.c. resistance of the loudspeaker(s) is determined by passing a current through the speaker coil(s) and measuring the consequent voltage drop across it.. Because of the peak current that the power stages can handle, the Class H section is switched off when a 4  $\Omega$  loudspeaker is detected. The IC then operates as a Class B amplifier. When the load impedance drops below  $0.5 \Omega$ , it is considered a short circuit and the entire IC is disabled. The impedance sensor is very sensitive and may be actuated by spurious pulses (for instance, when a car door gets closed during switch-on: the loudspeakers then act as microphones). The sensor may be disabled by shorting pin 3 to ground.

Finally, the IC contains an internal reference voltage source for the input circuits. This reference is decoupled by a capacitor at pin 4.

#### **Circuit description**

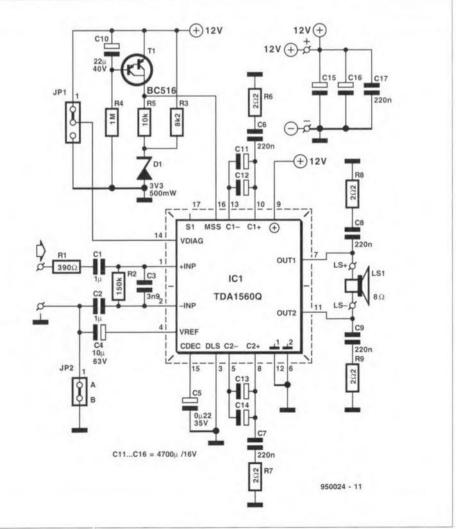

The circuit diagram of the 30 W AF amplifier is shown in Fig. 3. The input is connected to the differential input stage (pins 1 and 2) via coupling coupling capacitors  $C_1$  and  $C_2$ . Although the -ve input is linked to earth via wire bridge A-B, the arrangement gives good commonmode rejection in spite of the assymetrical input. A true symmetrical input is obtained when wire bridge A-B is omitted from the board. Network R1-C3 forms a low-pass filter that suppresses HF interference at the input. The input impedance is determined largely by the value of  $R_2$ .

The circuit around darlington  $T_1$  provides a delay at switch-on to suppress switching noise reaching the output stages. This is essential since

the impedance measuring sensor (which normally provides the suppression) has been disabled here (pin 3 to ground).

As soon as the supply voltage is on, a potential of 3 V is applied to pin 16 via  $R_3$  and  $D_1$  to place the IC in the mute mode. Initially, since  $C_{10}$  is discharged,  $T_1$  remains off. However, the capacitor then gets charged via  $R_4$  and within a few seconds the voltage across it has risen to a level at which  $T_1$  begins to conduct. This results in a voltage of 12 V being applied to pin 16, whereupon the power stages operate normally.

Various facilities are open to the user via pin 14. For instance, it may be used to detect whether one of the protection circuits is working. Normally, this pin is at the level of the supply voltage. If its potential is only half that value, one of the protection circuits is actuated. When the pin is linked to ground via jumper JP<sub>1</sub>, the amplifier is muted. When the jumper is connected to +12 V, all protection circuits are disabled. For normal operation, therefore, no jumper should be placed at JP<sub>1</sub>.

Capacitors  $\rm C_{15}$  and  $\rm C_{16}$  buffer the 12 V battery voltage. Capacitors  $\rm C_{11}\text{-}C_{12}$  and

$C_{13}\text{-}C_{14}$  are required by the lift/control circuit. Two parallel-connected 4700  $\mu F$  electrolytic capacitors are used in each case, because these take up less space on the board than a single 10,000  $\mu F$  component. Networks  $R_6\text{-}C_6$  and  $R_7\text{-}C_7$  are interference suppressors.

A Boucherot network,  $R_8$ - $C_8$  and  $R_9$ - $C_9$ , is provided at each loudspeaker terminal to maintain a 'normal' load at high frequencies (at which the loudpeaker impedance rises appreciably owing to its inductive behaviour).

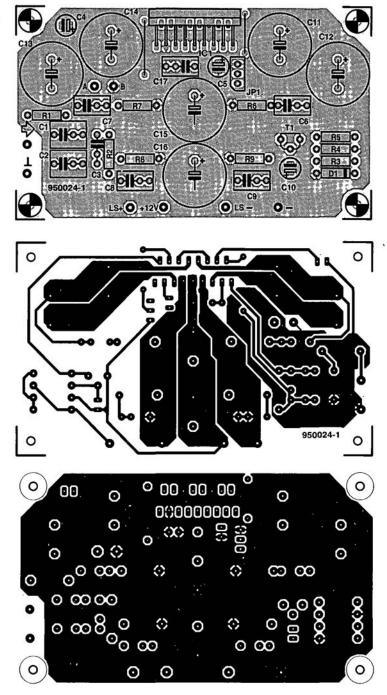

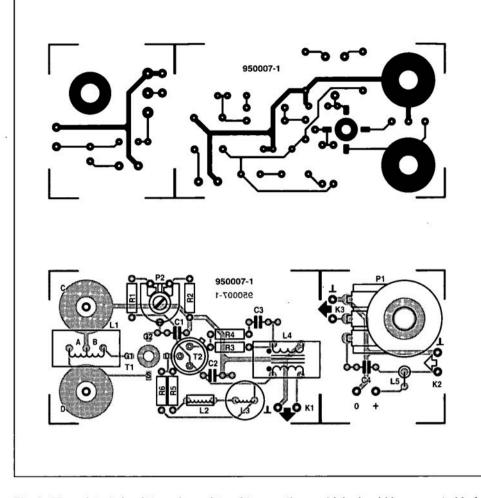

#### Construction

The construction is limited to populating the printed-circuit board shown in **Fig. 4**. The IC must protrude slightly from the board so that it can be fitted flush against the heat sink. An insulating washer between IC and heat sink is a must: apply heat conducting paste to both the base of the IC and the heat sink. The insulating washer may have to be cut to size from a mica T03 washer.

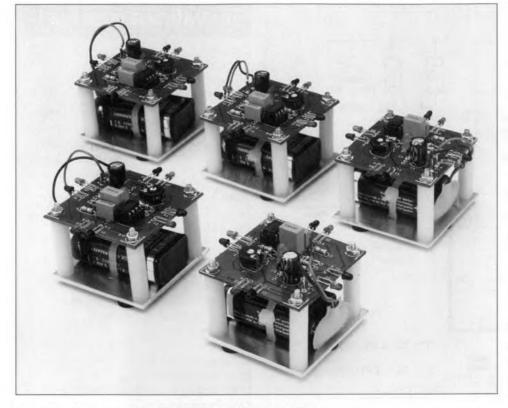

Most constructors will use two amplifiers in one enclosure for a compact stereo setup. It is, however, also possible to use four amplifiers in one case: one for each

Fig. 3. Circuit diagram of the 30 W AF amplifier for cars.

#### .

AUDIO & HI-FI

of the two front and rear speakers. Make sure that none of the loudspeaker cables or terminals can touch the chassis, because that does not do the bridge amplifier any good in the long term in spite of the protection circuits.

#### **Parts list**

8

#### **Resistors**:

$\begin{array}{l} R_1 = 390 \ \Omega \\ R_2 = 150 \ k\Omega \\ R_3 = 8.2 \ k\Omega \\ R_4 = 1 \ M\Omega \\ R_5 = 10 \ k\Omega \\ R_6 - R_9 = 2.2 \ \Omega \end{array}$

#### Capacitors:

C<sub>1</sub>, C<sub>2</sub> = 1  $\mu$ F, pitch 5 mm C<sub>3</sub> = 3.9 nF C<sub>4</sub> = 10  $\mu$ F, 63 V, radial C<sub>5</sub> = 220 nF, 35 V, tantalum C<sub>6</sub>-C<sub>9</sub>, C<sub>17</sub> = 220 nF C<sub>10</sub> = 22  $\mu$ F, 40 V, radial C<sub>11</sub>-C<sub>16</sub> = 4700  $\mu$ F, 16 V, radial

#### Semiconductors:

$D_1 = zener, 3.3 V, 500 mW$  $T_1 = BC516$

#### Integrated circuits:

$IC_1 = TDA1560Q$

#### Miscellaneous:

Heat sink for IC<sub>1</sub>;  $R_{th} \ll 2.5 \text{ K W}^{-1}$ PCB Order No. 950024-1

[950024]

Fig. 4. Printed circuit board for the 30 W AF amplifier for cars.

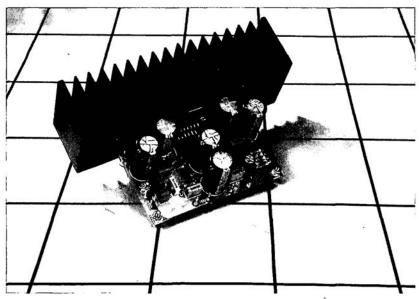

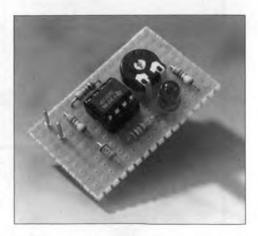

Fig.5. The completed (prototype) 30 W AF amplifier for cars.

# WIDEBAND ACTIVE LOOP ANTENNA

Wideband antenna design is problematic because size and performance are conflicting aspects. The wideband antenna described in this article covers the long, medium and shortwave bands up to about 50 MHz, and achieves excellent efficiency while remaining reasonably sized.

#### Design by J. Barendrecht

ANY shortwave DXers lack the space to erect a large, tuned, antenna, and have to resort to much smaller alternatives. Not surprisingly, these are nearly always active antennas, which are expected to do 'the impossible' (well, almost). Ideally, they should have a low noise level, good large signal handling, wideband characteristics with a stable output level across the entire frequency range, and, last but not least, they should be usable in areas with a high noise level (i.e., in and around the city). Unfortunately, you can not expect all that from an active antenna. Low noise and a wideband response, for instance, are contending aspects, while immunity against man-made noise is very difficult to achieve. However, if the latter aspect is the most important (and in many cases it will, unless you live in the middle of nowhere), there is

no alternative than to use a rhombic or loop antenna, which (ideally) responds to the magnetic component only of the energy picked up from the transmitter. Because it ignores electric components, this type of antenna keeps out a lot of man-made interference.

However, choosing a loop antenna does not solve all problems because good wideband response is difficult to achieve with this type of antenna. The voltage induced in the antenna drops significantly below the resonance frequency. At higher frequencies, too, problems occur because the induced voltage is in series with the loop's selfinductance. This, in combination with the amplifier's input capacitance, creates a low-pass filter with a roll-off frequency which can be so low that it becomes a troublesome factor. Consequently, it is essential to ensure proper matching between the passive part of the antenna (i.e., the loop) and the active part (i.e., the amplifier). In all cases, however, the best you will be able to achieve is still a trade-off.

#### A MOSFET amplifier

Recapping the above, the active part of the antenna should couple good large signal behaviour with low noise, and in addition present a very low input capacitance.

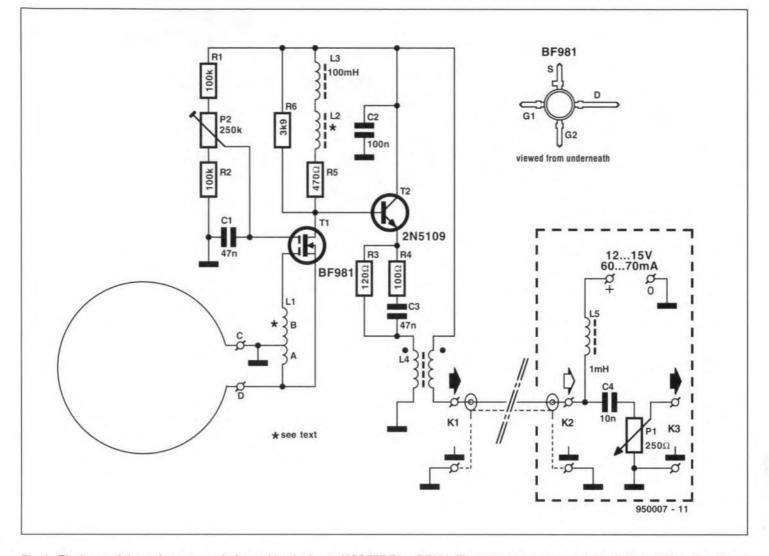

The circuit diagram shown in Fig. 1 shows the amplifier sitting between the loop (which will be reverted to) and the phantom power supply. A dualgate MOSFET, T1, is used as a transconductance amplifier to match the impedance of the loop to that of the output coax cable. Transistor T<sub>2</sub> is the actual amplifying device. Some of you may wonder about the use of the BF981 MOSFET, which would appear to be designed for VHF/UHF applications only. However, the specifications of this MOSFET indicate that it also has low noise at lower frequencies. provided its very high input impedance is properly matched.

Input matching is not a problem at relatively low frequencies. The loop antenna used here has a diameter of about 1 m (3 feet), and its low impedance at low frequencies is easily stepped up. Problems occur at higher frequencies, however, because then the self-inductance of the loop (approx. 5 µH) is also stepped up, and starts to cause trouble. The BF981 has an input capacitance of about 2 pF. while the capacitance of a regular input transformer lies between 0.5 pF and 1 pF. Some form of damping is, therefore, required to prevent unwanted resonance peaks. Although that can be achieved by the simple addition of a resistor, everything possible has to be done not to attenuate the already weak signals picked up by the antenna. Hence, some means of damping the loop has to be devised which does not unduly attenuate the RF signal

The problem is not new, of course, and had to be contended with in the design of RF stages in early FM receivers using valves. Triodes offered a lower noise figure than pentodes, but only if neutralizing ( or 'neutrodyne') techniques were applied. If that could not be done, there was the grounded grid amplifier to resort to. Not a good alternative, though, because it had a higher noise figure, and offered less gain.

A compromise was found in the

Fig. 1. The heart of the active antenna is formed by dual-gate MOSFET T1, a BF981. The antenna proper consists of a loop with a diameter of about 1 m.

inter-grid or inter-base amplifier. This type of bridge circuit required no neutralizing, and did not degrade the noise figure with respect to the commoncathode amplifier.

The amplifier used here revives the above technology, and may be called an inter-gate type (the electrical behaviour of a MOSFET being very similar to that of a thermionic valve). This circuit is easy to recognize from the fact that the source of the MOSFET is connected to the input transformer rather than to ground, while the tap on the transformer is connected to ground. The amplifier is therefore, best classified between a grounded-gate and a grounded-source circuit.

Here, the choice of an inter-base circuit has nothing to do with avoiding neutralization as in the valve era — the prime design targets are now (1) matching and (2) damping. As already mentioned, there are no problems at relatively low frequencies. The output impedance of  $T_1$  (approx. 100  $\Omega$ ) is then insignificant, and the gate-source voltage is about six times the voltage induced in the loop. From about 3.4 MHz, the source input starts to act as a damping resistance, which eliminates resonance effects while extending the bandwidth of  $L_1$ . Precisely what we are after!

As a matter of course, the damping reduces the signal level supplied by the loop. The loop output voltage being small already, the MOSFET has to provide considerable gain at higher frequencies also. This has been achieved by inserting an inductor-resistor combination,  $R_5$ - $L_2$ , between the drain of  $T_1$  and choke  $L_3$ . The *RL* combination ensures a high drain impedance at higher frequencies also, because  $L_3$ then has a fairly high capacitive reactance. Resistor  $R_6$  keeps the gain of  $T_1$ within reasonable limits.

The amplified signal is coupled out via emitter follower  $T_2$  and a bifilar output transformer,  $L_4$ . From there, the signal is fed to the input of the receiver. At the receiver side, a small passive network is fitted. A potentiometer,  $P_1$ , is available to reduce the input signal when necessary. This control will be particularly useful when the active antenna is used with a receiver suffering from poor or average large-signal handling.

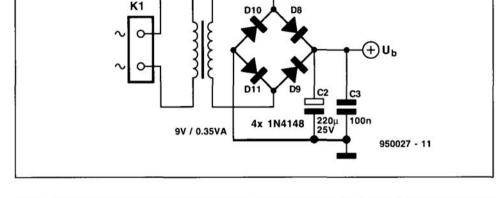

Choke  $L_5$  and capacitor  $C_4$  allow the RF signal and the preamplifier's supply voltage to be carried via the same coax cable. In most cases, it will be possible to take the supply voltage from the receiver. If not, the simplest of regulated power supplies is also fine, the current consumption of the preamplifier being modest at between 60 mA and 70 mA.

#### The loop antenna

The antenna proper consists of a loop with a diameter of about 1 m. Ideally, the loop should be made from metal tubing with a diameter of about 20 mm. The choice of metal is not so important. Plate material or even rectangular tubing of the same width may be used also. Ordinary copper wire is not suitable because it is too thin.

Those of you who live outside Europe may make the loop much larger to increase the output voltage and the signal-to-noise ratio. In Europe, a diameter of about 1 m is just 12

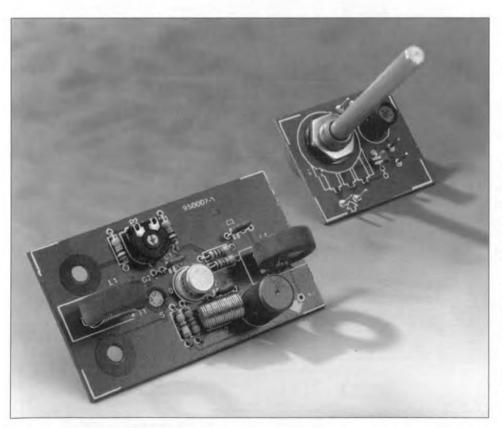

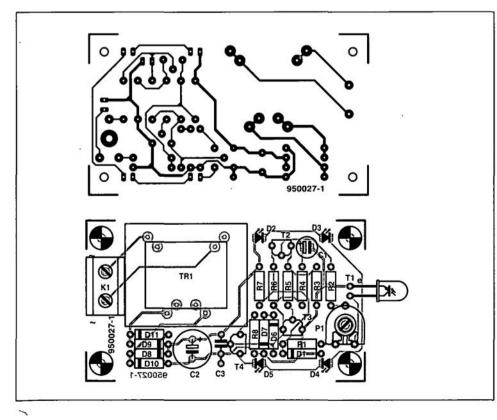

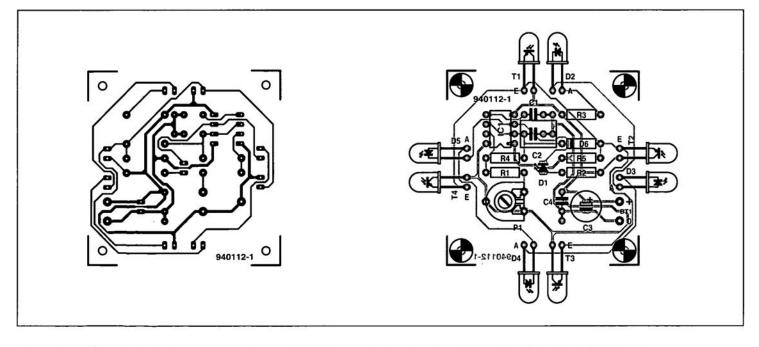

Fig. 2. The printed circuit board consists of two sections, which should be separated before they are populated. The section which has the potentiometer (P1) on it corresponds to the sub-circuit in the dashed box in Fig. 1.

about the maximum because of the very high signal levels which exist as a result of the area being the target of a very large number of short-wave broadcast transmitters. Increasing the loop diameter will, therefore, almost certainly cause input blocking effects in the receiver. A smaller loop is, of course, possible, although that will reduce the performance.

#### Construction

The artwork of the printed circuit board designed for the active antenna is shown in Fig. 2. Unfortunately, this board is not available ready-made through our Readers Services, so you . will have to make it yourself. Two important points have to be mentioned with respect to this board. The first is that the right-hand section has to be cut off because it holds the sub-circuit which is fitted inside or near the receiver. Secondly, the loop ends must be connected directly to points 'C' and 'D' on the board. In practice, it is best to secure the board between the loop ends.

Populating the board is straightforward with the possible exceptions of mounting  $T_1$  and making the inductors. The MOSFET,  $T_1$ , is fitted at the **copper** side of the board. Its type number should be legible when looking through the hole in the board from the component side. The longest terminal of the device is the drain (see also the pinout inset in Fig. 1).

The circuit has a total of five inductors. Three of these, L1, L2 and L4, are home-made, while L3 and L5 are offthe-shelf chokes. L2 consists of 20turns of 0.4-mm dia. enamelled copper wire, and has an internal diameter of 6 mm. No core is used, and the inductor may be wound on, say, a PCB spacer.  $L_1$  and  $L_4$  are both wound on a ferrite ring core type G2.3-FT16. L<sub>1</sub> consists of 24 turns with a tap at 4 turns; L<sub>1A</sub> has 4 turns, and L<sub>1B</sub>, 20 turns. Use 0.4 mm dia. (28SWG) enamelled copper wire. L4 is wound with slightly thinner wire (0.3 mm dia, 30SWG), and has two bifilar windings of 4 turns each. Bifilar means that you wind two wires at a time, so that the inductor halves run alongside each other. In all home-made inductors, the wire is close-wound, i.e., it is not spaced.

The prototype of the preamplifier

#### **COMPONENTS LIST**

#### **Resistors:**

- $R_1, R_2 = 100 k\Omega$

- $R_3 = 120\Omega$

- $R_4 = 100\Omega$

- $R_5 = 470\Omega$

- $R_6 = 3k\Omega 9$  $P_1 = 250\Omega$

- $P_2 = 250 k\Omega$  preset H

#### Capacitors:

$C_1, C_3 = 47$ nF Sibatit (Siemens)  $C_2 = 100$ nF Sibatit (Siemens)  $C_4 = 10$ nF Sibatit (Siemens)

#### Inductors:

$L_1 = 24$  turns 0.4 mm CuL (A = 4 turns, B = 20 turns), on ferrite ring core G2.3-FT16 \*.

$L_2 = 20$  turns 0.4 mm CuL, no core, diameter 6 mm.

$L_3 = 100$ mH (Toko 10RB-181LY-104).  $L_4 = 4+4$  turns 0.3 mm CuL, bifilar on ferrite ring core G2.3-FT16 \*.  $L_5 = 1$  mH (Toko).

Semiconductors:  $T_1 = BF981$  $T_2 = 2N5109$  (SGS Thomson)

#### Miscellaneous:

$K_1;K_2,K_3 = BNC$ -socket. PCB not available ready-made through the Readers Services.

\* C-I Electronics, P.O. Box 22089, NL-6360-AB Nuth, The Netherlands. Fax: (+31) 45 241877.

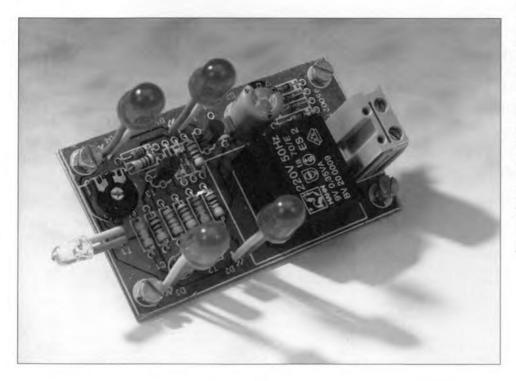

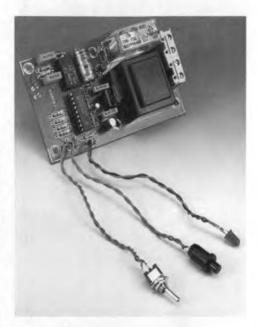

board is shown in **Fig. 3**. The photograph gives a fair indication of the construction of the home-made inductors.

Finally, a word about fitting the circuit into a case. The case should be a plastic type. If the antenna is installed out of doors, a watertight case should be used. Connectors  $K_1$ ,  $K_2$  and  $K_3$  should be good-quality BNC types.

#### Adjustment

You do not need expensive test equipment to adjust the active antenna. A multimeter, a short-wave receiver and a good sense of hearing are all that is needed.

To begin with, adjust preset  $P_2$  until the voltage at the drain of  $T_1$  is 1 V higher than half the supply voltage, i.e., 7 V if the supply voltage is 12 V, or 8.5 V if the supply voltage is 15 V. Next, check during the evening hours that signals in the 41-m, 31-m and 25m broadcast bands are sufficiently

13

strong. A considerable improvement should be noted over the regular whip antenna. If not, run a thorough check on the complete circuit.

If the antenna appears to work so far, the receiver is tuned between 21 MHz and 21.5 MHz (13-m band). Listen carefully for spurious signals in this band like harmonics, 'birdies', 'whistles' or intermodulation products. If such signals are noted, the receiver is probably overdriven. If the spurious signals do not disappear when the input level is reduced by operating potentiometer P1, carefully adjust the preset, P<sub>2</sub>, until a setting is found at which the level of the spurious signals is at a minimum. Next, tune to a weak signal in the 13-m band to check that the new setting does not unduly decrease the signal-to-noise ratio. possibly, a minor adjustment of P1 brings some improvement.

Finally, the above mentioned time for the adjustment is only valid for the winter months, and in the spring up to the end of April. In the summer months, the adjustment is best done around midnight.

Fig. 3. Although three inductors in the circuit are home made, the circuit is simple to build. ELEKTOR ELECTRONICS MARCH 1995 (950007)

## FOCUS ON: CD ROM STANDARDS AND APPLICATIONS

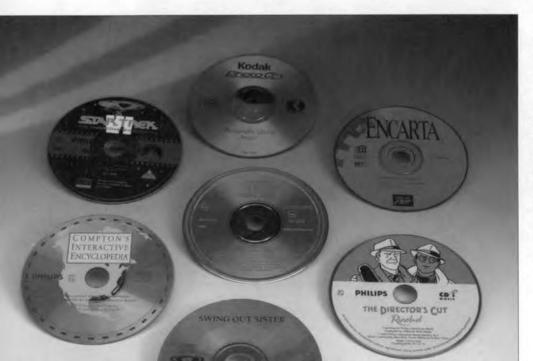

Since the introduction of the audio compact disc (CD) in 1982, this digital information carrier has been the nucleus of many developments. Today, the CD is not only used for music, but also for computer data and video. This article discusses the various CD standards that have evolved over the years. These are world standards which have been defined in the Red Book, Yellow Book, Green Book, Orange Book and White Book.

#### By our editorial staff

16

THE Compact Disc was born in Eindhoven, The Netherlands, at the Philips Research Laboratories. There, the concept of optical registration of digital data was developed. In 1980, when Philips N.V. and Sony agreed to promote the CD as a carrier of digital audio, it was difficult to foresee the overwhelming effect the silver disc would have on the music industry. In five years' time, some 30 million CD players were operational, and 450 million CDs sold. The gramophone, Edison's invention, and the most important sound medium for 80-odd years, was dead and buried at 'record' speed.

Since then, there's no stopping the CD. The shining silver disc is used for an increasing number of applications. The White Book, for instance, published in 1994 by Philips and JVC, gives details of the video CD, a CD variant which looks poised to open the attack on the prerecorded video tape. In the course of this year, both the computer industry and manufacturers of consumer electronics will introduce various systems which support digital video based on the video CD. This puts the video CD in a position to become accepted just as rapidly as the CD-DA (audio CD).

Today there are so many CD standards that it is difficult to see the wood for the trees. These standards are, therefore, briefly discussed below.

#### Red Book, CD-DA

The standard for digital audio, **CD-DA**, may be found in the Red Book, which contains all technical specifications concerning registration and error correction pertaining to the CD. The Red Book has become the basis for later CD standards and developments, which were once beyond the specs laid down in the Red Book

because of high technical demands on the CD.

The information on a CD consists of a spiral-shaped string of holes pressed into a transparent polycarbonate layer. Next, a reflecting aluminium layer is applied which is covered with a transparent protection layer. The space between two holes is called an island. A laser beam scans the spiral from centre of the disc. Because the recording device in the laser drive unit is capable of detecting whether the light is reflected by a hole or an island, it is possible to recover the information pressed on the CD. Variations in the intensity of the reflected light are used to focus the laser via a complex servo system.

The spiral on the CD is divided into three sections: the lead-in, the program (data) and the lead-out. To make the best possible use of the space on the CD, the spiral is scanned at a constant speed. The CD's rotation speed is therefore dependent on the position of the laser. In the program section, the rotation speed can vary between 197 and 539 revolutions per minute. Because a mechanical speed control alone does not enable a constant data flow, the player has a buffer memory which has to be half filled all the time. If less than 50% of the available space is used, the drive speed is increased. If more than 50% is used, the speed is lowered accordingly. The data read by the laser is clocked out of the buffer with the aid of a quartz-controlled oscillator. The buffer/clock system guarantees a perfectly stable datastream into the DAC which follows the CD drive unit.

All data on an audio CD represents sound signals which have been sampled at a frequency of 44.1 KHz. Each sound channel is linearly digitized at a resolution of 16 bits. The result is a datastream with a speed of 1.4112 Mbit per second.

#### Yellow Book, CD-ROM

The next standard to appear on the market was defined in the Yellow Book, again produced jointly by Philips and Sony. Once the enormous storage capacity of CDs was fully recognized, the idea of a **CD-ROM** was born. The CD-ROM is marketed as the replacement for magnetic media such as floppy disks and hard disks. It has a number of advantages and disadvantages. The advantages include low cost, large storage capacity, non-volatile character, and reliability. On the down side, a CD-ROM is a read-only medium.

To maintain compatibility with the

CD-DA, the CD-ROM also contains one long spiral. This is in stark contrast with the long-established system of parallel tracks on magnetic media. Because the CD-ROM is also read at constant speed, it has a fairly large random read access time. Any time a file has to be read, the motor speed has to be adjusted until the right reading speed is achieved, and that takes time. Furthermore, the data transfer speed offered by the CD-ROM is relatively low at about 150 KByte per second. Fortunately, double, triple and quadruple speed CD-ROM drives have arrived, and we may see further improvements in the near future.

The information in the Yellow Book does not go much further than a description of the idea to store computer information in the program section. Further, it indicates the types of error correction methods which can be added to the system. The Yellow Book contains neither descriptions of the structure of files and directories as used with computers, nor information on how audio-visual (multimedia) information is to be stored. Consequently, the ISO-9660 and CD-ROM-XA standards were introduced later.

The ISO-9660 standard was initially developed by the High Sierra Group, and taken over by the ISO in 1988. It describes the file structure used with IBMcompatible PCs, and has become the basis for later standards. The UNIX platform uses the RRIP (Rock Ridge Interchange Protocol), while Apple Macintosh users have the HFS (Hierarchical File System) for their CD-ROMs.

#### Green Book, CD-i

In 1986, less than a year after the introduction of the CD-ROM, the CD Interactive (CD-i) was announced as a multi-media system for the consumer market. The complete system description may be found in the Green Book. Multimedia systems which process audio-visual information are an interesting application area of the CD-ROM. As already mentioned in the description of the CD-DA, audio information is recorded at a speed of 1.4112 MBit/s. Because video information is far more complex than audio information, the amount of data required for digital video will be even greater. Both with audio and video, there is an interaction between the necessary datastream and the quality of the encoded signal. The CD-i specification describes lots of possibilities for the recording of multi-media information such as sound, still-video, animations and video. Moreover, the information is stored in an interleaved pattern, which means that, for instance, audio and video are interwoven in blocks. That allows the CD-i player to read several types of information simultaneously.

The essential difference between CD-i

Fig. 1. The CD-DA (audio CD) was the first CD for a big audience. This Philips CD player was a market hit during the early nineteen-eighties.

and CD-ROM is that the specifications of the former include a complete description of the hardware which is necessary to be able to use the CD-i software. The Green Book also provides information on the structure of the data pressed on a CD-i disc. A marked difference with the Yellow Book, which has nothing on data storage formats.

Chapter 9 of the Green Book describes how MPEG1 full-screen video encoded according to ISO 11172 may be added to CD-i information. This system is called 'digital video on CD-i' and has been added to the CD-i system as an option.

17

#### CD-ROM XA

**CD-ROM XA** (eXtended Architecture) denotes an extension of the CD-ROM standard drawn up to make the medium better suited to multi-media applications. Broadly speaking, the XA standard enables a number of CD-i compatible audio and video formats to be used with CD-ROM also. Furthermore, it intro-

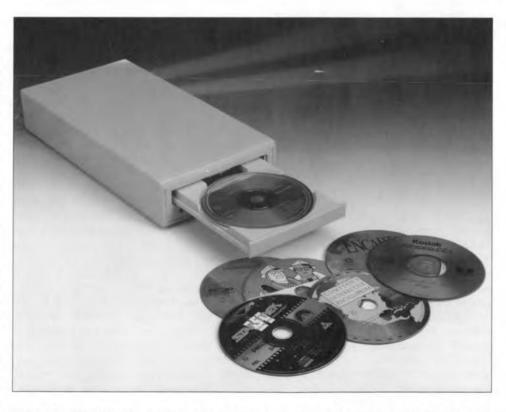

Fig. 2. The CD-ROM drive is on the way to becoming just another standard peripheral in computer land.

#### GENERAL INTEREST

duces the possibility of different start directories, which enables you to run a CD under different operating systems. Finally, the CD-ROM-XA standard, like the CD-i, is structurally compatible with the ISO-9660 standard. That makes the CD-ROM-XA suitable for many different computer systems. This type of disc is, however, unsuitable for CD-i players because they often lack the appropriate programs. Despite the fact that the XA standard has been with us for some time, little software has become available so far which utilizes this standard.

#### Sector structure

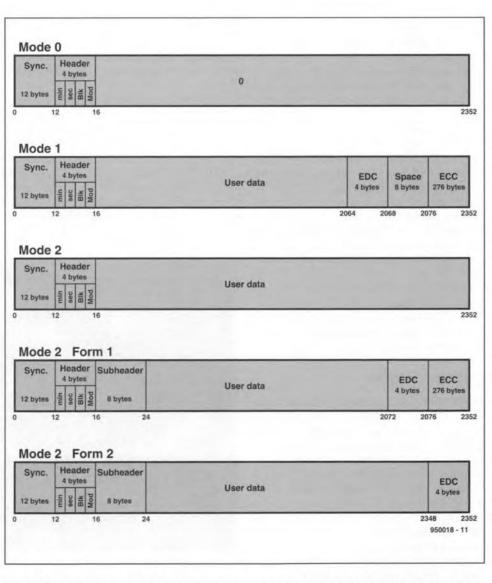

According to the definitions in the Yellow Book, sectors on a CD have a length of 2,352 bytes, and are subdivided into a number of fields to make them accessible to computers. The start of a sector is indicated by a synchronization pattern of 12 bytes. This is followed by a 4-byte header which contains its absolute address in minutes, seconds and sectors, as well as a mode byte. That leaves 2,336 bytes available for data storage in each sector.

All sectors in one track use the same mode. Sectors exist in three different modes. In Mode-0 sectors, all remaining 2,336 bytes are empty, i.e., zero. Mode-1 sectors contain 2,048 bytes of user data, protected by an EDC (error-detecting code) and an ECC (error-correcting code). This error protection is additional to the protection already used for CDs. Although the standard error correction for CDs is application independent, it is not powerful enough for computer applications. This is because small data errors are unacceptable in computer systems, although they may go by unnoticed in audio systems.

In Mode-2, which is the format used for normal CD-ROMs that do not require extra error correction (for instance, digiaudio/video), the remaining tized 2,336 bytes are available to hold data. The structure of Mode-2 sectors is further detailed in the Green Book to ensure compatibility with the ISO-9660 standard. The extension with Mode-2 is used with CD-i and CD-ROM-XA. It involves the storage of data in sectors by assigning a sub-header to each sector. This subheader contains a file and channel number coding information for details on the type of data contained in the sector, as well as a sub-mode byte. The file number is used to distinguish between sectors of different, interleaved, files. The channel number is used to support the different channels a file may be composed of. The sub-mode byte contains the end-of-file (EOF) and end-of-record (EOR) bits, an interrupt trigger bit to enable synchronization, and a real-time bit which indicates that the file is used in real time mode.

Finally, three bits follow which indi-

| Table 1.        |               |                |              |

|-----------------|---------------|----------------|--------------|

| Standard        | standard book | system holder  | introduction |

| CD-DA           | Red Book      | Philips, Sony  | 1982         |

| CD-ROM          | Yellow Book   | Philips, Sony  | 1985         |

| CD-i            | Green Book    | Philips, Sony  | 1987         |

| CD-ROM XA       |               | Philips, Sony  | 1989         |

| CD-ROM MO/CD-WO | Orange Book   | Philips, Sony  | 1990         |

| CD-Bridge       |               | Philips, Sony  | 1991         |

| Photo CD        |               | Kodak, Philips | 1992         |

| Video CD        | White Book    | JVC, Philips   | 1994         |

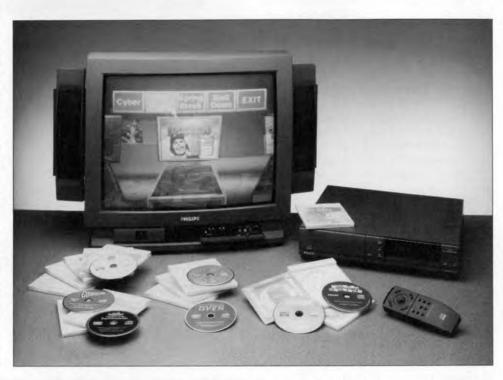

Fig. 3. A CD-i player is compatible with many different CD formats.

cate the type of data (video, audio, computer, etc.) in the sector. This extension has two options: mode-2/form-1 and mode-2/form-2, where the form bit indicates whether or not the additional error correction used in Mode-1 sectors is employed. Mode-2/form-1 sectors do have this extra error correction (EDC and ECC), while mode-2/form-2 sectors have an EDC block only. The absence of extra error correction is justified if the CD contains audio or video information. With these file types, the absence of the realtime bits (even occasionally) is much more important than small data errors. Because the extra error correction is not used, 280 bytes are available for data storage. With a real-time file stored in a mode-2/form-1 sector, the error detection and correction operations have to be performed in real time also, which makes high demands on the relevant hardware.

The eight space bytes in a Mode-1 sector are usually zero, and used for the header in Mode-2. Consequently, the locations for the data and the EDC fields are moved by eight bytes. A mode-2/form-2 sector is closed off by a 4-byte EDC field only, which may contain parity bits which serve as quality indicators in the CD production process. These bytes may also be made zero. If they are used, it is recommended to employ the same EDC as with mode-2/form-1 sectors.

#### Orange Book, CD-MO and CD-WO

The Compact Disc Magneto-Optical (**CD-MO**) and Compact Disc Write Once (**CD-WO**) are specified in the Orange Book. This extension has given the CD an even wider application area, because it specifies how CDs may be produced in small quantities.

The CD-MO enables the information on a CD to be re-written several times. By contrast, the CD-WO system allows data to be written once only. The CD-MO has a magneto-optical layer in which the

#### information is stored in a completely different manner than with a normal CD. The read section of the laser recognizes a CD-MO disc from a change in the polarization direction of the laser light. A special drive unit is required for the reading and writing of this type of CD.

A CD-WO, *a.k.a.* CD Recordable (CD-R) has three status levels: it is either blank, partly written on, or completely written on. Like the CD-MO, the CD-WO contains a special pre-recorded track with information required for tracking and timing. The CD-WO contains a light absorbing layer of which the reflection characteristics are modified with a special laser during recording. A CD-WO enables CD's to be 'burnt' which are compatible with the Red, Yellow and Green Book. These discs can be played on any conventional CD player or CD-ROM drive.

The CD-WO standard also supports the use of multiple partitions on a single CD ('multi-session'). Each of these partitions has its own lead-in, program and lead-out sections, and is compatible with the standards in the Red, Green or Yellow Book. Such a multi-session CD can only be read by a special multi-session drive. An ordinary CD-ROM drive can only read the data in the first session.

#### CD-Bridge

The **CD-Bridge** standard was developed to bridge the CD-i and CD-ROM standards. It is a very open standard with plenty of room for the implementation of the various system specifications. A CD-Bridge disc is a CD-ROM-XA disc which also contains a CD-i program. Consequently, this type of disc may be used in a computer as well as in a CD-ROM-XA drive. The popular photo-CD and Video-CD are examples of CD-Bridge discs.

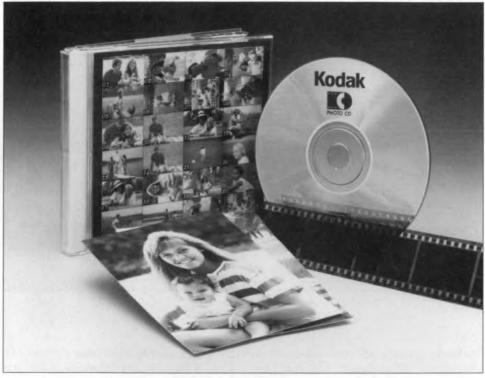

#### Photo-CD

The **Photo-CD** is a CD-Bridge disc of which the standard was designed by Philips and Kodak. This type of CD is intended for the storage of photographs which have been digitized at a very high solution, and so allows you to view photographs on your TV or computer screen. The relevant file may be processed further on the PC, or printed on paper.

A Photo-CD may be an ordinary CD, produced with conventional means, or a CD-WO. The latter format allows photos to be added to the CD during further sessions. Obviously, pre-recorded Photo-CDs have one session only, and can be read by all types of CD-ROM.

The standard version of the Photo-CD is based on 35-mm photographic negatives which are digitized at a resolution of 3782 x 2048 pixels. The file recorded on the CD consists of five sub-files: Base/16, Base/4, Base, 4xBase and

#### ELEKTOR ELECTRONICS MARCH 1995

Table 2.

Compatibility between disk format and player.

| Disk           |       |        | player/syste | em   |          |          |

|----------------|-------|--------|--------------|------|----------|----------|

|                | CD-DA | CD-ROM | CD-ROM-XA    | CD-i | Photo CD | Video CD |

| CD-DA          | х     | x      | x            | ×    | ×        | x        |

| CD-ROM         | -     | x      | ×            | -    | -        | -        |

| CD-ROM XA      | -     | -      | x            | -    | -        | 4        |

| CD-i           | -     | -      | -            | x    | -        | -        |

| CD-Bridge      | -     | -      | x            | x    | -        | -        |

| Photo CD       | -     | -      | x            | ×    | ×        |          |

| Video CD       |       | •      | ×            | ×    | -        | x        |

| x = compatible |       |        |              |      |          |          |

| - = not compa  | tible |        |              |      |          |          |

16xBase. Thanks to data compression techniques, an ordinary CD can hold more than 100 digitized 35-mm photographs. These days it is also possible to put larger film formats onto a Photo-CD. This is particularly interesting for professional users of photographic material.

19

Fig. 4. The data structure on a CD-ROM is strongly dependent on the application. This drawing shows the sector structure of the CD-ROM, CD-ROM-XA and Cd-i formats.

Fig. 5. The Photo-CD format was designed Kodak and Philips. It allows over 100 35-mm negatives to be stored on a single CD without loss of quality.

> Standards, an Introductory Overview, by Jan Korst and Verus Pronk, Philips Research Laboratory, Eindhoven, The Netherlands.

(950018)

#### White Book, Video-CD

The last CD-Bridge variant discussed in this article is the Video-CD. This was developed for the storage of full-motion, full-screen, video, as already described in Chapter 9 of the Green Book (CD-i). The pictures on the CD are encoded to the MPEG-1 standard. A normal 12-cm diameter CD has storage capacity for 74 minutes of digital video. The technical specifications of the Video-CD are described in the White Book. Initially, this version was also known as the Karaoke-CD standard.

To further the acceptance of this medium, the standard explicitly describes the possibility of adding full-motion video decoder to a conventional audio CD player. As a matter of course, that is only possible if the player is modified accordingly.

#### Other formats

CD-Video, not to be confused with Video-CD, is a CD format which has been in use for some time to record five to six minutes of analogue video on a CD. This format is described as an extension in the Red Book. In addition to the video information, the CD has spare capacity for about 20 minutes of digital audio. After a few false starts, this format soon went into oblivion. Today, it is hardly produced any more.

The CD Background Music (CD-BGM) format was developed for background music ('Muzak') systems, and is based on technologies derived from the

CD-i standard. By virtue of the ADPCM encoding used, a single CD can hold up to 20 hours of background music at reasonable quality.

CD+MIDI and CD+G were also developed on the basis of the audio CD. These formats enable graphics and MIDI data to be put on a CD, together with digital audio.

The last format to be mentioned is called CD-i Ready. With these audio CDs, an amount of CD-i software is stored in the background. When the CD

#### drive. Use the information in Table 2 to check for yourself which standards are actually required for your particular applications, and then select a player which supports at least those standards. Source: Compact Disc

Fig. 6. The Video-CD is expected to take a large market share away from the pre-recorded video tape. Computer users, too, can use this CD format to load and display digitized photos with the aid of an MPEG insertion card.

is played on an audio CD player, this extra functionality is not noticed because the disc behaves just like any other music CD. The CD-i software comes to life once the disc is inserted in a CD-I player. Additional functions which are then available include song texts, photographs, discographies, etc. To make sure that the CD-i information does not interfere with the music reproduction, the CD-i player first reads its own information, and stores it in a buffer. Next, the associated audio track is played.

A plethora of CD standards is currently in use, and the overall situation is complex enough to look pretty bewildering at first glance. As a general tip, formulate your requirements before you go out and purchase a CD player or a CD-ROM

#### Finale

**DIGITAL SIGNAL PROCESSORS**

#### By L. Lemmens

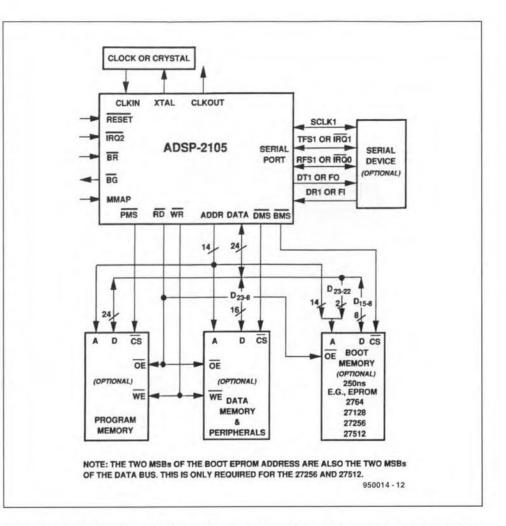

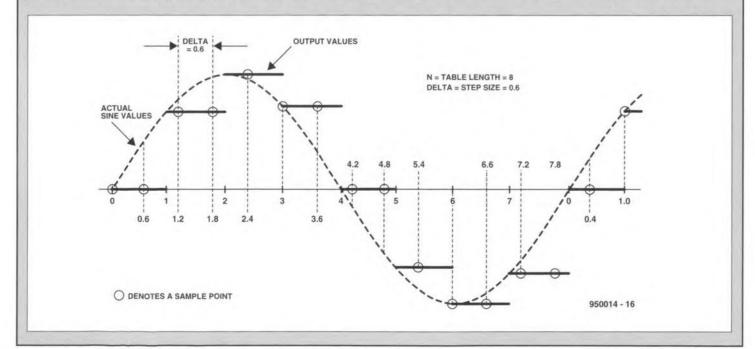

This article is intended as a brief introduction to digital signal processors (DSPs) and what makes them different from traditional processors and microcontrollers. The description is based on the ADSP-2100 family from Analog Devices, which includes the ADSP-2105 used in the DSP function generator described elsewhere in this issue.

The fundamental theory of DSP is Shannon's Sampling Theorem (1949) which states how often a time-varying signal is to be monitored if it is to be reconstructed exactly from its digital samples. It can be simply stated as follows:

In order to recover the signal function f(t) exactly, it is necessary to sample f(t) at a rate greater than twice its highest frequency component.

For instance, an audio signal whose highest frequency is 18 kHz should be sampled at 36 kHz to preserve and recover its waveform exactly.

Sampling a signal at a rate below its highest frequency component results in a phenomenon called *aliasing*. This results in a frequency erroneously taking on the identity of an entirely different frequency when recovered.

#### Multi-functionality

In spite of their name, digital signal processors are intended to process analogue signals. However, since they are digital devices, the signal must first be passed through a analogue-to-digital converter. After the signal has been processed, a digital-to-analogue converter (DAC) is needed in many applications. The two conversions are not normally carried outby the DSP but by external devices.

When analogue signals are digitized, their waveform is translated into a digital number at set intervals. The consequent series of numbers is passed through a digital filter (or filters) and their frequency spectrum is then determined by a Discrete Fourier Transform (DFT) or a Fast Fourier Transform (FFT). The power spectrum determination lies at the heart of a range of DSP operations, from speech recognition to the analysis of seismic data.

The mathematics underlying the sampling theory and the Fourier transform are too complex to be discussed in an article of this nature, but can be found in many textbooks. However, in practice, the processes come down to the computation of a series of products. Such a computation consists of (a) fetching two numbers from the memory; (b) multiplying the numbers; (c) accumulating the result; (d) storing the result in memory.

Apart from the fact that standard processors do not possess a multiplication facility, they would need many cycles to perform one such operation. Digital signal processors can perform several actions in parallel during one cycle and can even do so in real time.

A typical DSP in the ADSP-2100 family operates at 12.5 MHz and executes an instruction in a single 80 ns cycle. Since all instructions are carried out in a single cycle, MIPS (Million Instructions Per Second)= MHz. Its flexible architecture and comprehensive instruction set make possible a number of parallel operations. In one cycle, the ADSP-2100 can

- generate the next program address;

- fetch the next instruction;

- performone or two data moves;

- updata one or two data address pointers;

· perform a computational operation.

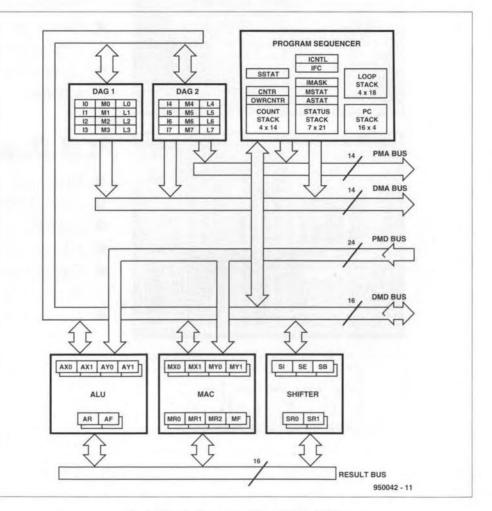

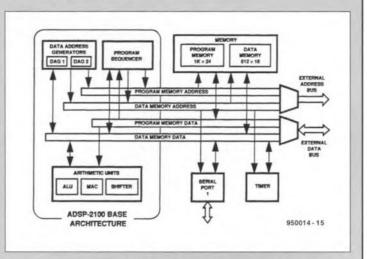

#### Architecture

**Figure 1** is an overall block diagram of the ADSP-2105. The processor contains three independent computational units: the arithmetic logic unit (ALU), the multiplier/accumulator (MAC) and the Shifter. These units process 16-bit data directly and have provisions to support multiprecision computations.

The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported.

The MAC performs single-cycle multiplication, multiplication/addition and multiplication/subtraction operations.

The Shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations. The Shifter can be used to implement efficiently any degree of numeric formal control, up to and including full floating point representations.

Fig. 1. Block diagram of the ADSP-2105.

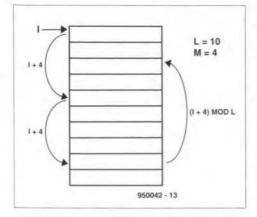

#### Fig. 2. When a register is scanned and an overflow occurs, the pointer is placed modulo L at the beginning of the register.

The computational units are arranged side by side instead of serially for flexible operation sequencing. The internal result (R) bus interconnects the units, so that the output of any one of them may be the input of any unit on the next cycle.

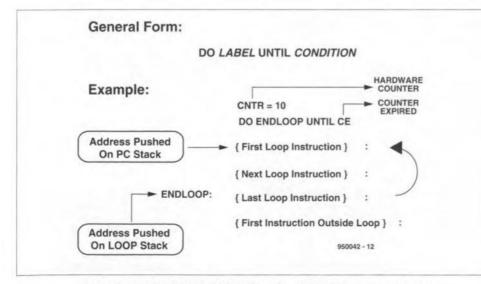

A powerful program sequencer and two dedicated data address generators ensure efficient use of these computational units. The program sequencer generates the next instruction address. To minimize overhead cycles, the seuqnecer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the DSP executes looped code with zero overhead; no explicit jump instructions are required to maintain the loop.

The data address generators (DAGs) handle address pointer updates. Each DAG keeps track of up to four address pointers. Whenever the pointer is used to access external data (indirect addressing), it is modified by a prespecified value. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers. With two independent DAGs, the processor can generate two addresses simultaneously for dual operand fetches.

Efficient data transfer is achieved with the use of five internal buses:

- Program Memory Address (PMA) bus;

- Program Memory Data (PMD) bus;

- · Data Memory Address (DMA) bus;

- Data Mmeory Data (DMD) bus;

- Result (R) bus.

The program memory (PMA, PMD) buses and data memory (DMA, DMD) buses extend off-chip to provide direct connections to external memories.

The DMD bus is the primary bus for routeing data internally and to and from external data memory.

The 14-bit DMA bus provides direct addressing of 16k×16 of external memory. Although the primary function of the program memory is for storing instructions, it can also store data. In this case, the PMD bus provides a path for routeing data to and from program memory, permitting dual operand fetches.

The 14-bit PMA bus provides direct addressing of 16k×24 of external memory, expandable to 32k×24 by using the program memory data access (PMDA) signal as the 15th address line.

The data address generators provide indirect addressing for data stored in external memories. The processor contains two independent DAGs so that two data operands (one in program memory and one in data memory) can be addressed simultaneously.

The two generators are identical except that DAG1 has a bit reversal option on the output and can only generate data memory addresses, while DAG2 can generate both program and data memory address, but has no bit reversal capability.

There are three register files in each DAG: the modify (MO register file, the indirect (I) register file, and the length (L) register file. Each of these register files contains four 14-bit register which are readable and loadable from the DMD bus. The

Fig. 2. Example of a DO–UNTIL loop in a DSP. The processor has a discrete loop counter.

I registers hold the actual addresses used to access external memory.

25

When the indirect addressing mode is used, the selected I register content is driven on to either the PMA or DMA bus. This value is post-modified by adding the content of the selected M register. The modified address is passed through the modulus logic.

Associated with each I register is an L register which may contain the length of the buffer addressed by the I register. In case of an overflow, the pointer is placed modulo L at the beginning of the register see **Fig. 2**. The L register and the modulus logic together enable circular buffer addressing, which is used, for example, in the DSP Function Generator described elsewhere in this issue for Direct Digital Synthesis DDS).

The modulus logic is disabled by setting the length of the associated buffer to zero.

The program sequencer incorporates powerful and flexible mechanisms for program flow control, such as zero-overhead looping, single-cycle branching (both conditional and unconditional) and automatic interrupt processing.

The sequencing logic controls the flow of the program execution. It outputs a program memory address on to the PMA bus from one of four sources: the PC incrementer, PC stack, instruction register or interrupt controller. The next address source selector controls which of these four sources are selected based on the current instruction word and the processor status. A fifth possible source for the next program memory address is provided by DAG2 when a register indirect jump is executed.

The loop counter is used for DO-UNTIL loops (see **Fig. 3**); there is thus no variable that needs to be checked bh the program, but a register that is automatically decreased and signals when the end condition (CNTR=0) is reached.

When a data fetch from program memory is required, an extra memory cycle is automatically appended to enable the next instruction fetch. To avoid this extra cycle, the device has an internal instruction cache (16 instructions deep) which serves an an alternate source for the next instruction. The cache monitor circuit transparently determines when the cache contents are valid. When the next instruction is in the cache, no extra cycle is necessary.

[950042]

Although the information in this article is based on information from their Data Sheets, Analog Devices disclaim all responsibility for its use or any infringements of patents or other rights of third parties which may result from its use.

Analog Devices, One Technology Way, PO Box 9106, Norwood, MA 02062-9106, USA. Telephone +1 617 329 4700. Fax +1 710 394 6577. **APPLICATION NOTE**

The content of this article is based on information obtained from manufacturers in the electrical and electronics industries, and does not imply practical experience by *Elektor Electronics* or its consultants.

### LMD18245 3A, 55V DMOS FULL-BRIDGE STEPPER MOTOR DRIVER

#### Source: National Semiconductor

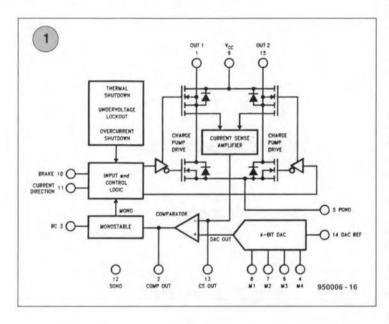

HE LMD18245 is a full-The LMD 102 to a mplifier which incorporates all the circuit blocks required to drive and control current in a brushed type d.c. motor, or one phase of a bipolar stepper motor. The multitechnology process used to build the device combines CMOS control and protection circuitry with DMOS power switches on the same monolithic structure. The LMD18245 controls the motor current via a fixed offtime chopper technique.

An all-DMOS H-bridge power stage delivers continuous output currents up to 3 A (6 A peak) at supply voltage up to 55 V. The DMOS power switches feature low  $R_{DS(on)}$  for high efficiency, and a diode intrinsic to the DMOS body structure eliminates the discrete diodes typically required to clamp bipolar power stages. An innovative current sensing method eliminates the power loss associated with a sense resistor in series with the motor. A four-bit digital-toanalogue converter (DAC) provides a digital path for controlling the motor current, and, by extension, simplifies implementation of full, half and microstep stepper motor drives. For higher resolution applications, an external DAC can be used. The block diagram of the LMD18245 is shown in **Fig. 1**.

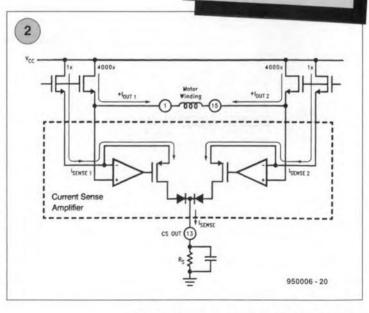

#### The current sense amplifier

Many transistor cells in parallel make up the DMOS power switches. The current sense amplifier (**Fig. 2**) uses a small fraction of the cells of both upper switches to provide a unique, low-loss means for sensing the load current. In practice, each upper switch functions as a  $1 \times$  sense device in parallel with a 4000× power device. The current amplifier forces the voltage at the source of the sense device to equal that at the source of the power device; thus, the devices share the total drain current in proportion to the 1:4000 cell ratio. Only the current flowing from drain to source, i.e., the forward current, registers at the output of the current sense amplifier. The latter therefore sources 250  $\mu$ A per ampère of total forward current conducted by the upper two switches of the power bridge.

The sense current develops a potential across R<sub>s</sub> that is proportional to the load current; for example, per ampère of load current. the sense current develops 1 V across a  $4-k\Omega$  resistor (the product of 250 µA per ampère and 4 k $\Omega$ ). Since chopping the load current occurs as the voltage at CS OUT surpasses the threshold (the DAC output voltage), Rs sets the gain of the chopper amplifier; for example, a  $2-k\Omega$  resistor sets the gain at 2 A of load current per volt of the threshold (i.e., the reciprocal

### FEATURES

- » DMOS power stage rated at 55V and 3A continuous

- » Low R<sub>DS(on)</sub> of typically

- 0.3Ω per power switch

- » Internal clamp diodes

- » Low-loss current sensing method

- » Digital or analogue control of motor current

- » TTL and CMOS compatible inputs

» Thermal shutdown

- (outputs off) at Tj=155°C

- » Overcurrent protection

» No shoot-through currents

- » 15-lead TO-220 moulded power package

### APPLICATIONS

- » Full, half and microstep stepper motor drives

- » Stepper motor and brushed d.c. motor servo drives

- » Automated factory, medical and office equipment

of the product of 250 µA per A and 2 k $\Omega$ ). The specified operating voltage at the CS OUT pin is 0 to 5 V.

#### The digital-to-analogue converter (DAC)

The DAC sets the threshold for chopping at  $V_{DAC REF} \times$ D/16, where D is the decimal equivalent (0-15) of the binary number applied at the DAC inputs, M4 through M1. M4 is the most-significant bit (MSB). For applications that require higher resolution, an external DAC may be used to drive the DAC REF input. The specified operating voltage range at DAC REF is 0 to 5 V.

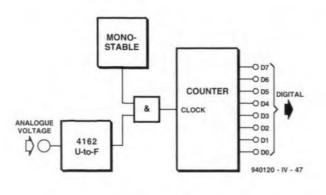

#### Comparator, monostable and winding current threshold for chopping

As the voltage at CS OUT surpasses that at the output bridge, so that the current the directions of the winding

of the DAC, the comparator triggers the monostable. This, once triggered, provides a timing pulse to the control logic. During the timing pulse, the power bridge shorts the motor winding, causing current in the winding to recirculate and decay slowly towards zero. A parallel RC network connected between RC (pin 3) and ground sets the timing pulse, or off-time, to about 1.1RC seconds.

Chopping of the winding current occurs as the voltage at CS OUT exceeds that at the output of the DAC; so chopping occurs at a winding current threshold of about

$(V_{DAC REF} \times D/16) \div [(250 \times$  $10^{-6}$ ) × Rs] ampères.

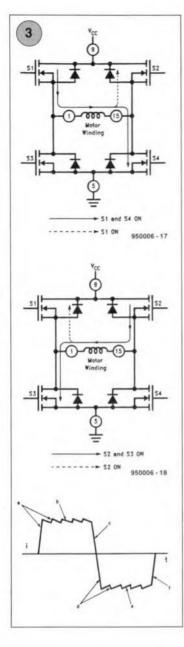

Apart from processing the MMV signal, the control logic also interprets the levels applied to the DIREC-TION and BRAKE inputs of the IC. The H-bridge is capable of assuming different configurations, as illustrated in Fig. 3. Turning ON a source switch and a sink switch in opposite halves of the bridge forces the full supply voltage less the switch drops across the motor winding (a). While the bridge remains in this state, the winding current increases exponentially towards a limit dictated by the supply voltage, the switch drops, and the winding resistance. Subsequently turning OFF the sink switch causes a voltage transient that forward biases the body diode of the other source switch. The diode clamps the transient at one diode drop above the supply voltage, and provides an alternative current path. While the bridge remains in this state, it essentially shorts the winding, and the winding current recirculates and decays exponentially towards zero (b). This process is repeated until the DIRECTION signal changes. Both the switches and the body diodes then provide a decay path for the initial winding current, which rapidly drops to zero (c). Next, the control logic re-configures the H-

current waveshape is then described by (d), (e) and (f) in the lower drawing.

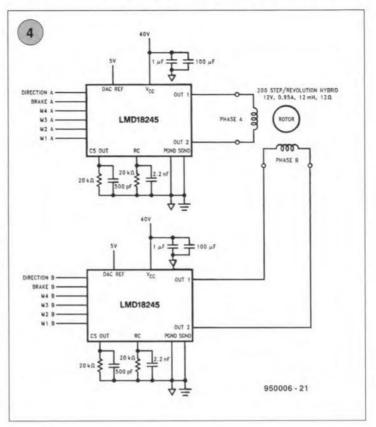

#### Modes of operation

A typical application of two LMD18245s driving a stepper motor is shown in Fig. 4. The chopper off-time is set to about 48 µs by the 20-k $\Omega$  resistor and 2.2-nF capacitor connected between RC and ground. The chopper gain is set to about 200 mA per volt of the threshold by the 20 $k\Omega$  resistor at the CS OUT pin. Digital signals supplied by a microcontroller govern the thresholds for chopping,

flows through S2, the motor currents, and, by extension, winding and S3. The motor the drive type (full step, half step, etc.).

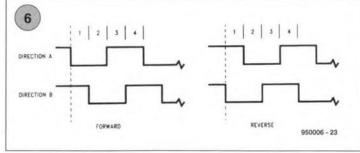

#### Full step drive

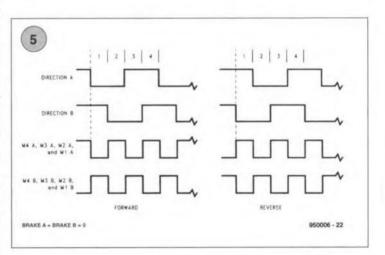

There are two types of full step drive. In one-phase drive (Fig. 5), the motor can be made to take full steps by energizing windings A and B in the sequence

```

A \rightarrow B \rightarrow A' \rightarrow B' \rightarrow A \rightarrow \dots

```

where A and B represent the currents in one direction through the respective windings, and A' and B', the reverse currents. The motor takes one full step each time one winding is de-energized and the other is energized. To make the motor reverse,

30

$A'B' \rightarrow B' \rightarrow AB' \rightarrow A \rightarrow \dots$

It is important to note that

although half stepping dou-

bles the step resolution,

changing the number of energized windings from two to

one decreases torque by

about 40%, resulting in significant torque ripple and

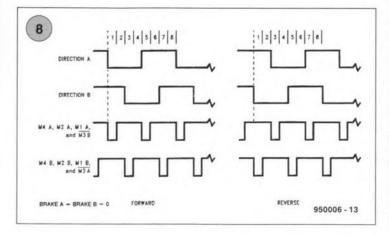

Half-step drive with torque

The above problem can be

solved by torque compensation (Fig. 8). Essentially, the

windings are then energized

with sinusoidal currents.

Controlling the winding cur-

rents in this fashion doubles

the step resolution without

the significant torque ripple

possibly noisy operation.

compensation

the above sequence must be  $A \rightarrow AB \rightarrow B \rightarrow A$ reversed. That is achieved by swapping the levels of the DIRECTION signals.

Two-phase drive (Fig. 6) also results in full steps, and is described by the sequence

$AB \rightarrow A'B \rightarrow A'B' \rightarrow AB' \rightarrow AB$ + ...

Because both windings are energized at all times, this sequence produces more torque than with one-phase drive. All DAC inputs are held permanently high.

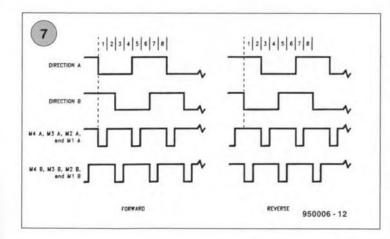

#### Half-step drive without torque compensation

To make the motor take half steps (Fig. 7), windings A and B can be energized in the sequence

| L                                | 0  | /e  | 180    | 1     | 15 | 0 |

|----------------------------------|----|-----|--------|-------|----|---|

|                                  | 11 | Sel | 225    | 0.707 | 11 | 0 |

| 950006 - 23                      |    | -   | 270    | 0     | 0  | 1 |

|                                  |    |     | 315    | 0.707 | 11 | 1 |

|                                  |    |     | REPEAT |       |    |   |

| $A'B \rightarrow A' \rightarrow$ |    |     |        |       |    |   |

orward

1

erse

0

45

90

135

100

Table 1. Lookup table for half-step drive with torque compensation. Note: 90° electrical/full step ÷ 2 microsteps/full step = 45° electrical/step.

DACA

15

11

0

11

15

cos a

1

0.707

0

0.707

DIR A

1

1

0

0

sin a

0

0.707

1

0.707

0

0.707

1

0.707

DAC B

0

11

15

11

0

11

15

11

DIR B

1

1

1

1

0

0

0

0

|    | α      | cos α | DAC A | DIR A | $\sin \alpha$ | DAC B | DIR B |

|----|--------|-------|-------|-------|---------------|-------|-------|

|    | 0      | 1     | 15    | 1     | 0             | 0     | 1     |

|    | 22.5   | 0.924 | 14    | 1     | 0.383         | 6     | 1     |

|    | 45     | 0.707 | 11    | 1     | 0.707         | 11    | 1     |

| 1  | 67.5   | 0.383 | 6     | 1     | 0.924         | 14    | 1     |

| DO | 90     | 0     | 0     | 0     | 1             | 15    | 1     |

|    | 112.5  | 0.383 | 6     | 0     | 0.924         | 14    | 1     |

| Ď  | 135    | 0.707 | 11    | 0     | 0.707         | 11    | 1     |

| -  | 157.5  | 0.924 | 14    | 0     | 0.383         | 6     | 1     |

| -  | 180    | 0     | 15    | 0     | 0             | 0     | 0     |

| ä  | 202.5  | 0.924 | 14    | 0     | 0.383         | 6     | 0     |

| ~  | 225    | 0.707 | 11    | 0     | 0.707         | 11    | 0     |

|    | 247.5  | 0.383 | 6     | 0     | 0.924         | 14    | 0     |

| L  | 270    | 0     | 0     | 1     | 1             | 15    | 0     |

|    | 292.5  | 0.383 | 6     | 1     | 0.924         | 14    | 0     |

|    | 315    | 0.707 | 11    | 1     | 0.707         | 11    | 0     |

|    | 337.5  | 0.924 | 14    | 1     | 0.383         | 6     | 0     |

|    | REPEAT |       |       |       |               |       |       |

Table 2. Winding currents and Lookup Table for guarter-step drive with torque compensation. Note: 90° electrical/full step ÷ 4 microsteps/full step = 22.5° electrical/microstep.

of the prior drive technique. Along with the obvious advantage of increased step resolution, this microstepping reduces both full-step oscillations and resonances that occur as the motor and load combination is driven at its natural resonant frequency, or subharmonics thereof. When compared to full step drive, microstepping makes the motor run quieter. smoother and Table 1 shows the phase angle,  $\alpha$ , and the associated cosine values for winding A, and sine values for winding B, for each of the eight different half steps (each full 360° cycle comprises of four full steps).

#### Quarter step drive with torque compensation

The quarter step drive mode only differs from the halfstep mode in respect of the resolution. A 360° cycle is divided into 16 steps. Four microsteps then equal one full step. The relevant control data is shown in Table 2. (950006)

#### Source:

LMD18245 data sheet. National Semiconductor.

#### LMD18245 Electrical Characteristics

The following specifications apply for  $V_{CC} = +42V$ , unless otherwise stated. Bold-face limits apply over the temperature range -40 °C  $\leq T_J \leq +125$  °C. All other limits apply for  $T_A = T_J = 25$  °C.

| ymbol           | Parameter                             |                     | Conditions                 | Min. | Тур.  | Max. | Unit    |

|-----------------|---------------------------------------|---------------------|----------------------------|------|-------|------|---------|

| cc              | Quiescent current                     |                     | DAC REF = 0V,              |      | 8     | 15   | mA      |

|                 |                                       |                     | V <sub>CC</sub> = +20V     |      |       |      |         |

| OWER            | OUTPUT STAGE                          |                     |                            |      |       |      |         |

|                 |                                       |                     |                            |      |       | 0.4  | Ω       |

|                 |                                       |                     | $I_{LOAD} = 3A$            |      | 0.3   | 0.6  | Ω       |

| RDS(on)         | Switch ON resistance                  |                     |                            |      |       | 0.4  | Ω       |

|                 |                                       |                     | $I_{LOAD} = 6 A$           |      | 0.3   | 0.6  | Ω       |

| DIODE           | Body Diode Forward Voltage            |                     | I <sub>DIODE</sub> = 3A    |      | 1.0   | 1.5  | V       |

| Γπ              | Diode Reverse Recovery Time           |                     | I <sub>DIODE</sub> = 1A    |      | 80    |      | ns      |

| Q <sub>rr</sub> | Diode Reverse Receovery Charge        |                     | I <sub>DIODE</sub> = 1A    |      | 40    |      | nC      |

|                 | Output Ture ON Delay Time             | Sourcing Outputs    | I <sub>LOAD</sub> = 3A     |      | 5     |      | μs      |

| D(ON)           | Output Turn ON Delay Time             | Sinking Outputs     | I <sub>LOAD</sub> = 3A     |      | 900   |      | ns      |

|                 | Output Turp OFF Delay Time            | Sourcing Outputs    | I <sub>LOAD</sub> = 3A     |      | 600   |      | ns      |

| D(OFF)          | Output Turn OFF Delay Time            | Sinking Outputs     | I <sub>LOAD</sub> = 3A     |      | 400   |      | ns      |

|                 | Output Turn ON Switching Time         | Sourcing Outputs    | I <sub>LOAD</sub> = 3A     |      | 40    |      | μs      |

| ON              | Output full ON Switching fille        | Sinking Outputs     | I <sub>LOAD</sub> = 3A     |      | 1     |      | μs      |

|                 | Output Turn OFF Switching Time        | Sourcing Outputs    | $I_{LOAD} = 3A$            |      | 200   |      | ns      |

| OFF             | Output Turn OFF Switching Time        | Sinking Outputs     | I <sub>LOAD</sub> = 3A     |      | 80    |      | ns      |

| pw              | Minimum Input Pulse Width             | pins 10 and 11      |                            |      | 2     |      | μs      |

| DB              | Minimum Dead Band                     |                     |                            |      | 40    |      | ns      |

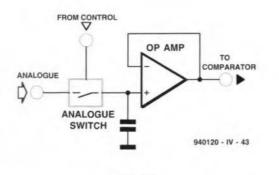

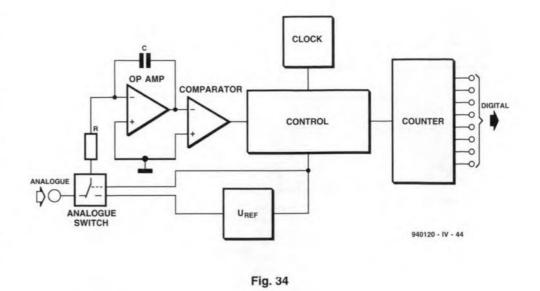

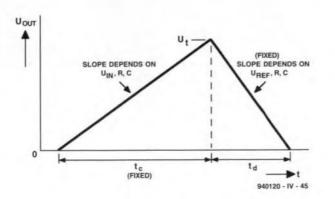

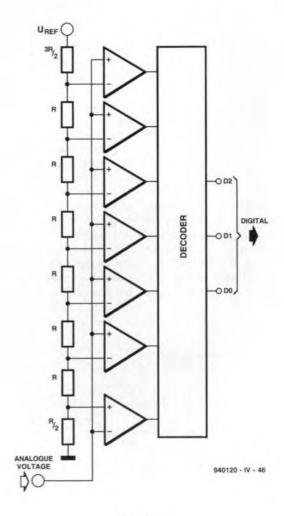

| CURREN          | IT SENSE AMPLIFIER                    |                     |                            |      |       | -    |         |