THE INTERNATIONAL ELECTRONICS MAGAZINE

### **BUMPER CHRISTMAS ISSUE** With over 50 construction projects

Medium power HEXFET amplifier

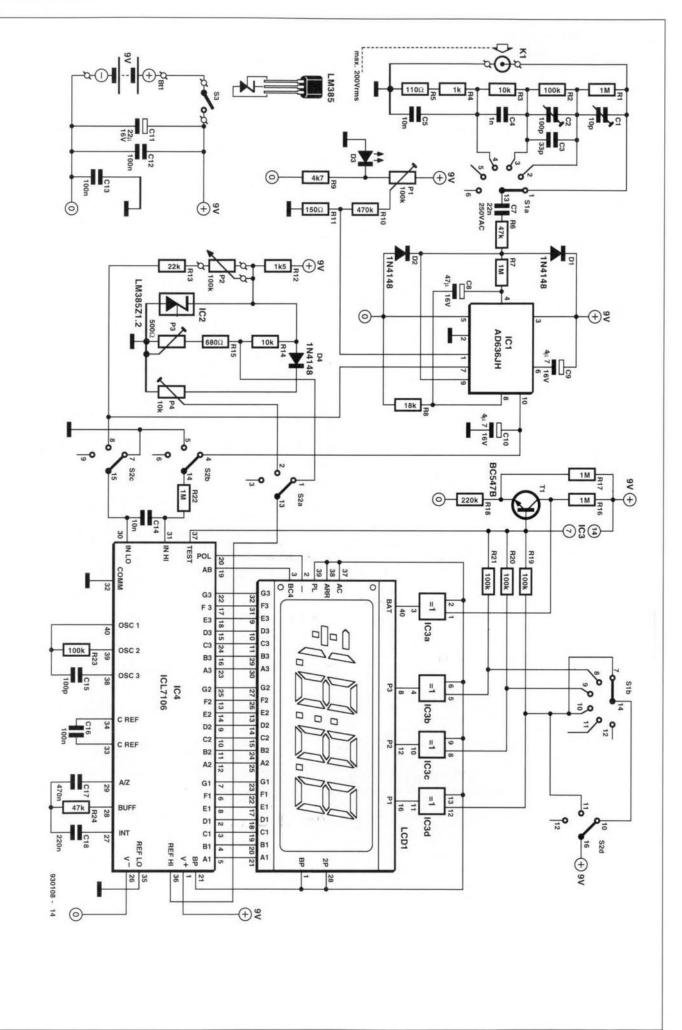

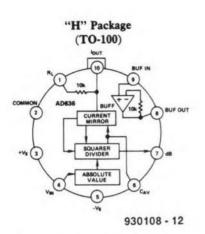

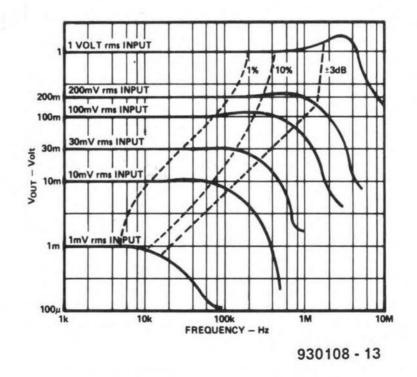

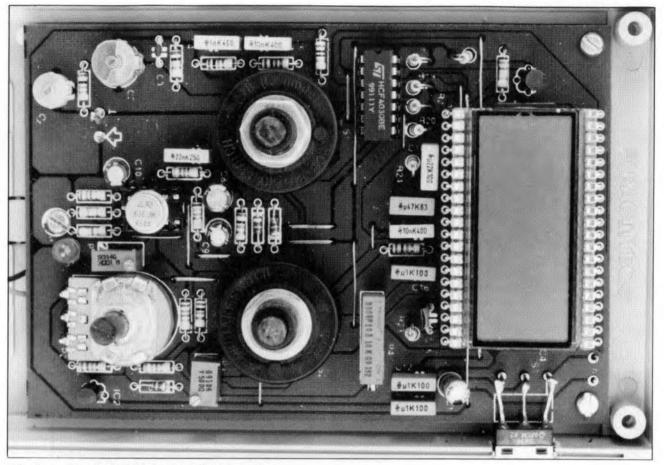

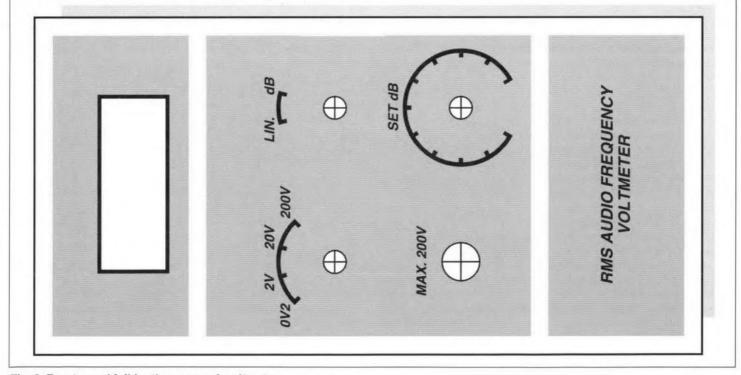

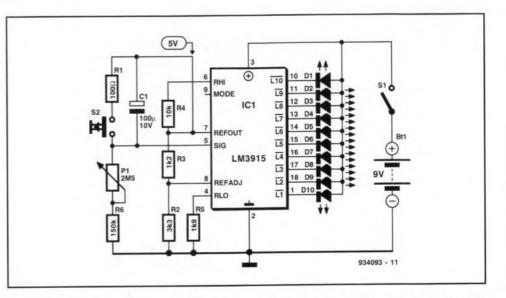

AF RMS Voltmeter

Choosing component values for LC resonant circuits

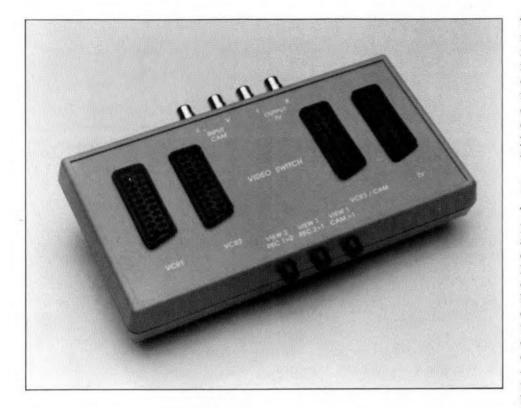

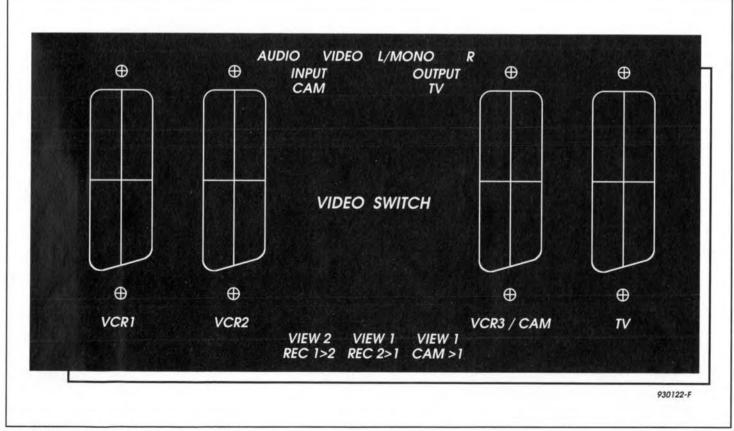

SCART switching box

## MEDIUM POWER HEXFET AMPLIFIER

### **Design by T. Giesberts**

In spite of their relatively modest TO220 case, the International Rectifier HEXFETs used in the present 60-watt output amplifier can cope with fairly large voltages and currents. The amplifier is absolutely symmetrical from input to output. Its mechanical design is such that it can be accommodated on a fairly small printed-circuit board, including the electrolytic capacitors of the power supply.

The design objective was to arrive at a not too complex unit that nevertheless offered excellent performance, was fairly simple to build and could be reproduced relatively easily. The result is a straightforward amplifier without any unnecessary gimmicks.

A bipolar transistor may be considered a current-amplifying device that enables a (relatively) large current to be controlled by a much smaller one. A field-effect transistor (FET) behaves differently: it is a sort of variable resistance whose conduction is controlled by a voltage. It follows that the drives of these devices is quite different: an important consideration in the design of an output amplifier. A bipolar transistor needs a base current before it can function, whereas a FET can be driven almost without any energy. All it needs is a control voltage; the current it draws is negligible. When power FETs first came on to the market, many designers thought that they would simplify the design of output amplifiers beyond belief. That quickly proved to be not so, however, because power FETs have a fairly large capacitance between the gate and the drain/source channel (sometimes of the order of a few nanofards). This means that at high audio frequencies the driver stages need to deliver fairly large transfer currents to keep the bandwidth sufficiently large.

It may well be asked what advantage(s) aFET offers. In a bipolar power transistor, it is difficult to combine high voltage, large current, and wide bandwidth, because its operation must remain within the Safe Operating Area—SOA. It is not enough to just look at the peak voltage and current in the relevant data sheet. By virtue of modern production techniques, FETs can be fabricated that can handle high voltages (100 V and more) and, in spite of their modest dimensions, large currents. It is, therefore, much simpler to design an output amplifier with reasonable power output with power FETS than with power transistors. Of course, there are other requirements as well, such as slew rate and matching of complementary semiconductors ...

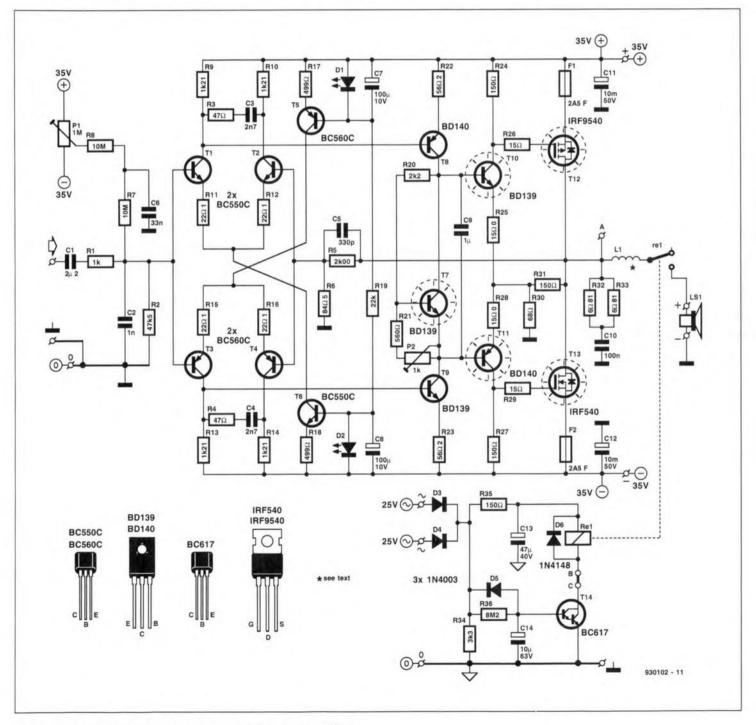

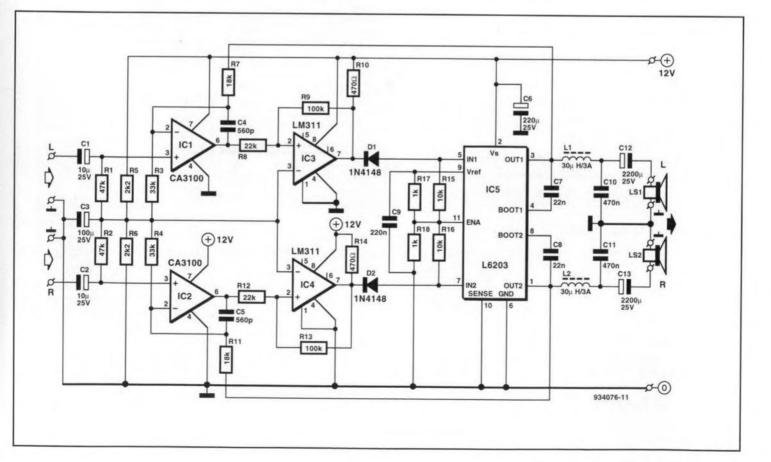

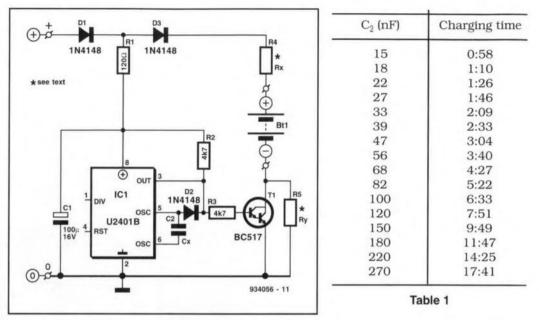

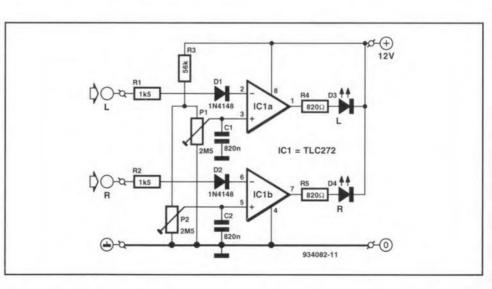

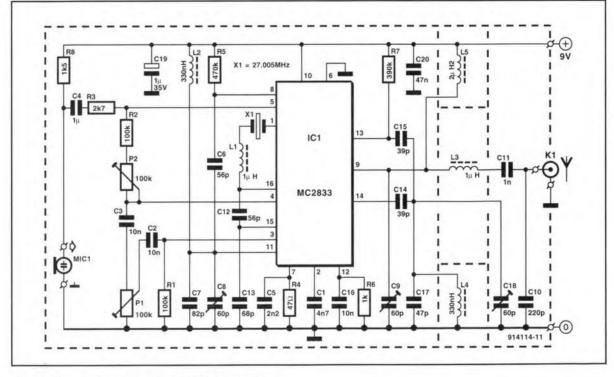

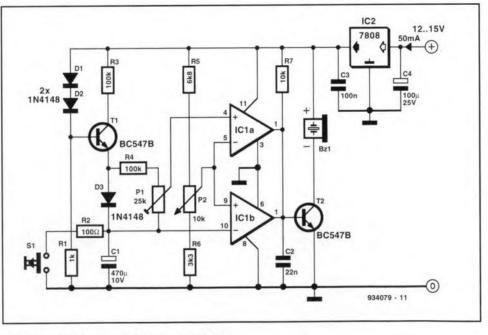

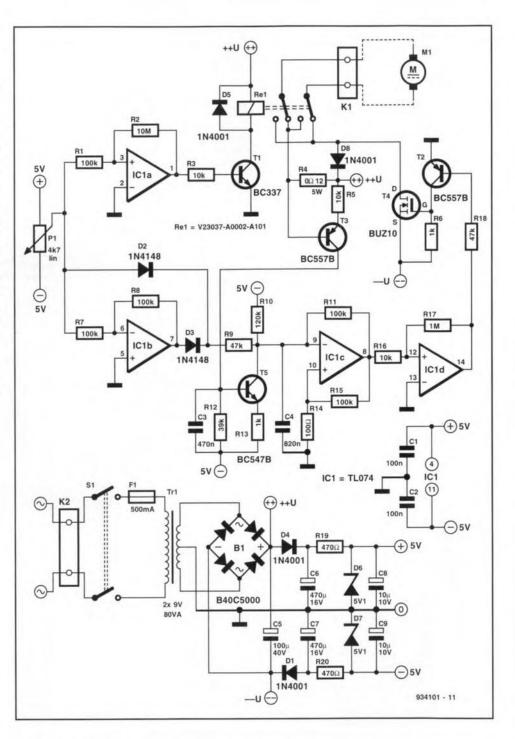

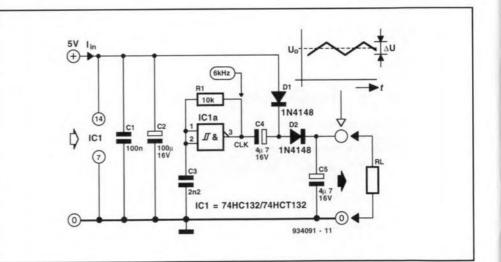

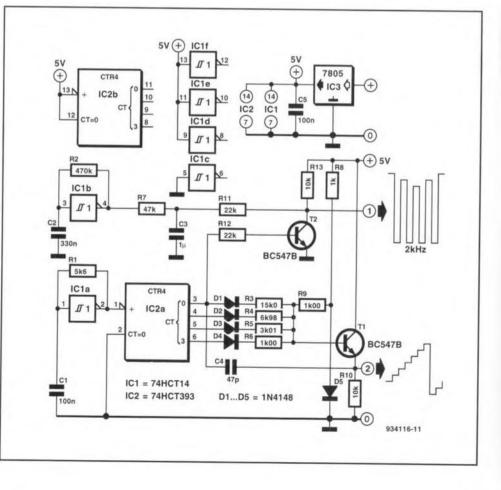

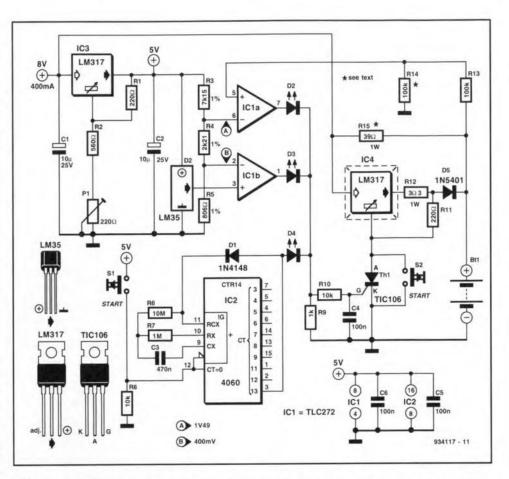

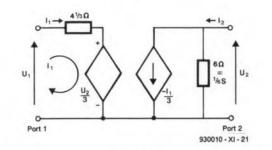

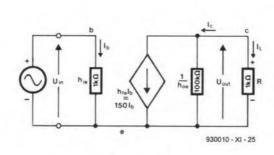

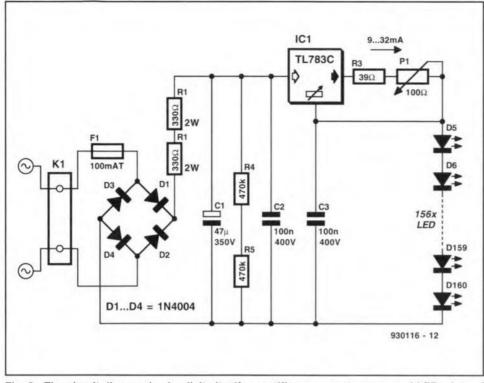

#### The circuit

A symmetrical design has the advantage that it minimizes problems with distortion, particularly that associated with even harmonics. Therefore, the input stages consist of two differential amplifiers,  $T_1$ - $T_2$  and  $T_3$ - $T_4$ . These use discrete transistors, not expensive dual devices, to keep the cost

#### Brief technical data

Input sensitivity Input impedance Power output (1 kHz, 0.1% THD) Music power (500 Hz burst, 5 cycles on 5 cycles off) Power bandwidth (35 W into  $8 \Omega$ ) Slew rate Signal-to-noise ratio (1 W into  $8 \Omega$ ) Harmonic distortion (1 W into  $8 \Omega$ )  $(60 \text{ W into } 8 \Omega)$ Intermodulation distortion (50 Hz: 7 kHz; 4:1) Dynamic intermodulation distortion rectangular 3.15 kHz + sine wave 15 kHz) Damping factor (at  $8 \Omega$ ) Supply voltage Quiescent current (T12 and T13)

down. Performance is excellent, particularly if the transistors are matched.

A differential amplifier is one of the best means of combining two electrical signals: here, the input signal and the feedback signal. The amplification of the stage is determined mainly by the ratio of the collector and emitter resistances (in the case of  $T_1$ - $T_2$  these are  $R_9$ ,  $R_{10}$ ,  $R_{11}$  and  $R_{12}$ ). These form a sort of local feedback: limiting the amplification reduces the distortion.

Two *RC* networks ( $R_3$ - $C_3$  and  $R_4$ - $C_4$ ) limit the bandwidth of the differential amplifiers and these determine, to a degree, the open-loop bandwidth of the entire amplifier (which is 6.5 kHz).

| l V r.m.s.                              |        |

|-----------------------------------------|--------|

| 48 kΩ                                   |        |

| 63 W into 8 Ω                           |        |

| $105 \text{ W}$ into $4 \Omega$         |        |

| 68 W into 8 Ω                           |        |

| 120 W into 4 $\Omega$                   |        |

| 1.5 Hz-125 kHz (+0 dB, -                | -3 dB) |

| 20 V µs <sup>-1</sup> (with input filte |        |

| >99 dB (A-weighted)                     |        |

| <0.006% (1 kHz)                         |        |

| <0.005% (1 kHz)                         |        |

| <0.05% (20 Hz-20 kHz)                   |        |

| <0.008% (35 W into 8 Ω)                 |        |

| <0.003% (35 W into 8 Ω)                 |        |

| >160 (20 Hz-20 kHz)                     |        |

| ±35 V                                   |        |

| 200 mA                                  |        |

The d.c. operating point of the differential amplifiers is provided by two current sources. Transistor  $T_6$ , in conjunction with  $R_{18}$  and  $D_2$ , provides a constant current of about 2 mA for  $T_1$ - $T_2$ . Transistor  $T_5$ , with  $R_{17}$  and  $D_1$ , provides a similar current for  $T_3$ - $T_4$ . The combination of a transistor and an LED creates a current source that is largely independent of temperature, since the temperature coefficients of the LED and the transistor are virtually the same. It is, however, necessary that these two components are thermally coupled (or nearly so) and they are, therefore, located side by side on the printed-circuit board.

In the input stage,  $C_1$  is followed by a low-pass section,  $R_1$ - $C_2$ , which limits the bandwidth of the input to a value that the amplifier can handle. Resistor  $R_2$  is the base resistor of  $T_1$  and  $T_3$ . So far, this is all

pretty normal. Network  $P_1$ - $R_7$ - $R_8$  is somewhat out of the ordinary, however. It forms an offset control to adjust the direct voltage at the output of the amplifier to zero. Such a control is normally found **after** the input stage. The advantage of putting it before that stage is that the inputs of the differential amplifiers are exactly at earth potential, which means that the noise contribution of their base resistors is negligible.

The signals at the collectors of  $T_1$  and  $T_3$  are fed to pre-drivers  $T_8$  and  $T_9$ . Between these transistors is a 'variable zener' formed by  $T_7$  which, in conjunction with  $P_2$ , serves to set the quiescent current of the output FETS.

The output of the pre-drivers is applied to  $T_{10}$  and  $T_{11}$ , which drive HEXFETS  $T_{12}$  and  $T_{13}$ . This power section has local feedback

#### (R<sub>30</sub>-R<sub>31</sub>).

The design of  $T_{10}$ – $T_{13}$  is a kind of compound output stage, since the drain of the power FETs is connected to the output terminal. Note that  $T_{12}$  is a p-channel FET and  $T_{13}$  an n-channel type. Therefore, the stage provides current amplification as well as voltage amplification. The voltage amplification is limited to ×3 by the local feedback resistors ( $R_{30}$ – $R_{31}$ ). Here again, this feedback serves to reduce the distortion. The overall feedback of the amplifier is provided by  $R_5$ -R-C<sub>5</sub>.

9

Fuses are provided in the source lines of the HEXFETS. Power FETS have an inherent current limitation by virtue of their positive temperature coefficient: when the device gets hot, its drain-source resistance rises and this reduces the current through it. The fuses and this property pro-

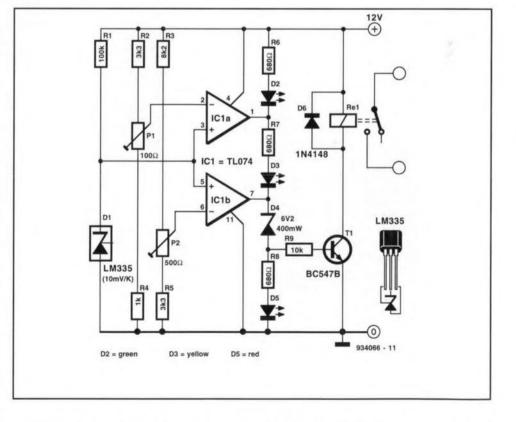

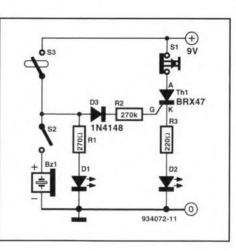

Fig. 1. Circuit diagram of the medium power HEXFET amplifier.

**ELEKTOR ELECTRONICS DECEMBER 1993**

#### AUDIO & HI-FI

10

vide adequate protection against brief short-circuits. Note that the HEXFETs used can handle peak currents of up to 75 A. Electrolytic capacitors  $C_{11}$  and  $C_{12}$  (10,000  $\mu F$  each and part of the power supply) are located close to the FETs, so that the heavy currents have only a short path to follow.

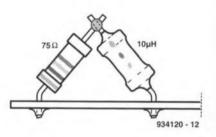

At the output is a Boucherot network,  $R_{32}$ - $R_{33}$ - $C_{10}$ , that ensures an adequate load on the amplifier at high frequencies, since the impedance of the loudspeaker, because of its inductive character, is fairly high at high frequencies.

$\label{eq:limits} Inductor\,L_l\,limits\,any\,current\,peaks\,that\\ may\,arise\,with\,capacitive\,loads.$

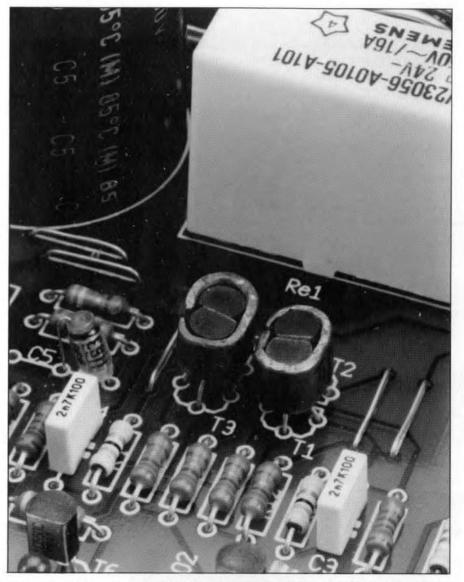

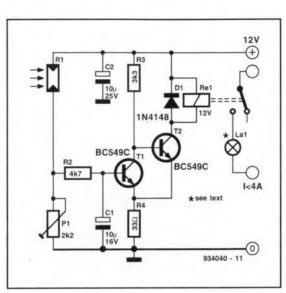

The signal is finally applied to the loudspeaker,  $LS_1$ , via relay contact  $Re_1$ . The relay is not energized for a few seconds after the power is switched on to obviate any plops from the loudspeaker. Such plops are caused by brief variations in the direct supply voltage arising in the short period that the amplifier needs to reach its correct operating level.

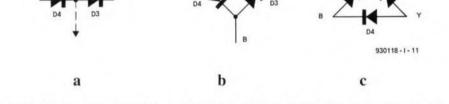

The supply voltage for the relay is derived directly from the mains transformer via  $D_3$  and  $D_4$ . This has the advantage that the relay is deactuated, by virtue of the low value of  $C_{13}$ , immediately the supply voltage fails. The delay in energizing the relay is provided by  $T_{14}$  in conjunction with  $R_{36}$  and  $C_{14}$ . It takes a few second before the potential across  $C_{14}$  has risen to a value at which  $T_{14}$  switches on. This darlington transistor requires a base voltage of not less than 1.2 V before it can conduct.

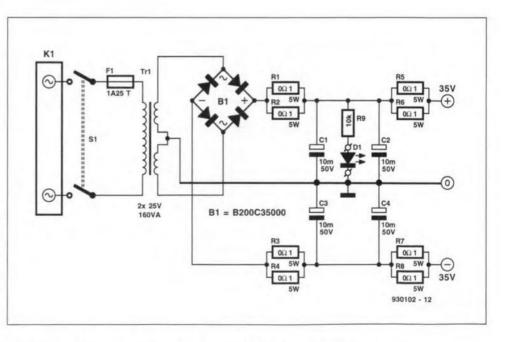

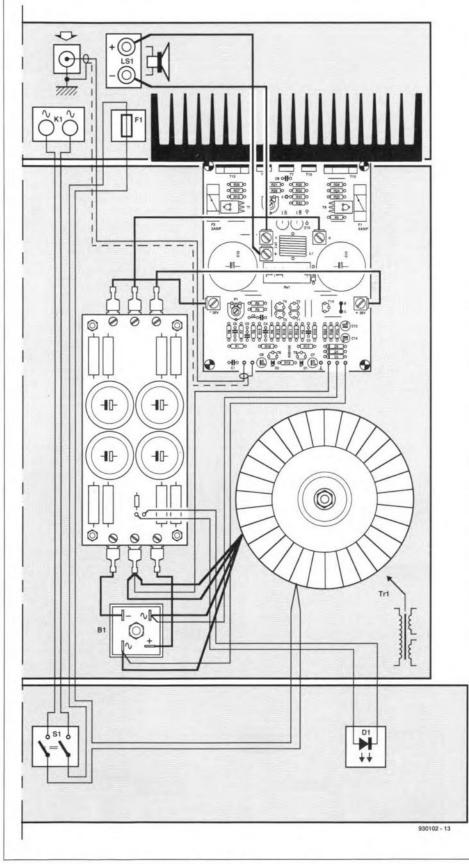

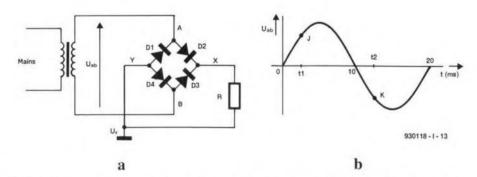

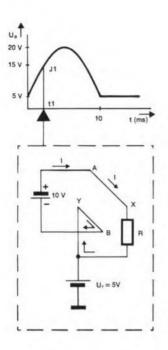

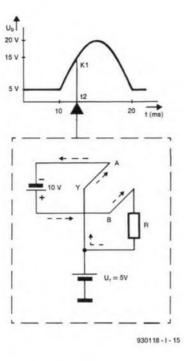

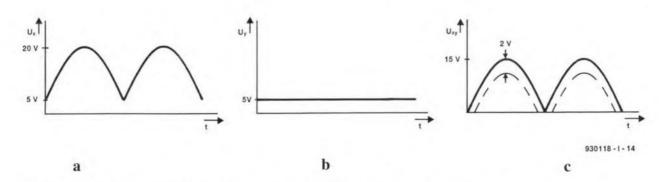

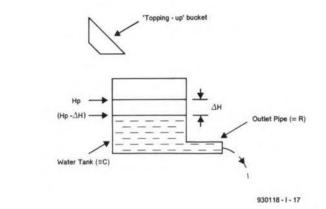

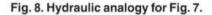

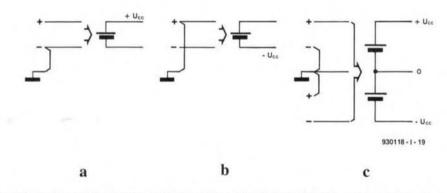

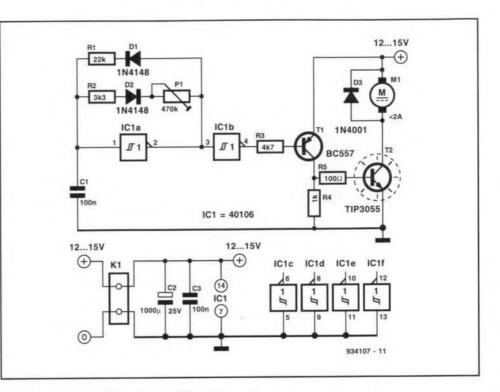

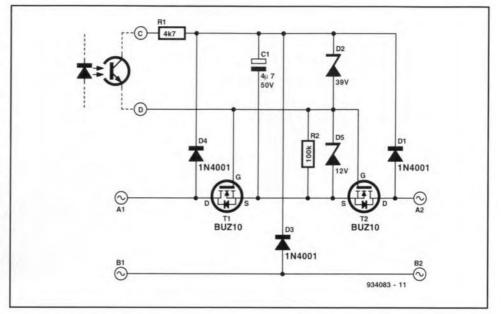

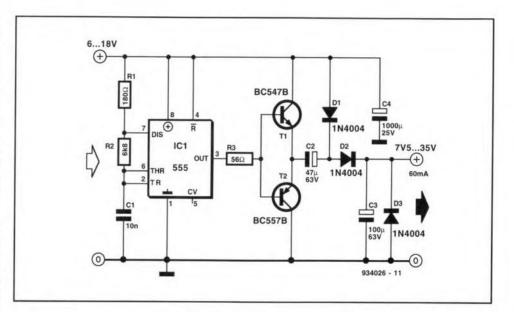

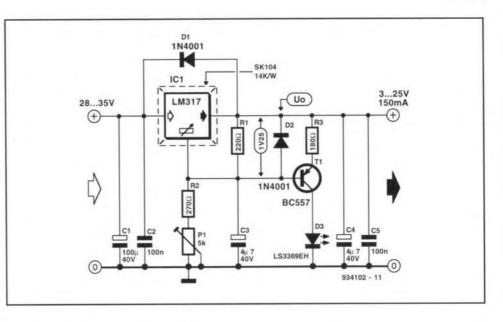

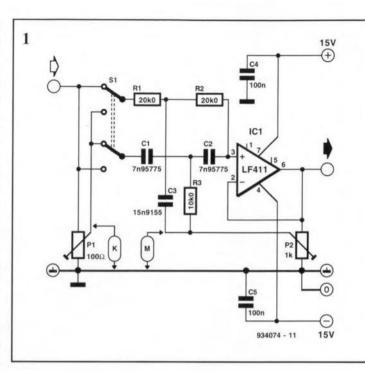

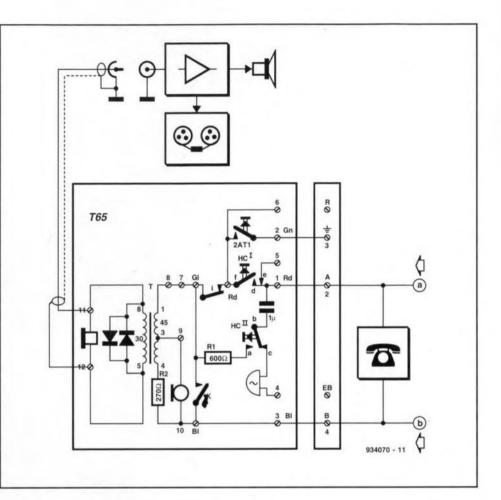

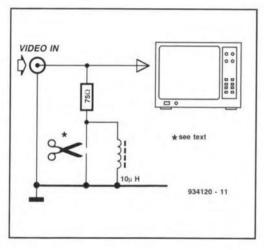

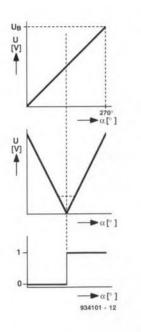

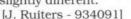

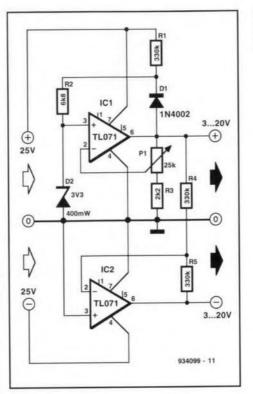

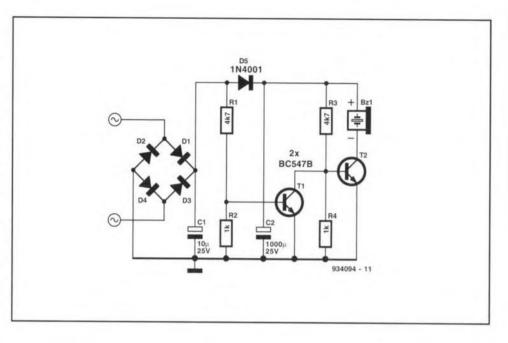

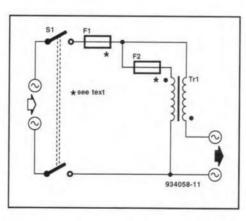

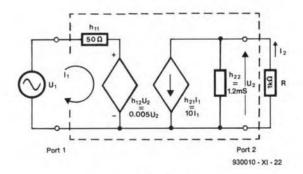

The power supply—see **Fig. 2**—is traditional, apart from the resistors,  $R_5-R_8$  in the power lines. These limit, to some degree, the very large peak charging currents to electrolytic capacitors  $C_{11}$  and  $C_{12}$ . Moreover, together with these capacitors, they form a filter that prevents most spurious voltages from reaching the amplifier. Measurements on the prototype showed that this was particularly evident at frequencies below 500 Hz.

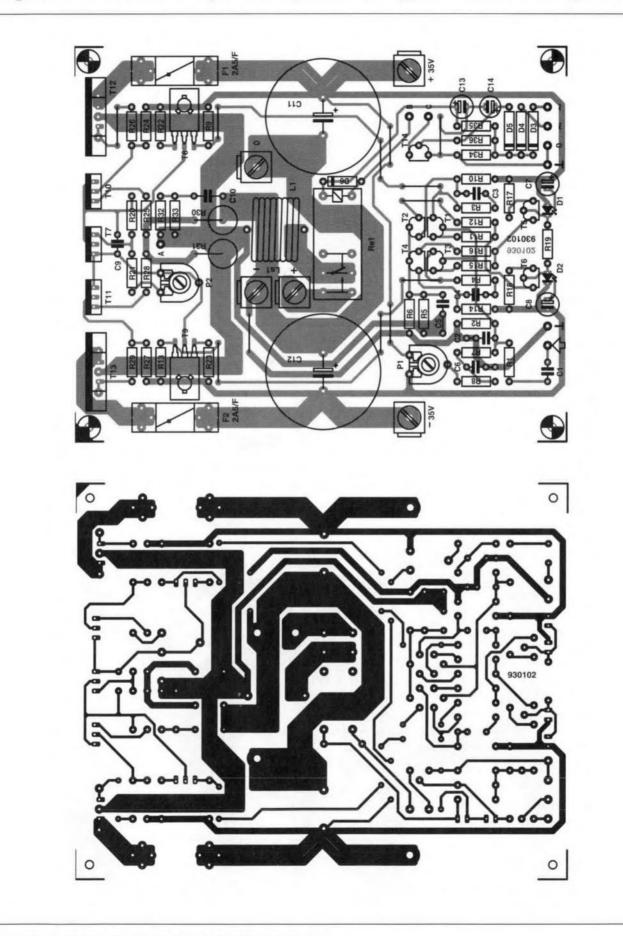

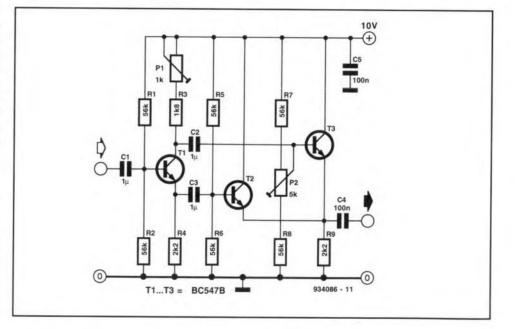

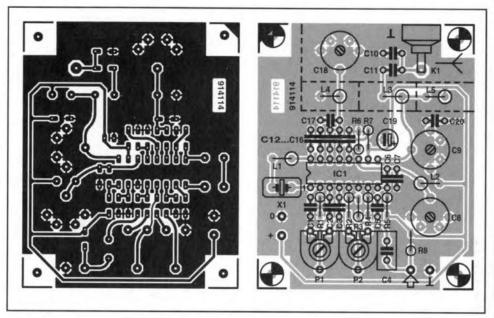

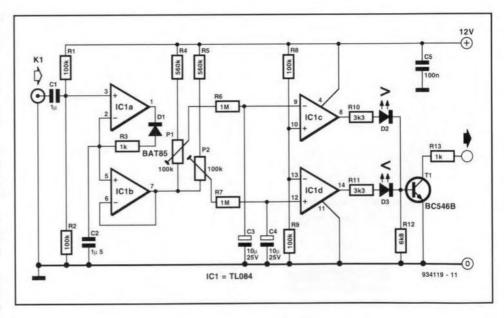

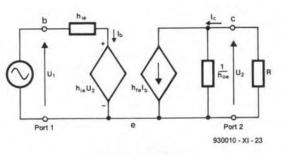

#### Construction

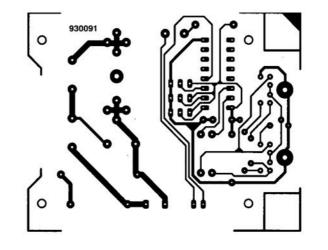

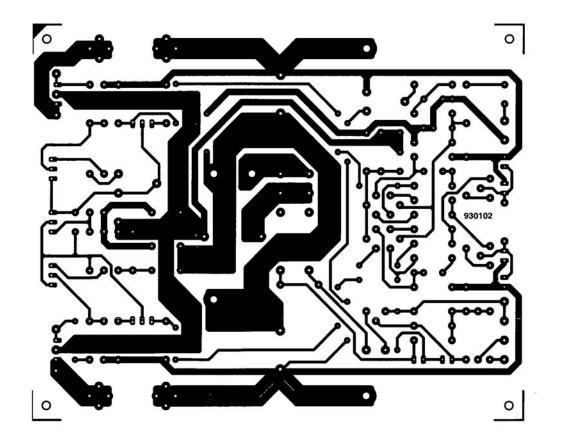

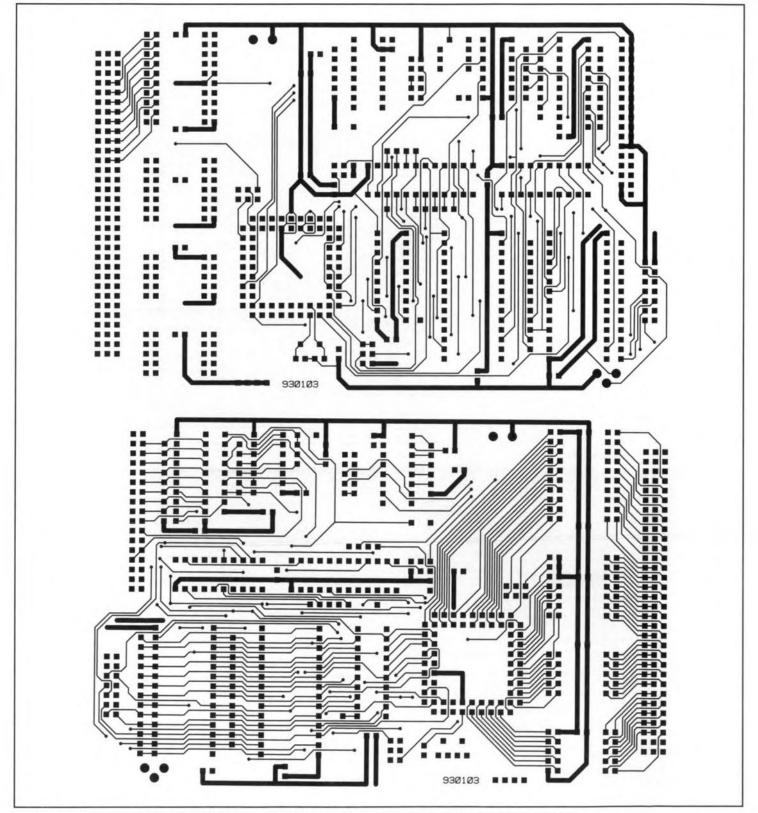

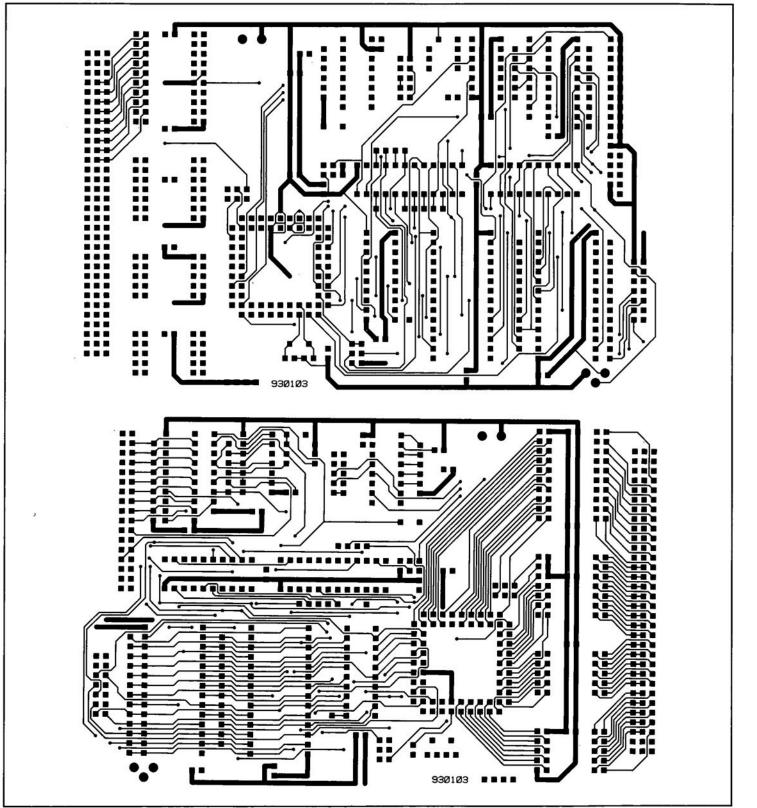

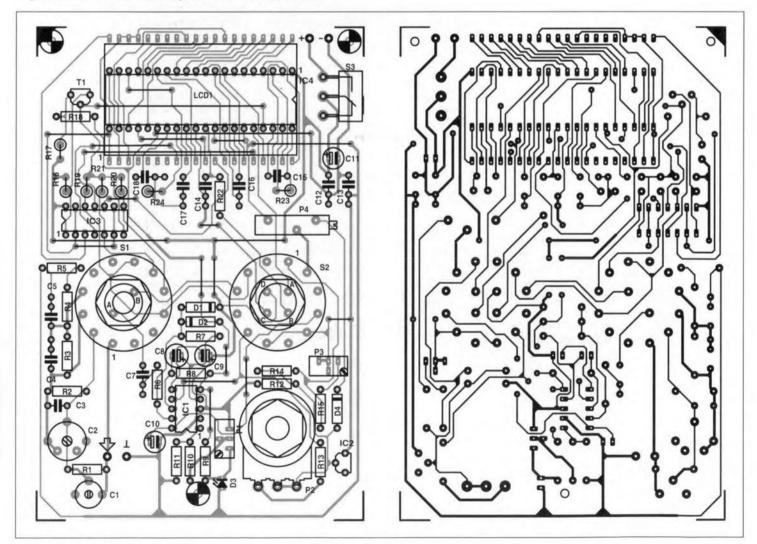

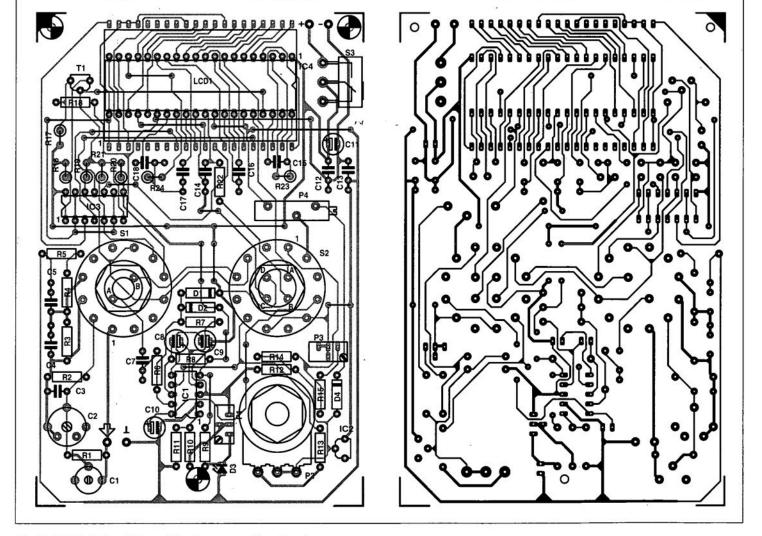

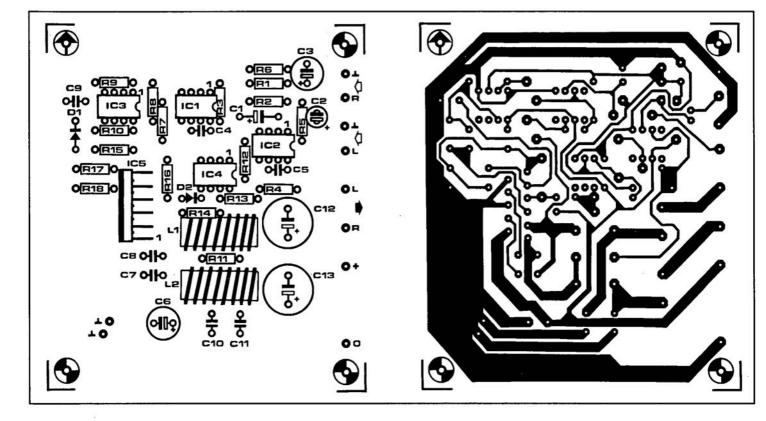

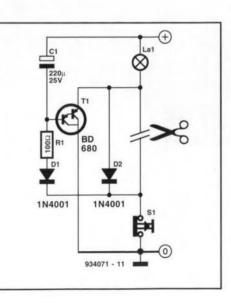

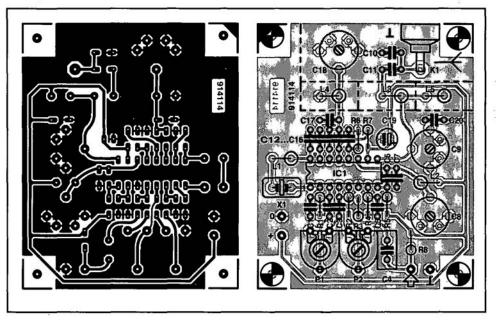

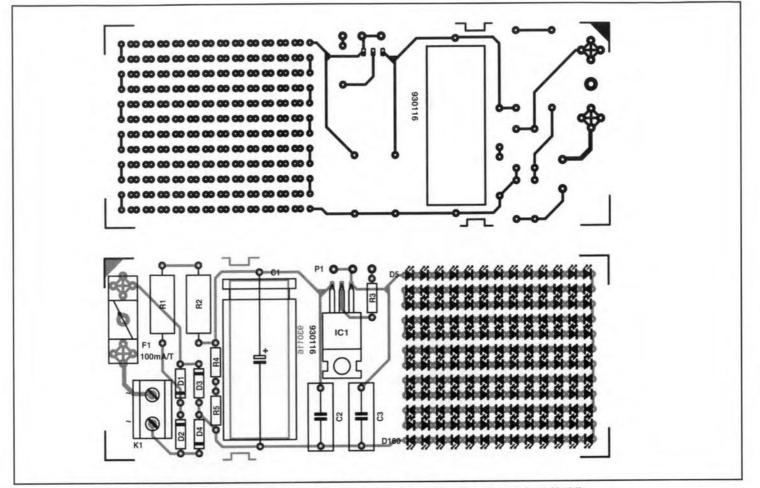

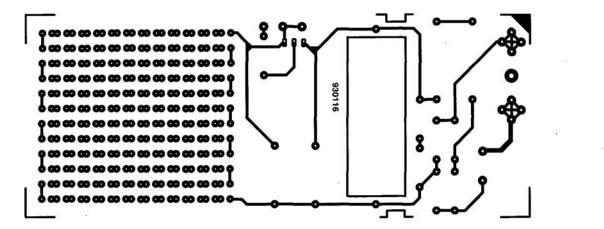

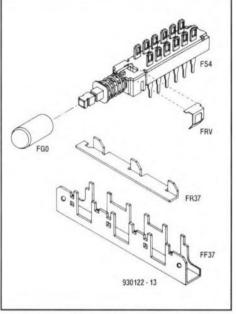

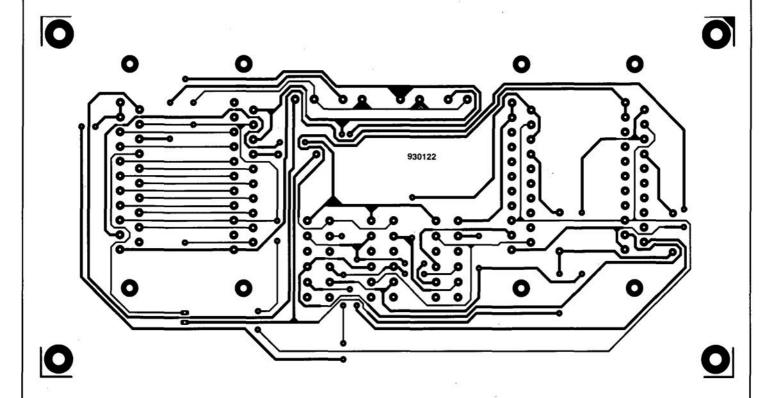

The design of the printed-circuit board for the amplifier (**Fig. 4**) takes good account of the large currents that flow in the amplifier. This has given rise to a couple of tracks being paralleled instead of combined, so that the effect of currents in the power section on the input stages is minimal.

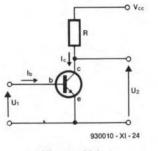

Populating the board is straightforward. Although not strictly necessary, it is advisable to match the transistors used in the differential amplifiers. This may be done conveniently on an  $h_{fe}$  tester by measuring the amplification at a collector current of about 1 mA. If such a tester is not available, use a base resistor that results in a collector current of about 1 mA measured with a multimeter. With the same resistor, test a number of other transistors and note the collector currents. Mount the selected pairs on the board and pack them closely together with a 5 mm wide

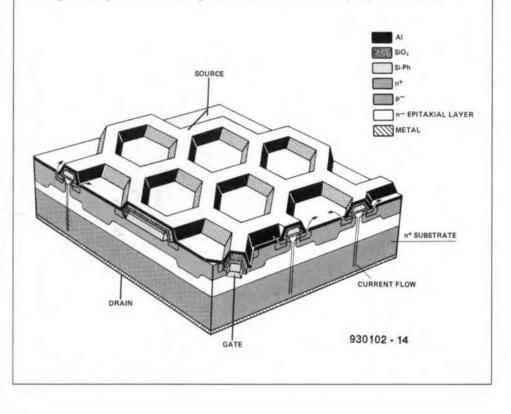

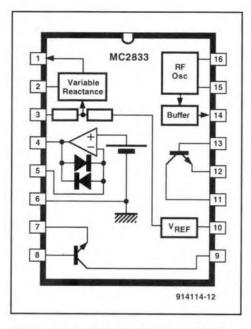

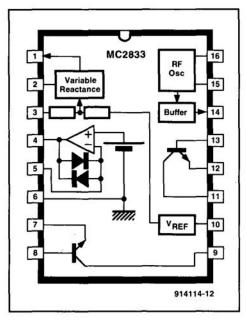

#### The HEXFET structure

As implied, the HEXFET structure involves an hexagonal device geometry. At the core is a radically new hexagonal, cellular structure as illustrated. It is this hexagonal geometry, along with advanced MOS processing, that gives the HEXFET an on-state resistance,  $R_{DSon}$ , one-third of that possible with the best previous MOSFET technology, in a given die size.

A planar, non-V-groove structure, the HEXFET conducts current vertically. For high packaging density, it uses a silicon-gate structure. The density of the hexagonal source cells on the top surface of the silicon die is over half a million cells per square inch. Electrons flow from a source cell through the channel which is around the periphery of that cell and then into the drain body. The bottom surface of the drain body is in electrical and thermal contact with the holder.

The efficient hexagonal source pattern, the silicon gate, and advanced MOS processing techniques combine to produce the HEXFET's unique performance.

Fig. 2. Circuit diagram of the power supply for the HEXFET amplifier.

copper ring (made from a piece of 12 mm copper water pipe) as shown in Fig. 5.

Inductor  $L_1$  consists of six turns, inner diameter 16 mm (5/8 in), of insulated copper wire 1.5 mm (1/16 in) thick.

The large transistors are located on one

side of the board, so that they can be fixed transistor at a later stage. directly to the heat sink. They must be insulated with the aid of ceramic washers.

The two sizes indicated on the board for  $T_{12}$  and  $T_{13}$  may be ignored: they are a precaution for possible different types of

Connections from the power supply and to the loudspeaker are by means of terminal blocks that can be screwed on to the board.

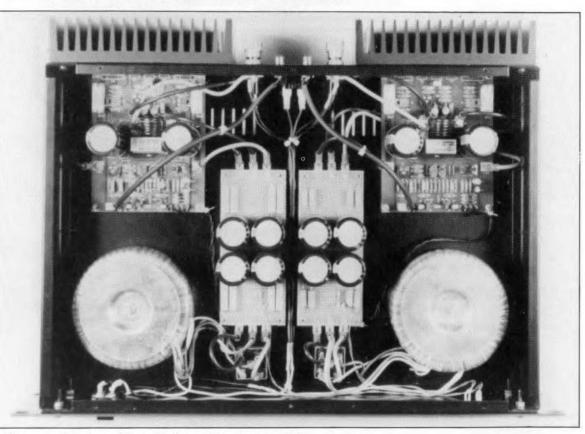

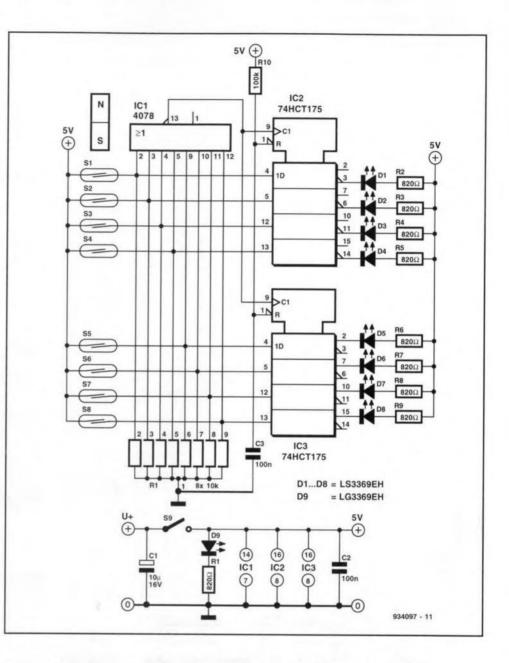

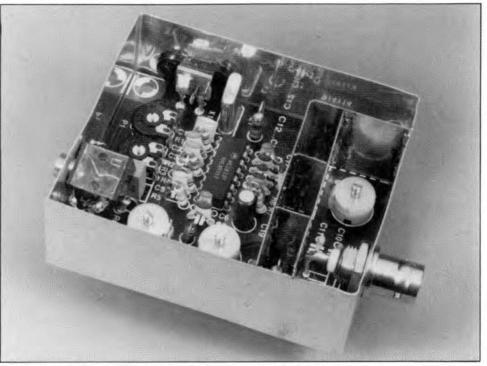

Mount the two amplifier boards, mains

Fig. 3. Printed-circuit board for the medium power HEXFET amplifier.

Fig. 4. The differential amplifiers are clamped together with a (DIY) copper ring.

transformers and electrolytic capacitors in a suitable enclosure. The wiring diagram for one channel is given in **Fig. 6**.

It is advisable to measure the supply voltages before they are connected to the amplifiers. Also, turn  $P_2$  to maximum (wiper towards  $R_{33}$ ) before connecting the power supply to the amplifiers. Set input presets  $P_1$  to the centre of their travel. A few seconds after the supply has been switched on, the relay should come on. Connect a multimeter (1 V direct voltage range) and adjust  $P_1$  until the meter reads zero (both channels!).

Switch the supply off again and insert a multimeter (1 A d.c. range) in one of the supply lines; **do not** substitute it for one of the fuses, since that would affect the operating point of the relevant power FET. Switch the supply on again, wait 5–10 minutes (when the current has stabilized) and adjust  $P_2$ for a meter reading of 330 mA. After about half an hour, the current will remain steady at about 230 mA. The quiescent current through the output transistors is then around 200 mA. Switch off the supply, remove the meter from the supply line and repeat the above procedure with the other channel.

Finally, recheck the direct voltages at the outputs of the amplifiers and, if necessary, readjust  $P_1$  slightly.

The loudspeakers must be 4-ohm or 8-ohm types, whose impedance must not drop below  $3\Omega$ . It is not permissible to connect two 4-ohm units in parallel to the amplifier, because that would give problems when large drive signals are applied to the FETS.

Fig. 5. Top view of the completed amplifier with the enclosure removed.

$\begin{array}{l} \label{eq:point} \textbf{Parts list} \ (\text{one channel}) \\ \textbf{Resistors:} \\ R_1 = 1 \ k\Omega \\ R_2 = 47.5 \ k\Omega, \ 1\% \\ R_3, \ R_4 = 47 \ \Omega \\ R_5 = 2.0 \ k\Omega, \ 1\% \\ R_6 = 84.5 \ \Omega, \ 1\% \\ R_7, \ R_8 = 10 \ M\Omega \\ R_9, \ R_{10}, \ R_{13}, \ R_{14} = 1.21 \ k\Omega, \ 1\% \end{array}$

$\begin{array}{l} R_{11},\,R_{12},\,R_{15},\,R_{16}=22.1\;\Omega,\,1\%\\ R_{17},\,R_{18}=499\;\Omega,\,1\%\\ R_{19}=22\;k\Omega\\ R_{20}=2.2\;k\Omega\\ R_{21}=560\;\Omega\\ R_{22},\,R_{23}=56.2\;\Omega,\,1\%\\ R_{24},\,R_{27}=150\;\Omega,\,1\%\\ R_{25},\,R_{28}=15.0\;\Omega,\,1\%\\ R_{26},\,R_{29}=15\;\Omega \end{array}$

MEDIUM POWER HEXFET AMPLIFIER

13

$\begin{array}{l} R_{30} = 68 \; \Omega, \; 5 \; W \\ R_{31} = 150 \; \Omega, \; 5 \; W \\ R_{32}, \; R_{33} = 6.81 \; \Omega, \; 0.6 \; W, \; 1\% \\ R_{34} = 3.3 \; k\Omega \\ R_{35} = 150 \; \Omega \\ R_{36} = 8.2 \; M\Omega \\ P_1 = 1 \; M\Omega \; preset \\ P_2 = 1 \; k\Omega \; preset \end{array}$

#### Capacitors:

$\begin{array}{l} C_1 = 2.2 \, \mu \mathrm{F}, 50 \, \mathrm{V}, \, \mathrm{MKT} \\ C_2 = 1 \, \mathrm{nF} \\ C_3, \, C_4 = 2.7 \, \mathrm{nF} \\ C_5 = 330 \, \mathrm{pF}, \, \mathrm{polystyrene}, \, \mathrm{axial} \\ C_6 = 33 \, \mathrm{nF} \\ C_7, \, C_8 = 100 \, \mu \mathrm{F}, \, 10 \, \mathrm{V}, \, \mathrm{radial} \\ C_9 = 1 \, \mu \mathrm{F} \\ C_{10} = 100 \, \mathrm{nF} \\ C_{10} = 100 \, \mathrm{nF} \\ C_{11}, \, C_{12} = 10,000 \, \mu \mathrm{F}, \, 50 \, \mathrm{V}, \, \mathrm{radial}, \, \mathrm{for} \, \mathrm{PCB} \\ \mathrm{mounting} \\ C_{13} = 47 \, \mu \mathrm{F}, \, 40 \, \mathrm{V}, \, \mathrm{radial} \\ C_{14} = 10 \, \mu \mathrm{F}, \, 63 \, \mathrm{V}, \, \mathrm{radial} \end{array}$

#### Inductors:

$L_1 = air-core, 0.1 mH$  (see text)

#### Semiconductors:

$\begin{array}{l} D_1, D_2 = 3 \text{ mm LED, red (1.6 V drop at} \\ 3 \text{ mA)} \\ D_3 - D_5 = 1N4003 \\ D_6 = 1N4148 \\ T_1, T_2, T_6 = BC550C \\ T_3 - T_5 = BC560C \\ T_7, T_9, T_{10} = BD139 \\ T_8, T_{11} = BD140 \\ T_{12} = IRF9540 \\ T_{13} = IRF540 \\ T_{14} = BC617 \end{array}$

#### Miscellaneous;

$\begin{aligned} &\text{Re}_1 = \text{relay, } 24 \text{ V, } 1 \text{ make contact (e.g.,} \\ &\text{Siemens V23056-A0105-A101*)} \\ &\text{F}_1, \text{F}_2 = \text{fuse, } 2.5 \text{ A, fast, with holder for} \\ &\text{PCB mounting} \\ &\text{Ceramic washers (5) for } T_7, T_{10}\text{-}T_{13} \\ &\text{Terminal block (5) (see text)} \\ &\text{Heat sink, } 0.6 \text{ KW}^{-1} (e.g., \text{Fischer SK85**}) \\ &\text{PCB No. } 930102 \text{ (see p. 110)} \end{aligned}$

#### Power supply:

Mains transformer,  $2 \times 25$  V, 160 VA Mains on-off switch with indicator Fuse 1.25 A, slow with holder Bridge rectifier Type B200C35000 Electrolytic capacitor (4), 10,000  $\mu$  F, 50 V Resistor (8) 0.1  $\Omega$ , 5 W

\* ElectroValue, 3 Central Trading Estate, Staines, TW18 4UX, L (0784) 442 253. Private customers welcome.

\*\* Dau (UK) Ltd, 7075 Barnham Road, Barnham, West Sussex PO22 0ES. L (0243) 553 031. Trade only, but information as to your nearest dealer will be given by telephone. **END**

Fig. 6. Wiring diagram of one channel of the medium power HEXFET amplifier.

ELEKTOR ELECTRONICS DECEMBER 1993

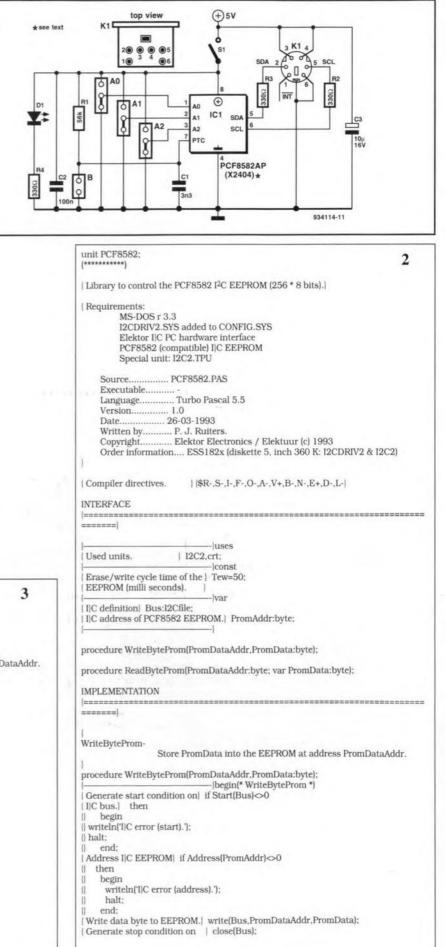

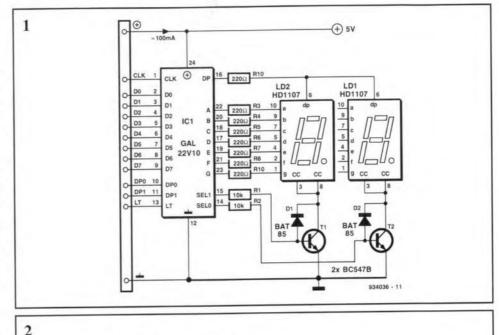

# 535 CARD WITH EPROM EMULATOR (PART 2)

Although there is also a signal on the  $\overline{ACK}$  line of the Centronics interface in emulator mode (unless JP6 is swapped), this of little consequence because the BUSY line is held high permanently in run mode. If you use P4.0

16

as an input, make sure that the line does not short-circuit the output of your application when 'emulator' mode is used. It is, therefore, recommended to drive P4.0 from an open-collector or open-drain output. This avoids the risk of short-circuits, while a pull-up resistor is not required because it is already contained in the controller.

If you want to use the Centronics input in an application, do remember that the circuit is switched to emulator

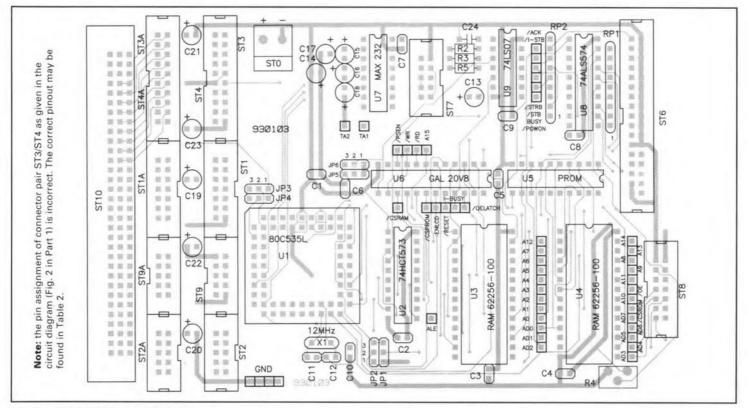

Fig. 3a. Track layouts of the double-sided through-plated printed circuit board designed for the 535 system.

mode when a strobe pulse is received. Since it not normally possible to copy data into the data latch without making use of the strobe pulse, the jumper shown in the block diagram must be swapped to enable a program to be tested. Once that is done, the GAL can no longer switch the circuit to emulator mode. The same jumper is also swapped if EPROM instead of RAM is used for the program memory.

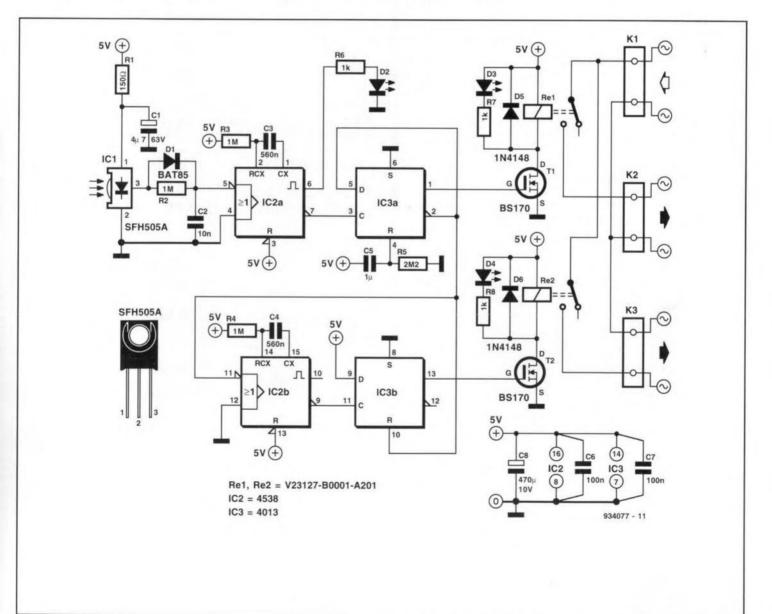

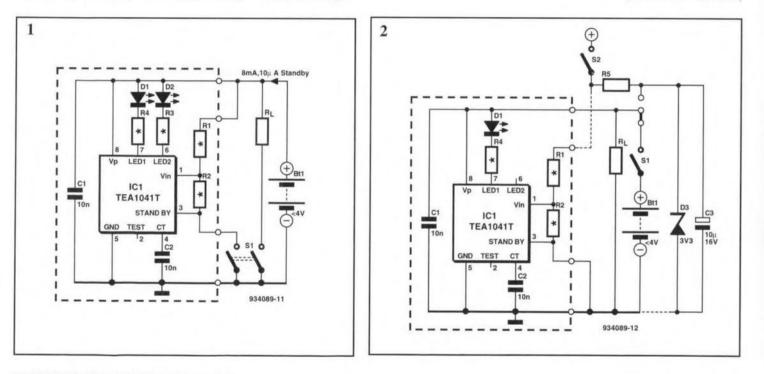

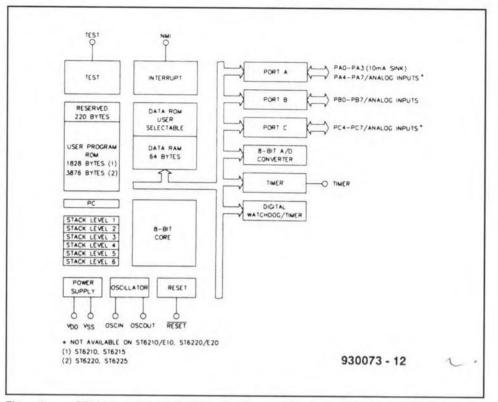

#### The 535 system

The circuit diagram of the 535 system, Fig. 2, is basically a worked out copy of the block diagram, with only a few extra details that require explanations. Among these details are the test points marked with 'P's and the signal name.

The 535 board may be built in two versions: with emulator or without emulator. The version with emulator is typically used to test software for applications of the 535 board. Once the test and debugging phases have been completed successfully, the software may be burned into EPROM for use on a 535 system without an emulator function. The difference between the two versions is, of course, the presence of the parts required for the emulator

function. In a system without emulator function, components U5, U8, U9, RP1, ST6, R2, R5 and C24 may be omitted, while pins 8 and 9 of the socket for U9 are interconnected. Note, however, that the GAL (U5) and the PROM (U6) for this project are always supplied as a set, i.e., these parts can not be ordered separately.

17

As a consequence of the user being able to configure the system with or with an emulator function, provision must be made to use RAM or (EP)ROM respectively for the program memory. Because there are two differences in the pin order of 32-kByte RAMs and

Fig. 3b. Component mounting plan.

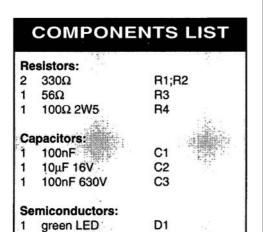

### COMPONENTS LIST

| Re | sistors:            |             | 1 GAL 20V8-15* U6 3 14-way boxheader ST1;ST1A;S              | ST8  |

|----|---------------------|-------------|--------------------------------------------------------------|------|

| 1  | 2kΩ2                | R2          | 1 MAX232 U7 4 20-way boxheader ST3;ST3A;S                    | ST4; |

| 1  | 10kΩ                | R3          | 1 74LS574 U8 ST4A                                            |      |

| 1  | 10kΩ preset H       | R4          | 1 74LS07 U9 1 96-way DIN41612                                |      |

| 1  | 10Ω                 | R5          | connector (a-b or                                            |      |

| 2  | 8-way 10kΩ SIL arra | ay RP1;RP2  | IC-sockets: a-c row) ST10                                    |      |

|    |                     |             | 1 68-pin PLCC 1 Press-key, make contact (reset)              |      |

| Ca | pacitors:           |             | 2 28-pin 1 Printed circuit board 930103*                     |      |

| 10 | 100nF               | C1-C10      | 1 24-pin, 0.3" wide * PROM U5, GAL U6 and the PCB fo         | ir   |

| 2  | 27pF                | C11;C12     | 3 20-pin this project are available as a set und             | ler  |

| 1  | 10µF 6V3 tantalum   | C13         | 1 16-pin order code 930103. The PROM and 0                   | GAL  |

| 3  | 10µF 6V3            | C14;C15;C17 | 1 14-pin are also available separately under o               | rder |

| 2  | 10µF 16V            | C16;C18     | code 6311. Price and ordering inform                         | la-  |

| 5  | 1μF 6V3             | C19-C23     | Miscellaneous: tion on page 110.                             |      |

| 1  | 4nF7                | C24         | 6 3-way pin header with                                      |      |

|    |                     |             | jumper JP1-JP6 Options:                                      |      |

| Se | miconductors:       |             | 1 12MHz quartz crystal X1 LCD-module, e.g., LM093LN (Hitachi | ) or |

| 1  | SAB80C535L          | U1          | 1 2-way PCB terminal compatible type.                        |      |

| 1  | 74HCT573            | U2          | block, pitch 5mm ST0 MCS51 assembler course software:        |      |

| 2  | RAM 62256-100       | U3;U4       | 5 10-way boxheader ST2;ST2A; 1661 MSDOS version              |      |

| 1  | PROM TBP28L22*      | U5          | ST7;ST9;ST9A 1681 Atari version                              |      |

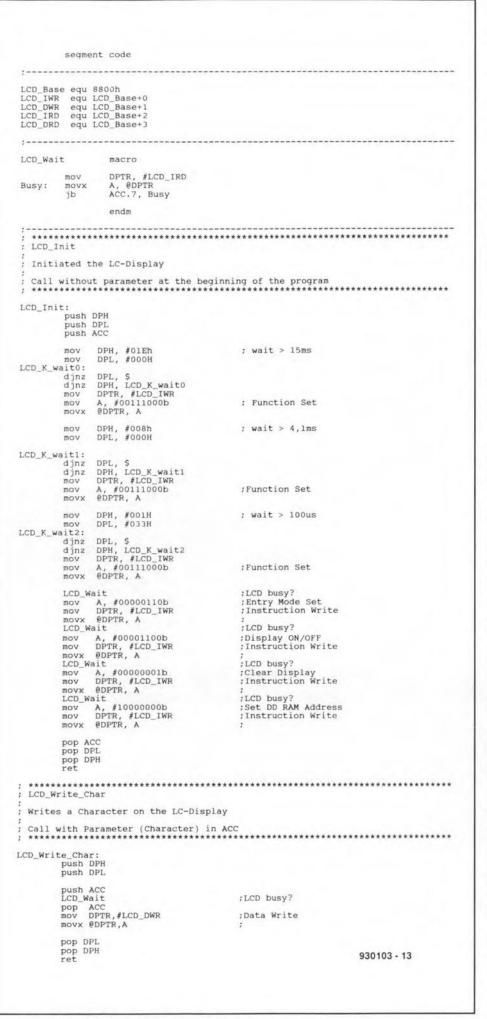

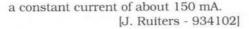

Fig. 4. Example of an LCD driver for the 535 controller.

EPROMs, jumpers JP1 and JP2 are added. These jumpers may be set to RAM or EPROM, just like JP5 and JP6.

The use of the Centronics interface for the emulator function leaves the controller's serial interface free for your own applications. Note, however, that the controller is capable of receiving and generating TTL level signals only. A MAX232 single-chip TTL/RS232 level converter is, therefore, used to allow the controller to be connected to a standard RS232 port on a PC.

Apart from digital I/O ports, the SAB80C535 also has eight analogue inputs, which are connected to an onboard 12-bit A-D (analogue-to-digital) converter. Jumpers JP3 and JP4 enable you to select either the supply voltage or an external voltage (max. 5 V; via ST1) as the ADC reference.

Finally, preset R4 acts as a contrast control for the LC display, which is connected to ST8.

#### Construction

The complete circuit is easily accommodated on a single Eurocard-size (100×160 mm) printed circuit board, which is double-sided and through plated. This board is available readymade through our Readers Services, together with the programmed GAL and PAL. The artwork for the 535 board is given in Fig. 3. Connectors ST1-ST4 are 'twins', while ST10 is fitted alongside the edge of the board to enable this to be fitted in a 19-inch case, or to be connected to another board. Connectors ST1A to ST4A enable the connection of ST1-ST4 and ST9 to ST10 to be 'tailored' to requirements. This is useful when the card is to be connected to an existing system. If you are not bound by an existing system, simply make the connection go straight across the board using two press-on (IDC) sockets and a length of flatcable. The relevant pin connections are given in Table 2.

If it is desired to fit the board into a 19-inch enclosure, special attention should be given to connectors ST0, ST2(A), ST3(A), ST8, and resistor R4. These parts are located close to the board edge, and make it impossible to use the card guides normally present in 19-inch racks. You may just be lucky with ST8 and R4, but lacking space for the boxes, ST2(A) and ST3(A) will have to be changed into normal pin headers. Also, PCB terminal block ST0 may have to be turned 180° to enable the supply wires to be inserted from the centre of the board.

The connection order of 34-way boxheader STs is identical to that of the Centronics connector, with the exception of two missing pins (36-way

box headers do not exist). This does not cause problems if you use a length of flatcable between ST8 and the Centronics connector, making sure that pin 1 on one connector goes to pin 1 of the other (use the single coloured wire on one side of the flatcable for this purpose). Pins 18 and 36 of the Centronics connector are not used. Also, remember that there is no pinfor-pin correspondence between the Centronics connector at the side of the 535 system and the 25-way sub-D connector at the side of the PC. Therefore keep in mind that some wires will have to be crossed if you use a flatcable to establish the connection between STs and the PC's printer port. The best way to avoid all problems in this regard is to use a ready-made IBM PC parallel printer cable, which is often cheaper than two connectors and a length of flatcable.

#### Software

Like many other microcontroller boards, the present 535 system board is not more than the basis of a larger circuit designed to perform a certain function in conjunction with dedicated software. An example of a circuit based on a 80C535 microcontroller core is the Watt-hour meter (Ref. 2).

As already mentioned, you will need an assembler to be able to produce software for the 535 board. Fortunately, MCS51 assemblers come in a wide variety of levels and capabilities. If you are on a tight budget, do consider the assembler contained on the '8051/80C32 assembler course' diskette (Ref. 3), which is good value for money. Note, however, that the examples on this course disk may require small modifications because of the different memory structure of the 535 board.

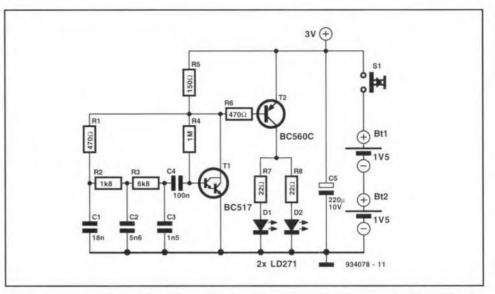

A programming example specifically written for the present 535 board is given in Fig. 4. This is the listing of an LCD driver, which may be used to write messages on to the LCD that tell you what has happened during the course of a program under development. Alternately, such messages many be written to the PC via the RS232 interface on the 535 board. The routine shown in Fig. 4 has been written with a so-called macro assembler. which enables frequently called, small, program chunks to be defined only once. An example of such a macro is found at the top of the listing. Unfortunately, the assembler mentioned above does not support the use of macros. Consequently, the three individual instructions that make up the macro (LCD\_Wait) must be repeated at every location this macro appears in the program.

#### **References:**

**1.** I<sup>2</sup>C alphanumerical display. Elektor Elec*tronics* September 1993.

**2.** Watt-hour meter. *Elektor Electronics* February 1993.

**3.** 8051/8032 assembler course. *Elektor Electronics* February through November 1992. Disk/EPROM order code: 1661 (see page 70).

| signal | pi                                    | in                | signal               | Hel My Real End       | pin            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|--------|---------------------------------------|-------------------|----------------------|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        |                                       | 25 2 2            |                      | row a                 | ST             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | row b/c     |

|        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | and the state     |                      | 1                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1           |

|        |                                       | The second second |                      | 2                     | and the second | and the second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2           |

|        | S                                     | 12                | and and              | 1.2.2                 | ST             | 2A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| P1.0   | 2 4                                   | 1                 | +5V                  | 3                     | 2              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3           |

| P1.2   |                                       | 3                 | P1.1                 | 4                     | 4              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4           |

| P1.4   | 6                                     | 5                 | P1.3                 | 5                     | 6              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5<br>6<br>7 |

| P1.6   | 8                                     | 7                 | P1.5                 | 5<br>6<br>7           | 8              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6           |

| GND    | 10                                    | 9                 | P1.7                 | 7                     | 10             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7           |

|        | S                                     |                   | and the state of the |                       | ST             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| P3.7   | 9                                     | 10                | GND                  | 8                     | 9              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9      |

| P3.5   | 7                                     | 8                 | P3.6                 |                       | 7              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| P3.3   | 5                                     | 6                 | P3.4                 | 10                    | 5              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10          |

| P3.1   | 3                                     | 4                 | P3.2                 | 11                    | 3              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11          |

| +5V    | 1                                     | 2                 | P3.0                 | 12                    | 1              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12          |

|        | S                                     | [1                | Star Barrier         | and the second second |                | ST1A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| ANO    | 2                                     | 1                 | +5V                  | 13                    | 2              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13          |

| AN2    | 4                                     | 3                 | AN1                  | 14                    | 4              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14          |

| AN4    | 6                                     | 5                 | AN3                  | 15                    | 6              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15          |

| AN6    | 8                                     | 7                 | AN5                  | 16                    | 8              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16          |

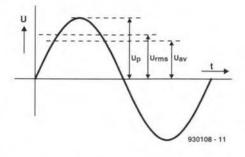

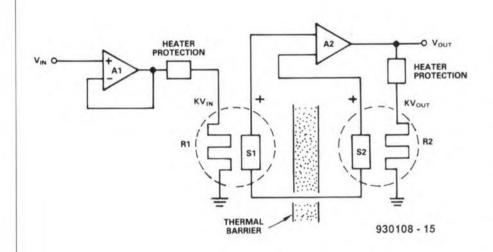

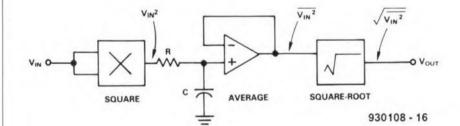

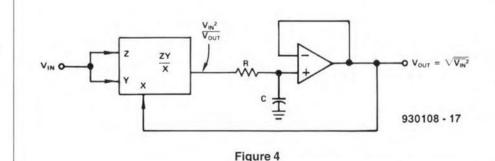

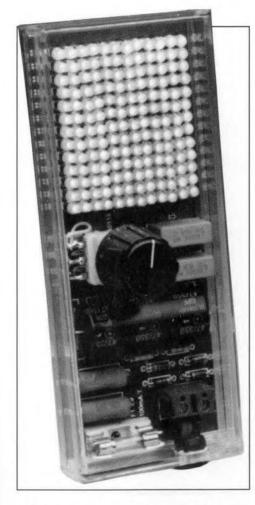

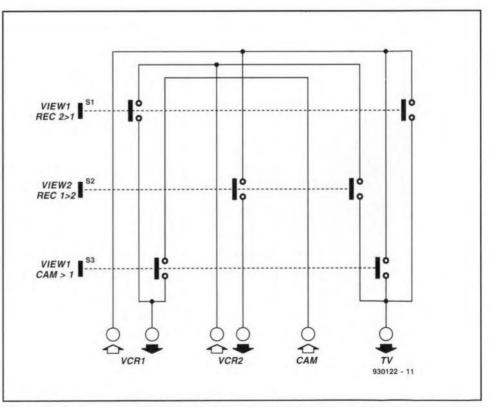

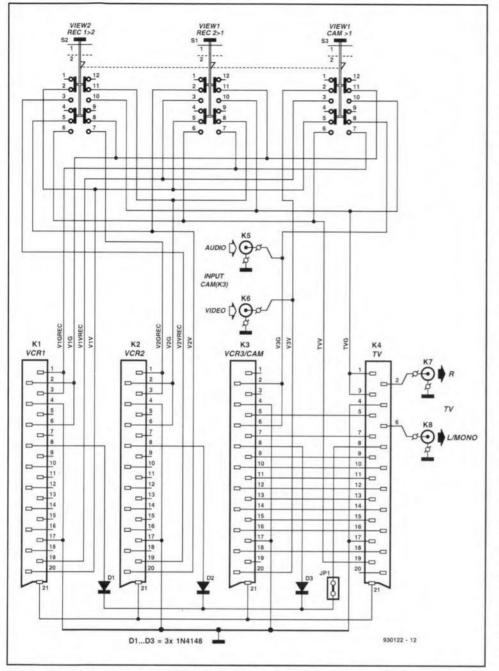

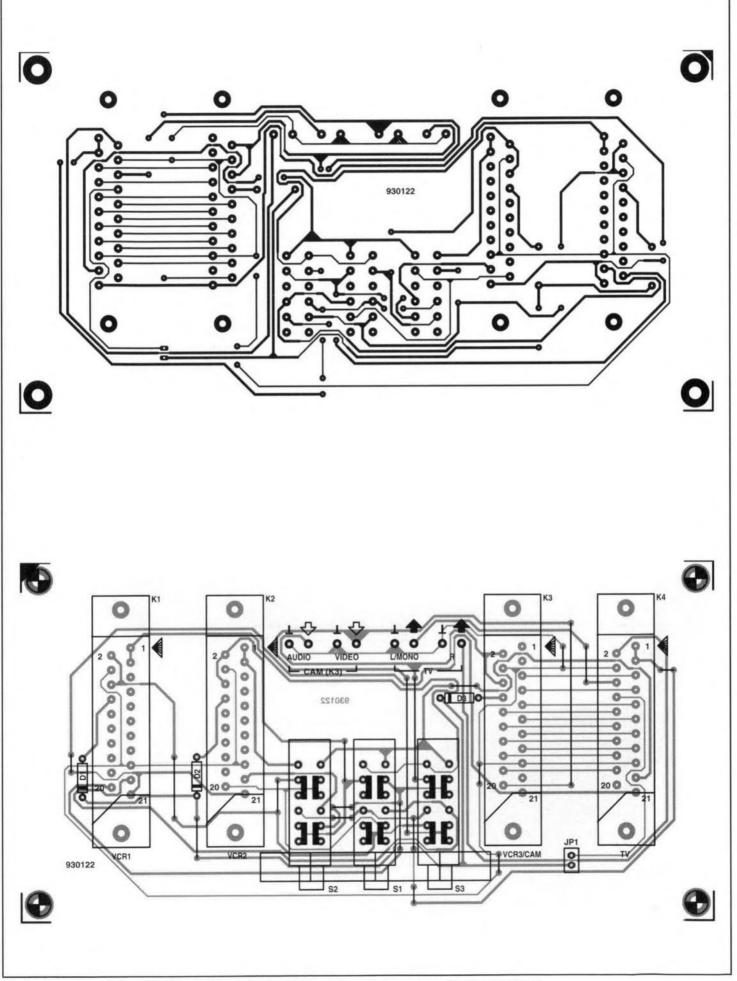

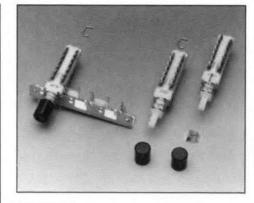

| GND    | 10                                    | 9                 | AN7                  | 17                    | 10             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17          |