# VHF/UHF TELEVISION TUNER 930069 (PART 1)

Together with a suitable colour monitor, the television tuner described here forms a complete television set.

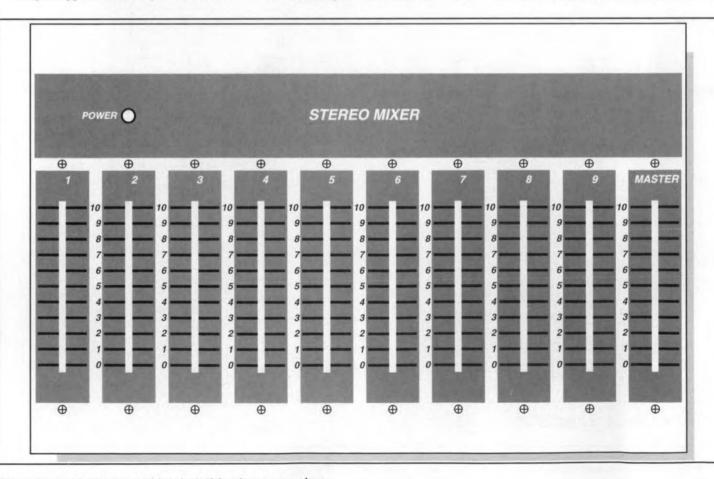

Microprocessor controlled, menu-driven, with digital tuning, a small LCD text screen, optional infra-red remote control, and memory capacity for up to 100 preset stations, the tuner is ideal for TV DXing and interfacing to a computer system via a video digitizer. The unit offers full coverage of the VHF and UHF TV bands, and apart from the normal mono sound channel, analogue stereo sound as used in some countries on the European continent is also provided.

#### Design by W. Sevenheck

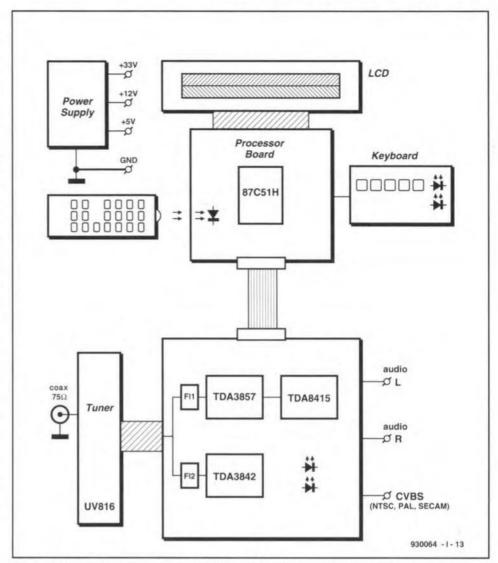

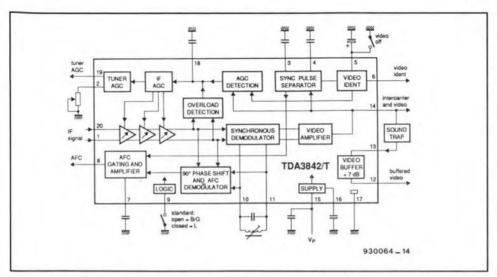

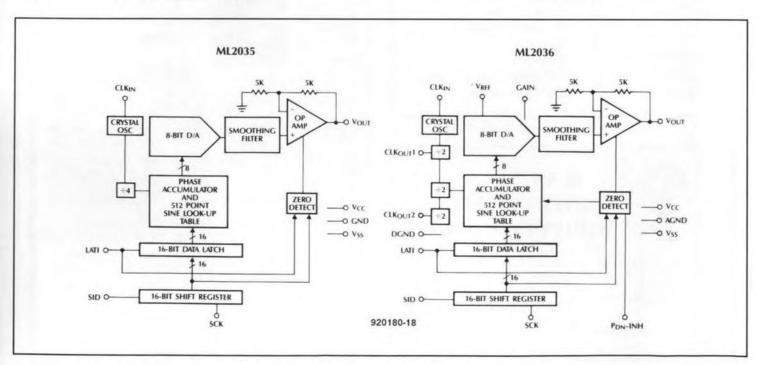

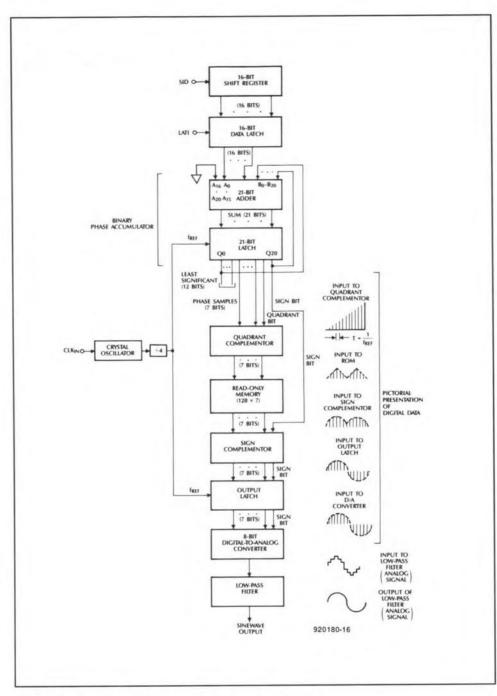

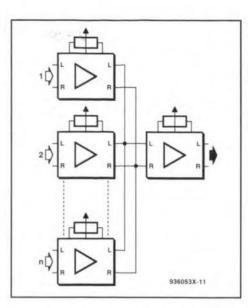

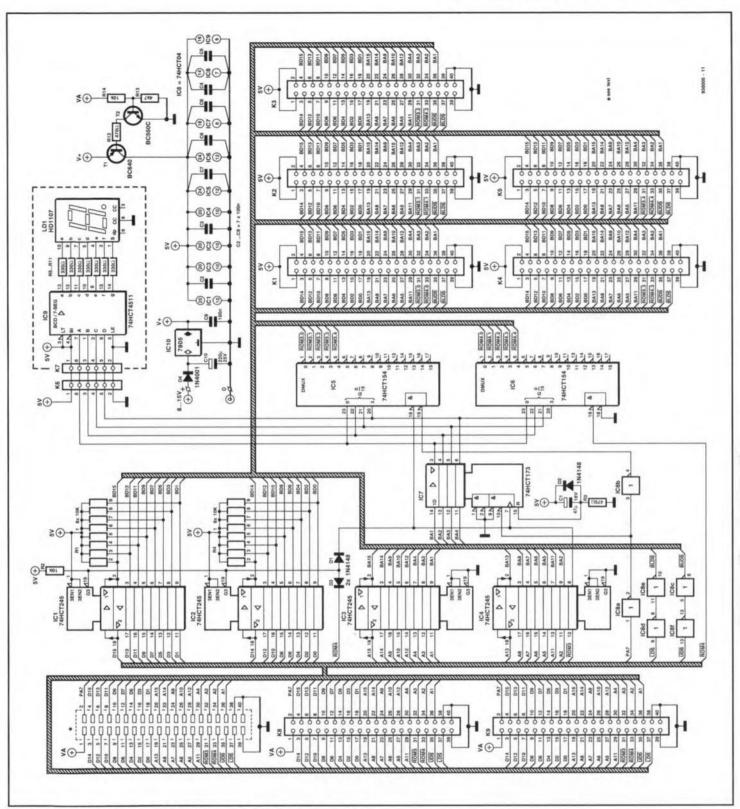

HE block diagram of the TV tuner is given in **Fig. 1**. The most important sections are the power supply, the (ready-made) VHF/UHF tuner module. and the intermediate frequency (IF) circuit plus sound decoder. A microprocessor core based on a 8751 controller arranges, among others, the control of a two-line LCD text display, a small keyboard, and the tuning of the tuner module. The serial I<sup>2</sup>C bus is used for the communication between the microcontroller and a number of other ICs in the circuit. The digital signals needed for this communication are generated by the microcontroller itself. In addition, the 8751 also decodes and processes the digital RC5 codes received from an RC5 compatible infra-red remote control.

The TV tuner supplies a colourvideo-blanking-synchronization (CVBS, or simply 'composite video'), output signal into a standard load impedance of  $75 \Omega$ .

#### Circuit description

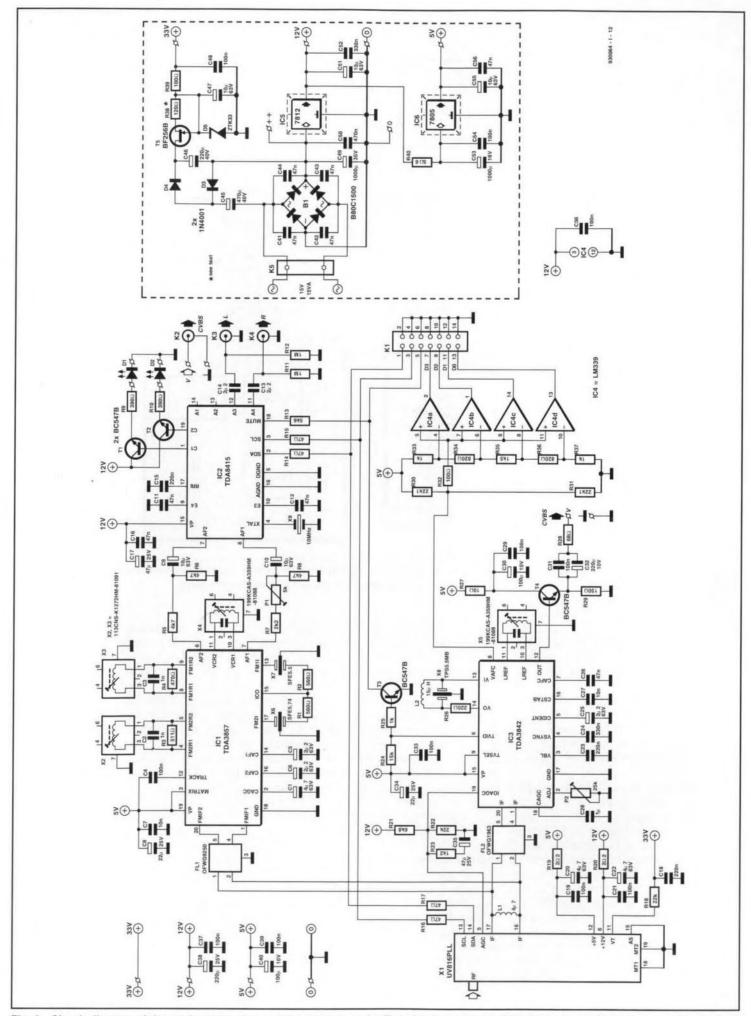

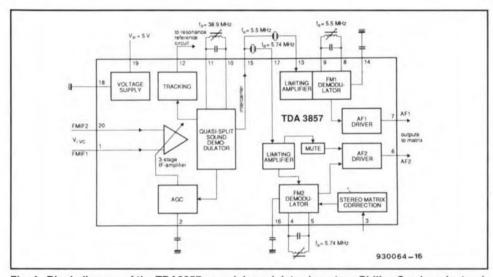

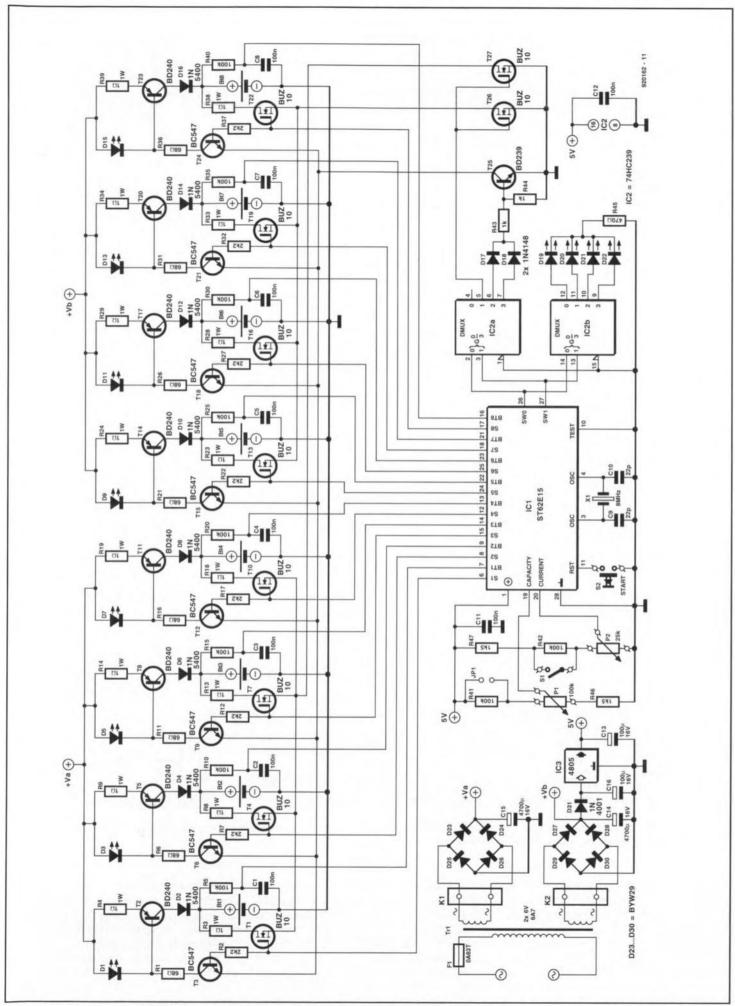

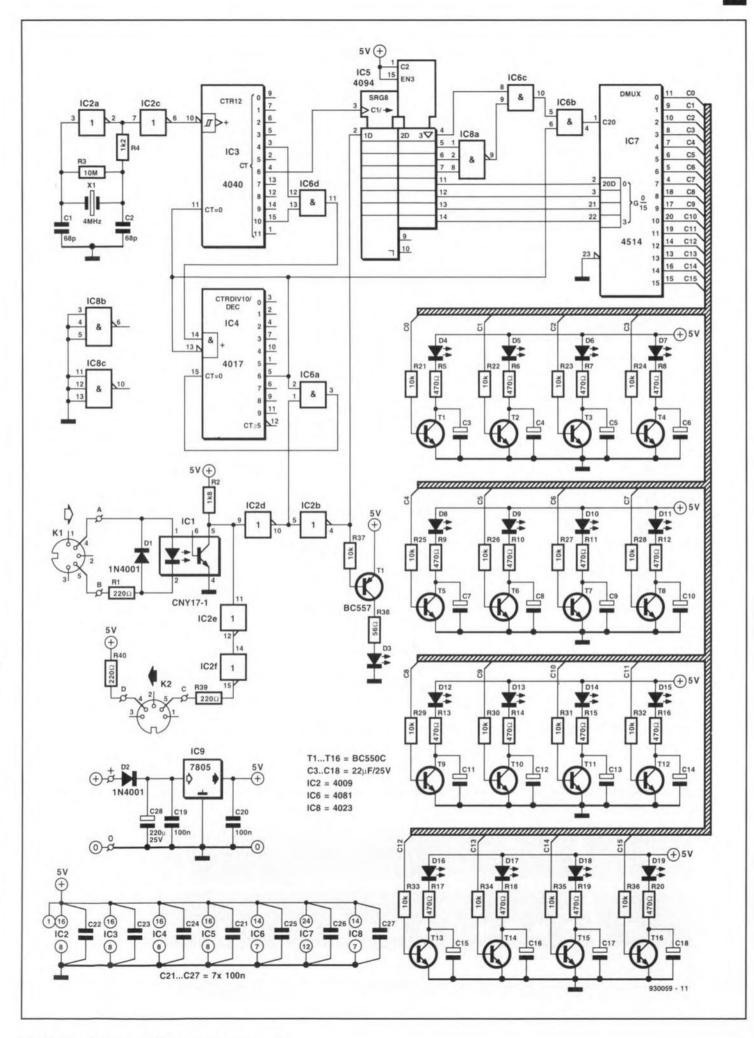

The circuit diagram in **Fig. 2** shows the VHF/UHF tuner module, the sound and vision decoders, and the

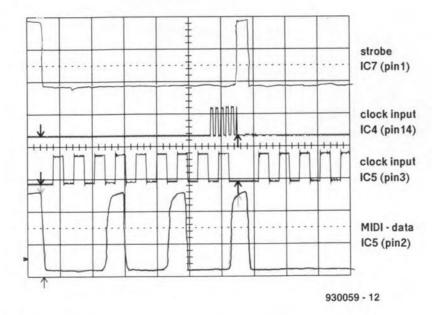

power supply. Nearly all the 'work' in the circuit is done by three powerful integrated circuits from Philips Semiconductors. All three the TDA3842 multistandard video IF processor, the TDA3857 sound IF processor, and the TDA8415 sound processor, appear in recommended application circuits as found in the Philips datasheets. Two surfaceacoustic wave (SAW) filters from Siemens are used to minimize crossinterference between sound and vipass Both filters the down-converted 38.9-MHz reference carrier. Filter Fl1 also passes the sound component, while Fl2 does the same with the vision component. In both cases, the 38.9-MHz signal is needed as a reference in the decoding operation. A simple analogue-to-digital converter (ADC) based on a resistor ladder network and an LM339 opamp (IC4) converts the AFC (automatic frequency control) signal supplied by IC3 into four logic levels that are accepted by the microcontroller, which uses the 4-bit code to ensure the best possible tuning of the tuner module.

The tuner module, a Type UV816PLL from Philips Components, requires three supply voltages: 5 V, 12 V and

33 V. The unit gives full coverage of the VHF-1 (channels E2 to C; 48.25 MHz to 82.25 MHz), VHF-3 (175.25 MHz to 224.25 MHz) and UHF (channels E21 to E69; 471.25 MHz to 855.25 MHz) TV bands. It should be noted that the VHF-1 and VHF-3 bands are no longer used for television in the UK. They are still of interest, however, because of the many signals that can be received (under favourable propagation conditions) from overseas TV stations transmitting in these bands.

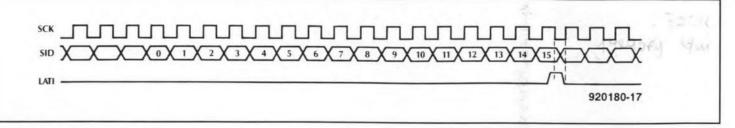

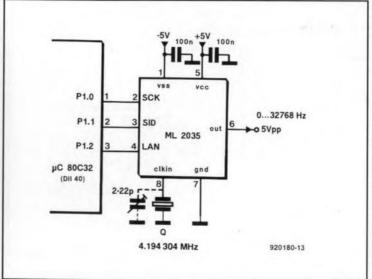

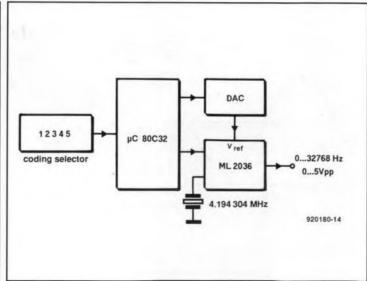

Tuning is accomplished with the aid of (serial) digital commands applied to the module via its I2C bus connections, SDA and SCL. The intermediate frequency signal is available on the two IF outputs, pins 16 and 17. The UV816PLL is provided with a digital programmable phase-locked loop (PLL) tuning system. This enables tuning with a 62.5-kHz raster at crystal accuracy. Apart from tuning, band switching is also carried out via the I2C bus. The tuner's AGC input is driven by the TDA3842 video processor. The video (vision) and audio (sound) decoder circuits are connected in parallel to the tuner's IF outputs.

#### Vision channel

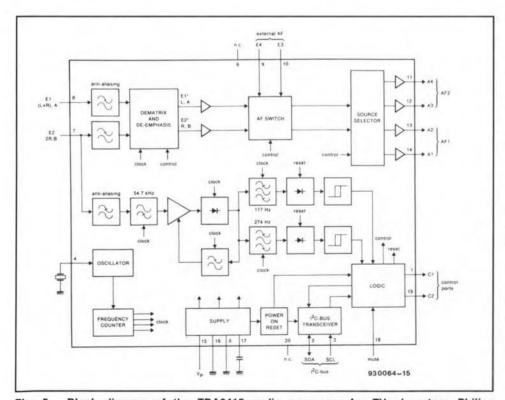

After the sound information has been eliminated by SAW filter Fl2, the IF signal is applied to IC3, a Type TDA3842 multi-standard video IF amplifier/demodulator. The internal structure of this IC is given in Fig. 3. Glancing back at the circuit diagram in Fig. 2, it is easily seen that the TDA3842 is used in its standard application circuit. However, the switch marked 'video-off' is not implemented, while the video switch at pin 9 is available as a connection (solder spot) only, which allows the AGC to be driven by negative (B/G) or positive (L) modulation of the sync signal. The B/G option is the default. The L option is only used with TV systems other than PAL, such as

SECAM.

In the following descriptions, frequencies that apply to the UK television standard (CCIR System I) are given in brackets.

A 5.5 MHz (6.0 MHz) sound subcarrier trap is connected between pins 13 and 14 of the TDA3842. The parallel LC tuned circuit required for the video demodulator is connected to pins 10 and 11. The demodulator supplies the AFC (automatic frequency control) via a 90° phase shift. The preset potentiometer connected to pin 2 determines the operating point of the AGC. If the signal level is too low, transistor T3 arranges for the mute circuit to be actuated. The audio channel in the TDA8415 (IC2) is then cut off, so that the loudspeaker does not produce noise. The sound channel is opened again when a sufficiently strong signal is received.

The BC547B transistor at the video output of the TDA3842 buffers the video signal, and ensures an output impedance of about 75  $\Omega$ . Capacitors C31 and C32 block the d.c. component in the output signal.

The AFC output signal produced by the TDA3842 is fed to the above mentioned 4-level comparator circuit around IC4. The resultant 4-bit code supplied by the four comparator outputs is used by the microcontroller to fine-tune the receiver.

#### Sound channel

The sound channel is based on two further ICs from Philips Semiconducof family high-integration TV/video building blocks. These ICs are the TDA3857 IF amplifier with two FM demodulators, and the TDA8415 sound processor for two-language sound, with integrated filters and I2C bus control. To begin with, the video component is suppressed by SAW filter Fl1, while the 38.9 MHz reference carrier and the sound component are passed. Next, the balanced IF signal is applied to IC1.

The internal organisation of the TDA3857 is given in Fig. 4. First, the level of the IF signal is 'stabilized' with the aid of an automatic gain control (AGC). The speed of this control is determined by capacitor C1, which is connected to pin 2. The sound intercarrier is restored on the basis of the input signal, while any residual AM signals are suppressed. The two components produced by the mixer, 5.5 MHz (6.0 MHz) and 5.74 MHz, are separated by appropriate external ceramic filters, X6 and X7, and then processed separately in the IC. The 5.5 MHz (6.0 MHz) subcarrier supplies the main sound channel as produced by any mono TV set. The second lim-

Fig. 1. Block diagram of the VHF/UHF TV tuner. A microcontroller is used to control the analogue sections, while an LCD is useful for operating the tuner.

iter/demodulator in the TDA3857 is tuned to a narrow band around 5.74 MHz, which contains information for stereo or two-language broadcasts. Note that this type of analogue stereo sound with TV broadcasts is used in some European countries only, including Germany and Holland. It is not used in the UK, where stereo TV sound is digital and based on the NICAM-728 standard. Two tuned circuits. X2 and X3, are used to demodulate the sound signals at 5.74 MHz and 5.5 MHz (6.0 MHz) respectively. In the absence of a 5.74-MHz component, the associated sound channel is automatically muted, leaving the main sound channel to be heard only. The two audio signals are output via pins 6 and 7, and fed to the audio processor, IC2. Preset P1 is included in the circuit to allow the level of the two audio channels - 5.5 MHz (6.0 MHz) and 5.74 MHz — to be made equal. This is necessary to ensure the best possible channel separation with stereo broad-

The sound processor, IC2, is a TDA8415. This IC has been developed

for stereo or two-language sound in TV sets and video recorders. As shown in the block diagram in Fig. 5, audio signals are applied to the two inputs of this processor: '(L+R)/2' or language 'A' goes to input AF1, and 'R' or language 'B' to input AF2. In this notation, 'L' is the left-hand audio channel in a stereo broadcast, and 'R' the righthand audio channel. A pilot tone modulated 50% AM on a subcarrier at 54.6875 KHz enables the sound processor to distinguish between stereo and two-language broadcasts. The pilot tone is contained in the signal for the second channel (E2) and has a frequency of 117.4 Hz for stereo broadcasts, or 274.1 Hz for two-language broadcasts. Depending on the mode of the sound processor (mono, stereo or two-language), LED D1 and/or D2 is controlled by IC outputs C1 and C2 via two buffer transistors. The sound processor IC itself is controlled via the SCL and SDA lines that form the I2C bus. Special commands on this bus allow the processor's signal inputs to be selected, and the muting to be actuated. The timing signals

Fig. 2. Circuit diagram of the analogue section and the power supply. The circuit remains relatively simple thanks to the use of three dedicated integrated circuits developed for the modern TV industry.

Fig. 3. Block diagram and typical surroundings of the TDA3842 video demodulator (courtesy Philips Semiconductors).

Fig. 4. Block diagram of the TDA3857 sound demodulator (courtesy Philips Semiconductors).

Fig. 5. Block diagram of the TDA8415 audio processor for TVs (courtesy Philips Semiconductors).

required for these operations are derived from a 10-MHz quartz crystal, X9, which is connected to an on-chip oscillator. The audio output signals are fed out of the circuit via capacitors C13 and C14. The additional audio inputs, E3 and E4, and the additional audio outputs, A3 and A4, are not used in the present circuit.

#### Power supply

All supply voltages required for the VHF/UHF TV tuner are derived from a single 15-V, 15-VA mains transformer, whose secondary winding is connected to K5. A voltage doubler, D3-D4-C45-C46, turns the 15 V a.c. into about 35 V d.c., which is stepped down to a regulated voltage of 33 V by a zener diode, D5, connected to a current source, T5-R38. The regulated and temperature-compensated 33-V supply voltage is applied to the UV816PLL TV tuner module.

The direct voltage of about 18 V across C49 is stepped down to 12 V by regulator IC5. This also powers the second regulator, IC6, which provides the 5-V supply rail. Resistor R40 is connected between the output of IC5 and the input of IC6 to reduce the dissipation of the 5-V regulator.

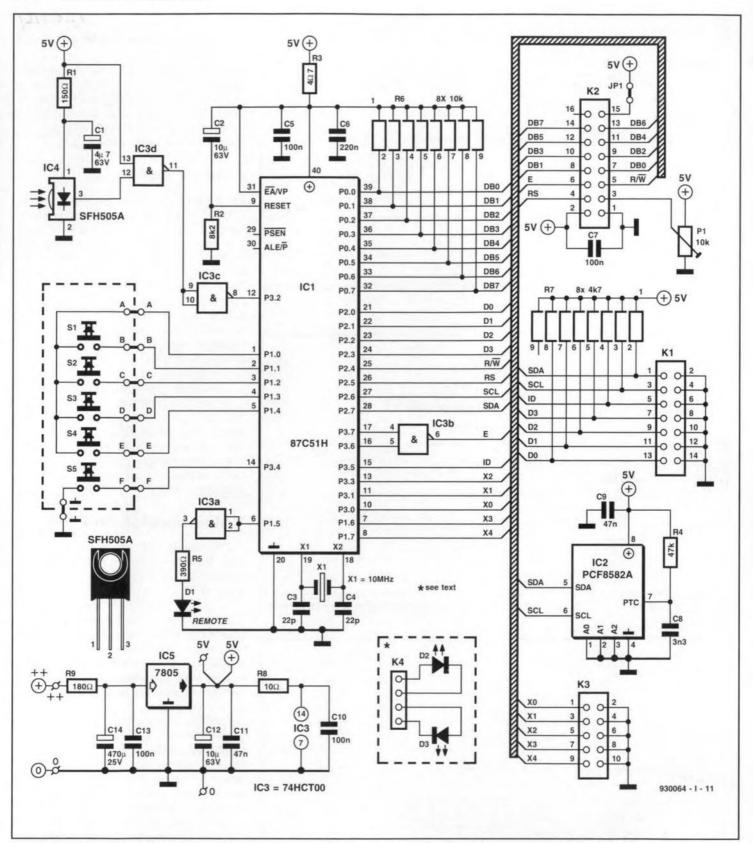

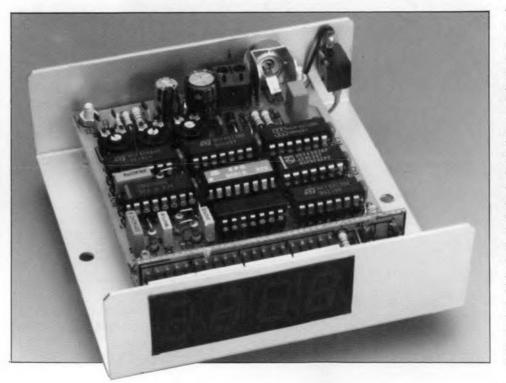

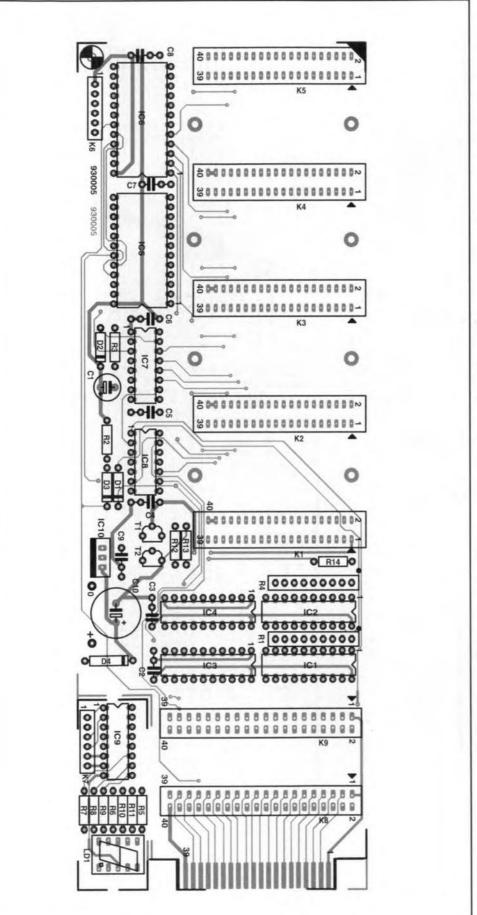

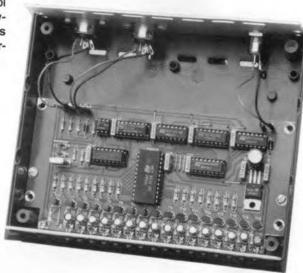

#### Traffic control: an 8751

The remainder of the circuit is given in Fig. 6. All control activities are assumed by a single microcontroller Type 8751, which comes ready-programmed through Readers our Services. The circuit around the microcontroller has no surprises. The power-up reset network is formed by R2-C2. The 10-MHz clock signal is generated with the aid of crystal X1. Two resistor arrays, R6 and R7, provide the necessary pull-up resistors on a number of I/O lines. The two-line LC display is connected to boxheader K2. which supplies all the necessary drive signals, including the contrast voltage which is set with P1. Jumper JP1 is used to actuate the background light on some types of display unit.

Connector K<sub>1</sub> forms the link with the rest of the circuit. Apart from the SDA and SCL signals, this bus also carries the 4-bit AFC information supplied by IC4, and the mute signal, ID.

As already mentioned, the TV tuner has a capacity of 100 preset stations. Since the 8751 does not have enough internal memory for this purpose, external memory has been added in the form of an I<sup>2</sup>C compatible EEPROM with a capacity of 256 bytes. The EEPROM, a Type PCF8582A, is capable of retaining data without a backup voltage. An RC network, R4-C8, is connected to the PTC input to make sure

Fig. 6. Circuit diagram of the digital control based on an 87C51 microcontroller from Intel. The preset stations are stored in an EEPROM, IC2.

that the timing of the read/write cycle in the memory is correct.

The local keyboard on the tuner consists of five press-keys which are connected directly to microcontroller port lines.

The infra-red receiver is formed by IC4, an SFH505A module from Siemens. The pulses supplied by the IR receiver reach the microcontroller via inverters IC3c and IC3d. The microcon-

troller is programmed to respond to codes transmitted by RC5 compatible (Philips standard) remote control units, and causes LED D1 to flash while a valid IR signal is being received.

Finally, the processor board has its own 5-V regulator to improve the separation between the digital and analogue sections of the tuner. An additional advantage of the separate supply is that the processor board may

be used for other applications. In this regard it is useful to mention connector K3, which carries the non-used I/O lines.

Next month's second and final instalment of this article will discuss the construction of the printed circuit boards, and the enclosure in which the tuner is fitted. Also, the operation of the unit will be discussed extensively.

amplifier?). The output pulse is picked up by a microphone and fed back into the IMP where it is digitized and then fed into an IBM (compatible) computer via the printer port. The IMP software then analyses the input via Fourier transforms and outputs the results on to the computer screen in graphical form in the shape of amplitude and phase response curves. Full control is via the PC. The amplifier output can be sampled via a probe to correct for errors in the pulse spectrum and amplifier response.

IM P allows the collection and analysis of 12-bit analogue data up to 4,095 samples in length and sample rates are selectable at either 61.441 kHz or 1.92 kHz which, along with the internal filtering, allows measurements from several hertz to 20 kHz.

Further information from Falcon Acoustics Ltd, Tabor House, Norwich Road, Mulbarton, Norfolk NR14 8JT, England. Telephone +44 (0)508 78272; fax +44 (0)508 70986.

#### **CORRECTIONS**

DIGITAL DIAL (January 1994)

An attentive reader has drawn our attention to the fact that the digital dial can not be used in conjunction with the receiver illustrated (a Yaesu Type FRG-7) since the IF of that receiver is much too high for the dial. Sorry for that oversight! [Editor]

#### VHF/UHF TUNER (Oct/Nov 1993)

The tuner module used in this design is no longer in production with Philips and its availability will thus become a problem. Fortunately, the Type UV916H is an excellent alternative. The snag is, however, that this unit is slightly smaller than the UV816,

so that the antenna connector no longer protrudes from the enclosure. This can be overcome by terminating the antenna cable into a coaxial plug and making the entrance hole slightly larger. Moreover, one of the two earth tags of the UV916H must be connected at a different position.

#### **LETTERS**

#### SCART SWITCHING BOX

(December 1993)

I have a few problems with this project, which I believe have to do with the connections. Pin 1 of one connector is linked to pin 2 of the other. The same is true of pins 3 and 19, which are linked to pins 6 and 20 respectively. All other pins are interlinked as one would expect, i.e., pin 5 to pin 5, pin 10 to pin 10, and so on.

L. Bastiaenssen

In a SCART cable, the wires for the video and audio connections are always crossed. That is why the video output (pin 19) at one end of the cable is linked to the video input (pin 20) at the other end. This arrangement ensures that the input of one piece of equipment is always connected properly to the output of another. There is, therefore, nothing wrong with your cable.

Note that two pieces of equipment must never be connected simultaneously to  $K_3$  and  $K_5/K_6$ . Use SCART connector  $K_3$  or the phono plugs  $K_5/K_6$ , but not both at the same time! [Editor]

#### PRECISION CLOCK FOR PCs

(November 1993)

I have encountered a problem with the Precision

clock for PCs. I have an IBM (compatible) PC486 and have, as stated in the article, complemented the CONFIG.SYS file with the following (last) line:

DEVICE C:\MSDOS\DCFCLOCK.SYS.

I should be pleased if you would tell me:

1. Whereto should the files of the software provided (DCFCLOCK.ASM, DCF-CLOCK.DOC and DCFCLOCK.SYS be copied? To the root, the MSDOS or a separate directory?

2. Once the files have been loaded, how is the program called up to initialize the driver and to fill the options P, I, S, B and D? (M. Meersschaut)

The file DCFCLOC. ASM is the assembler listing of the program, which you no longer need (it is of interest only to dyed-in-thewool programmers). The file DCF-CLOCK. DOC contains the instructions for the program, which you can read with a word processing program. It is not necessary to store this file on a hard diksk.

The only program that you need to copy to the hard disk is DCFCLOCK.SYS. Place this file in the directory containing the DOS commands (e.g., C:\DOS). Add a line that indicates where the computer can find that program to CONFIG.SYS (in C:\), e.g. DE-VICE = C:\DOS\DCFCLOCK.SYS. Other suffixes may be added for changing certain settings (see DOC file), but even without these the system should work correctly.

Note, however, that the receiver circuit must be connected to the COM port 2 and that the computer must be restarted after the software has been installed. The program will then automatically set the correct time in the internal clock of the PC every minute.

[Editor]

## Ah METER WITH DIGITAL DISPLAY

Design by K. Bachun

Knowing the current drawn (by a battery) or generated (by a solar cell) over a period of time is a requirement in many applications that can be met with the meter described in this article.

The product of current and time is a measure of the electric charge that has been transported in a circuit. It is usually measured in ampere hours (Ah = 3600 coulomb). It must not be confused with power, which is a product of current and voltage. An instrument that measures ampere hours is of interest, for example, in assessing the effectiveness of a solar battery. Normally, it is not accurately known how much charge the solar cells generate nor how much the load connected to the battery needs. The present meter can become a permanent part of such a setup or be used in the design stage to measure both quantities. It indicates these on a threedigit LED display.

#### Principle of measurement

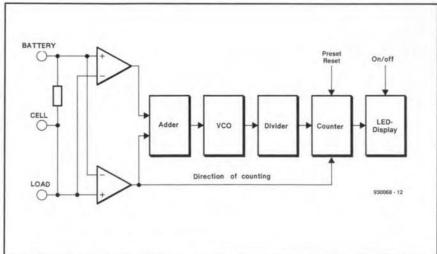

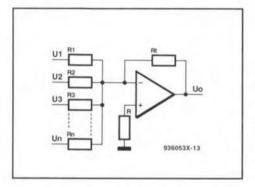

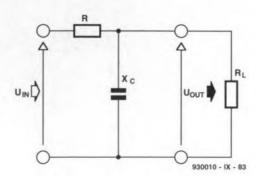

The principle of operation is shown in the block diagram of **Fig. 1**. A low value resistor has been introduced in the circuit between the solar cell and battery charged by this cell. The potential drop (pd) across this resistor caused by the charging cur-

rent (from the solar cell) or the discharge current (through the load) is evaluated by the Ah meter.

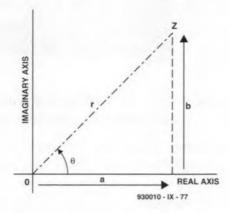

The pd is applied to two differential amplifiers, whose output voltages would be equal but 180° out of phase (that is, inverted with respect to one another), if the input were not a simple supply voltage. Thus, the adder amplifies only one voltage; the other (which, with a symmetrical supply, would be negative) is nil. The output of the non-reactive adder is, therefore, a voltage that is proportional to the current and which is used to drive a voltage-controlled oscillator (VCO – also called voltage-to-frequency converter).

The VCO generates rectangular pulses whose frequency is proportional to the current. The pulses are divided and counted, and then used to drive an LED display.

Since the polarity of the drop across the shunt resistor shows whether the pd is caused by a charging current or a discharge current. the output of a differential amplifier also shows the direction of the current. The output can thus be used

to indicate the direction of counting. When energy is drawn from the battery, the counter counts downward; when the battery is being charged by the solar cell, it counts upward.

The meter does not in any way control or affect the charging current; this can be done only by a special solar charging regulator.

The display does not show the state of charge of the battery to the nearest millampere second, since self dicharge and temperature dependence of the battery are not taken into account.

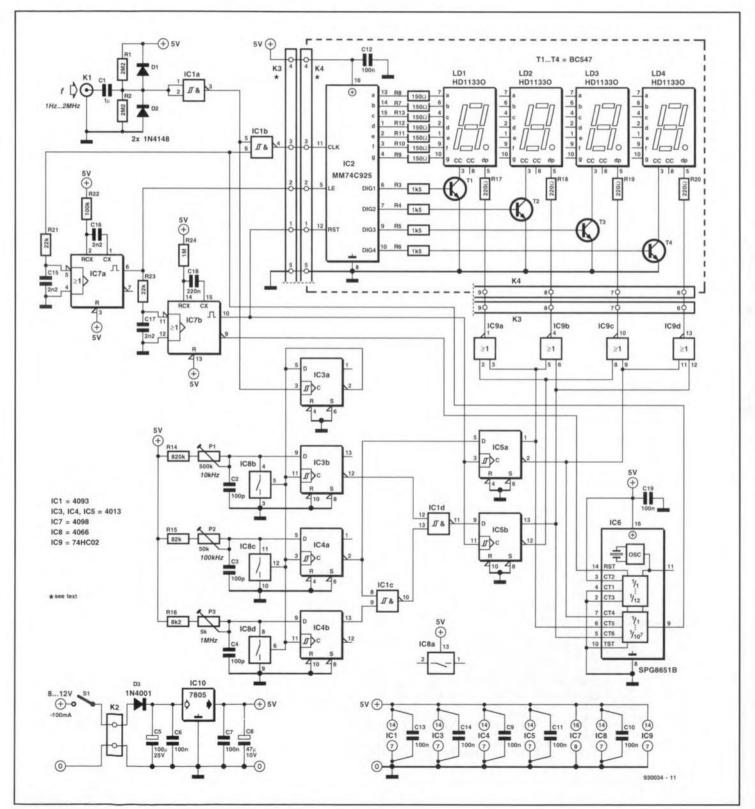

#### The circuit

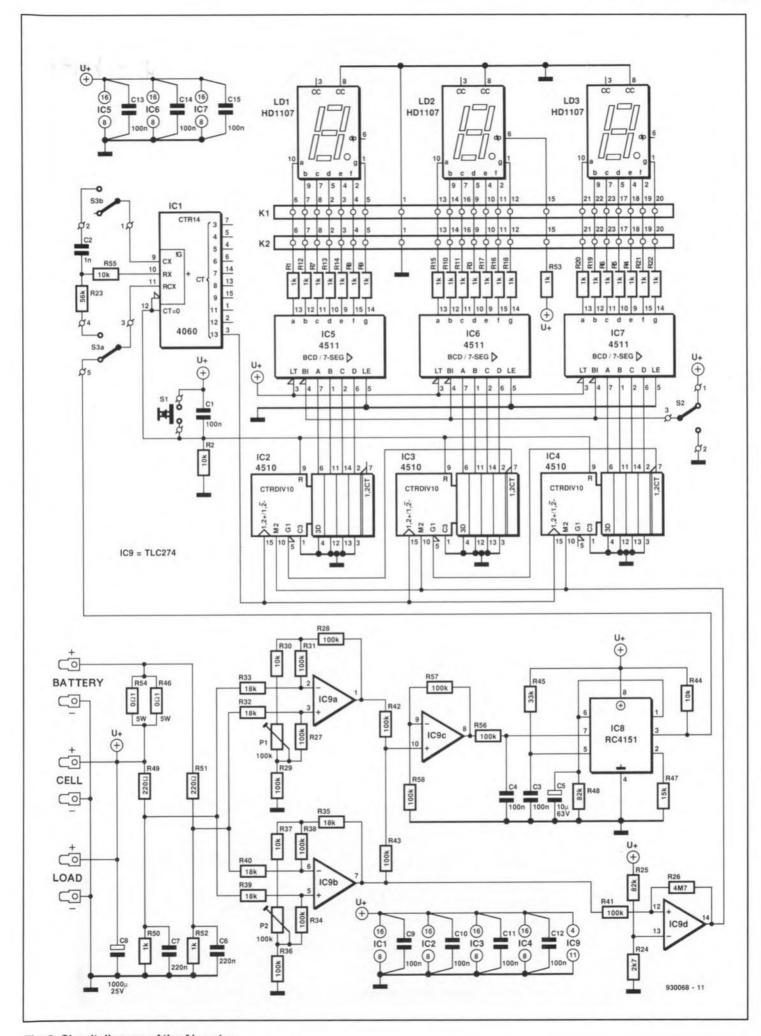

The battery, solar cell and load are connected to the circuit in **Fig. 3** by heavy duty connectors. The shunt resistor between battery and cell is formed by two parallel power resistors, R<sub>46</sub>-R<sub>54</sub>. If the maximum value of the current is assumed to be 10 A, the drop across the shunt resistor is 0.5 V. If the value of the shunt resistor were higher, the drop would be unacceptably

Fig. 2. Circuit of the RC4151 (IC8).

Fig. 3. Circuit diagram of the Ah meter.

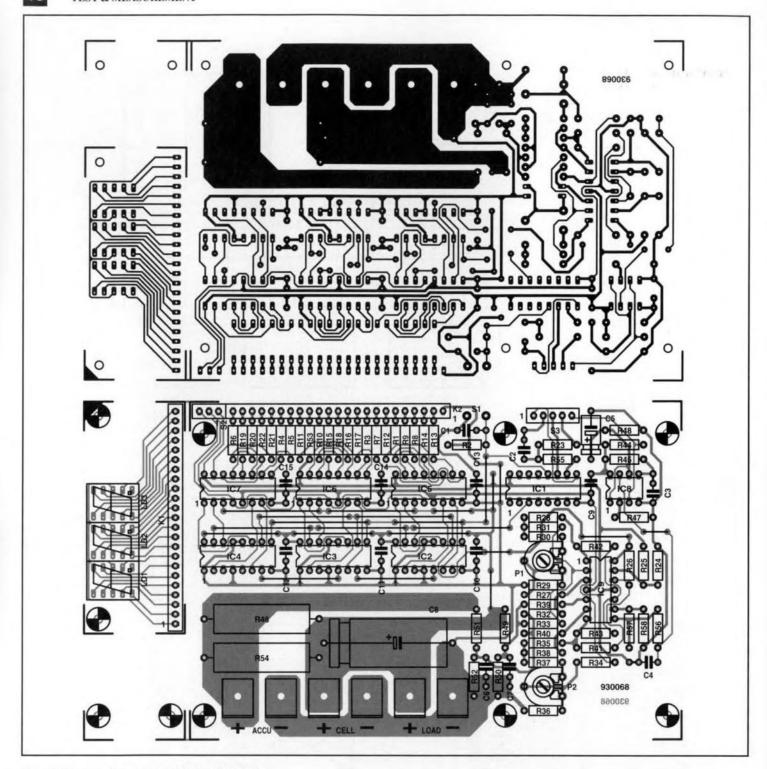

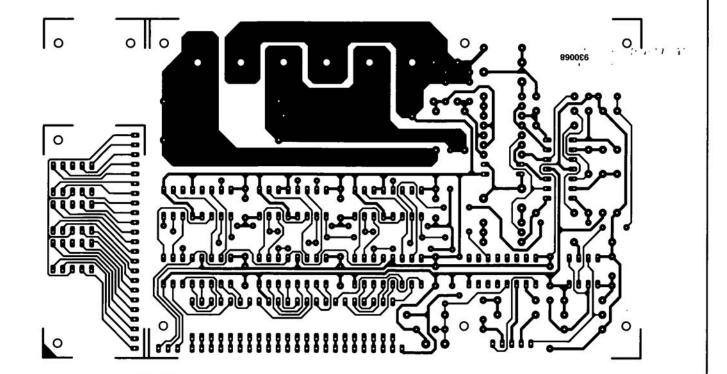

Fig. 4. Printed-circuit board for the Ah meter.

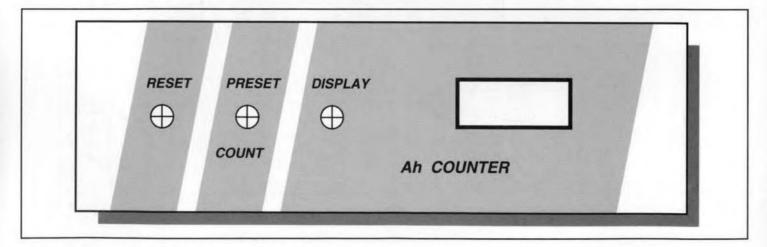

Fig. 5. Front panel foil for the Ah meter (see page 70).

high.

Potential dividers  $R_{49}$ - $R_{50}$  and  $R_{51}$ - $R_{52}$  reduce the common-mode voltage by about a fifth, so that the unregulated supply voltage which the meter draws from the battery or solar cell is always a little higher than the input voltage at one of the differential amplifiers. If the supply voltage is regulated, it is imperative that the differential input voltage, which in the present design is only four fifths of the drop across  $R_{46}$ - $R_{54}$ , that is, not more than 400 mV, cannot exceed the common-mode range of the opamps.

The accuracy of the measurement is not affected by the variable supply voltage, as long as this lies within the usual range of 10-14 V. By the way, the Ahmeter cannot be used with 24 V cells and batteries

Capacitor C<sub>8</sub> smooths the charging and

#### PARTS LIST

#### Resistors:

$R_1$ ,  $R_3$ – $R_{22}$ ,  $R_{53} = 1 \text{ k}\Omega$

$R_2$ ,  $R_{30}$ ,  $R_{37}$ ,  $R_{44}$ ,  $R_{50}$ ,  $R_{52}$ ,  $R_{55} = 10 \text{ k}\Omega$

$R_{23} = 56 \text{ k}\Omega$

$R_{24} = 2.7 \text{ k}\Omega$

$R_{25} = 22 \text{ k}\Omega$

R26-R29, R31, R34-R36, R38, R41-R43,

$R_{56}-R_{58} = 100 \text{ k}\Omega$

$R_{32}$ ,  $R_{33}$ ,  $R_{39}$ ,  $R_{40} = 18 \text{ k}\Omega$

$R_{45} = 33 \text{ k}\Omega$

$R_{46}$ ,  $R_{54} = 0.1 \Omega$ , 5 W

$R_{47} = 15 k\Omega$

$R_{48} = 82 \text{ k}\Omega$

$R_{49}$ .  $R_{51} = 2.2 \text{ k}\Omega$

$P_1$ ,  $P_2 = 100 \text{ k}\Omega$  preset potentiometer

#### Capacitors:

$C_1$ ,  $C_3$ ,  $C_4$ ,  $C_9$ – $C_{15}$  = 100 nF

$C_2 = 1 \text{ nF}$

$C_5 = 10 \,\mu\text{F}, 63 \,\text{V}$

$C_6$ ,  $C_7 = 220 \text{ nF}$

$C_8 = 1000 \, \mu F, 25 \, V$

#### Integrated circuits:

$IC_1 = 4060$

$IC_2-IC_4 = 4510$

$IC_5 - IC_7 = 4511$

IC<sub>8</sub> = RC4151 (Raytheon)

$IC_9 = TLC274$

#### Miscellaneous:

$S_1 = SPST$  switch

$S_2$  = spring-loaded, press-to-make switch

$S_3$  = double-pole, change-over switch

$LD_1-LD_3 = HD1107$

6 off 10 A, banana socket for chassis

mounting\*

6 off car-type spade terminal (male and female) for PCB mounting\*

2 off 23-way terminal strip, male

Enclosure, as required

PCB No. 930068 (see p. 70)

Front panel foil No. 930068F (page 70)

\* either of these are required, see text.

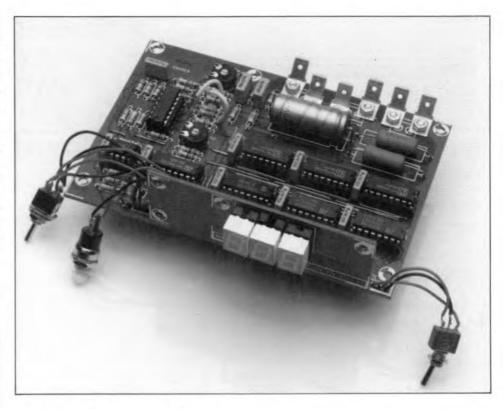

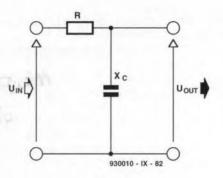

Fig. 6. Completed prototype without enclosure.

supply voltages so that voltage peaks cannot cause spurious measurements. Capacitors  $C_6$  and  $C_7$  short out any short spurious pulses at the inputs of the operational amplifiers.

The design of the differential amplifiers is traditional. Their amplification is about ×20, which gives a peak output voltage of around 8 V. The value of the resistors at the non-inverting inputs corresponds to that of the resistors at the inverting inputs. The common-mode rejection of a differential amplifier relies on the equality of these resistors. To avoid the necessity of costly close-tolerance resistors, the amplification factors can be adjusted with  $P_1$  and  $P_2$ . This also serves another function. It is well known that a battery must be charged with 40% more energy than can be drawn from it. If, for instance, it has been charged with a quantity of electricity of 1 Ah, only 715 mAh can be drawn from it. This means that the amplification of IC9a must be 1.4 times as large as that of IC9b.

As explained earlier, the polarity of the drop across the shunt resistor causes  $IC_{9a}$  to amplify when the battery is being discharged, and  $IC_{9b}$  when the battery is being charged. The output of the non-amplifying opamp is 0 V. Since both outputs are connected to the high-impedance, non-inverting (+) input of  $IC_{9c}$ , potential divider  $R_{42}$ - $R_{43}$  functions as if it were connected to ground. This means that the amplification of  $IC_{9c}$  is  $\times 2$ .

The output of  $IC_{9b}$  is also applied to Schmitt trigger  $IC_{9d}$ . As soon as the output of  $IC_{9b}$  reaches a certain level,  $IC_{9d}$  changes state (goes high). The output of  $IC_{9d}$  determines the direction of counting

of IC2-IC4.

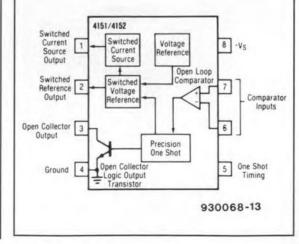

Reverting to the output of IC9c, this voltage, which is directly proportional to the charging/discharge current, is applied to voltage-controlled oscillator (VCO) IC<sub>8</sub>—see Fig. 2. The output of the comparator in this circuit drives a monostable multivibrator (MMV), which in its turn controls the switched current source, the switched voltage reference and the open-collector logic output transistor. When the voltage at pin 7 of IC8 exceeds that at pin 6, the comparator changes state and triggers the MMV. This stage then enables the current source, the voltage reference and the output transistor. It operates basically in the same way as the well-known Type 555 timer, in that it charges a capacitor (C3), which is connected to U+ via R45. The capacitor voltage is monitored at pin 5; as soon as this reaches 67% of the supply voltage, the mono time is terminated, upon which the capacitor is discharged immediately via a transistor.

During the mono time, the current source provides a current at pin 1 that is directly proportional to the reference voltage and external resistor R47. The switched voltage reference provides a potential of 1.9 V at pin 2, which is equal to fixed internal reference voltage. The open-collector transistor connects the output (pin 3) to ground. In other words, during the mono times, the switched voltage reference generates a positive voltage pulse; the current source generates a current pulse that is well defined in duration and amplitude; and the output transistor has transmitted a logic pulse that is compatible with most logic cards. All these signals are directly proportional to the level of the input voltage. When the mono time elapses, these three functions are disabled.

Circuit IC8 operates here in a standard application. The output of IC9c is applied to the non-inverting input of the comparator (pin 7) via a low-pass filter, R56-C4. The MMV operates as an oscillator since it is continuously triggered by the commonmode input voltage. The current source provides a current of  $U_{ref}/R_{47} = 40 \,\mu$ A for a time  $1.1 \cdot R_{45} \cdot C_3 = 3.63$  ms into integrating network R48-C5. Critical is the feedback of the integrator to the inverting input of the comparator (pin 6), which raises the pulse repetition rate until the average potential across the integrator is equal to the common-mode voltage at pin 7. The average voltage at pin 6 is directly proportional to the output frequency (and that at the opencollector output) since the quantity of charge in each current pulse is accurately controlled. In other words, the output frequency is directly proportional to the input voltage.

The external components determine the design parameters. The time constant of the output signal is the product of the mono time, the amplitude of the output current at pin 1, and the reciprocal of the current through the integrating resistor. From this, the formula for the output frequency,  $f_0$  is

$$f_0 = (U_{ref} / R_{47} \cdot R_{48} / U_{in} \cdot 1.1 \cdot R_{45} \cdot C_3)^{-1}$$

.

With component values as specified, this yields an output frequency of 212 Hz. This will be reverted to later on.

If any component values are altered, it should be noted that the value of  $R_{47}$  must be between  $12~k\Omega$  and  $20~k\Omega$ . Also, because

of the offset of the operational amplifier, it is not possible to obtain an input voltage of exactly 0 V. It does not pay to compensate the offset, because IC8 in its standard configuration operates correctly only from 10 mV onward in any case. The consequent error of 2 Hz (equivalent to <1% of full-scale deflection) is negligible compared with, for instance, that caused by the self discharge of the battery.

The output of the voltage-to-frequency converter is applied to divider  $IC_1$  via switch  $S_3$ . Divided by  $2^{13}$ , it is output at pin 13 and applied to cascaded CARRY OUT /CARRY IN binary-coded decimal (BCD) counters  $IC_2$ – $IC_4$ . Pressing  $S_1$  sets the counters (and the divider) to 0. Note that  $R_{23}$ ,  $R_{55}$ , and  $C_2$  serve no useful function in normal operation.

The counting direction inputs of  $IC_2$ – $IC_4$  are driven by  $IC_{9d}$ . Note that the preset inputs are not used. The outputs of the counters are fed to BCD-to-7-segment decoders  $IC_5$ – $IC_7$ . The decoders control the 7-segment LED displays  $LD_1$ – $LD_3$ .

During normal operation, the displays are not on, since the Bl(anking) inputs of the decoders are at ground potential via S<sub>2</sub>. It is advisable to use a spring-loaded switch here, so that the display cannot be left on inadvertently. Note that the right-hand decimal point is always on, however, to show that the meter is functioning.

To ensure that the display increases from 00.0 to 10.0 when a constant current of 10 A has flown for 1 hour, the counters need 100 pulses per hour or 100/3600 pulses per second. This means that the VCO must generate a signal at a frequency of  $100/3600.2^{13} = 227.56$  Hz. Working back, this means that the VCO needs an input

of 8.58 V. Since the differential input voltage is fairly accurately 410 mV when a current of 10 A flows through the shunt resistor, the differential amplifier must have an amplification of 8.58 / 0.41 = 20.9.

Owing to component tolerances and other imponderables, the potentiometers should be preset empirically. This is done by connecting the positive output of an accurate  $500 \, \text{mV}$  source to the '+ battery' terminal, and the negative output to the '+ cell' terminal. Turn  $P_2$  until a frequency counter at the output of (pin 3) of  $IC_8$  shows  $228 \, \text{Hz}$ . Then reverse the connections of the voltage source and adjust  $P_1$  until the display reads  $1/1.4 \cdot 228 = 163 \, \text{Hz}$ .

The display is checked by switching into circuit (with  $S_3$ ) components  $R_{23}$ ,  $R_{55}$ , and  $C_2$ . This actuates an RC oscillator in IC<sub>1</sub>. If everything is all right, the display will fairly quickly give a high reading. This position of  $S_3$  is also for presetting a given counter state when, for instance, the Ah meter is connected to a fully charged battery.

#### Construction

The printed-circuit board in **Fig. 4** can, if desired, be cut into two to enable the displays to be mounted at an angle behind the front panel. Otherwise, fit them in IC sockets so that they protrude above the other components. The 23-way terminal strips,  $K_1$  and  $K_2$ , must be used in both cases.

Use car-type insulated spade terminals (male and female) for 'battery', 'cell' and 'load'. If, however, the meter is given its own enclosure, use the 10 A chassismounted banana sockets specified in the parts list.

END

# FUZZY LOGIC MULTIMETER (PART 2) H. Scholten

There is little to say about the true-r.m.s. converter. The circuit diagram (Fig 5) shows a standard application of the AD736JN, connected to a non-critical *R-C* network, C4-R15, and three electrolytic capacitors (also uncritical), C5, C6 and C7. The bandwidth of the true-r.m.s. converter exceeds that of the multimeter IC input by far. In fact,

the multimeter IC limits the -1%-bandwidth of the DMM to about 300 Hz. Keep this in mind when measuring signals with a lot of distortion (i.e., containing many higher harmonics), because for the measurement to be accurate, the strongest harmonics have to fall within the 300-Hz bandwidth of the DMM.

The multimeter power supply is relatively simple, consisting essentially of a 5-V regulator, IC10, and an inverter, IC3. Jumpers JP16 and JP17 are remnants of the experimental phase of the circuit, and determine where the analogue and digital ground are interconnected. On the final design of the printed circuit board, JP16 is a

| ADDRESS OR<br>REGISTER NUMBER | REGISTER NAME | REGISTER CO   | ONTENTS                                              |         |             |

|-------------------------------|---------------|---------------|------------------------------------------------------|---------|-------------|

| 0                             | Ones          | Conversion Re |                                                      |         |             |

|                               |               |               | east significant digit                               |         |             |

|                               | Tens          |               | ved digit used fot digital autoz<br>onversion Result | ero)    |             |

|                               | lens          |               | ant displayed digit)                                 |         |             |

| 2                             | Hundreds      |               | onversion Result                                     |         |             |

| 3                             | Thousands     | BCD Data of C | onversion Result                                     |         |             |

| 4                             | 10 Thousands  | BCD Data of C | onversion Result                                     |         |             |

| 5                             | Status        | D3            | D2                                                   | D1      | DO          |

|                               |               | Always 1      | Latches Continuity                                   | Holding | Low Battery |

| 5                             | Status        |               |                                                      | -       |             |

| ADDRESS OR      |         |                |               |           |

|-----------------|---------|----------------|---------------|-----------|

| REGISTER NUMBER | D3      | D2             | D1            | DO        |

| 0               | Hold    | High Frequency | Beeper ON     | Sleep     |

| 1               | 10-0    | Filter Short   | ÷5            | 50Hz      |

| 2               | 10-4    | 10-3           | 10-2          | 10-1      |

| 3               | DC      | Ext AC         | Divider Sense | Ohms R/2  |

| 4               | Current | X2             | Read Zero     | Filter On |

| BIT SET | VOLTAGE<br>RANGE | OHMS<br>RANGE |

|---------|------------------|---------------|

| 10-0    | 400mV            | 4M and 40M    |

| 10-1    | 4V               | 400 kΩ        |

| 10-2    | 40V              | 40 kΩ         |

| 10-3    | 400V             | 4kΩ           |

| 10-4    | 4000V            | 400Ω          |

| MEASUREMENT RESULT | BCD DATA |

|--------------------|----------|

| + 40000            | 40000    |

|                    | -        |

| +00100             | 00100    |

|                    |          |

| +00001             | 00001    |

| 00000              | 00000    |

| -00001             | 99999    |

| -                  | _        |

| -40000             | 60000    |

| FILTER ON | FILTER SHORT | FUNCTION                                                                                        |

|-----------|--------------|-------------------------------------------------------------------------------------------------|

| 1         | 0            | Normal filter on condition                                                                      |

| 1         | 1            | Filter on, RFILTERI is bypassed. Use this bit combi- nation to compensate for the higher source |

|           |              | Impedance of the 4V range.                                                                      |

| 0         | 1            | Bypasses the Filter.                                                                            |

| 0         | 0            | Invalid combi-<br>nation, do not use                                                            |

Table 1. Overview of data contained in the MAX134 registers.

| A14                                      | A13 | A12              | A11            | A10                           | A9 A8 A7 A6 A5 A4 A   | A2 A1 A0 PC address line                                         |

|------------------------------------------|-----|------------------|----------------|-------------------------------|-----------------------|------------------------------------------------------------------|

| R4                                       |     | R3               | K0 -           | K7                            |                       | R2 R1 R0 MicroSystem                                             |

| card card address<br>register<br>address |     | ress             | PC I/O address | register<br>address<br>MAX134 |                       |                                                                  |

| R4                                       | R3  | R2               | R1             | R0                            | read                  | write                                                            |

|                                          | 0   | 0                | 0              | 0                             | units                 | input data (see table 1)                                         |

| 0                                        |     |                  | 0              | 1                             | tens                  | input data (see table 1)                                         |

| -                                        | 0   | 0                | U              | ,                             |                       | 7779                                                             |

| 0                                        | 0   | 0                | 1              | 1                             | hundreds              | input data (see table 1)                                         |

| 0                                        | 0   | 0                | 1 0            | 1 0                           | hundreds<br>thousands |                                                                  |

| 0                                        | 0   | 0 1 1            | 1              | 1 0 1                         |                       | input data (see table 1)                                         |

| 0                                        | 0   | 0<br>1<br>1<br>x | 1              | 1<br>0<br>1<br>x              | thousands             | input data (see table 1)<br>input data (see table 1)             |

| 0                                        | 0   | 0<br>1<br>1      | 1<br>0<br>0    | 1                             | thousands<br>status   | input data (see table 1)<br>input data (see table 1)<br>not used |

Table 2. Addressing standard adopted for the MicroSystem bus/DMM card combination.

jumper, and JP17 must never be fitted. That leaves JP14 in the power supply section. JP14, together with JP10 on the PC interface board, selects the source of the supply voltage. The available options are: (1) the computer's 12-V supply, (2) an external 12-V supply connected to K2 on the interface board, or (3) an external power supply connected to the DMM board (between points U<sub>x</sub> and 0).

The design of the digital output section is simplicity itself. Data is clocked directly from the databus into two eight-bit registers, IC4 and IC9. The clock signal is supplied by address decoder IC6, which is controlled by register address lines R3 and R4 (more about this further on). Six bits of IC9 are reserved for internal use. The first bit (pin 19), is used as a software-controlled interrupt enable switch. Thus, the interrupt generated by the DMM on completion of the conversion cycle may be blocked (disabled) either by removing JP13, or by setting the first bit in IC9. If this bit is at 0, NAND gate IC5b no longer feeds the EOC (end-ofconversion) signal supplied by IC1 to transistor T1. The second bit is used to control a LED, D6, which forms a 'software activity' indicator and has, strictly speaking, nothing to do with the function of the DMM card. As long as the LED flashes, you are assured that the PC is talking to the DMM card.

The remaining bits in IC9 are all fed to driver IC11, which is capable of handling far more output current than the average HCT gate. Four bits are used to control relays in the multimeter's input circuit. These bits are also suitable for controlling bistable relays, which have two coils. The advantage of a bistable relay is that it has to be energized only to switch over the contacts, which automatically remain in the new position. This means that a bistable relay does not require a con-

stant current to keep its contacts in a certain position. The advantage is obvious: reduced current consumption. Unfortunately bistable relays are still relatively expensive as well as hard to find as one-offs, and that is why normal, monostable, relays appear in the components list. The control software also assumes that monostable relays are used.

The inputs of drivers 7 and 8 in IC11

may be connected in parallel with driver 6 or 5 by fitting jumper JP11 and JP12 respectively in position 'A'. The parallel connection is useful where two lines are always controlled simultaneously under the control of one bit at one address. If jumpers JP11 and JP12 are set to position 'B', drivers 7 and 8 are controlled separately via two bits of IC4.

The DMM chip, IC1, is controlled via latch IC7 and databus buffer IC8. It was already seen from Fig. 4 that the register addresses of IC1 have to be stable quite a while before data can be read or written. This is achieved by the following trick. Each time a register is addressed in IC1 (R2/R4=00B), address decoder IC6 clocks the register address (R0/R1/R2) in latch IC7. If the desired register address is read first, and the data simply forgotten, the latch will ensure that the address remains stable on the address inputs of IC1. After 3.5 µs, the same register may be addressed again, and data may be read or written.

Address decoder IC6 has a crucial function in the write and read actions to and from the card. It is enabled via the PC interface by the strobe signal and one of the card selection lines en-

|    |                    |                      | -   |                                            |            |        |

|----|--------------------|----------------------|-----|--------------------------------------------|------------|--------|

|    |                    | COMPON               | ENT | rs List                                    |            |        |

| DI | MM BOARD           |                      | 11  | 10pF                                       | C14        |        |

|    |                    |                      | 4   | 100μF 16V radial                           | C20-C23    | 3      |

| Re | sistors:           |                      | 1   | 1pF                                        | C24        |        |

| 2  | 1kΩ 0.1%           | R1;R5                |     |                                            |            |        |

| 2  | 10kΩ 0.1%          | R2;R6                | Se  | miconductors:                              |            |        |

| 1  | 100kΩ 0.1%         | R3                   | 4   | BYV27-100                                  | D1-D4      |        |

| 1  | 1M1 0.1%           | R4                   | 1   | ICL8069C                                   | D5         |        |

| 2  | 301kΩ 1%           | R7;R8                | 1   | LED, red, high-effic                       |            | )      |

| 1  | 1M2 1%             | R9                   | 1   | BC547B                                     | T1         |        |

| 1  | 1M 1%              | R10                  | 1   | MAX134CPL                                  | IC1        |        |

| 1  | 10MΩ 1%            | R11                  | 1   | AD736JN                                    | IC2        |        |

| 1  | 332kΩ 1%           | R12                  | 1   | ICL7660CPA                                 | IC3        |        |

| 2  | 10kΩ               | R13;R14              | 1   | 74HCT08                                    | IC5        |        |

| 1  | 22ΜΩ               | R15                  | 1   | 74HCT138                                   | IC6        |        |

| 2  | 1Ω5                | R16;R21              | 3   | 74HCT574                                   | IC4;IC7;   | IC9    |

| 1  | 2Ω2                | R17                  | 1   | 74HCT245                                   | IC8        |        |

| 1  | 1kΩ2               | R18                  | 1   | 7805                                       | IC10       |        |

| 1  | 2kΩ2               | R19                  | 1   | ULN2803                                    | IC11       |        |

| 1  | 1Ω 1%              | R20                  |     |                                            |            |        |

| 1  | 3kΩ3               | R22                  | Mi  | scellaneous:                               |            |        |

| 1  | 4kΩ22 1%           | R23                  | 1   | Passive AC buzzer                          |            | Bz1    |

| 1  | 5kΩ11 1%           | R24                  | 1   | Multifuse 0.4A/50V                         |            | F1     |

| 1  | 100kΩ multiturn pr | eset P1              | 1   | 14-way box header                          | , angled   | K1     |

|    |                    |                      | 1   | 34-way header, and                         | gled, side |        |

| Ca | pacitors:          |                      |     | latches                                    |            | K2     |

| 1  | 4nF7 MKT           | C1                   | 1   | PTC max. 2kΩ                               |            | PTC1   |

| 2  | 22nF               | C2;C3                | 1   | 32.768kHz crystal                          |            | X1     |

| 9  | 100nF              | C4;C9;C10;           | 2   | V23042-A1001-B10                           | 1 relay    |        |

|    |                    | C12;C13;C15;         |     | (Siemens)                                  | Re         | 1;Re2  |

|    |                    | C16;C18;C19          | 1   | Printed circuit board                      |            |        |

| 1  | 33μF 16V radial    | C5                   | 1   | order code 920049                          | -1 (see pa | ge 70) |

| 5  | 10μF 16V radial    | C6;C7;C8;C17;<br>C25 |     | e control software is parately: order code |            |        |

| 1  | 22µF 16V radial    | C11                  | 70  | )                                          |            |        |

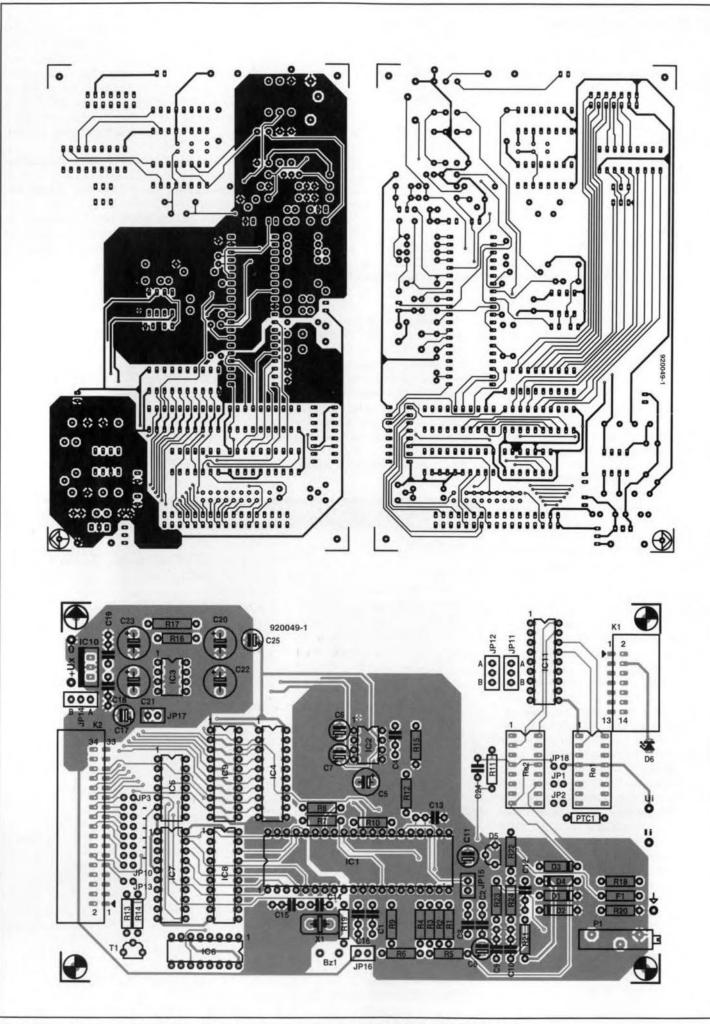

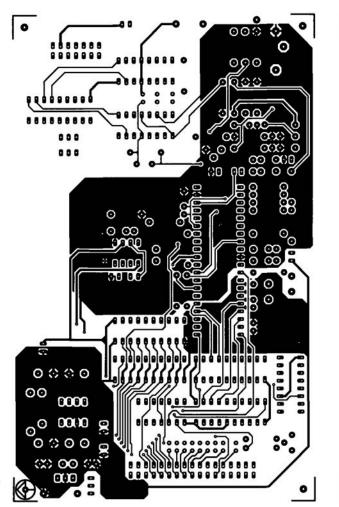

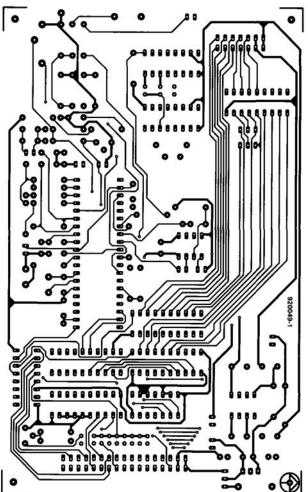

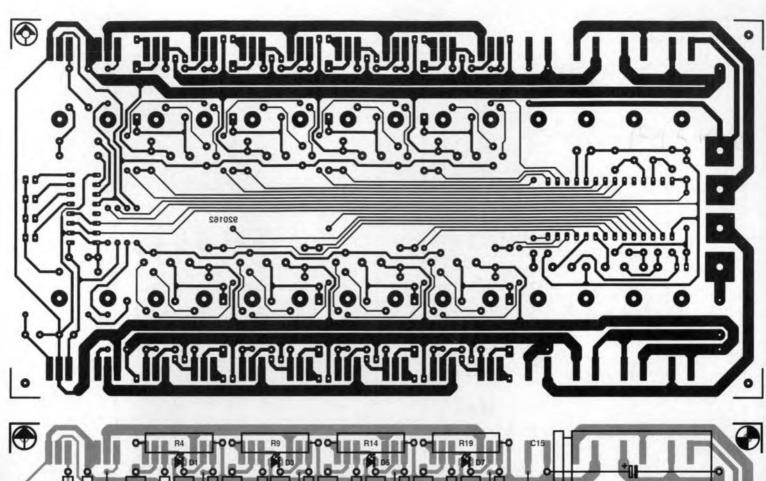

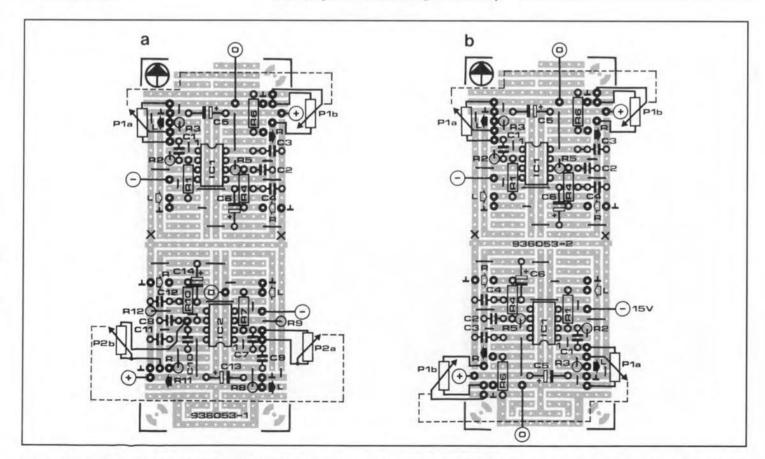

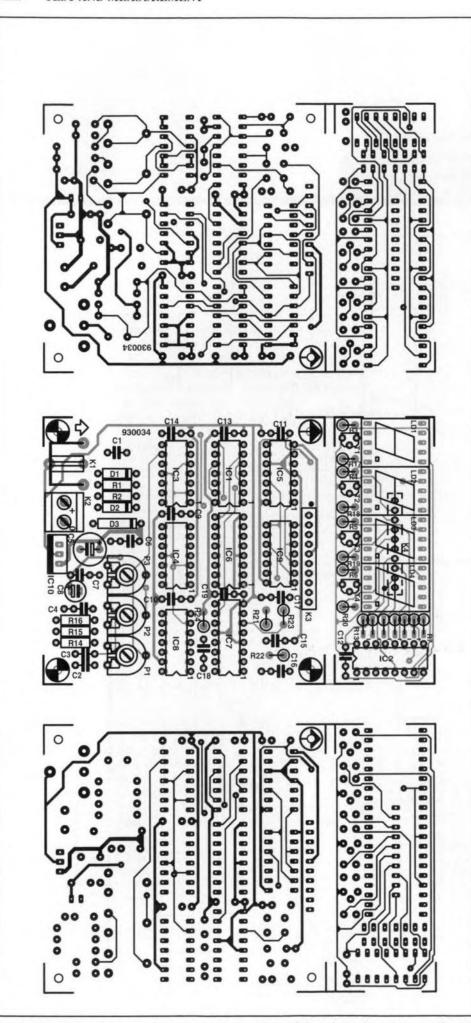

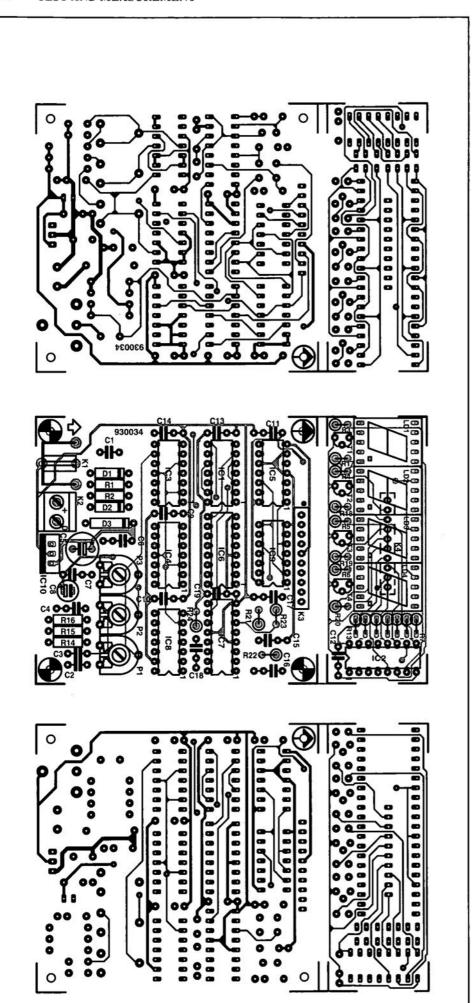

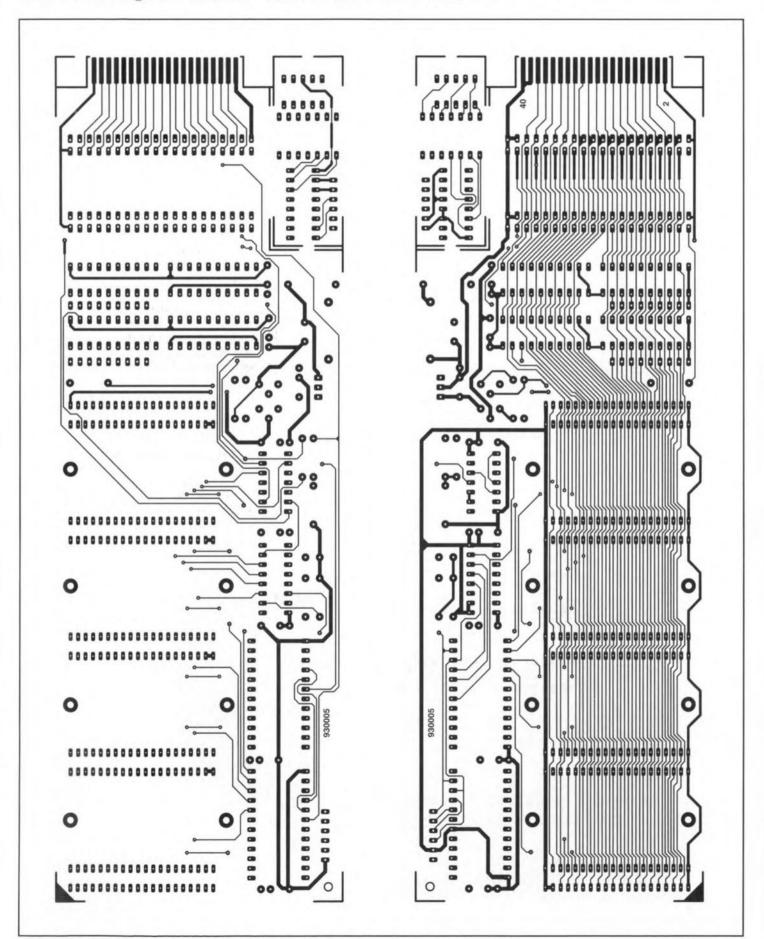

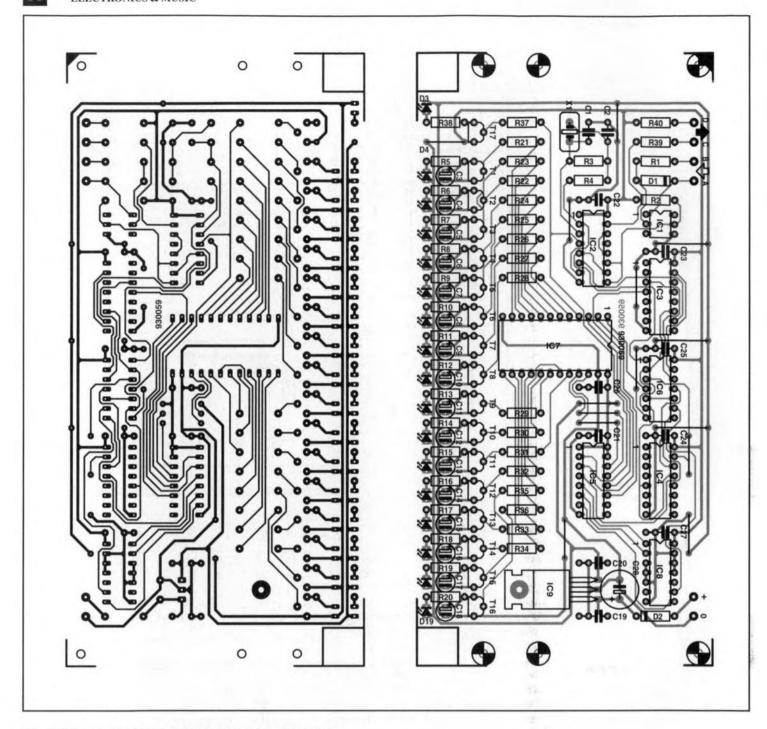

Fig. 6. Track layouts (reduced to 80% of true size) and component mounting plan for the DMM board.

#### Jumpers/ switches on PC interface card: Jumpers: JP1-JP7; JP11-JP14: open (interrupts not used) JP8: open (no clock required for DMM IC) JP9: ground (CHRDY on slot = HIGH) DIP switch S1: S1-1 - S1-5: on. S1-6: off. Sets card base address to 300H. Jumpers on DMM card: JP1: closed JP2: open JP3-JP9: open JP10: closed (DMM = card 0) JP11: see text JP12: see text JP13: open (interrupts not used) JP14: U JP15: closed (filter effective) JP16: closed

Table 3. Default settings of the jumpers and the DIP switch.

JP17: open (never close!)

JP18: open

abled via jumpers JP3-JP10. IC6 accomplishes the final addressing with the aid of lines R3, R4 and write. Together with R0, R1 and R2, this gives the addressing shown in Table 2.

The final section of the multimeter circuit to be discussed is the measurement circuit around IC1. The components vital for correct measurement results are resistors R1-R6 and R11, since they determine the resistance and voltage ranges. Unlike R1-R6, R11 is a 1% resistor. A 0.1% type would, of course, be preferred, but proved unobtainable for the value required (10 M $\Omega$ ). Fortunately, the error (if any) introduced by the higher tolerance on R11 is compensated by calibration preset P1. Tolerance compensation is not available for R1-R6, so any deviation from the stated resistance values causes inevitable differences between the ranges. These differences are kept to a minimum by using 0.1% resistors.

Nearly all switches required for switching between the various ranges are available in IC1. There is, however, one exception. To be able to use the meter as an ohmmeter, the input circuit has to be modified. Junction R1-R2-R5-R6 is usually connected to ground via relay contact Re2. For resistance measurements, R11 has be connected to this junction also. This is achieved by energizing Re2. The junction is then also connected to the 400mV input of IC1 via PTC1. Together with diodes D3 and D4, the PTC protects the ohmmeter against high voltages (sparks and discharges) at the input terminals. To make sure that the PTC can not affect the lowest resistance range, its value may not be smaller than 2 kΩ under normal circumstances. Finally, for resistance measurements, input terminal U, has to be connected to the 400-mV input. This is accomplished by relay Re1, which is also used to connect Ui to the 400-mV input to create the 400-mV range of the multimeter. Jumpers JP1 and JP2 are intended to adapt the input circuit to different types of relay. In most cases, JP1 will be fitted. Jumper JP18 allows relays Re1 and Re2 to be shunted (in which case the relays may be omitted), which forfeits the resistance measurement function of the DMM, leaving the current and voltage (both AC and DC) only. Omitting the ohmmeter function is an option where resistance measurements are not required anyway.

#### Construction

The artwork for the DMM board (double-sided, through plated) is shown in Fig. 6. Like the PC interface card, this board is available ready-made through the Readers Services. Although construction is straightforward, great attention should be paid to neat and accurate solder work. Remember, one bad solder joint at a crucial point may reduce the accuracy of the meter considerably.

Important notice: although the DMM IC has a 4,000-V range, the printed circuit board is not suitable for such a high voltage. This range is, therefore, not available in software. If you write your own software for this circuit, you must not attempt to use the 4,000-V range. The PCB can withstand the mains voltage (220 or 240 V), but always check if the ground of the PC is separated from the mains earth. If the two are connected, swapping the live and neutral lines, although unlikely given their fixed positions on UK style mains plugs and sockets, may cause a short-circuit with disastrous results.

For the time being, preset P1 may be set to the centre of its travel. If you wish, you may want to adjust it for 655 mV measured with a voltmeter. However, before you can start testing the two boards, make the bus cable, and fit the jumpers. The standard jumper settings are given in Table 3. Settings other than the ones shown must be communicated to the program (this is explained in the help texts).

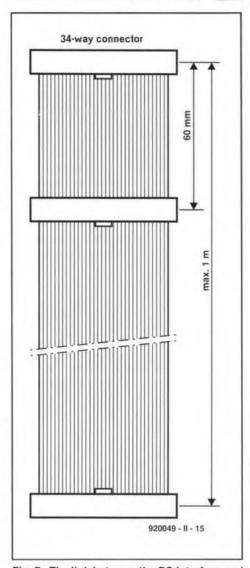

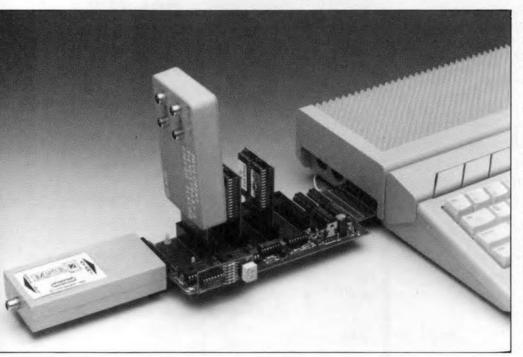

The construction of the 34-way flatcable is simple — see Fig. 7. Although a maximum length of 1 m is indicated, our prototypes gave no problems with cables of up to 1.5 m long. Both cable ends are fitted with an IDC (insulation displacement) socket. If you intend to use more than one DMM card, additional sockets may be pressed on to the cable as illustrated in Fig. 7. The

Fig. 7. The link between the PC interface and the I/O card is a bus formed by a length of flatcable. The number of connectors pressed on to the cable depends on the number of cards you wish to connect.

distance between the sockets should be about 6 cm. Finally, check the continuity of all 34 connections.

#### Software

The DMM does nothing without the appropriate software. Fortunately, this is available on a diskette for IBM PC-ATs (and up) running under MS-DOS. The control software package is called 'Fuzzy Control One', and has been produced by MicroSource. The introduction version of this program is available through our Readers Services, while the full version may be obtained from MicroSource only. As already indicated by its name, the program is tailored to developing control systems using fuzzy logic (Ref. 1). In spite of the designation 'introduction version', all features are available for use - more about this in next month's concluding instalment of this article.

For now, the part of the program that contains the multimeter software is of interest. Originally, the multimeter was intended as an aid in setting up fuzzy logic control systems. It grew, however, into a fully fledged measuring instrument.

The GUI creation routines are the only ones actually used from the 'LabWindows' package to develop the Fuzzy Control One software. Attention: LabWindows has nothing to do with MicroSoft Windows! Our thanks are due to National Instruments for allowing us to put Fuzzy Control One on floppy disk without having to raise a licence fee for every user. This means that the Fuzzy Control One software is not dearer than most other programs

sold through our Readers Services.

It can not be denied that Fuzzy Control One, despite being an 'introduction version', is a very complex program, which requires quite a bit of getting used to. The range of settings and options offered by the program to implement a fuzzy logic control system is staggering, and make the program one of a kind. Documentation is not lacking, either: the total size of the help files alone would easily fill all the pages of this magazine! Incidentally, the help files can be printed, so a manual is readily produced.

A couple of batch programs containing useful examples are supplied to get you going. One of these files, DVM.BAT, launches the multimeter software. Installation is easy: simply start the INSTALL batch, and follow the instructions. After installation, the program always shows the help text when the multimeter is started. This can be turned off by quitting the multimeter and returning to the main menu. Select 'preferences'\* from the 'Miscellaneous' menu. After quitting the help text on this part of the program you can turn off the option 'start with help'. To save this setting, store it in the file DVM.FZH. This is done via the 'files' and 'save hardware settings' menus.

The main menu also has an option called 'print data', which enables you to produce hard copy of the help texts (first, however, ascertain the printer port in the same menu).

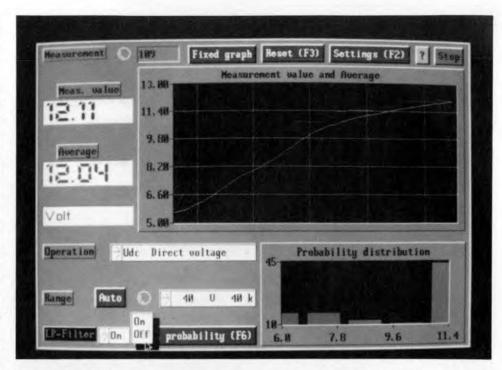

After starting the multimeter program, you are eventually presented with a screen that contains the following information: current measurement value, average value measured over a predefined number of samples (both values are displayed numerically in a graph), the set measurement range, the type of measurement, the number of measurements used to compute the average ('filter length'), and a histogram that shows the variance of the measurement values contained in the

Fig. 8. It is the DVM software contained on the Fuzzy Control One diskette that turns the combination of the DMM card and the PC into a digital multimeter with some astounding functions. Routines from LabWindows handle the graphics presentation of the measurement data, affording ease of program operation (using the mouse).

filter, or in a memory containing 100 measurements. In this way, you obtain information on the measurement value proper, its trend and stability. A number of meter settings can be changed by pointing the cursor at the relevant button and clicking on it. One button determines the rate of zero measurements performed by the instrument. This is necessary to compensate the internal offset of the DMM chip. The software has to deduce the result of the zero measurement from the current measurement value to obtain the real value. Another setting made via this window is 'software calibration', which allows the scale of the DMM to be adapted without having to redo the calibration of the DMM card itself.

The 'preferences' menu also allows you to select the mains frequency (50 Hz or 60 Hz). As already discussed, the reference voltage on the DMM board depends on this frequency, and it is vital to make the selection equal to the mains frequency used in your country. If the set mains frequency is changed, the DMM card has to be calibrated again.

#### Calibration

Once you have familiarized yourself a little with the control software, the meter is ready for calibration. For some applications it is sufficient to set P1 to the centre of its travel. For in-

stance, if you intend to change the calibration via software. However, if the meter is to measure 'real' volts, ampères and ohms, P1 has to be set more accurately. All you need for this purpose are a stable voltage of (nearly) 3.999 V, and an accurate voltmeter (min. 3% digit, and having an accuracy better than that of the DMM). Connect the test voltage to the DMM inputs, and set the meter to the 4-V range (i.e., autoranging function switched off). To prevent overflow, the input voltage has to stay just under 4 V. The adjustment of P1 is simple: turn the wiper until the DMM reads the same value as the voltmeter you have connected in parallel. That is all! All other ranges are then automatically calibrated.

Next month's instalment will discuss the Fuzzy Control One software in greater detail, along with an example of a fuzzy logic control system that makes use of the multimeter described here.

#### Reference:

1. Fuzzy logic: an introduction. *Elektor Electronics* July/August 1992.

Fuzzy Systems and MikroSysteem (MicroSystem) are registered trademarks of MicroSource/H. Scholten, P.O. Box 1243, 8001 BE Zwolle, Holland.

LabWindows a is registered trademark of National Instruments.

<sup>\*</sup> names of menus and menu options mentioned in this article may be different from the actual names used in the program.

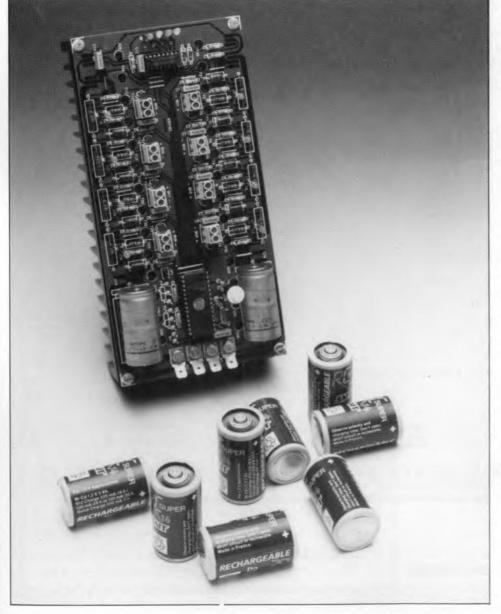

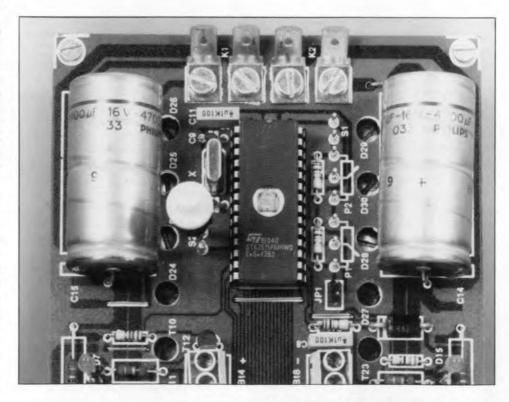

## MICROCONTROLLER-DRIVEN NICO BATTERY CHARGER

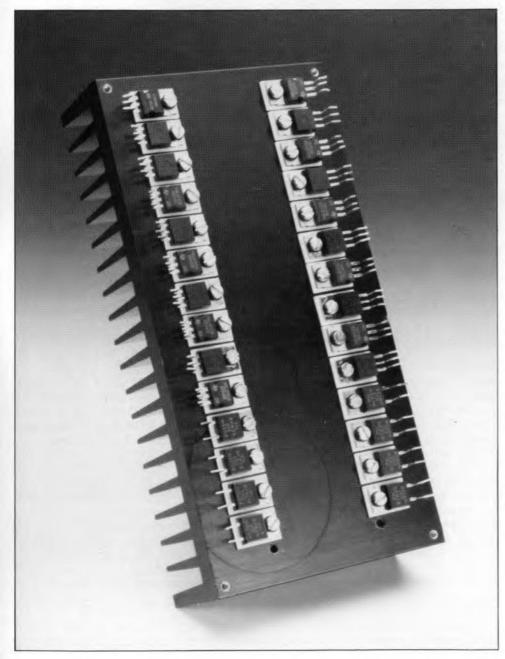

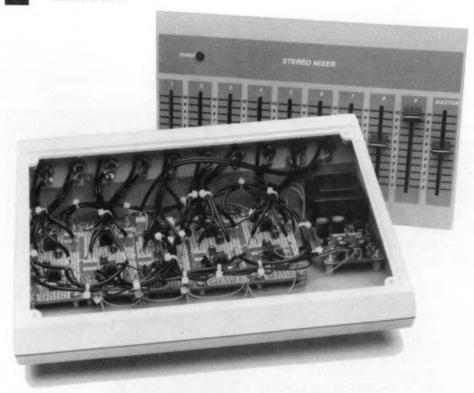

This nickel-cadmium (NiCd) battery charger is capable of charging up to eight cells individually. The power semiconductors needed to accomplish this are all fitted on to a single, large, heatsink, to which the printed circuit board is also secured. That saves 84 wires.

#### Design by A. Rietjens

THERE are many methods of charging a nickel-cadmium battery. The method used by the present circuit is probably the best: first, discharge the battery, then charge it for a certain period, and, finally, trickle-charge it.

Although there are more chargers that operate on this basis, you will rarely find one that offers continuous adjustment, over a wide range, of the battery capacity and the average charging current. That is a feature uniquely offered

by the present charger, which enables you to charge a wide variety of batteries. It must be noted, however, that the batteries which are charged at the same time must have the same nominal capacity. Remarkably, the set charge current is achieved by applying short pulses at the maximum charging current. This ensures good efficiency of the charging process, while the combination with the discharging periods helps to counteract the so-called memory effect. In addition to controlling the charging process, the charger also has a monitoring function. The charging of a battery is stopped the moment the cell voltage rises to a too high value.

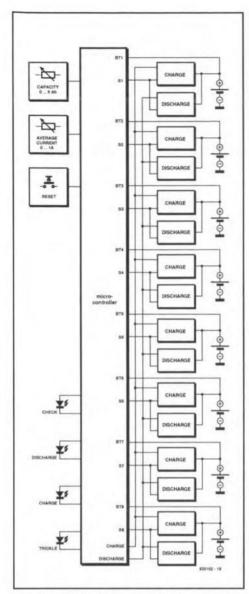

#### 8 + 1 = 8

The block diagram of the microcontroller-driven NiCd battery charger is given in Fig. 1. The unit consists, broadly speaking, of eight charging circuits and a microcontroller. Each charging circuit (which is divided into a charging and a discharging circuit) handles one NiCd cell (1.2-V battery). The controller is capable of detecting whether a battery is connected or not. If so, it checks the condition of that battery via analogue inputs BT1-BT8 and an on-chip A-D converter. If a battery is detected that needs to be discharged first, the discharging function of the relevant circuit is enabled with the aid of outputs S1-S8. Any time a battery is sufficiently discharged, the associated charging circuit is switched off. When all batteries connected are discharged, the charging circuits are selected and switched to charging.

The desired charging current and the battery capacity are adjusted beforehand by two potentiometers. Like the battery voltage, the setting of these potentiometers is measured by the A-D converter on board the microcontroller. The reset button on the unit is used to signal that a set of batteries has been installed, and that the charging process must begin again.

Four LEDs indicate what the charger is doing. After a reset, the controller starts by checking all eight battery connections. In fact, it checks if a battery is present. If so, the next check is the level of discharging. During this check, the 'CHECK' LED is on. If there are batteries that need to be discharged, this is indicated by the 'DISCHARGE' LED. Another LED, marked

Fig. 1. Block schematic of the microcontroller-driven NiCd charger.

'CHARGE' lights when all batteries are charged. The 'TRICKLE' LED, finally, lights to indicate that the batteries are kept 'topped up' by a trickle-charging current.

#### Charging/discharging current and battery voltage

Neither the charging nor the discharging current flows continuously through the battery. This is because the current sources are set to fixed values. The only way of making the (average) current adjustable is, therefore, to give current pulses with an adjustable pulse duration. To generate these pulses, the microcontroller places an appropriate pulse on the 'charge' or 'discharge' control line.

Making the charging current adjustable is not the only reason to opt for current pulses: the pauses between the pulses allow the microcontroller to measure the battery voltage. This can be done without losses introduced by

#### MAIN SPECIFICATIONS

- Charges up to eight NiCd batteries (1.2 V) simultaneously.

- If necessary, batteries are individually discharged.

- Individual monitoring of battery voltage.

- Adjustable charging current: 0-200 mA, 0-1 A, or

- 0-100 mA, 0-500 mA 0-10 Ah or 0-5 Ah, or

- Adjustable capacity:

0-10 A

- 0-2.5 Ah

- Trickle charging at 1/6th of nominal charging current

- Charging current indicator (LED) for each battery

- Charger state indication using 4 LEDs

- Microcontroller driven

- No adjustments

wires and contacts, since, theoretically, no current flows during the measurement. One complete cycle (current pulse followed by a pause during which the battery voltage is measured) lasts about 2.5 seconds.

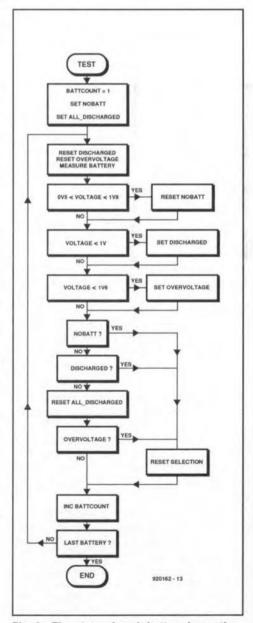

The different steps into which the test procedure may be divided are shown in the flow diagram, Fig. 2. Each time the procedure is called, the voltage on all battery stations (whether 'occupied' or not) is measured. The variable 'BATCOUNT' indicates the number of the battery station (connection) whose voltage is measured. The state of each output is recorded with the aid of five variables. Three voltage ranges are set up to determine what is connected to the battery terminals. If the voltage is between 0.5 V and 1.8 V. the controller assumes that a battery is connected. If the voltage is between 0.5 V and 1 V, the battery is assumed 'flat'. Finally, if the voltage is greater than 1.6 V, it is assumed to be too

The results are evaluated after these three measurements. From a point of view of logic, this part of the flow diagram is not complete. Not shown are the small differences in the charging level assessment, which depend on the state of the charger (check; discharge; charge or trickle). For instance, while in 'charge' mode, it is not necessary to check if the batteries are discharged, since that has already been done. Once the state of a battery at one of the terminals has been measured, the software continues with the next one, until all have been checked. Only then does the next charging cycle begin, taking into account the result of the test routines for each individual battery.

#### 16 current sources and one microcontroller

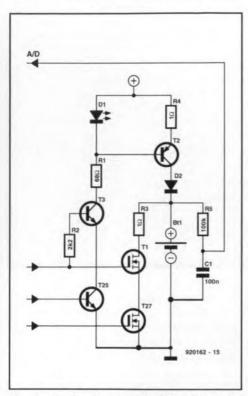

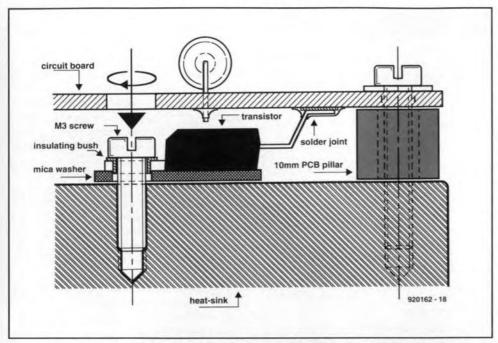

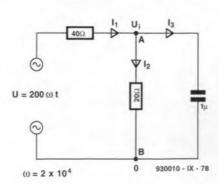

Before discussing the complete circuit diagram, we first examine the operation of one charging/discharging circuit — see **Fig. 3**. Transistors T25 and

T28 are common to all eight charging/discharging circuits, and serve to switch between these two functions. Each circuit is individually switched on and off by the 'select' line. The bat-

Fig. 2. The state of each battery is continuously checked during the entire charging operation.

Fig. 3. Basic charging/discharging circuit. The unit has eight of these.

tery voltage is measured by the microcontroller via filter R5-C1. To discharge the battery, the 'select' and 'discharge' lines have to be high simultaneously. The discharging current then flows via resistor R3 (which limits the current to about 1 A), and MOSFETs T1 and T27.

If the 'select' and 'charge' lines are high, current source D1-T2-R4 is switched on, and current is supplied to the battery. LED D1 has two functions. Firstly, the voltage across it is the reference for current source T2. Secondly, it serves as a 'charge' indicator because it flashes when the relevant battery is being charged. D1 is a red LED, which has a typical voltage drop of 1.6 V. After subtracting the base-emitter voltage of T2, this leaves 1 V across R4, so that a current of 1 A flows. This constant current leaves the circuit via the collector of T2, and is fed to the battery. Diode D2 protects T2 against excessive voltages. Since D1 is used as a reference, it **must** be a red LED (the voltage across LEDs depends on the colour). Also, do not use a high-efficiency type in position D1, since that, too, causes an incorrect reference volt-

As already mentioned, the battery is charged with a current pulse every 2.5 seconds, which is indicated by the LED flashing at the same rate. If the LED does not flash, or flashes irregularly, there is probably something wrong with the relevant battery. Do note confuse irregular flashing with 'slow' flashing (every 50 s), which indicates trickle charging.

The full circuit diagram of the mi-

| Table 1. Range selec | tions |            | R4;R9;R14;R19 | );R24;R29;R34;R39 |

|----------------------|-------|------------|---------------|-------------------|

|                      |       | 1Ω         | 2 Ω           |                   |

| Capacity             | P1    | JP1 open   | 0-5 Ah        | 0-2.5 Ah          |

| Capacity             | P1    | JP1 closed | 0-10 Ah       | 0-5 Ah            |

| Charging current     | P2    | S1 closed  | 0-1 A         | 0-500 mA          |

| Charging current     | P2    | S1 open    | 0-200 mA      | 0-100 mA          |

crocontroller-driven NiCd charger is given in **Fig. 4**. Controller IC1 is a member from the ST62xx family which was introduced in Ref. 1. The eight charging circuit are divided into two groups of four, which are separately powered. In this way, the maximum load on the charging/discharging circuits is limited to 4 A, which is easier to handle than the 8 A which would be required if all circuits were connected to a single supply.

The division into two groups is also found back with T27. To prevent all discharge currents flowing through this transistor, it is shunted by a second power MOSFET, T26. Each of these transistors handles one group of charging/discharging circuits, and, thus, half the total discharging current. Furthermore, the division into two groups comes in handy for the design of the printed circuit board, because it allows the tracks that carry the total charging/discharging current to be kept as short as possible. Transistor T25 does not need 'assistance' since it can easily handle the current drawn by the eight LEDs in the charging circuits on its own.

Since microcontroller IC1 has a limited number of inputs and outputs, the

four modes of the charger (check; discharge; charge; and trickle) are conveyed to the circuit via two outputs only. These two control bits are decoded by demultiplexers IC2a and IC2b. The latter controls LEDs D19 (check), D20 (discharge), D21 (charge) and D22 (trickle). These LEDs indicate the state of the charger. IC2b decodes the two output bits to control T25, T26 and T27. In 'check' mode, these three transistors are switched off, allowing the microcontroller to measure the battery voltage (remember, no current flows at this stage). In 'discharge' mode, T26 and T27 are switched on, while T25 is switched on in 'charge' as well as in 'trickle' mode. Current pulsing is achieved by switching between 'check' mode on the one hand, and 'discharge', 'charge' or 'trickle', on the other.

The charger is adjusted with the aid of P1 and P2 (for the ranges, see Table 1). P1 enables the battery capacity, or, more properly, the energy (in Ah) put into the battery, to be set. This means that the battery charger does not compensate the efficiency of the charging process. Fortunately, that is not a problem because the efficiency of the charging process is relatively high

Fig. 4. Circuit diagram of the NiCd charger. Most discrete electronics is contained in the charging/discharging circuits. Inside IC1 lurks a complete computer system with RAM, ROM and an A-D converter.

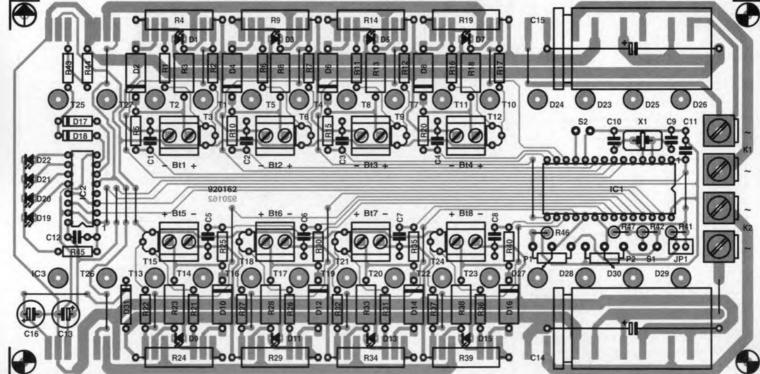

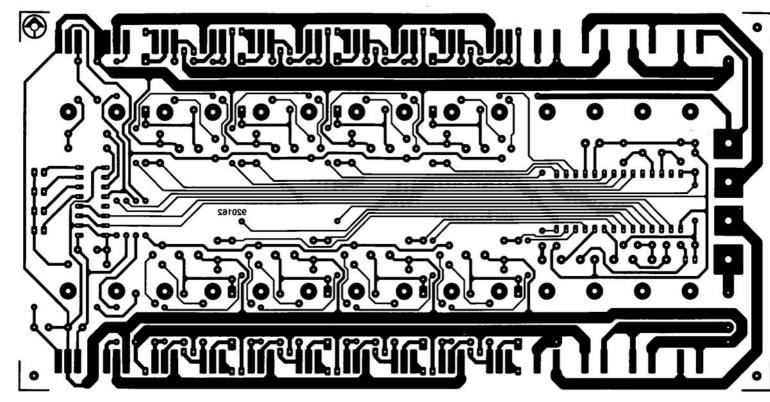

Fig. 5. The printed circuit board is designed to fit on the SK47/100/SA heatsink. Use a photocopy of the component mounting plan as a templatye to drill the holes for the power semiconductors.

by virtue of the high charging current. In practice, you will come very close to a 'full' battery if you set its nominal capacity with P1. If, after having used the batteries, they appear not to have had the full capacity, try setting a higher capacity with P1 next time (however, do not go higher than 1.4 times the nominal capacity).

The second control, P2, allows the average charging current to be set.

That may appear strange, since the current sources pump fixed 1-A pulses through the battery, no matter how small this is. However, by matching the average current to the specification of the battery, this is given sufficient time to recover from the current pulse. Current pulses cause gas bubbles in the battery. Although these disappear as a result of the chemical reaction set off the charging current, this takes

some time. Since the gas bubbles increase the pressure inside the battery, the amount of gas must be restricted. Here, this is achieved by a pause following each current pulse.

If you frequently use small batteries which seem to have problems with the 1-A charging current, it is recommended to change R4 (and its counterparts in the other current sources) from 1  $\Omega$  into 2  $\Omega$ . This modification

|     |                     | COMPON           | ENT  | S LIST                             |                  |

|-----|---------------------|------------------|------|------------------------------------|------------------|

| Res | sistors:            |                  | 1 8  | BYW29                              | D23-D30          |

| 8   | 68Ω                 | R1;R6;R11;       | 1    | 1N4001                             | D31              |

|     |                     | R16;R21;R26;     | 10   | BUZ10                              | T1;T4;T7;T10;    |

|     |                     | R31;R36          | 1000 |                                    | T13;T16;T19;     |

| 8   | 2kΩ2                | R2;R7;R12;       |      |                                    | T22;T26;T27      |

|     |                     | R17;R22;R27;     | 8    | BD240                              | T2;T5;T8;T11;    |

|     |                     | R32;R37          | -    |                                    | T14;T17;T20;     |

| 16  | 1Ω 1W               | R3;R4;R8;R9;     |      |                                    | T23              |

|     |                     | R13;R14;R18;     | 8    | BC547B                             | T3;T6;T9;T12;    |

|     |                     | R19;R23;R24;     |      |                                    | T15;T18;T21;     |

|     |                     | R28;R29;R33;     |      |                                    | T24              |

|     |                     | R34;R38;R39      | 1    | BD239                              | T25              |

| 10  | 100kΩ R5;R10;R15;   |                  | 1    | ST62E15 microcrontroller; supplied |                  |

|     |                     | R20;R25;R30;     |      | ready-programmed; order code:      |                  |

|     |                     | R35;R40;R41;     |      | 7071* (see page 70)                | IC1              |

|     |                     | R42              | 1    | 74HC239                            | IC2              |

| 2   | 1kΩ                 | R43;R44          | 1    | 4805                               | IC3              |

| 1   | 470Ω                | R45              | 1    |                                    |                  |

| 2   | 1kΩ5                | R46;R47          | Mis  | scellaneous:                       |                  |

| 1   | 100kΩ linear poten  |                  | 8    | 2-way PCB terminal                 |                  |

| 1   | 25kΩ linear potenti | ometer P2        |      | block, pitch 5mm                   | Bt1-Bt8          |

|     |                     |                  | 1    | fuse 630mA, slow                   | F1               |

|     | pacitors:           |                  | 1    | jumper                             | JP1              |

| No. | 100nF               | C1-C8;C11;C12    | 4    | PCB mount spade                    |                  |

| 2   | 22pF                | C9;C10           | 1 3  | terminal                           | K1;K2            |

| 2   | 4700μF 16V          | C14;C15          | 1    | SPST switch                        | S1               |

| 2   | 100μF 16V radial    | C13;C16          | 1    | Press-key                          | S2               |

| -   |                     |                  | 1    | Mains transformer 2:               |                  |

|     | miconductors:       | AND DE COMMON TO | 1    | 8MHz quartz crystal                | X1               |

| 10  | LED, red, 3mm       | D1;D3;D5;D7;     | 1    | Mains socket with in               | tegral fuseholde |

|     |                     | D9;D11;D13;      |      | and switch                         |                  |

| -   |                     | D15;D19;D21      | 1    | Heat-sink SK47/100/                |                  |

| 8   | 1N5400              | D2;D4;D6;D8;     | -    | size: 200x100x40mn                 |                  |

|     |                     | D10;D12;D14;     | 1    | Printed circuit board              | plus IC1; set    |

| -   | 4514440             | D16              |      | order code 920162.                 |                  |

| 2   | 1N4148              | D17;D18          |      | 1.1. 1000100                       |                  |

| 1   | LED, yellow, 3mm    | D20              | * pa | art of set 920162.                 |                  |

| 1   | LED, green, 3mm     | D22              | 1    |                                    |                  |

results in current pulses of 500 mA instead of 1 A (see also Table 1).

Since the energy to be put into the battery is set with the aid of P1, the charging time of the battery is easily computed by dividing the set capacity by the set current. Only if the charging current is at or near the maximum, you will have to allow for some extra time, which goes on account of the microcontroller running state checks on the batteries.

Last but not least, the power supply of the NiCd charger. The mains transformer is a fairly heavy type with two separate 6-V secondary windings, each rated at 6-7 A. Here, too, the supply is divided into two parts to keep the maximum currents within reason. None the less, the rectifier diodes have a pretty hard time, and to keep them cool they have to be fitted on the heatsink, together with the power transistors. That is also why TO-220 style diodes are used. For the rest, the power supply is straightforward: bridge rectifier, smoothing capacitor and a 5-V regulator, IC3, to supply IC1

and IC2. A low-drop voltage regulator is used because of the relatively low transformer secondary voltage (which is necessary to keep the dissipation in the current sources within limits).

#### Construction