THE INTERNATIONAL ELECTRONICS MAGAZINE OCTOBER 1992 UK £2.25

# 8051 SINGLE-BOARD COMPUTER

0

History of the valve

Mains sequencer

Pascal routines for measuring card

### Using the MAR-x seri

0

SI (SI (SI )

#### In next month's issue (among others):

- · Digital slide overflow unit

- · Automatic printer switch

- · AF current amplifier

- Difference thermometer

- · Compact spiral antenna

- Unblocking the pump

- Sound sampler for Amiga

- Wheatstone bridge

- Model analysis

#### Front cover

The collage symbolizes the variety of projects we publish throughout the year and the technology used in them. In the past 12 issues, we have published no fewer than 74 large projects (a number of them multi-part) and over 100 smaller projects. These were backed up by descriptive articles on new components, new techniques and new applications. Also in that period we started the 8051/8032 assembler course which has proved popular beyond expectations.

14

Copyright © 1992 Elektuur BV

## CONTENTS

#### **AUDIO & HI-FI**

21

PROJECT: A.F. digital-to-analogue converter Part 3 (final) Design by T. Giesberts

#### COMPONENTS

28 Flash EPROMs by T. Scherer

#### **COMPUTERS & MICROPROCESSORS**

35 COURSE: 8051/8032 assembler - Part 7 by Dr M. Ohsmann

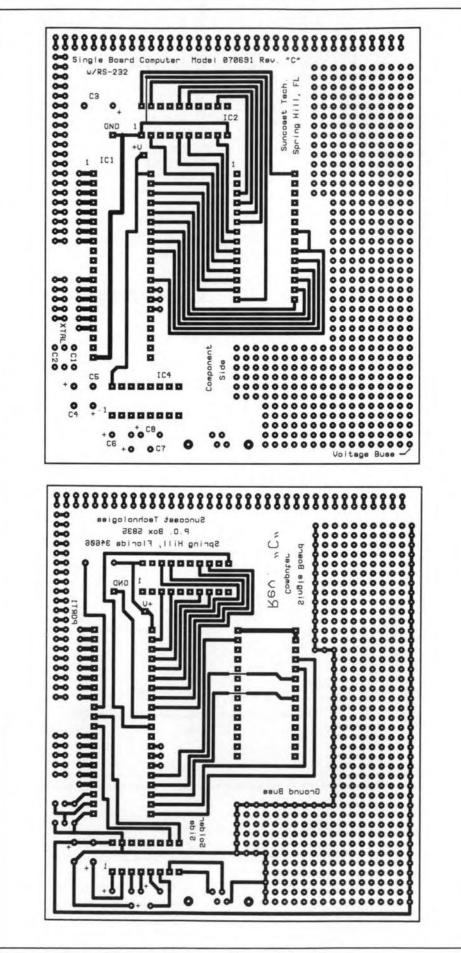

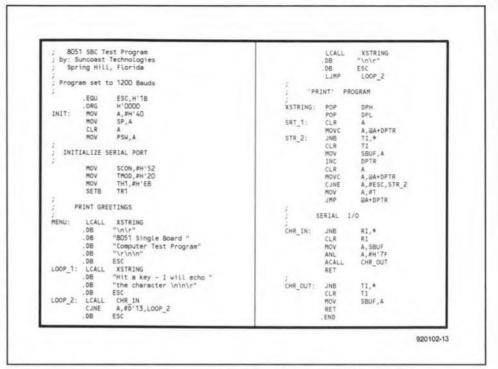

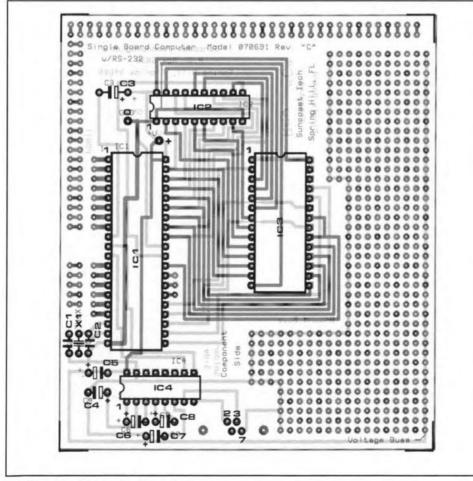

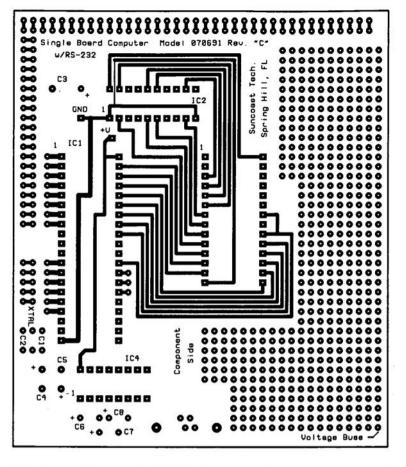

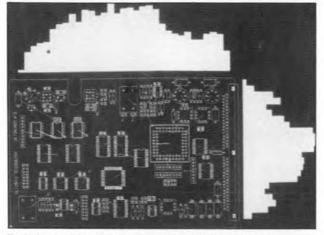

40 PROJECT: 8051 single board computer by Steve Sokolowski

DESIGN IDEAS

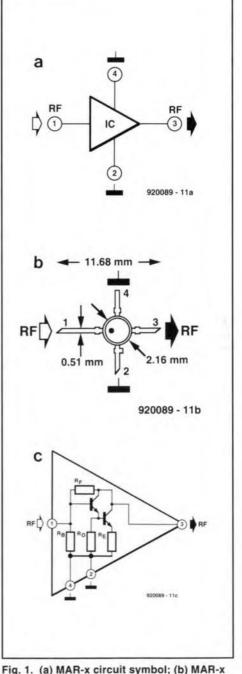

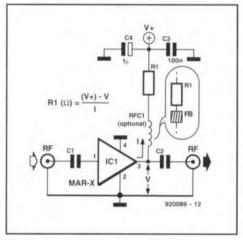

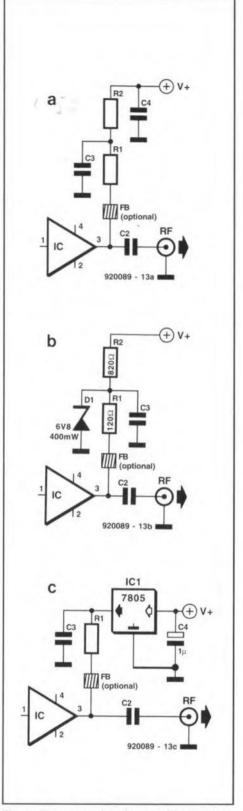

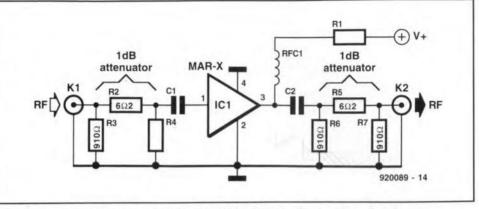

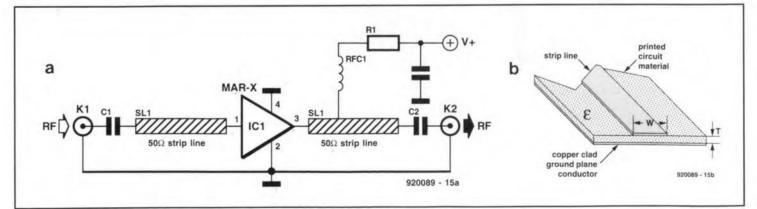

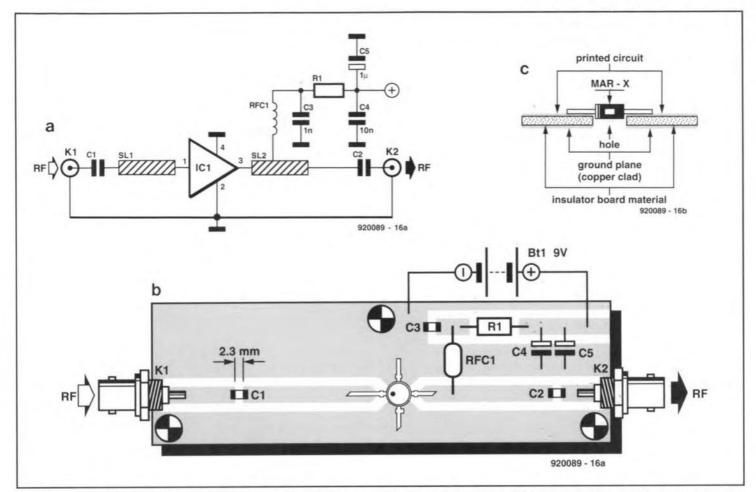

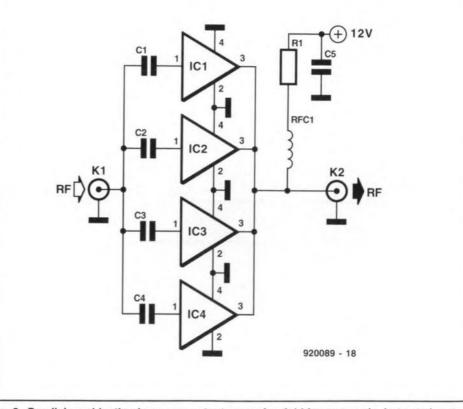

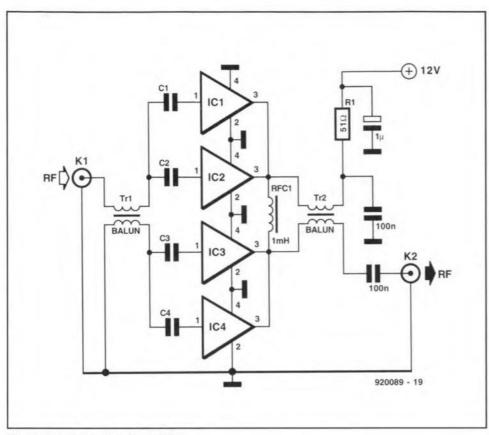

52 Using the MAR-x series of very wideband monolithic microwave integrated circuits (MMICs) by Joseph J. Carr

#### GENERAL INTEREST

- 58 REVIEW: Ultimate Technology's Challenger by David J. Silvester

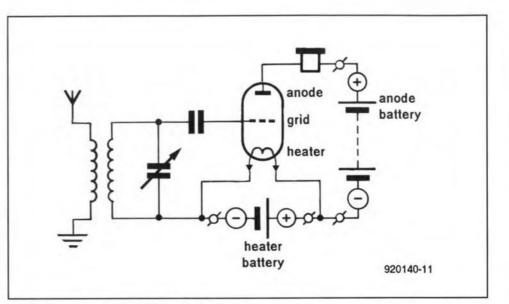

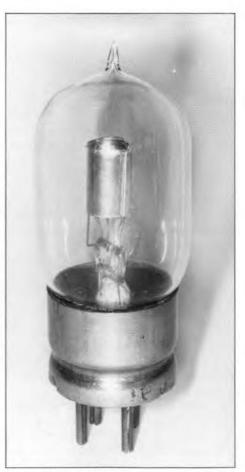

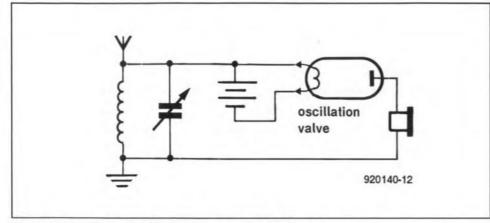

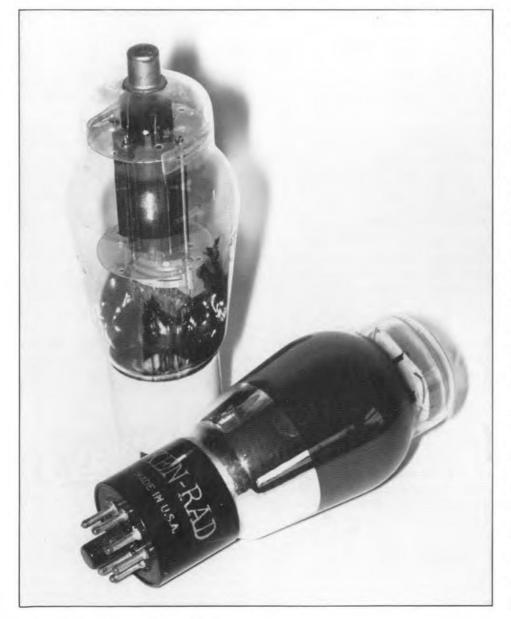

60 A brief history of the valve

- by Ian Poole, G3YWX

#### **POWER SUPPLIES & BATTERY CHARGERS**

16 PROJECT: Mains sequencer Design by T. Giesberts

#### **RADIO, TELEVISION & COMMUNICATIONS**

- **PROJECT**: Wideband active antenna for 10 kHz – 220 MHz Design by J. Barendrecht

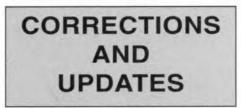

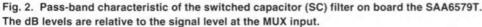

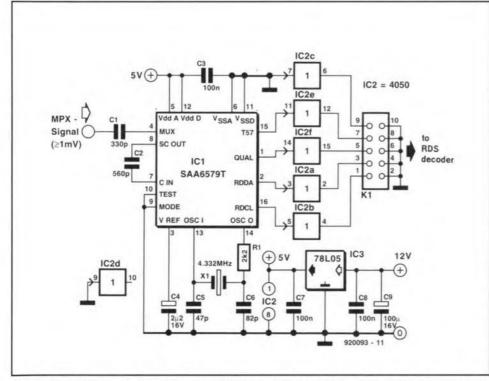

- PROJECT: RDS demodulator with integrated filter Design by G. Kleine

#### SCIENCE & TECHNOLOGY

46 An eternal enigma: the applicable and constructable fictions of electronics by M.C. Soper, MA

#### **TEST & MEASUREMENT**

32 PROJECT: Pascal routines for multifunction measurement card Design by J. Ruiters

#### MISCELLANEOUS INFORMATION

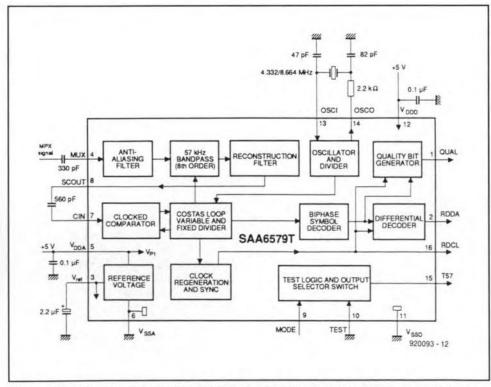

Electronics scene 11–12; Events 13; New books 39; Corrections 57; Readers' services 70; Terms of Business 72; Index of advertisers 74

A brief history of the valve - p. 60

October 1992

Volume 18

Number 204

### WIDEBAND ACTIVE ANTENNA FOR 10 kHz - 220 MHz

This design goes to show that low noise and substantial amplification can go hand in hand in a single amplifier with excellent wideband characteristics. Ideal for use with car radios and communication receivers, or as an active probe for a high-frequency sampling oscilloscope, the design presented here is simple to build from a handful of components.

#### Design by J. Barendrecht

14

**M**OST wideband antenna amplifiers are simply impedance converters that provide some gain. The impedance of a whip or telescopic rod antenna is relatively high because these antennas are short with respect to the wavelength of the received signal. Obviously, this high impedance needs to be transformed down to 50  $\Omega$  or 75  $\Omega$  to match the receiver input, and that is why most wideband antenna amplifiers 'begin' with an old faithful: the J-FET based source follower.

Now while a J-FET is a nearly ideal impedance converter, its use in a wideband active antenna has two major disadvantages. First, it has a relatively large input capacitance (typically 10 pF), which easily creates a filter in combination with the high antenna impedance. Second, one of the rules of good antenna amplifier design is that the first active stage should provide at least some amplification to ensure the lowest overall noise figure of the design. Unfortunately, this requirement can not be met by the source follower, because it forms an attenuator, and so degrades the overall noise figure considerably.

#### A different approach

Thus, at the input of a wideband antenna amplifier we require a device that (1) has a low input capacitance; (2) is capable of very high frequency operation at low noise; (3) has a very high input impedance; (4) can cope with high signal levels without running into high intermodulation figures; and (5) provides some gain. That may seem a lot to ask from a single active device, but fortunately a good compromise can be struck by using a dual-gate MOSFET at the amplifier input.

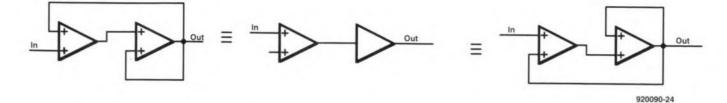

The amplifier discussed here is one of the 'overall feedback' type, of which every one of the three stages provides amplification. Actually, it is a two-stage amplifier with an emitter follower at the output.

As opposed to the J-FET source fol-

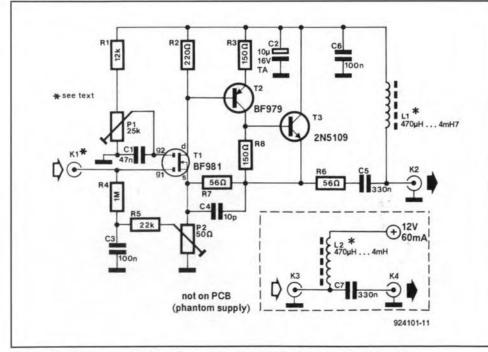

Fig. 1. Circuit diagram of the antenna booster and its phantom power supply.

lower, the MOSFET used here functions as an amplifier, and has an input capacitance of only 2 pF. As shown in the circuit diagram, Fig. 1, a BF981 is used.

The second stage is coupled direct to the MOSFET drain, and is built around the BF979 pnp UHF transistor. A mediumpower wideband cable TV driver transistor Type 2N5109 (from Motorola) is used in the emitter follower stage.

Feedback is created by taking the emitter signal of T<sub>3</sub> back to the source of T<sub>1</sub>, via network R7-C4. Without feedback, the gain of the amplifier lies between 15 dB and 20 dB (measured at an output impedance of 50  $\Omega$ ). With the feedback parts fitted, the gain starts to rise a little at about 100 MHz. The increase amounts to about 2 dB towards the end of the mobile communications section of the VHF band, at about 160 MHz. This effect is caused by the increased phase shift at lower frequencies, which result in a less effective feedback.

The amplifier is powered by a 12-V regulated supply via the downlead coax cable. This so-called phantom supply is shown separately in the circuit diagram. If you are lucky, your receiver has a 12-V power supply, in which case it is conveniently used to power the antenna amplifier. It should be noted that the components in the phantom supply, i.e., the two connectors (K3 and K4), the choke (L2) and the decoupling capacitor (C7) are not fitted on the PCB.

The inductance of chokes L1 and L2 depends on the frequency that is of interest to you. The highest inductance value, 4.7 mH, is used for VLF reception; the lowest value, 470  $\mu$ H, for VHF/UHF reception. Finding the best value may require some experimenting. In all cases, the d.c. resistance of the chokes must be smaller than 10  $\Omega$ .

The output of the amplifier is connected to the phantom supply via BNC connectors and a length of 50-75  $\Omega$  coax cable. Inexpensive TV coax cable will be adequate for this application.

The current consumption of the antenna amplifier is not more than 60 mA.

#### Construction and adjustment

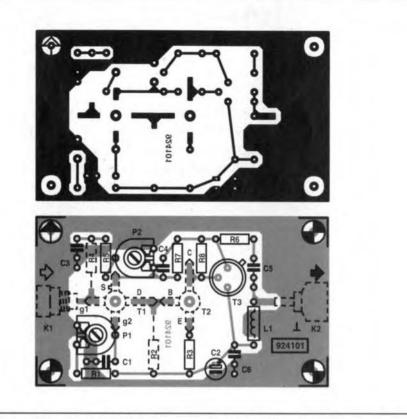

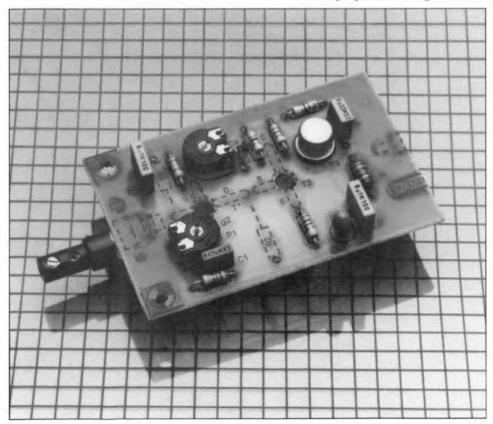

The amplifier is constructed on the small single-sided printed circuit board shown in Fig. 2. Note that the **dashed parts indicated on the component overlay are fitted at the track side of the board**. The whip or telescopic rod antenna is connected to the amplifier input via a banana socket. The antenna should not be longer than strictly

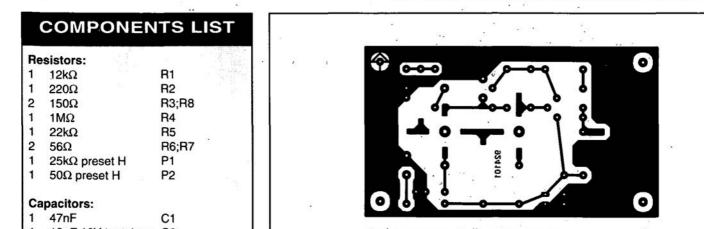

#### COMPONENTS LIST

|     | sistors:              |        |  |  |  |  |

|-----|-----------------------|--------|--|--|--|--|

| 1   | 12kΩ                  | R1     |  |  |  |  |

| 1   | 220Ω                  | R2     |  |  |  |  |

|     | 150Ω                  | R3;R8  |  |  |  |  |

| 1   |                       | R4     |  |  |  |  |

|     | 22kΩ                  | R5     |  |  |  |  |

| 2   | 56Ω                   | R6;R7  |  |  |  |  |

| 1   | 25kΩ preset H         | P1     |  |  |  |  |

| 1   | 50Ω preset H          | P2     |  |  |  |  |

| Ca  | pacitors:             |        |  |  |  |  |

| 1   | 47nF                  | C1     |  |  |  |  |

| 1   |                       | C2     |  |  |  |  |

|     | 100nF                 | C3;C6  |  |  |  |  |

|     | 10pF ceramic          | C4     |  |  |  |  |

| 1   |                       |        |  |  |  |  |

| Se  | miconductors:         |        |  |  |  |  |

| 1   | BF981                 | T1     |  |  |  |  |

| 1   | BF979                 | T2     |  |  |  |  |

| 1   | 2N5109                | Т3     |  |  |  |  |

| Ind | ductor                |        |  |  |  |  |

| 1   | choke 470µH to        |        |  |  |  |  |

|     | 4mH7 (see text)       | L1     |  |  |  |  |

| Mi  | scellaneous:          |        |  |  |  |  |

| 1   | Banana socket, insu   | lated, |  |  |  |  |

|     | for chassis mounting  |        |  |  |  |  |

|     | receptacle dia. 2.6 r | W .    |  |  |  |  |

| 1   | BNC socket            | K2     |  |  |  |  |

| 1   | Printed circuit board | 924101 |  |  |  |  |

| Dh  | antom supply (not c   | DCB)   |  |  |  |  |

|     | BNC socket            | K3:K4  |  |  |  |  |

| 4   | 330nE                 | C7     |  |  |  |  |

| 2 | DINC SUCKEL | N3,N4 |

|---|-------------|-------|

| 4 | 220nE       | 07    |

- choke 470µH to

- L2 4mH7 (see text)

Fig. 2. PCB artwork for the project. Note that a number of components are fitted at the track side of the board.

necessary - 30 to 50 cm is long enough in most cases. The prototype used a bicycle spoke cut to about 40 cm and secured to a banana plug. When your reception area is 'infested' with hum (e.g., from nearby mains wiring), the antenna should be coupled to the amplifier input via a 10-pF capacitor.

To ensure proper screening, the com-

pleted printed circuit board is fitted in a metal box.

The d.c. setting of the amplifier is dependent on a number of factors, and may require some experimenting for best results. In general, P1 and P2 should be adjusted for a voltage of 6-8 V at the emitter of T3. When the amplifier is used for daytime short-wave or medium-wave reception, the best possible S/N ratio is required. Hence, preset P1 must be adjusted for a gate2-to-source voltage (Ug2-s) of between 3 V and 6 V. The lowest voltage that gives adequate reception of a weak station should be used.

For night-time reception, a different setting is required to cope with the much higher signal levels. In that case, we require the smallest possible IM (inter-modulation) distortion, which can only be achieved by passing more current through the MOS-FET, so that  $U_{g2-s}$  will be nearer 6 V than with daytime reception. Adjust P1 for minimum IM distortion when very strong signals are received. IM distortion will not occur easily, and a good way to pick up extremely strong signals is to tune to the 21-MHz band (14 m) in the late evening hours, or couple the amplifier input to a large antenna via a very small capacitance (a piece of wire wound around the 'outdoor antenna' cable and connected to K1 will be adequate). Remember, the amplifier input forms a very high impedance, which does not allow coax cable to be connected.

Finally, the prototype of the amplifier worked right up to 220 MHz, at which frequency a gain of 5 dB was achieved.

15

#### WIDEBAND ACTIVE ANTENNA FOR 10 KHZ - 220 MHZ

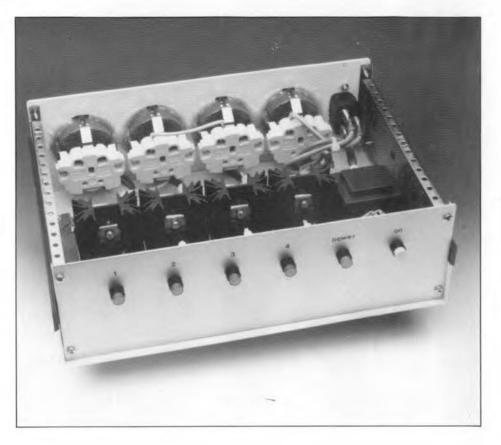

### MAINS SEQUENCER

**Design by T. Giesberts**

When a group of mains-operated electrical or electronic appliances is switched on simultaneously, it may very well happen that the mains fuse(s) blow or the circuit-breakers cut out. This is caused by the peak currents that flow at switch-on, which can be many times larger than the nominal current. A circuit is described that obviates such an unwelcome happening.

WHEN an electrical or electronic apparatus is switched on, a peak current much larger than the nominal one flows, particularly in the case of motors and transformers. If a group of such equipment is switched on at the same time, it is quite likely that the relevant fuse in the consumer unit or distribution board gives up the ghost. Modern circuit breakers react even more quickly to peak currents than fuses. The load already connected to the consumer unit or distribution board must, of course, also be taken into account. The circuit proposed here obviates that risk by switching on the units in a group in a predetermined order at intervals of one second.

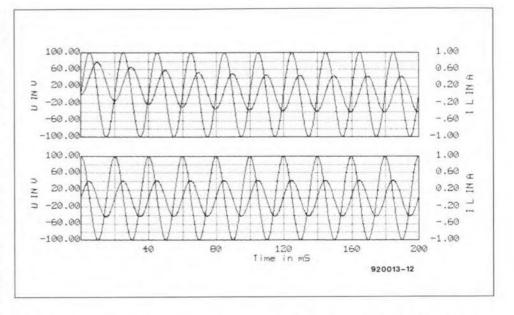

The circuit does more than just spreading the switch-on times. It also has a facility that enables determining the switch-on instant with respect to the zero (voltage) crossing of the mains supply. The zero (voltage) crossing is just about the most unfavourable instant for switching inductive loads if it comes to preventing high peak currents. Assuming a pure inductance, voltage and current are 90° out of phase, so that the zero crossing occurs at the instant when the current is maximum. If the appliance is switched on at the zero (voltage) crossing, the current will be extra large because it has a tendency to make up for the lag. If it is switched on at maximum voltage, however, the current will almost immediately assume its nominal value-see Fig. 1. In the upper half of the figure, the appliance is switched on at the zero (voltage) crossing. The current is then initially 'lifted' well above the base line, after which it drops back slowly until equilibrium is reached. In this theoretical case, the current at switch-on has about twice the nominal value. In the bottom half, equilibrium is reached immediately, because the appliance is switched on at maximum voltage. In practice, of course, the correct switchon moment will lie somewhere between the zero crossing and maximum voltage. Two examples will illustrate the point.

A problem occurs when iron-cored transformers and inductors are switched on. The core will have to become magnetized before it functions properly. That means that at switch-on the impedance is determined mainly by the primary winding. This may vary from a few ohms to several hundreds

Fig. 1. When a sinusoidal voltage across an inductance is switched on, the phase angle at which this happens determines the level of the peak current through the inductance.

of ohms, depending on the nominal rating of the transformer. For instance, the impedance of a 300 VA toroidal transformer is 2–3  $\Omega$ , which could result in a peak current at switch-on of about 100 A. Although that current is limited to some extent by the mains supply, in practice, peak currents of 60 A can nevertheless arise.

2. Another problem occurs when inductors are switched off and then on again. Owing to residual magnetism, the core may have a weak magnetic field before switch-on. When switch-on occurs 90° after a zero (voltage) crossing, a large current will result. It is, therefore, better to ensure that no magnetic field exists just prior to switch-on.

In the proposed circuit, the instant of switchon can be preset to enable the user to choose the best (or rather, the least bad) moment for the particular appliance(s).

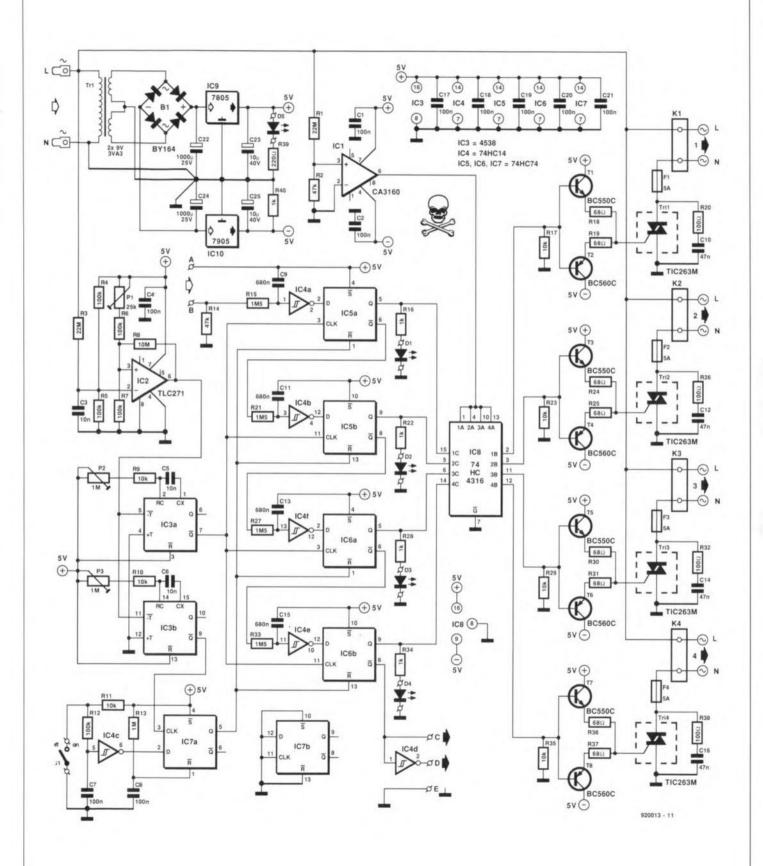

#### Circuit description

Although the design can handle four outputs drawing a current of 5 A each, in the UK it is best to limit this to 3–4 A each, because the maximum rating of the fuse in the usual ring mains plug is 15 A. That means loads of 800–1000 W per output.

The  $\pm 5$  V for the circuit is provided by a small power section that uses regulators Type 7805 and 7905. The transformer specified in the parts list is short-circuit-proof, so that a fuse is not needed.

There is no on/off switch, because that would have to be rated at 20 A, which is not a standard part. Instead,  $D_5$  indicates whether the unit is plugged into the mains or not. This diode and its bias resistor,  $R_{39}$ , form a minimum load for the positive voltage regulator, while  $R_{40}$  provides the same function for the negative voltage regulator. This arrangement means that the regulators always deliver at least a small current, so that regulation is ensured. If no, or only a tiny, current flows, the output voltage tends to rise to the level of the input voltage.

The zero (voltage crossing) is determined by  $IC_2$ , a sort of comparator with a small hysteresis. Its output is a square-wave voltage that is in phase with the mains voltage. The hysteresis can be set with  $P_1$  to a value where the trailing edge of the square-wave voltage

Fig. 2. Circuit diagram of the mains sequencer.

ELEKTOR ELECTRONICS OCTOBER 1992

#### PARTS LIST

#### **Resistors**:

18

$\begin{array}{l} \text{R1, R3} = 22 \ \text{M}\Omega \\ \text{R2, R14} = 47 \ \text{k}\Omega \\ \text{R4-R7, R12} = 100 \ \text{k}\Omega \\ \text{R8} = 10 \ \text{M}\Omega \\ \text{R9-R11, R17, R23, R29, R35} = 10 \ \text{k}\Omega \\ \text{R13} = 1 \ \text{M}\Omega \\ \text{R15, R21, R27, R33} = 1.5 \ \text{M}\Omega \\ \text{R16, R22, R28, R34, R40} = 1 \ \text{k}\Omega \\ \text{R18, R19, R24, R25, R30, R31, R36, R37} \\ = 68 \ \Omega \\ \text{R20, R26, R32, R38} = 100 \ \Omega \\ \text{R39} = 220 \ \Omega \end{array}$

#### **Capacitors**:

C1, C2, C4, C7, C8, C17–C21 = 100 nF C3, C5, C6 = 10 nF C9, C11, C13, C15 = 680 nF C10, C12, C14, C16 = 47 nF, 630 V C22, C24 = 1000 µF, 25 V, radial C23, C25 = 10 µF, 40 V, radial

#### Semiconductors:

D1-D4 = LED, high efficiency\* D5 = LED\* B1 = BY164 T1, T3, T5, T7 = BC550C T2, T4, T6, T8 = BC560C IC1 = CA3160 IC2 = TLC271 IC3 = 4538 IC4 = 74HC14 IC5-IC7 = 74HC74 IC8 = 74HC4316 IC9 = 7805 IC10 = 7905 Tri1-Tri4 = TIC263M

\* Use only with approved insulated holder.

#### Miscellaneous:

```

K1-K4 = 2-way terminal block, 7.5 mm pitch

S1 = single-pole mains switch

Tr1 = mains transformer; 2×9 V, 3.3 VA

secondary (e.g. Monacor VTR3209)

F1-F4 = fuse, 5 A

4 fuse holders for PCVB mounting

2 heavy-duty mains terminals for screwing

on to PCB

4 heat sinks for Tri1-Tri4, 5 K/W (e.g.

Fischer SK129, available from Dau,

Sussex,

Barnham,

Telephone 0243 553 031)

4 Mains outlet chassis socket

1 mains inlet chassis plug

5 insulated LED holders

4 LED lenses, red

1 LED lens, green

1 enclosure (e.g., LC860 from Telet)

1 PCB Type 920013 (see page 70)

```

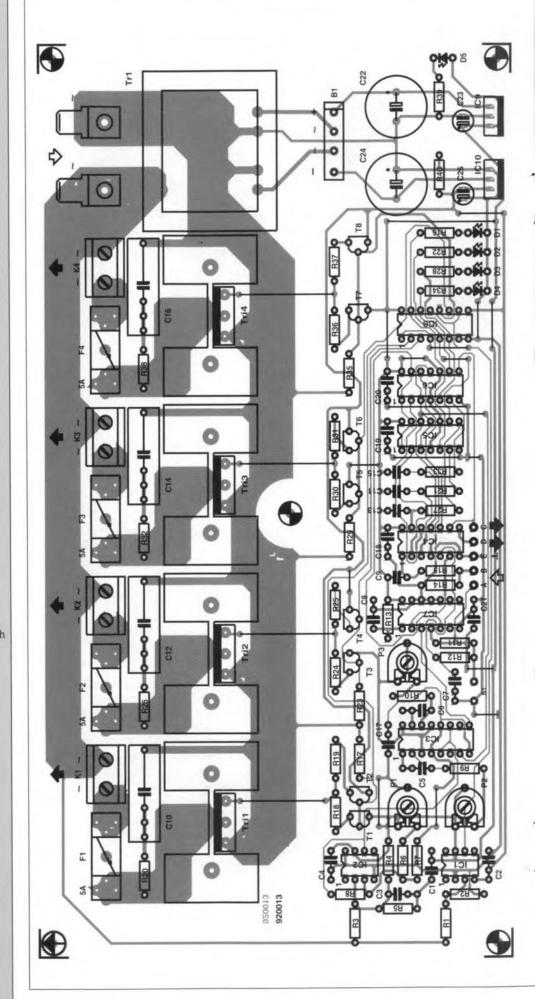

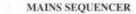

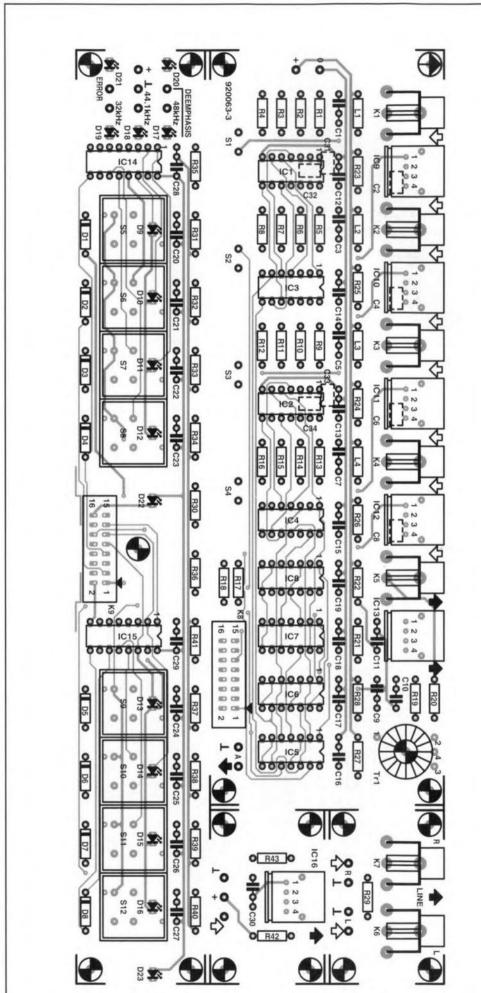

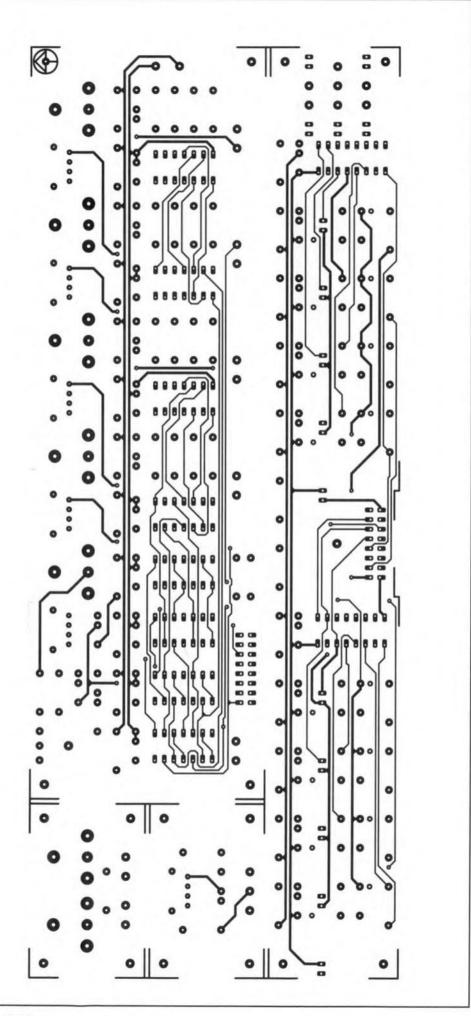

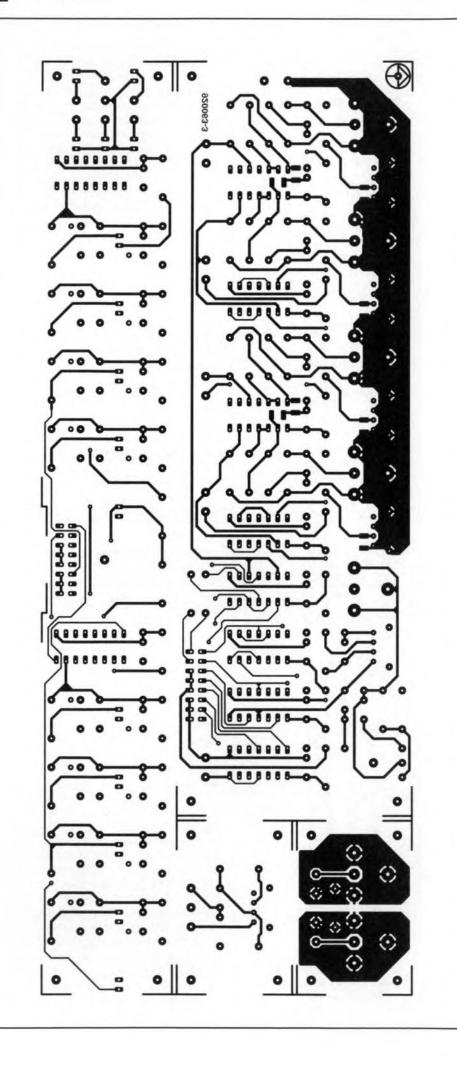

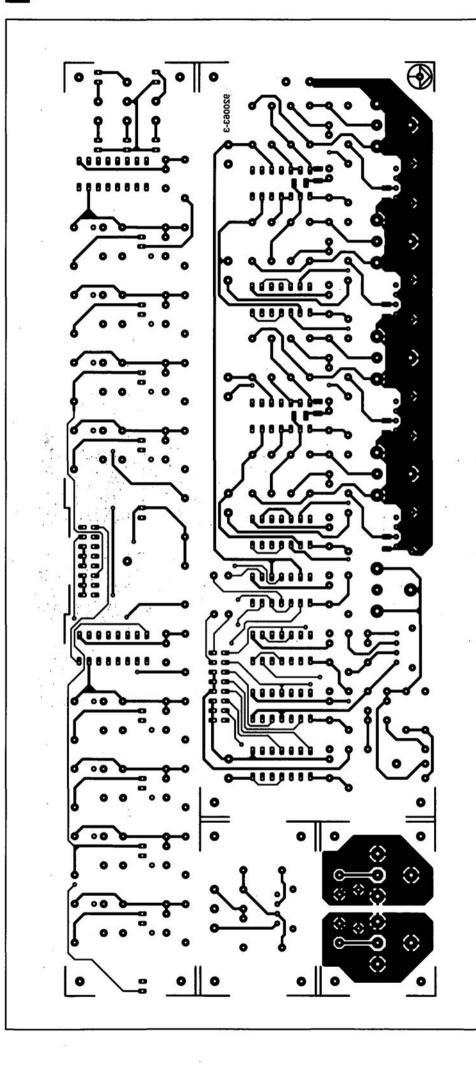

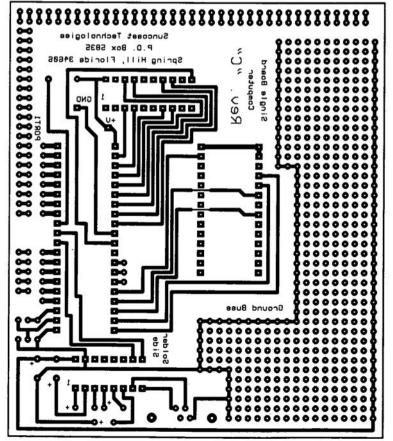

Fig. 3. Printed circuit board for the mains sequencer.

coincides exactly with the zero crossing at the start of a positive half cycle of the mains voltage.

The hysteresis, in conjunction with filter  $R_3$ - $C_3$ , ensures that IC<sub>2</sub> is virtually not affected by noise on the mains.

The trailing edge of the output signal of  $IC_2$  triggers two monostables,  $IC_{3a}$  and  $IC_{3b}$ , which, respectively, determine the switch-on and switch-off moment relative to the zero (voltage) crossing. The mono times may be set between 0.1 ms and 10 ms, which, in practical terms, means between a minute part of a period and a half period.

The sequential switching of the loads is effected by bistables IC5a, IC5b, IC6a, and  $IC_{6b}$ . In the following, it is assumed that  $S_1$  is closed and IC7a reset. The bistables are chainlinked via an RC network and a Schmitt trigger/inverter that ensures a 1 second delay between their being switched. Bistable IC5a is the first in the chain. When it is switched on, the D-input of IC<sub>5b</sub> goes high; when this bistable is clocked, its Q output goes high and the associated output is switched on. At the same time, the D input of IC<sub>6a</sub> goes high. The clock is provided by IC<sub>3a</sub>, which, as we have seen, is triggered at a zero (voltage) crossing after every period. The four bistables are not clocked, however, until the mono time of IC<sub>3a</sub> has elapsed. In other words, setting the pulse width also determines the delay between the zero crossing and the switch-on instant.

Switching off the outputs may be effected in two ways. The first is via  $IC_{3b}$ ,  $IC_{7a}$  and  $S_1$ . This action is similar to that at switch-on:  $IC_{3b}$  clocks  $IC_{7a}$  in step with the mains voltage, so that the switch-off instant can also be set relative to the zero crossing. When  $S_1$  is opened, the D input of  $IC_{7a}$  goes low via  $IC_{4c}$ , which causes the bistable to be reset. This results in the resetting of bistables  $IC_{5a}$ ,  $IC_{5b}$ ,  $IC_{6a}$  and  $IC_{6b}$ , so that all outputs are switched off. A power-up reset is arranged by  $IC_{7a}$  in conjunction with filter  $R_{13}$ – $C_8$ .

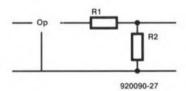

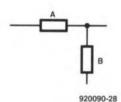

The second way of switching off the outputs is by closing a switch between A and B, in which case the switching off is sequential.

The signals at the Q outputs of  $IC_{5a}$ ,  $IC_{5b}$ ,  $IC_{6a}$  and  $IC_{6b}$  indicate whether an output is on or off. This can be made visible by connecting an LED to each of these pins.

Unfortunately, these signals cannot be used directly to drive the gates of the triacs. This is because, if the mains has a polarity relative to ground different from that of the gate voltage, part of the gate current will not flow directly to ground, but via the load and the mains. That means that a small direct current will flow through the load, to which mains transformers react adversely.

The design of the sequencer ensures that the gate current always flows directly to ground. The output signal of IC<sub>1</sub> indicates the polarity of the mains relative to ground. This signal is fed to four 'output stages',  $T_1$ – $T_8$ , via four analogue CMOS switches contained in IC<sub>3</sub> and controlled by IC<sub>5a</sub>, IC<sub>5b</sub>, IC<sub>6a</sub> and IC<sub>6b</sub>. Depending on the output signal of IC<sub>1</sub>, each of the output stages drives the associated gate with a current of ±50 mA. A switched-

on triac is, therefore, driven constantly via its gate, so that it remains on. This design has the advantage over pulse-driving the gate that not only ohmic, but also reactive, loads can be switched without any problems.

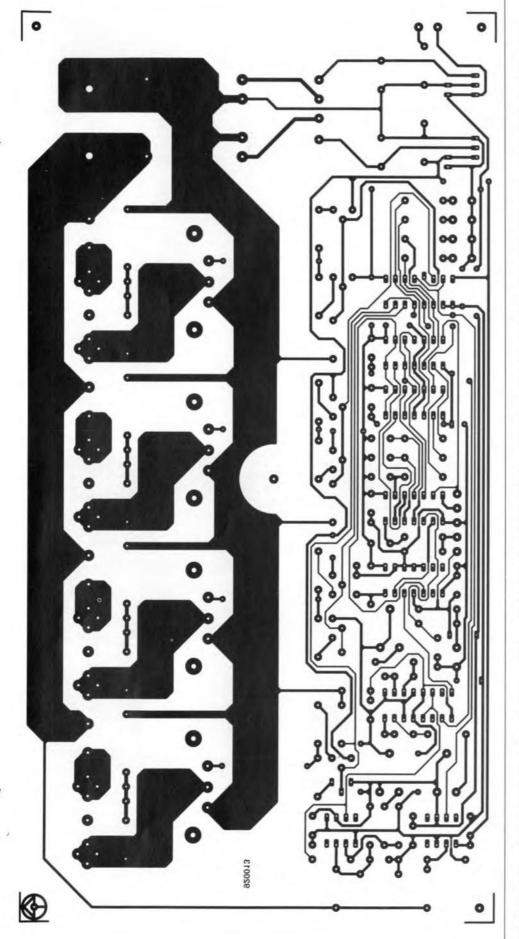

#### Construction

It must be borne in mind at all times that the entire circuit is electrically connected to the mains supply. As long as the circuit has not been built into a suitable enclosure, no mains should be supplied to it or, if it is for test purposes, extreme care should be taken not to touch the circuit with your bare hands or non-insulated tools.

Furthermore, under no circumstances must the ground of the sequencer be connected to earth (mains or otherwise).

Populating the ready-made printed-circuit board should present no problems. Although the triacs may be mounted uninsulated on to the heat sinks, it is better to use an insulating washer to keep the heat sinks free of mains voltage (but not safe!). Note also that the LEDs should be fitted in holders as specified in the parts list, because a 'bare' LED does not meet safety requirements.

Do not use screws thicker than 4 mm (4 BA) to prevent them getting too close to voltagecarrying parts of the board.

Fix the board with *five* screws: the fifth is essential at the centre of the board in view of the length of the board and the weight of the heat sinks.

Fit the board on to 10 mm  $(^{13}/_{32}$  in) long insulated (man-made fibre) spacers (metal ones might come too close to voltage-carrying parts, which would make protruding screws unsafe).

Keep conducting parts of the enclosure (also any metal parts of a man-made fibre one) that can be touched from the outside well away (at least 3 mm $-1/_8$  in— preferably 10 mm $-13/_{32}$  in) from voltage-carrying parts of the board.

When you link two boards, make absolutely sure that the mains connections are not interchanged, since the neutral line is connected to ground.

When choosing an enclosure, make sure that the ventilation holes are not larger than 5 mm ( $^{3}/_{16}$  in), but preferably 3 mm ( $^{1}/_{8}$  in).

Any metal parts of the enclosure that can be touched should be connected to mains earth.

The insulation of switch S<sub>1</sub> must conform to the relevant safety regulations for mainsoperating switches.

The hysteresis, in conjunction with filter  $R_3$ - $C_3$ , ensures that  $IC_2$  is virtually not affected by noise on the mains.

The trailing edge of the output signal of  $IC_2$  triggers two monostables,  $IC_{3a}$  and  $IC_{3b}$ , which, respectively, determine the switch-on and switch-off moment relative to the zero (voltage) crossing. The mono times may be set between 0.1 ms and 10 ms, which, in practical terms, means between a minute part of a period and a half period.

The sequential switching of the loads is effected by bistables IC<sub>5a</sub>, IC<sub>5b</sub>, IC<sub>6a</sub>, and  $IC_{6b}$ . In the following, it is assumed that  $S_1$  is closed and IC7a reset. The bistables are chainlinked via an RC network and a Schmitt trigger/inverter that ensures a 1 second delay between their being switched. Bistable IC5a is the first in the chain. When it is switched on, the D-input of IC<sub>5b</sub> goes high; when this bistable is clocked, its Q output goes high and the associated output is switched on. At the same time, the D input of IC<sub>6a</sub> goes high. The clock is provided by IC<sub>3a</sub>, which, as we have seen, is triggered at a zero (voltage) crossing after every period. The four bistables are not clocked, however, until the mono time of IC<sub>3a</sub> has elapsed. In other words, setting the pulse width also determines the delay between the zero crossing and the switch-on instant.

Switching off the outputs may be effected in two ways. The first is via  $IC_{3b}$ ,  $IC_{7a}$  and  $S_1$ . This action is similar to that at switch-on:  $IC_{3b}$  clocks  $IC_{7a}$  in step with the mains voltage, so that the switch-off instant can also be set relative to the zero crossing. When  $S_1$  is opened, the D input of  $IC_{7a}$  goes low via  $IC_{4c}$ , which causes the bistable to be reset. This results in the resetting of bistables  $IC_{5a}$ ,  $IC_{5b}$ ,  $IC_{6a}$  and  $IC_{6b}$ , so that all outputs are switched off. A power-up reset is arranged by  $IC_{7a}$  in conjunction with filter  $R_{13}$ – $C_8$ .

The second way of switching off the outputs is by closing a switch between A and B, in which case the switching off is sequential.

The signals at the Q outputs of  $IC_{5a}$ ,  $IC_{5b}$ ,  $IC_{6a}$  and  $IC_{6b}$  indicate whether an output is on or off. This can be made visible by connecting an LED to each of these pins.

Unfortunately, these signals cannot be used directly to drive the gates of the triacs. This is because, if the mains has a polarity relative to ground different from that of the gate voltage, part of the gate current will not flow directly to ground, but via the load and the mains. That means that a small direct current will flow through the load, to which mains transformers react adversely.

The design of the sequencer ensures that the gate current always flows directly to ground. The output signal of IC<sub>1</sub> indicates the polarity of the mains relative to ground. This signal is fed to four 'output stages',  $T_1-T_8$ , via four analogue CMOS switches contained in IC<sub>3</sub> and controlled by IC<sub>5a</sub>, IC<sub>5b</sub>, IC<sub>6a</sub> and IC<sub>6b</sub>. Depending on the output signal of IC<sub>1</sub>, each of the output stages drives the associated gate with a current of ±50 mA. A switched-

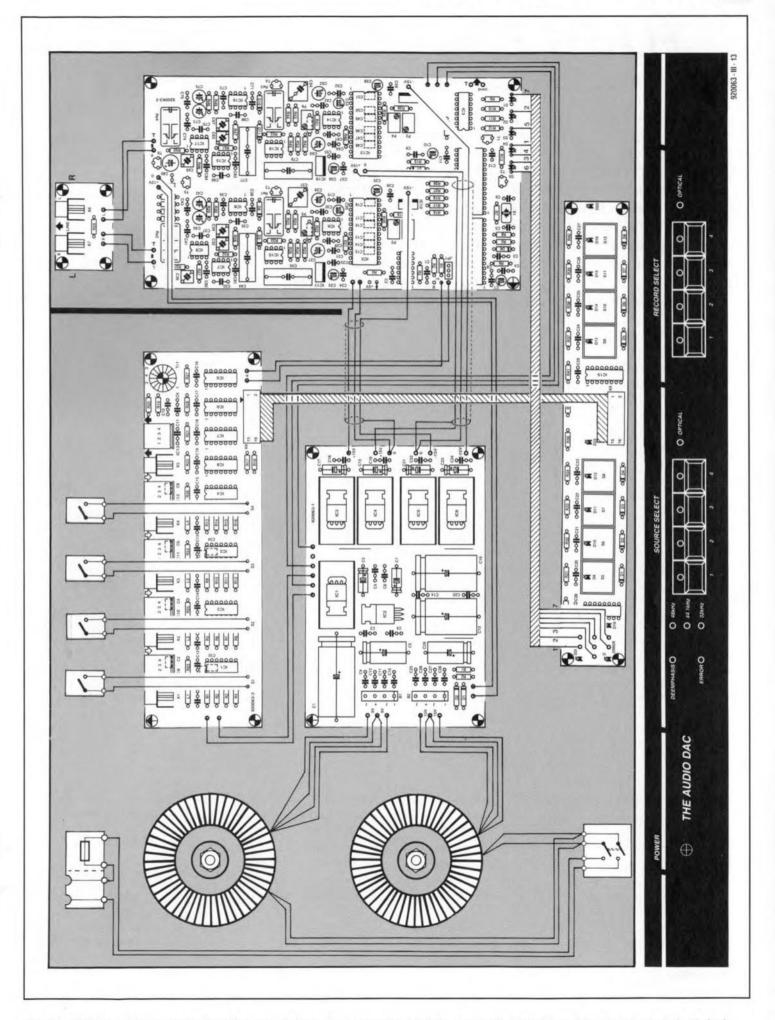

### A.F. DIGITAL-TO-ANALOGUE CONVERTER PART 3 (FINAL)

**Design by T. Giesberts**

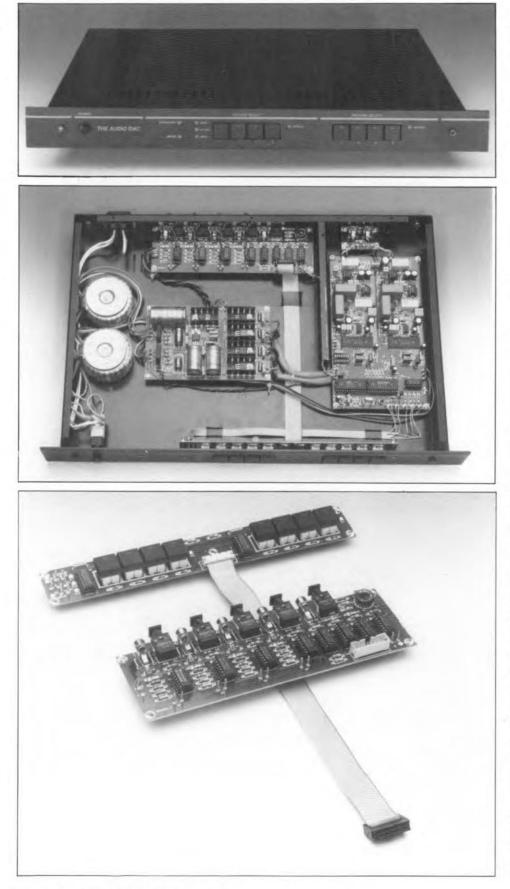

TRICTLY speaking, the converter described So far does not need switching logic, since it can simply be connected direct to a CD player. However, developments in digital audio equipment make it a wise decision to fit the converter with the input/output selector circuit described in this final part of the article. This circuit enables the selection of one of four different digital input signals. Moreover, a tape out facility makes it possible to connect one of the four inputs to a digital recorder, while one of the other three can be listened to at the same time. All inputs and outputs can be linked to either coaxial or optical lines. The inputs are selected with key switches. Four more of these switches facilitate the looping of one of the inputs to the tape record output. The selected source and record inputs, as well as the various settings of the converter, are indicated on the front panel-see Fig. 18.

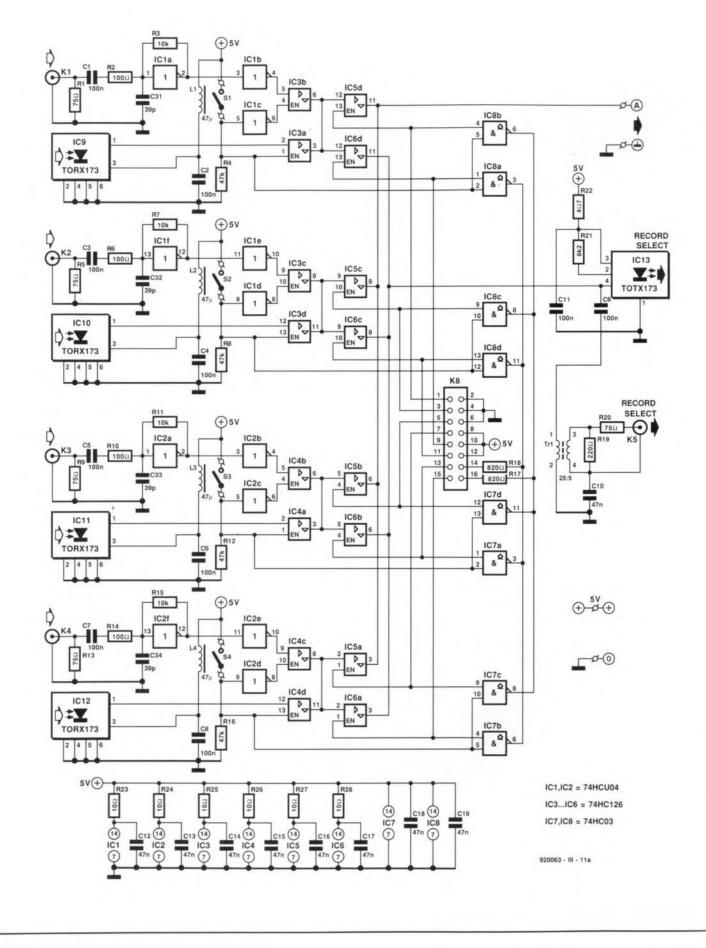

#### Circuit description

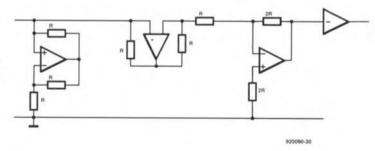

The circuit will be described with reference to channel 1: the design of the other three channels is identical—see Fig. 16.

The coaxial input is terminated into a 75  $\Omega$  resistor, R<sub>1</sub>. The bi-phase signal is fed via C<sub>1</sub> and R<sub>2</sub> to inverter IC<sub>1a</sub>, which operates as an amplifier. Capacitor C<sub>31</sub> suppresses any tendency of the gate to oscillate. Feedback resistor R<sub>3</sub> enables an amplification of ×6 to be obtained, so that the output of the inverter is about 3 V<sub>pp</sub>. Note that the design of the circuit is identical to that of the input circuit in Fig. 5 (in Part 1).

The level of the output of  $IC_{1a}$ , which is applied to  $IC_{1b}$ , is exactly half-way between that of the supply voltage and earth. This enables  $IC_{1b}$  to produce rectangular signals with minimal displacement of the transitions (edges) of the signal. This is important for an optimum reconstruction of the original digital signal.

The signal is then applied to three-state buffer  $IC_{3b}$ , which processes it if switch  $S_1$  is open. If  $S_1$  is closed,  $IC_{3b}$  is off and buffer  $IC_{3a}$ , which is fed with the signal from the optical input circuit,  $IC_{9}$ , is on.

The three-state buffers are followed by two more buffers,  $IC_{5d}$  and  $IC_{6d}$ , which are operated by the key-switch logic. In that way it is determined which of the input signals drives the converter ( $IC_{5d}$ ) or the tape output ( $IC_{6d}$ ).

The optical input consists of a receive diode and a components contained in a small plastic module called a Toslink (named after its manufacturer, Toshiba). Externally, the circuit, whose output is TTL compatible, only needs a power line decoupler, here consist22

Fig. 16. Circuit diagram of the input/output selector.

ELEKTOR ELECTRONICS OCTOBER 1992

#### Toslinks

23

The TORX173 and TOTX173 devices are available from

Highland Electronics Ltd Albert Drive Burgess Hill RH15 9TN England Telephone (0444) 236 000

ELEKTOR ELECTRONICS OCTOBER 1992

#### ing of L1 and C2.

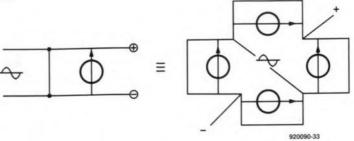

The tape output, too, is coaxial or optical, the latter again with the aid of a Toslink. Here, this circuit externally needs two resistors,  $R_{21}$  and  $R_{22}$ , and a capacitor,  $C_{11}$ . The coaxial output needs to be isolated (to ensure that no earth loop can arise via the ground line of the digital connection) and this is achieved by a small transformer,  $Tr_1$ . In the CD player a special Philips transformer was used, but here a wind-it-yourself type is used—how it is made is described later. Note already, however, that its bandwidth is far greater (at least in our prototype) than that of any readymade type that was tried.

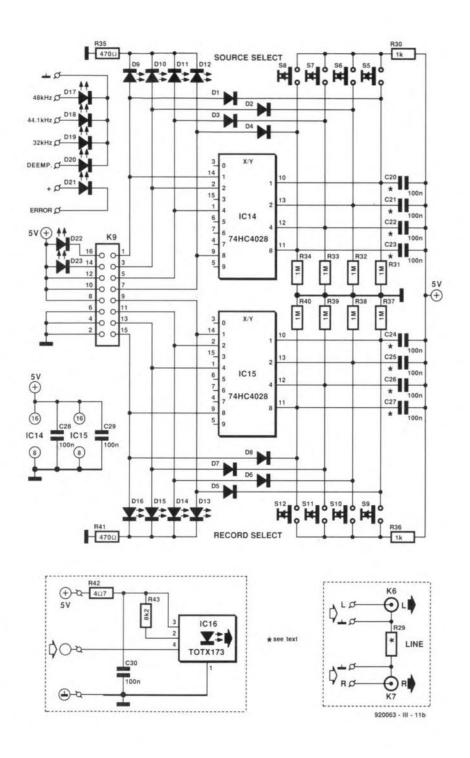

The switching signals are provided by two identical circuits, IC<sub>14</sub>, which determines which signal is applied to the converter, and IC<sub>15</sub>, which ensures that one of the input signals is applied to the tape output. Only the circuit based on IC<sub>14</sub> will be described.

Four key-switches,  $S_5$ – $S_8$ , are connected to the inputs of the circuit, a BCD-to-decimal decoder. When a key-switch is operated, the associated input becomes logic high. The decoder translates this into the relevant decimal level to render the appropriate output high (input A is associated with output  $Q_1$ , pin 14; input B with output  $Q_2$ , pin 2 and so on).

The outputs are fed back to the inputs via diodes  $D_1$ - $D_4$  to ensure that an output remains high when the relevant key-switch is released.

The outputs are connected to LEDs that indicate which output is active.

Of the four capacitors  $C_{20}$ - $C_{23}$ , only that in the output associated with the input selected on power-up is used.

In the same way, only one of capacitors  $C_{24}$ - $C_{27}$  in the tape select circuit is needed.

Gates IC<sub>7</sub> and IC<sub>8</sub> serve to show the user (on the front panel) which type of input (optical or coaxial) is in use with the selected source and record signal. To this end, each gate is connected with the control input of one of the three-state buffers and with one of the selector switches,  $S_1$ – $S_8$ . When a given source or record input is selected,  $D_{22}$  or  $D_{23}$  indicates whether a coaxial (LED out) or optical connection (LED on) is in use with that input.

Five more LEDs at the front panel indicate which of the three sampling frequencies is being used, whether the deemphasis correction is on, and when there is an error in the digital transmission chain.

Audio output connectors  $K_6$  and  $K_7$  are shown separately on the diagram, because they are housed on a discrete small PCB. Resistor  $R_{29}$  is for use only if earth loops occur between the left-hand and right-hand channels. Its value (anywhere between a short circuit and a few ohms) must be determined empirically. If, as should be expected, there are no earth loops,  $R_{29}$  is simply omitted.

Also shown by itself is the optical output based on IC<sub>16</sub>, which too is housed on a separate small PCB. This board is really intended for installation in the CD player (the output board of the player already has provision in the shape of three solder pins—for receiving it).

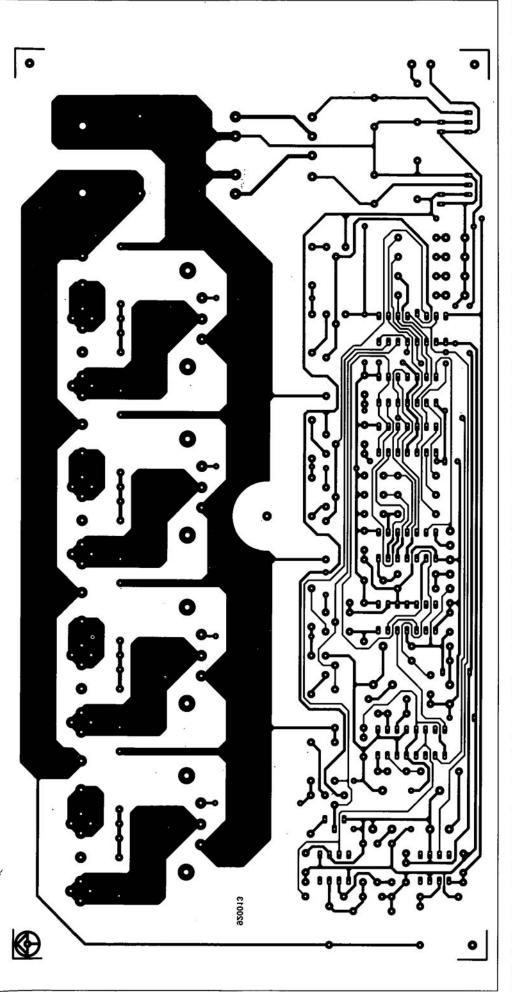

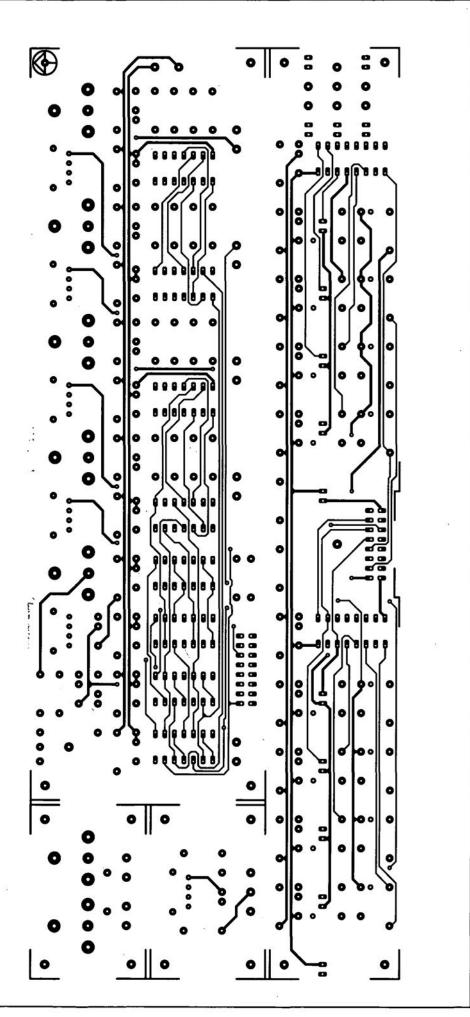

Fig. 17. Printed-circuit board for the input/output selector (continued on pages 25

#### Construction

The printed-circuit board in Fig. 17 should be snapped into four along the relevant seams. The resulting parts are: the busboard with the digital inputs and outputs, the switching board, the analogue output board, and the board for the optical output of the CD player. The analogue board is not needed if insulated audio sockets are used at the rear panel of the converter, and a number of users will not want the optical output for the CD player.

Before buying any LEDs, note that some of them alreay appeared on the mother board (see Fig. 15 in Part 2).

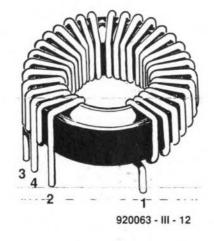

The core for Tr<sub>1</sub> (see inset at bottom right of Fig. 16) must be as indicated in the parts list or the transformer will not perform satisfactorily. Close-wind 25 turns of 1 mm<sup>2</sup> enamelled copper wire on to the core. Then wind five turns of the same type of copper wire over a width of about 5 mm ( $^{3}/_{16}$  in) over one end of the primary 25 turns. The numbers at the terminals correspond with numbers on the PCB.

Capacitors  $C_2$ ,  $C_4$ ,  $C_6$ , and  $C_8$ , are SMD (surface mount design) types that must be soldered at the track side of the board beneath the Toslinks.

The key-switches should preferably be types with integral LEDs, but this is, of course, not essential.

The switching board and the busboard are linked by a short length of 16-core flatcable; normally a length of 30 cm (12 in) will suffice, but this does, of course, depend on the way the boards are fitted in the enclosure. This cable is fitted to the switching board via a flatcable connector with solder tags, while its other end is terminated into a connector that mates with the 16-way header on the busboard.

How everything should be installed into the 19-inch enclosure and what connections are necessary are shown in Fig. 18. Mount the switching board directly behind the front panel. Note the central fixing hole, which is provided to prevent the board bending unduly when the keys are pressed. Run the flatcable under the board to the rear of the enclosure.

Fit the busboard to the rear panel of the enclosure to ensure that all plugs and sockets are easily accessible. The rear panel may be given individual holes for the various connectors or a common rectangular slot. Mount a small slide switch above each audio connector/Toslink combination in such a way that, when open, it points in the direction of the audio connector. It is, of course, not mandatory to fit the Toslinks.

Mount the two transformers at the left of the enclosure and the power supply board roughly at the centre immediately adjacent to the transformers—see photo on page 21.

Fit the busboard at the extreme right of the enclosure in such a way that the analogue output board can just be mounted behind it. It is advisable to screen the left-hand side of the busboard with a small piece of tin

plate running from the rear panel to the power supply connections, that is, only along the analogue section of the board.

First connect the power lines to the boards and then the signal cables. For the mains inlet use a fused type. When all connections are made as shown in Fig. 18, you should have a correctly working converter.

#### PARTS LIST

$\begin{array}{l} \textbf{Resistors:} \\ \textbf{R1, R5, R9, R13, R20 = 75 } \Omega \\ \textbf{R2, R6, R10, R14 = 100 } \Omega \\ \textbf{R3, R7, R11, R15 = 10 } \textbf{k}\Omega \\ \textbf{R4, R8, R12, R16 = 47 } \textbf{k}\Omega \\ \textbf{R17, R18 = 820 } \Omega \\ \textbf{R19 = 220 } \Omega \\ \textbf{R21 = 8.2 } \textbf{k}\Omega \\ \textbf{R22 = 4.7 } \Omega \\ \textbf{R23-R28 = 10 } \Omega \\ \textbf{R29 = see text} \\ \textbf{R30, R36 = 1 } \textbf{k}\Omega \\ \textbf{R31-R34, R37-R40 = 1 } \textbf{M}\Omega \\ \textbf{R35, R41 = 470 } \Omega \end{array}$

#### Capacitors:

C1, C3, C5, C7, C9, C11 = 100 nF, ceramic C2, C4, C6, C8 = 100 nF, SMD C10, C12–C19 = 47 nF, ceramic C20–C29 = 100 nF (see text) C31–C34 = 39 pF, SMD

#### Inductors:

$L1-L4 = 47 \,\mu H$

#### Semiconductors:

D1-D8 = 1N4148 D9-D16 = LED (in S5-S12?) D17, D21-D23 = LED, 3 mm, red\* D18, D20 = LED, 3 mm, yellow\* D19 = LED, 3 mm, green\* IC1, IC2 = 74HCU04 IC3-IC6 = 74HC126 IC7, IC8 = 74HC03 IC9-IC12 = TORX173 IC13 = TOTX173 IC14, IC15 = 74HCV4028

#### Miscellaneous:

K1-K7 = audio socket bus for PCB K8 = 16-way header K9 = 16-way flatcable connector for PCB mounting S1-S4 = mini slide switch, 1 make S5-S12 = key switch, 1 make Tr1 = see text (core = LAB G2-3FT12) PCB Type 920063-3 Front panel foil Type 920063-F

**Optional** (for optical output): R42 = 4.7  $\Omega$ R43 = 8.2 k $\Omega$ C30 = 100 nF, ceramic IC16 = TOTX173

Fig. 18. Wiring and interconnecting diagram of the entire converter, and the suggested front panel (scaled down to half size).

27

#### Construction

The printed-circuit board in Fig. 17 should be snapped into four along the relevant seams. The resulting parts are: the busboard with the digital inputs and outputs, the switching board, the analogue output board, and the board for the optical output of the CD player. The analogue board is not needed if insulated audio sockets are used at the rear panel of the converter, and a number of users will not want the optical output for the CD player.

Before buying any LEDs, note that some of them alreay appeared on the mother board (see Fig. 15 in Part 2).

The core for Tr<sub>1</sub> (see inset at bottom right of Fig. 16) must be as indicated in the parts list or the transformer will not perform satisfactorily. Close-wind 25 turns of 1 mm<sup>2</sup> enamelled copper wire on to the core. Then wind five turns of the same type of copper wire over a width of about 5 mm ( $^{3}/_{16}$  in) over one end of the primary 25 turns. The numbers at the terminals correspond with numbers on the PCB.

Capacitors  $C_2$ ,  $C_4$ ,  $C_6$ , and  $C_8$ , are SMD (surface mount design) types that must be soldered at the track side of the board beneath the Toslinks.

The key-switches should preferably be types with integral LEDs, but this is, of course, not essential.

The switching board and the busboard are linked by a short length of 16-core flatcable; normally a length of 30 cm (12 in) will suffice, but this does, of course, depend on the way the boards are fitted in the enclosure. This cable is fitted to the switching board via a flatcable connector with solder tags, while its other end is terminated into a connector that mates with the 16-way header on the busboard.

How everything should be installed into the 19-inch enclosure and what connections are necessary are shown in Fig. 18. Mount the switching board directly behind the front panel. Note the central fixing hole, which is provided to prevent the board bending unduly when the keys are pressed. Run the flatcable under the board to the rear of the enclosure.

Fit the busboard to the rear panel of the enclosure to ensure that all plugs and sockets are easily accessible. The rear panel may be given individual holes for the various connectors or a common rectangular slot. Mount a small slide switch above each audio connector/Toslink combination in such a way that, when open, it points in the direction of the audio connector. It is, of course, not mandatory to fit the Toslinks.

Mount the two transformers at the left of the enclosure and the power supply board roughly at the centre immediately adjacent to the transformers—see photo on page 21.

Fit the busboard at the extreme right of the enclosure in such a way that the analogue output board can just be mounted behind it. It is advisable to screen the left-hand side of the busboard with a small piece of tin

plate running from the rear panel to the power supply connections, that is, only along the analogue section of the board.

First connect the power lines to the boards and then the signal cables. For the mains inlet use a fused type. When all connections are made as shown in Fig. 18, you should have a correctly working converter.

PARTS LIST Resistors: R1, R5, R9, R13, R20 = 75  $\Omega$ R2, R6, R10. R14 =  $100 \Omega$  $R3, R7, R11, R15 = 10 k\Omega$  $R4, R8, R12, R16 = 47 k\Omega$  $R17, R18 = 820 \Omega$  $R19 = 220 \Omega$  $R21 = 8.2 k\Omega$  $R22 = 4.7 \Omega$  $R_{23}-R_{28} = 10 \Omega$ R29 = see textR30, R36 =  $1 k\Omega$ R31–R34, R37–R40 = 1 M $\Omega$ R35, R41 = 470  $\Omega$ **Capacitors**: C1, C3, C5, C7, C9, C11 = 100 nF, ceramic C2, C4, C6, C8 = 100 nF, SMD C10, C12-C19 = 47 nF, ceramicC20-C29 = 100 nF (see text) C31-C34 = 39 pF, SMD Inductors:  $L1 - L4 = 47 \mu H$ Semiconductors: D1 - D8 = 1N4148D9-D16 = LED (in S5-S12?) D17, D21-D23 = LED, 3 mm, red\* D18, D20 = LED, 3 mm. yellow\* D19 = LED, 3 mm, green\* IC1, IC2 = 74HCU04IC3 - IC6 = 74 HC126IC7, IC8 = 74HC03IC9-IC12 = TORX173 IC13 = TOTX173 IC14, IC15 = 74HCV4028 Miscellaneous: K1-K7 = audio socket bus for PCB K8 = 16-way header K9 = 16-way flatcable connector for PCB mounting S1-S4 = mini slide switch, 1 makeS5-S12 = key switch, 1 makeTr1 = see text (core = LAB G2-3FT12)PCB Type 920063-3 Front panel foil Type 920063-F **Optional** (for optical output):  $R42 = 4.7 \Omega$  $R43 = 8.2 k\Omega$ C30 = 100 nF, ceramic IC16 = TOTX173

ELEKTOR ELECTRONICS OCTOBER 1992

## **FLASH EPROMS**

by T. Scherer

For years nothing much happened in the field of nonvolatile read/write memory components until the EEPROM (Electrically Erasable and Programmable Read Only Memory), followed within a short time by the Flash EPROM, came along. The EEPROM has (not yet) lived up to its early promise, but the Flash EPROM has made a more auspicious start. Already, within two years of its commercial introduction, these devices are readily available and have been used in some commercial equipment. Chip manufacturers say (and, no doubt, hope) that the Flash EPROM has a promising future.

**I**F you have followed the fortunes of the world's giant semiconductor manufacturers over the past few years, you will know that, because competition in the chip markets is fierce and price wars are rife, the manufacture of memory chips is profitable only if gigantic quantities are produced. The manufacturer who is the first to develop a new technique and who will, therefore, be the first to bring a new generation of chips on the market has a decided advantage.

Currently, this intense rivalry is particularly noticeable in the market for dynamic RAMs (or DRAMs). These devices occupy the largest sector of the market. Since their structure is fairly simple, new techniques can be readily applied to them.

Processors also have a large share of the market, but they have been handled differently for a long time. Manufacturers of these devices created so-called industry standards that have given them a virtual monopoly for most of the 1980s. However, this cosy setup has recently started to show signs of movement. Intel processors are now being cloned or produced under licence (Harris, AMD, Sun). The most exciting development in the past18 months was undoubtedly the Apple-IBM cooperative setup that will ensure a much larger future market share for IBM processors.

What has all this to do with Flash EPROMs you may ask. As we have seen, all semiconductor manufacturers are under pressure. The market for DRAMs is nearing saturation, that for processors is hard to penetrate and it offers only small niches for all other types of chip. Now, as everyone knows, all computers contain at least one ROM or EPROM. However, since the market for computers expands (at present) only slowly, no fortunes can be made (any more) with these memory chips. Furthermore, the techniques for producing current ROMs or EPROMs are not really suitable for further development. However, Flash EPROMs with their different properties have given manufacturers (and users) new opportunities.

#### A comparison

The fact that Flash EPROMs are electrically erasable alone does not make these devices attractive. After all, EEPROMs are also electrically erasable. The important advantages of Flash EPROMs over the current erasable memory chips, summarized in Table 1, are as follows.

Table 1. Comparison of the various properties of erasable memory cells.

|                       | EPROM                  | Flash EPROM            | EEPROM        |

|-----------------------|------------------------|------------------------|---------------|

| relative size of cell | 1                      | 1.2-1.3                | about 3       |

| programming           | by external means      | internal               | internal      |

| technique             | hot electron injection | hot electron injection | tunnel effect |

| voltage               | 12.5 V                 | 12 V                   | 5 V           |

| resolution            | byte                   | byte                   | byte          |

| time taken            | <100 µs                | <10 µs                 | 5 ms          |

| erasing               | by external means      | internal               | internal      |

| technique             | ultraviolet light      | tunnel effect          | tunnel effect |

| voltage               | 12.5 V                 | 12 V                   | 5 V           |

| resolution            | whole chip             | whole chip or block    | byte          |

| time taken            | 15 min                 | 1 s                    | 5 ms          |

There is first of all the relative size of the memory cel (transistor) for one bit; this is an important factor, since the density of the chip, that is, bits per unit area, determines the quantity price of the memory. If the area occupied by one cell in a standard EPROM is taken as unity, that in a Flash EPROM is 1.2-1.3, and in an EEPROM about 3. Assuming equal production quantities, that would make the Flash EPROM 20-30% dearer than the standard EPROM. The EEPROM, particularly since its production quantities are much smaller, is much more expensive than these two. At the time of writing (spring 1992), the price of a 1 Mbit Flash EPROM, in quantities of 1000, is £10-£12 each, while that of Intel's 8 Mbit Flash EPROMs (which they call FlashFile<sup>™</sup> memories-Type 28F008SA) in quantities of 10 000 varies from £18 for the 120 ns version to £24 for the 85 ns version. Those prices are expected to come down rapidly over the next 12-18 months as more players enter the field.

Another aspect of chip density is that with current 1 µm technology only a certain number of transistors can be deposited on to a given area. At present, most DRAMs, EPROMs and Flash EPROMs are manufactured with a density of 1 Mbit per chip (although Intel introduced an 8 Mbit type in early 1992), and most static RAMs and EEPROMs with a density of 256 Kbit per chip.

Other important factors are the technology and manner of, and time taken for, programming of the memories. Between the three types, there is no difference in resolution: all three types can be programmed byte by byte, although the standard EPROM has the disadvantage that this must be done by an external apparatus. The other two types can be programmed in the equipment in which they are used, since the most important parts of the programming logic have been integrated in them. To make updating of an EPROM at a later date possible, the chip must be fitted in a socket, which increases manufacturing costs of the equipment in which it is used, ignoring for a moment the extra cost of updating to the user.

There is another aspect connected with programming: EPROMs and Flash EPROMs need an auxiliary voltage of 12 V, otherwise the hot electron injection technology does not work. An EEPROM can operate with the 5 V normally available in the computer: it raises this internally to 18 V. Since the load presented by a Flash EPROM on the 12 V supply is negligible (it draws no more than 30 mA), and most computers have a regulated +12 V line available, there is not likely to be a difficulty. If nevertheless there is no 12 V line available, a tiny voltage converter in a DIL package must be added at a cost of some £2.

It is also interesting to look at the time taken by the programming. A 1 Mbit EPROM needs not less than 15 s, whereas a Flash EPROM is programmed in about 1.5 s. An EEPROM may take minutes!

The technology and manner of erasing is also quite different. An EPROM must be removed from the apparatus in which it is used and be radiated for about 15 minutes with ultraviolet light in a special unit. Flash EPROMs and EEPROMs are electrically erasable and can, therefore, remain in the equipment in which they are used.

As far as the user is concerned, erasing an EEPROM is a normal read operation. Each byte can be erased and re-programmed separately. Since, as already mentioned, this can be a lengthy process, many (large) EEPROMs can be programmed in the socalled page mode at 16 or 32 times the normal speed.

A Flash EPROM is erased in a manner similar to that of an EEPROM, but it is not possible to do this byte by byte, that is, the entire memory or a block or blocks of bytes is erased. Erasure time for a 1 Mbit model is 1-4 s; moreover, before erasure can take place, all bits must be set to '0'.

It is clear that the Flash EPROM looks the most advantageous of the three memories. Its drawback of being erased completely, or in blocks, as compared with the byte-bybyte erasure of an EEPROM is more than made up by the speed with which it is erased (and re-programmed)—whence its name.

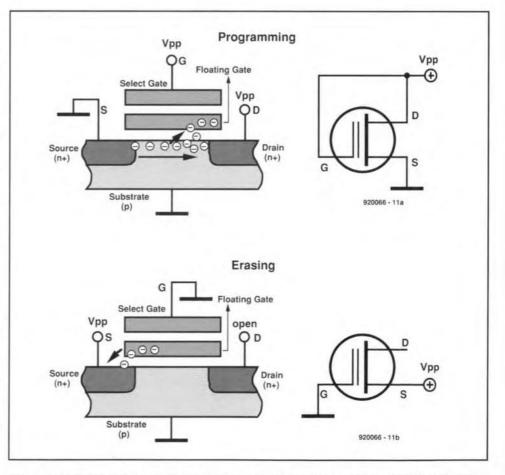

#### Construction and operation

The construction of a Flash EPROM differs not all that much from that of an EPROM. A bit is stored in the floating gate of a discrete MOS transistor—see Fig. 1. The figure also illustrates the manner in which programming and erasing take place. In the *p*substrate are two  $n^+$  zones that function as the drain and source of a MOSFET. Between the usual gate, that is, the select gate, and the channel there is another gate, the floating gate. The two gates are totally isolated from each other and from the substrate by a layer of silicon oxide. When the memory is erased, the floating gate is uncharged with respect to the source. When the drain is conTable

nected as normal to the Vpp line and the transistor is enabled via the select gate, the channel conducts and a logic 1 is available at the source. Programming such a cell requires a negative charge in or at the floating gate, which is not simple to arrange, since that gate is totally isolated.

That difficulty is overcome with the hot electron injection technique. Briefly, this process works as follows. If the cell is aranged as in Fig. 1a, the voltage at the drain and the gate is +12 V, and the source is at earth potential, a channel is formed through which a relatively high current flows. When that happens, a number of so-called hot electrons ensue and these capture other electrons from the substrate material; because of the high electron density, some of these electrons reach the oxide layer between substrate and floating gate. Because of the high potential of the select gate, several electrons actually pass through the substrate and reach the floating gate. The electron cluster so caused at the floating gate remains (according to the manufacturers for at least ten years) even when the +12 V programming voltage is removed. Thus, the floating gate is negative with respect to the source and the memory cell is inhibited.

In an EPROM there would be only one permissible way back: via ultraviolet light. For that reason, EPROMs have a window in the housing of the chip. Ultraviolet light has enough energy to remove the electrons from the floating gate.

A different process, based on the tunnel effect, is used in EEPROMs. Because of this effect, electrons are able to tunnel through a narrow potential barrier that would constitute a forbidden region if the electrons were treated as classical particles. However, quantum mechanics indicates that there is a definite probability of electrons tunnelling through the barrier. This technique, although slower than the injection process, has the advantage of permitting electrical erasing.

The Fowler-Nordheim variant of the tunnelling technique is used for erasing Flash EPROMs. Briefly, it operates as follows. If the memory cell is arranged as in Fig. 1b,

Fig. 1. Schematic representation of the construction and operation of a Flash EPROM.

**ELEKTOR ELECTRONICS OCTOBER 1992**

30

the source is at +12 V, the drain is at earth potential, and the select gate is open, electrons will tunnel from the floating gate to the source. The floating gate will attain the same potential as the source so that the transistor is on, that is, erased.

The erasing process in a Flash EPROM is even slower than that in an EEPROM, because it happens at a lower internal potential. It is, however, kinder on the oxide layer and altogether more reliable. A Flash EPROM can therefore be cycled considerably more times (up to 100 000) than an EEPROM (a few thousand). The real difference between an EPROM and a Flash EPROM lies in the much thinner oxide layer between substrate and floating gate in the latter. Moreover, the architecture of the floating gate of a Flash EPROM is optimized for the tunnelling process, resulting in shorter write/erase times.

#### Types and properties

To prevent spurious voltage levels or voltage peaks, occurring when the apparatus in which a Flash EPROM is used is switched on or off, from modifying the stored information, the chip is provided with logic that enables the erasing or programming mode only if well-defined combinations of levels exist in a fixed sequence at the control pins of the chip. The algorithms needed for the erasing or programming are available from the manufacturers of the memory.

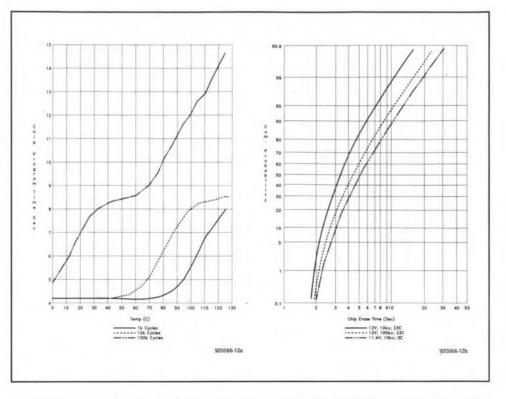

From a reliability consideration, it is important to know how a Flash EPROM behaves after a great many erase/write cycles. Manufacturers normally guarantee no fewer than 10 000, but Flash EPROMs usually still function properly after 100 000 cycles. It is interesting to note that with increasing cycling not one or more bytes become useless (which may, of course, happen once in a while), but that the erase/write times increase. Figure 2 shows the relevant correlations for a 2 Mbit (512 Kbyte capacity) Type 28F020 Flash EPROM from Intel.

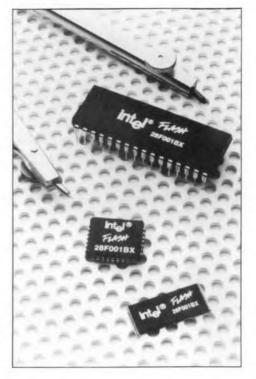

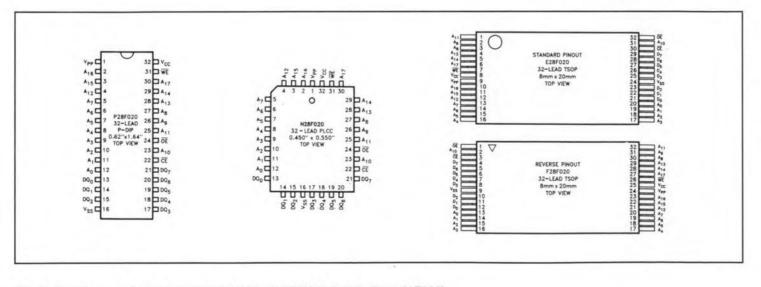

Flash EPROMs are normally housed in 32-pin DIL cases (see Fig. 3) which makes it possible to substitute them for pin com-

Fig. 2. Time taken by programming and erasing of Flash EPROMs as a function of the number of times the devices have been cycled.

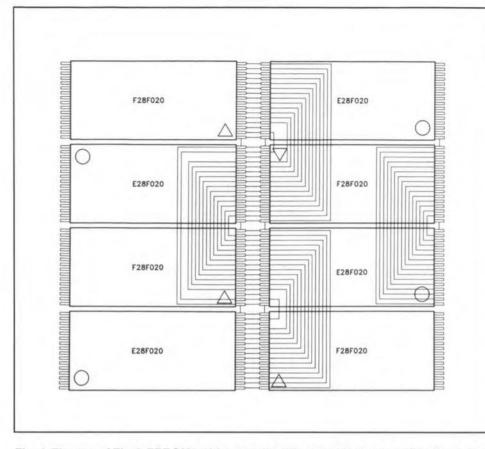

patible EPROMs or static RAMs. There are other housings available, for instance, the 32lead TSOP, which has the advantage of being very shallow (thickness 1.25 mm). The TSOP version is also available with a different pinout: standard E type, modified F type. As shown in Fig. 4, mixing these two types can simplify the layout of a printed circuit board greatly.

At the time of writing (spring 1992), standard Flash EPROMs are available with capacities ranging from 256 Kbit to 8 Mbit. Like EPROMs they are organized in bytes (8-bit data). Indications are that within 18–24 months there will be 16 Mbit versions (2 Mbyte).

There are also special types available, for example, the Blocked Flash EPROM that contains a number of individually erasable blocks, such as Intel's 1 Mbit Type 28F001BX in which block 1 has a capacity of 8 Kbyte; blocks 2 and 3 one of 4 Kbyte; and block 4 one of 112 Kbyte. This type is particularly aimed at IBM compatible PCs, where block 1 would function as boot loader, blocks 2 and 3 as data store and block 4 as BIOS.

Finally, there are Flash EPROMs that function as SIMMs (Single Inline Memory Modules) or are used in memory cards with memories from 1 Mbyte up to 20 Mbyte.

#### Applications

When a Type 28F001BX is used in a PC, the BIOS of that computer can be updated at any time without the need for opening it. All the manufacturer has to do is to send his customers a diskette with the relevant program. Since this is a good sales point, many

Fig. 3. Housings and pinouts of a 2 Mbit Flash EPROM (Intel's Type 28F020).

Fig. 4. The use of Flash EPROMs with mutually different pinouts simplifies the design of a printed circuit board greatly.

PCs have already been equippped with this Flash EPROM.

In Notebook computers, it is possible to incorporate the entire operating system in Flash EPROMs. The Notebook can then be updated as and when required. Manufacturers of operating systems such as Digital Research and Microsoft already offer their DOS in EPROM versions, and are now working on commercial operating systems using Flash EPROMs.

Flash EPROMs are also of great interest for industrial control equipment; they would enable such equipment to be reprogrammed without this having to be opened, which would reduce servicing costs.

Fig. 5. The Mustang accelerator card from Pyramid Computer, intended primarily as a retrofit for HP Laserjet printers, uses Intel's Type 28F020 Flash EPROM.

FLASH EPROMS

Even more fascinating is the use of Flash EPROMs in apparatus whose operation depends on integrated software, such as modems and printers whose control software is normally contained in ROMs or EPROMs. With today's rapidly moving technology, such equipment is hopelessly out of date after about three years from purchase. This is particularly true of laser printers. Updated versions of page description languages, such as Adobe's PostScript or Hewlett Packard's PCL, appear at fairly short intervals. Many users would love to have a laser printer that can be updated easily. To meet that wish, the German firm Pyramid Computer has brought out an accelator card (see Fig. 5) for laser printers that contains a fast RISC (Reduced Instruction Set Coding) processor and a 2 Mbyte Flash EPROM. The latter device stores an easily updatable PostScript clone and the necessary fonts.

Manufacturers are also working on the replacement of the hard disk drive in laptop and notebook computers by a Flash EPROM, which would mean a reduction in current consumption (by a factor of 3-5) as well as in weight and size. Furthermore, the computer's reliability would increase tenfold.

The 16 Mbit chip, which is not far off, will enable the production of memory cards in the form of a 3.5 in diskette (or even smaller) with a capacity of 50 Mbyte. As yet, there are some drawbacks. First of all, the write speed of a current Flash EPROM is only about double that of an HD diskette, that is, roughtly ten times slower than a modern hard disk. Another one is the incompatibility with systems like MS-DOS™. However, Microsoft has already produced a DOS using Intel's FlashFile<sup>™</sup> memory architecture.

Today's graphics oriented operating systems such as Microsoft Windows™, IBM's OS/2 and Apple's Finder may slowly but inexorably be replaced by solid-state architecture.

For the present, although technically Flash EPROMs can already replace diskettes, their price has to come down substantially before they can do so commercially. After all, 1 Mbyte on diskette today costs pence rather than pounds or just over a dollar.

#### References

Memory Products Data Book, AMD

Memory Products Data Book (210 830 010), Intel

Blocked Flash Memory Type 28F001BX, Data Sheet, Intel

Thin Small Outline Package Data Book (296514-001), Intel

Mustang Accelerator Card for Laser Printers, Data Sheet, Pyramid

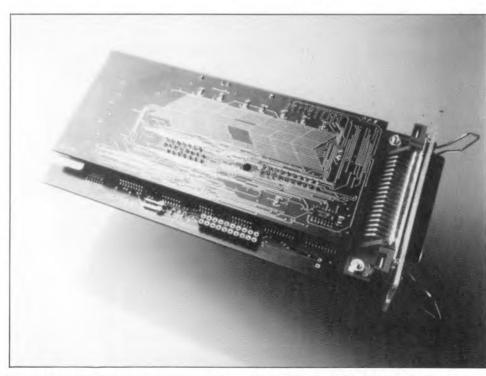

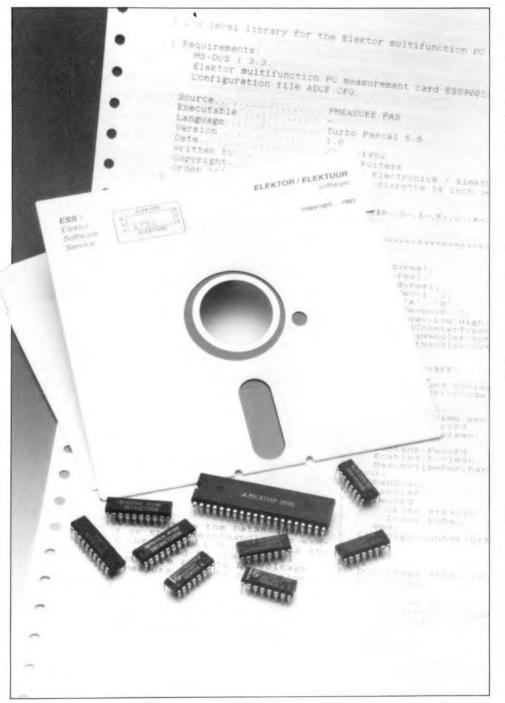

### PASCAL ROUTINES FOR MULTIFUNCTION MEASUREMENT CARD

This article presents a collection of Turbo Pascal routines that should assist constructors of the Multifunction Measurement Card for PCs in writing their own application software.

#### Design by J. Ruiters

32

**P**ART of the success of the Multifunction Measurement Card publication (Ref. 1) must be due to the application software developed for it, for instance, that for the multi-channel voltmeter/frequency meter, and the computer-controlled weather station modules. This application software is remarkable because they allow you to set up, say, an advanced data acquisition system built around a PC, without much knowledge of IBM PC hardware and programming languages such as C and Pascal.

None the less, 'low-level' programming remains of interest to many enthusiastic users of the measurement card, witness the large number of requests we received for hints on programming, for example, the ADC (analogue-to-digital converter) contained on the card. These requests are honoured by the present article, which presents software that shows how the various I/O protocols, A-D functions and frequency measurement algorithms may be put to use. In fact, we have thrown together, in a kind of library, a large number of elementary routines for the control of the measurement card. Both 'die-hard' programmers and beginners should find this library, written in Turbo Pascal 5.5, of great use in the development of their own application programs.

A typical feature of today's electronics is that hardware and software are efficiently combined to achieve target specifications. Depending on certain requirements (cost, speed, flexibility and available firmware), a system designer must consciously decide to implement a function either in hardware or in software. Such considerations have also existed in the early design stages of the measurement card. The large computing power of the IBM PC was the factor that made us decide to choose hardware (MSI and LSI building blocks) only for those applications that are impossible, or very difficult, to realize with the aid of software. This decision does have consequences: on the one hand, it means inexpensive hardware and a high degree of flexibility; on the other, a fairly complex piece of programming. Fortunately, the last point is not a problem any more thanks to the availability of the software we present here. This software is available on a diskette with order code ESS 1751.

The unit PMEASURE.PAS, or the compiled version of it, PMEASURE.TPU, con-

| MULTIFUNCTION    |   |

|------------------|---|

| MEASUREMENT CARD | l |

| FOR PCs          |   |

MAIN SPECIFICATIONS

#### DC Voltmeter Range: 0.1 V to 300 V Inputs: eight A-D converter: 12 bits, 3 μs, 0 to 5 V

#### **Frequency meter**

Range: 0.0025 Hz to 10 MHz Inputs: eight (TTL) Max. error: 0.0001% Accuracy: 6 digits

#### Pulse time meter

Range: 0 to 400 s Resolution: 0.1 µs Adjustable measurement level

Event counter Range: 32 bits Max. frequency: 10 MHz Adjustable trigger edge

#### Time related measurements

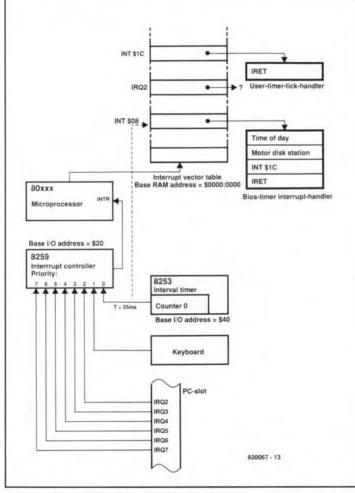

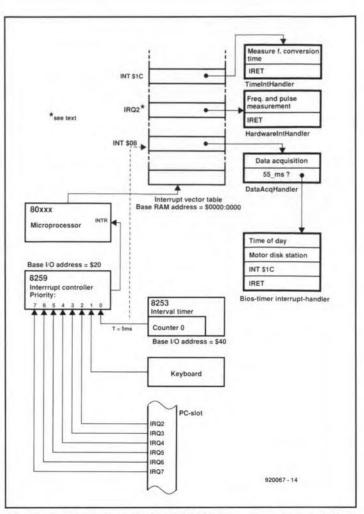

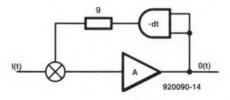

PMEASURE makes the best possible use of the available hardware facilities. Hence, the pulse time and frequency measurements are fully interrupt-driven. The IRQ input used in the PC needs to be set in hardware as well as in software. On the measurement card, one of the jumpers JP2 to JP7 is fitted in the X-row. Make sure to use a free IRQ line (usually IRQ2), and check that jumper JP8 is in position E. As to the software setting, the IRQ line must be identified in line 5 of the configuration file (see Fig. 1).

Depending on the type of measurement, a measurement cycle starts with a call to StartPulseTimeConversion or StartFrequencyConversion. The associated interrupt routine, HardwareIntHandler, starts automatically the moment hardware flag EOC-F is actuated. This happens at the end of each (sub-) conversion. By virtue of the interrupt procedure, the entire measurement remains fully transparent to the main program. Yet, the measurement results are simple to call up by subsequently reading the records called PulseTime and Frequency.

A second interrupt routine plays an important role when frequency measurement is used. A routine called TimeIntHandler monitors the time taken by the second phase of the measurement (fm'), and verifies this time against the maximum conversion time calculated during the test measurement. When the time limit is exceeded, this is taken to mean that the fre-

Fig. 1. Parameters in the configuration file ADCF.CFG may be edited with any ASCII-compatible wordprocessor.

tains, among others, functions for PPI initialization, multiplexer control, A-D conversion, digital I/O and pulse time and frequency measurement. These and all other procedures and functions that are declared in the unit may be called directly from the associated source file using the command 'uses PMEASURE'.

Before discussing the programming routines, we take the opportunity to refresh your memory: the 'specs' box of the measurement card is repeated on this page. Also, we suggest to once more go through the whole article on the measurement card.

#### Pascal unit

The effect of a unit function is nearly always apparent from the name: e.g., SelectFreqChannel(Channel:ZeroToSeven) connects channel number 'Channel' of multiplexer IC22 to the frequency meter. Where necessary, the declared constants, variables, procedures and functions are described by a few words of 'comment'. This comment obviates the need of a detailed description to be rendered here: for more information, refer to the source code.

The peripheral interfaces (PPIs), IC13 and IC14, are read from and written to via the procedures ReadPPI and WritePPI respectively. Although these are really very basic routines, they form the nucleus of the card control system. ReadPPI and WritePPI are, therefore, frequently called by other procedures and functions. Among the 'users' are: InvertInput, CounterValue, GetCurrentAnalogChannel, SelectRatioIO and StartEventCounter.

During the initialization phase, PMEA-SURE automatically loads the hardware configuration file ADCF.CFG, and the presence of the measurement card at the set base address is checked. If the card is found, the PPIs are automatically initialized at the end of the test (see the InitPPI routine in PMEASURE.PAS). This is an important event, because it takes place **before** the control program proper (i.e., your software) is started. The Boolean variable 'HardwareFound' thus allows software to decide to go on (card found) or not (card not found).

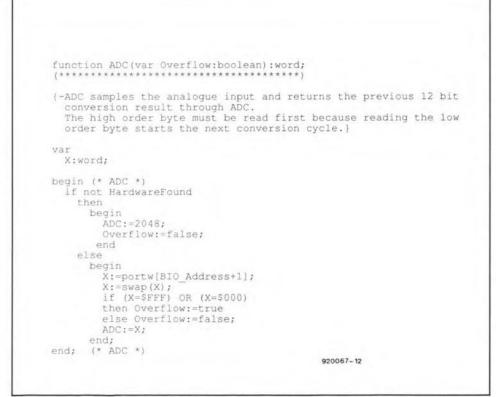

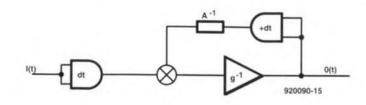

Fig. 2. This ADC function is one of the many routines contained in PMEASURE.PAS.

#### 33

| \$300<br>10000000<br>10<br>2.5<br>2 | RefFreq :<br>MaximumGateTime:<br>RefVolt : | Possible values are \$300 (JP1=A) and \$310 (JP1=B<br>Frequency meter (crystal-) reference in Hz.<br>Typical 410 seconds (10 Mhz referency frequency)<br>ADC full-scale voltage<br>Hardware interrupt (Possible values: 2 7) |

|-------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     |                                            | 920067-11                                                                                                                                                                                                                    |

34

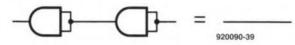

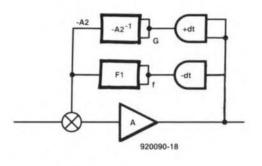

Fig. 3. Schematic representation of the standard PC interrupt network.

quency of the input signal has gone down so far that the test measurement and the set scale factor are no longer representative. To prevent frequency measurements taking up too much time, TimeIntHandler breaks off the current conversion, and starts a new test measurement. The procedure itself makes use of the PC-user-timertick-interrupt (\$1C), and is therefore actuated every 55 ms.

#### DC measurements

The function 'ADC' (Fig. 2) allows a 12-bit binary representation of an analogue input voltage to be acquired. The important thing about ADC is that the A-to-D conversion operations are not started until at the end of the function. This means that the value of ADC is related to the previous conversion, and, inevitably, that the first conversion result is meaningless.

Functions SelectAnalogChannel and SelectRatioIO are intended for the control of the input multiplexer (IC10), and the setting of the stepped attenuator (IC12), respectively.

Since the analogue circuitry on the measurement card is designed for direct voltages, it would seem logical to base each measurement result on an average obtained from a number of samples. This so-called stochastic measurement enables noise pulses to be suppressed efficiently.

The ADC function is called from a periodic interrupt routine to make sure that the d.c. measurements can run in the background, just as the frequency and pulse time measurements. The TimeIntHandler is not suitable to control the timing: being started 'only' 18.2 times a second, it is too slow, and would cause a stochastic calculation using, say, 100 samples, to take far too long. A different data acquisition routine was, therefore, devised, to make sure that the selected input can be sampled at 200 Hz. This sounds simpler than it is, because the only periodic interrupt that is still available in the IBM PC is the usertimer-tick, which runs at a rate of 55 ms. Drastic measures are required to make sure that a much shorter interrupt period is available. This is achieved by replacing the BIOS timer interrupt handler (interrupt \$08) by the data acquisition procedure 'DataAcqHandler'. After having reprogrammed the system clock prescaler, the handler is called at the desired rate, i.e., every 5 ms. The new scale factor (divisor) is supplied by ReProgTimer, while UnDoReProgTimer restores the default factor later.

To make sure that the real-time clock and the diskette station motors continue to function normally, the original BIOS timer interrupt handler (and, with it, interrupt \$1C) is started with the original frequency, and from the DataAcqHandler. For clar-

Fig. 4. As Fig. 3, but with the PMEASURE routines installed. Note the way the BIOS interrupt handler is given new parameters.

ity's sake, the usual interrupt network is drawn in Fig. 3, while Fig. 4 shows the configuration with the new interrupt routines installed.

#### Get cracking

Apart from the Pascal library, diskette ESS 1751 also contains an example program, PMDEMO.PAS. This program serves to demonstrate how the interrupt procedures are installed and removed, and show you how to get access to the measurement results. Incidentally, a nice feature of PMDEMO is that it makes use of the AutoScan mode. In this mode, the interrupt routines ensure that all channels defined in FChanScan and VChanScan are measured one by one.

As a matter of course, PMEASURE may be extended or adapted to meet your requirements. This will cause few problems as long as you keep to the rules of proper programming. Take care, however, with the special rules that apply to stack use and DOS interrupts, since these have many pitfalls in store for the 'unwary'. Once bitten, twice shy!

#### **Reference:**

1. "Multifunction measurement card for PCs", *Elektor Electronics* January and February 1991.

### 8051/8032 ASSEMBLER COURSE

### PART 7: SERIAL INTERFACE PROGRAMMING

Perhaps unwittingly, you have been using the serial communication features of the 8051 or 8032, and the supporting routines contained in the system monitor, EMON51, ever since the 80C32 singleboard computer (our 'course hardware') wrote its first 'welcome' message on your terminal. In this course instalment we will explore the not-so-simple operation of the serial interface with an aim to grasp the way it is programmed.

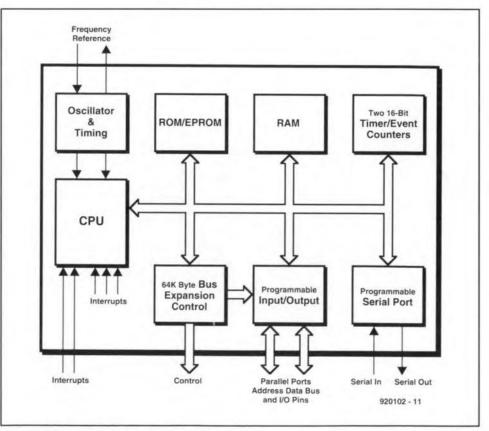

#### 8051 serial interface

The serial interface contained in the 8051 family of microcontrollers is the most complex 'on-chip peripheral'. Hence, this instalment is probably the most difficult of all in the course, and should be studied thoroughly. This effort is also required, unfortunately, on part of those of you who intend to implement only very basic serial communication on a 8051-based controller system, and even if a range of examples of software building blocks is available in the system monitor, EMON51.

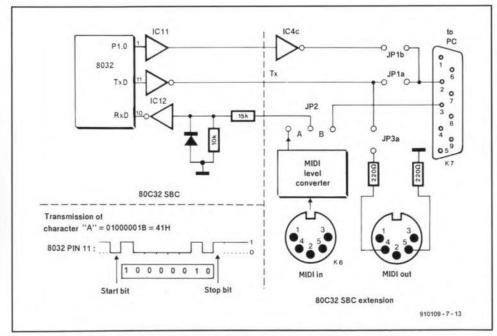

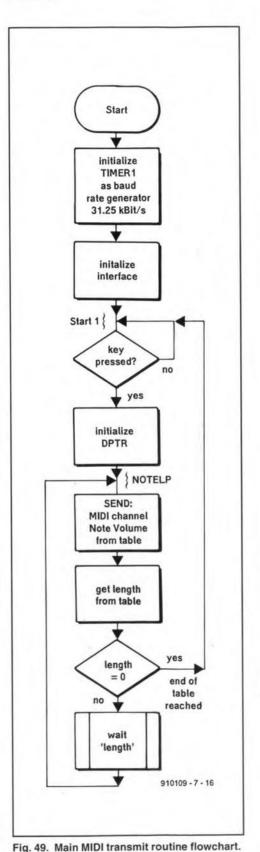

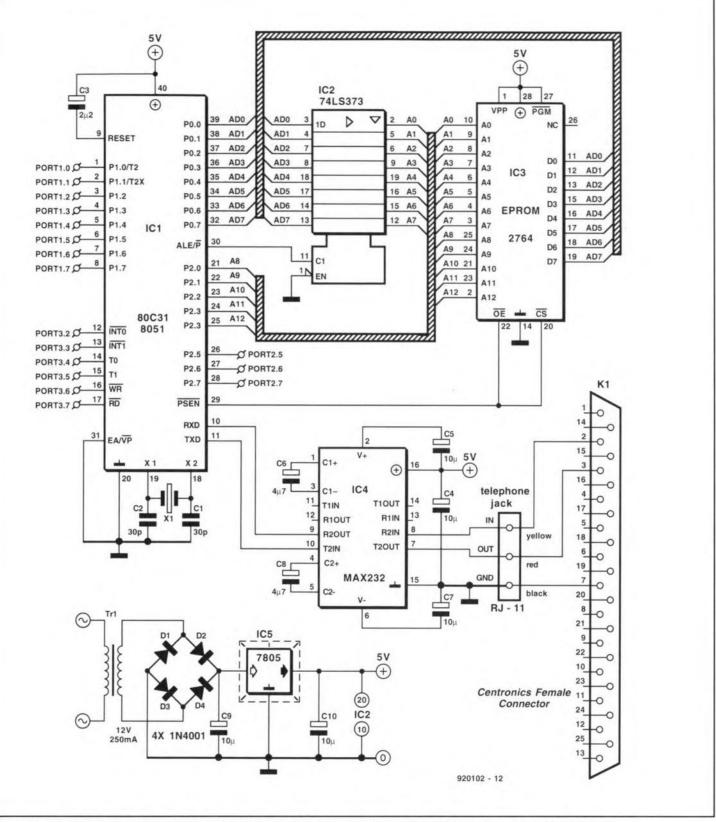

The serial interface can operate in a number of modes, some of which are of little interest here because they serve to implement 8051 network systems. We will concentrate on the simplest mode of operation: sending and receiving 8-bit data (asynchronously) with one start bit, one stop bit, and no parity. This mode allows the 80C32 SBC to communicate with a PC, as well as to exchange MIDI data (MIDI = musical instrument digital interface).

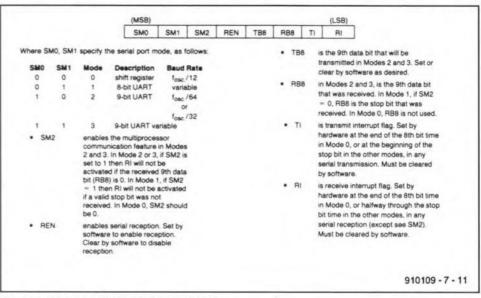

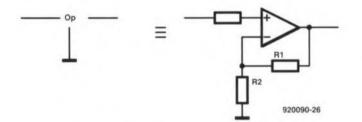

The special function register (SFR) identified as SCON (Serial CONtrol) at address 098H serves to control the onchip serial interface, and determine its mode of operation. The function of the bits contained in the SCON register are shown in Fig. 44. The mode we require can be set by programming SM0=0 and SM1=1. As shown in Fig. 44, this is mode 1, in which bit SM2 may be used to signal transmission errors. The function of the remaining bits in SCON will be reverted to below.

#### The transmit and receive buffers

Inside the 8051, serial data is transmitted and received with the aid of a shift register. Bits are transmitted by first loading them, in parallel, into the shift register, and then shifting them out, one by one, at By Dr. M. Ohsmann

Fig. 44. Overview of SFR SCON bit functions.

the programmed bit rate (baudrate). In receive mode, the bits are gathered, one by one, into the shift register, and are read out in parallel when all are in. In the 8051, the SFR called SBUF (at address 099H) is used as a receive and data buffer. It has the 'quasi-double' functions of a 'receive' buffer, and a 'data' buffer, the relevant function being selected by read or write operations on SBUF, respectively.

The transmit and receive functions are supported by their own shift registers, so that it is actually possible to transmit and receive simultaneously (full-duplex operation).

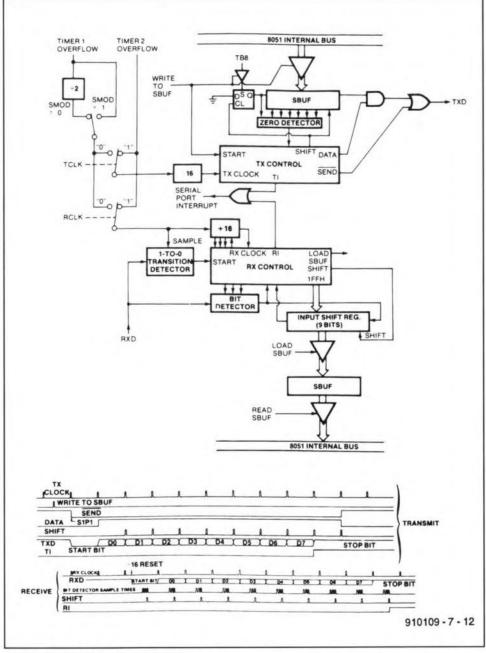

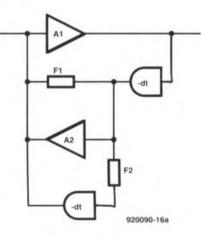

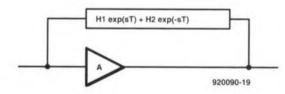

### Configurations and functions

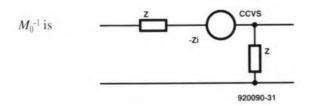

Figure 45 shows the internal structure of the serial interface contained in the 8051 family of microcontrollers. The baudrate generator is shown in the upper left-hand corner of the diagram. The overflow pulses produced by Timer 1 or Timer 2 (8052 only) may be used to clock the shift registers. The switch marked 'SMOD2' controls a divide-by-two scaler. The switches RCLK and TCLK (8032 and 8052 only!) select the receive clock and transmit clock respectively. The clock signals so obtained are divided by 16 before they are fed to the TX-CONTROL and RX-CONTROL sections.

The transmit control clocks and loads the transmit shift register, whose output is connected to the TXD terminal (pin 11) of the 8051 (upper part of the drawing). From the internal databus of the 8051, the databits are fed in parallel into the SBUF register. The 'zero-detector' finds out if all bits have been transmitted. If so, this is signalled to the transmit control section, which in return is capable of generating a serial port interrupt, TI. When this happens, the TI bit (SCON.1) is set.

35

The lower part of Fig. 45 shows the receive control section. Serial databits received on pin 10 (RXD) of the 8051 are gathered in the receiver shift register. The data simultaneously arrive in the 1-to-0 transition detector, which serves to recognize the start bit in the serial datastream, and to synchronize the receiver clock with the incoming bits. Data reception starts on a high-to-low level transition (falling pulse edge) at the RXD input, i.e., a start bit at pin 10 of the 8051. The incoming bits are clocked into the shift register. The last bit that is read is the stop bit (the receiver shift register has a width of 9 bits). Next, SBUF is loaded with the eight received bits, and the 'receiver full' bit is set (SCON.0=RI). This sequence does not take place, however, in the following two cases:

1). When RI is already set, which means that previously received data was not fetched.

2). When SM2=1, and the stop bit did not have the value '1'. Thus, by programming SM2=1, you can prevent bytes with a framing error (wrong stop bit) getting through.

The level of the RI bit thus allows us to check if a received byte is held ready in 36

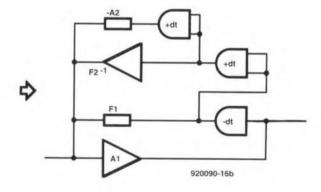

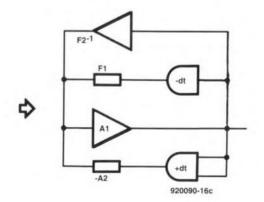

Fig. 45. 8051 serial interface architecture.

Fig. 46. V24 interface (80C32 single-board computer and extension board).

SBUF. If so, the byte can be fetched (read) for further processing.

The two interrupt events, TI (transmitter interrupt) and RI (receiver interrupt) actually generate only one interrupt, of which the cause (data transmitted, or data received) must be established by the interrupt software. The serial interface only generates interrupts when bit IE.4 in the interrupt enable register is set (see Part 6 of this course).