THE INTERNATIONAL ELECTRONICS MAGAZ

8 extra pages Results of our May competition

# **EPROM EMULATOR II** 23 cm transmitter-receiver

Current-sense power MOSFETs

CAN-controller area network

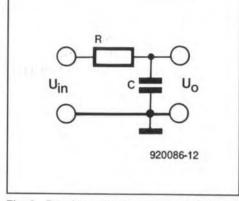

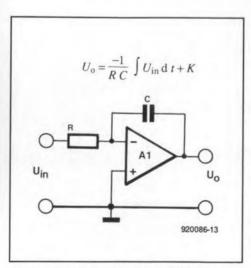

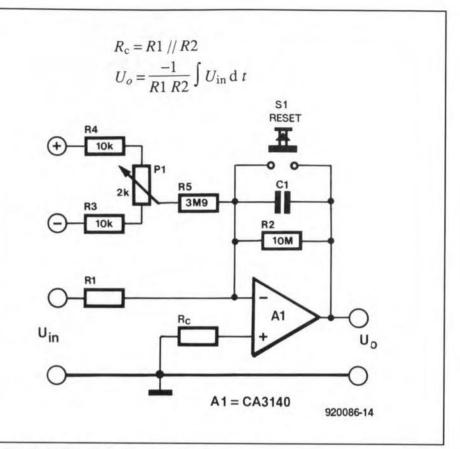

Analogue opamp integrator circuits

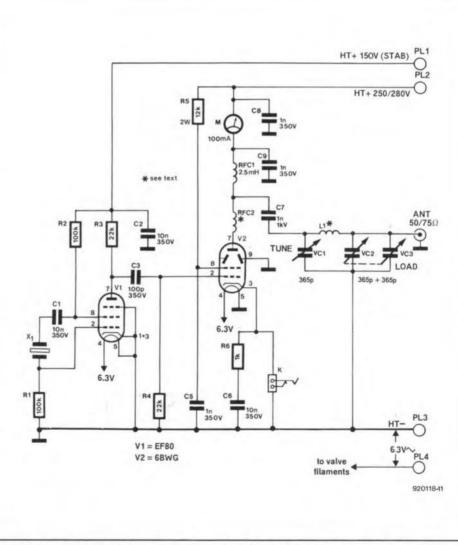

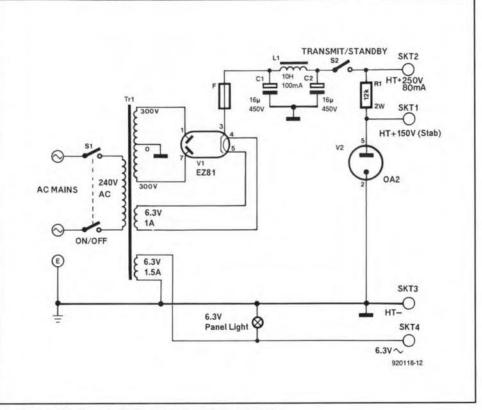

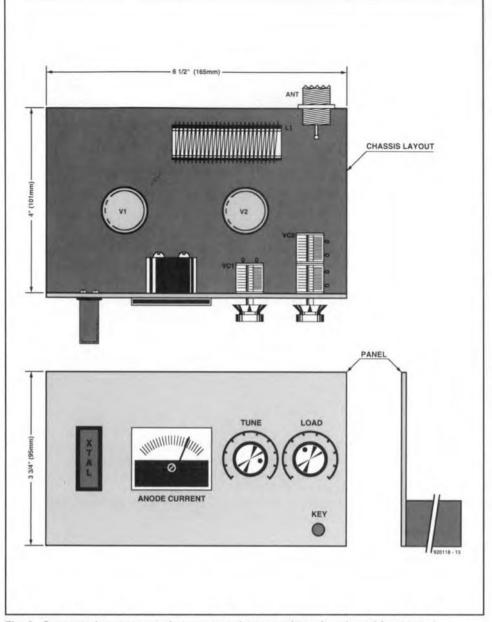

Antenna evaluation transmitter

#### In next month's issue (among others):

- Mains sequencer

- Flash EPROMs\*

- 8051 SBC

- · History of the valve

- Active antenna for the 10 kHz – 220 MHz band

- Pascal routines for measuring card

- 8051/8032 assembler course Part 7

- AF digital-to-analogue converter – final part

- RDS demodulator

\* It is regretted that, owing to circumstances beyond our control, this article has had to be postponed from the September to the October issue.

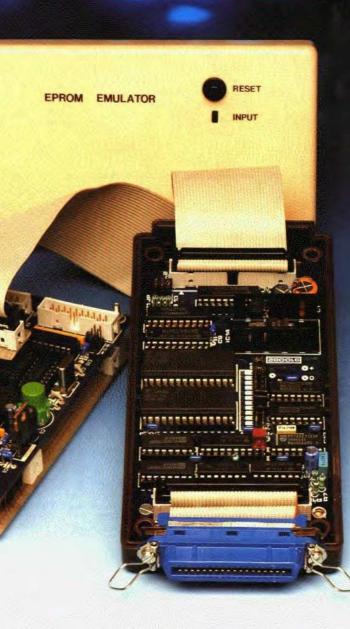

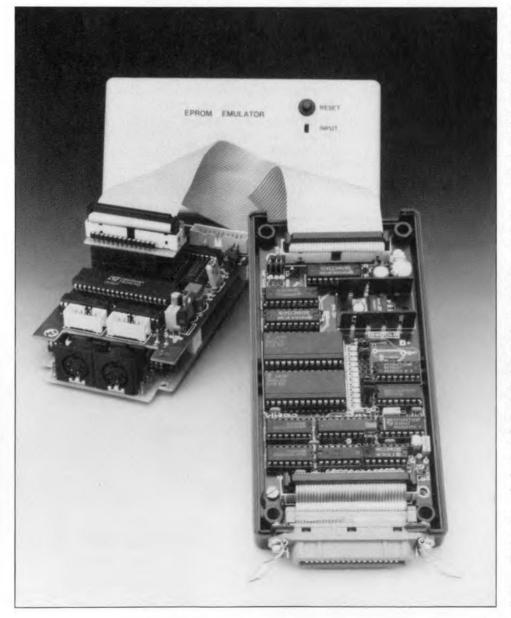

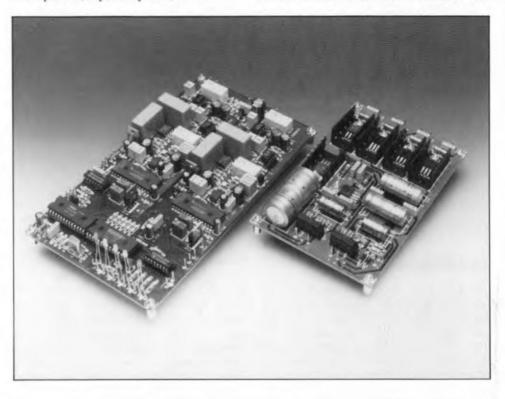

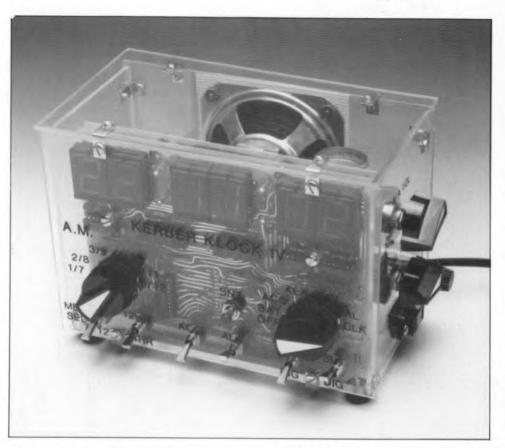

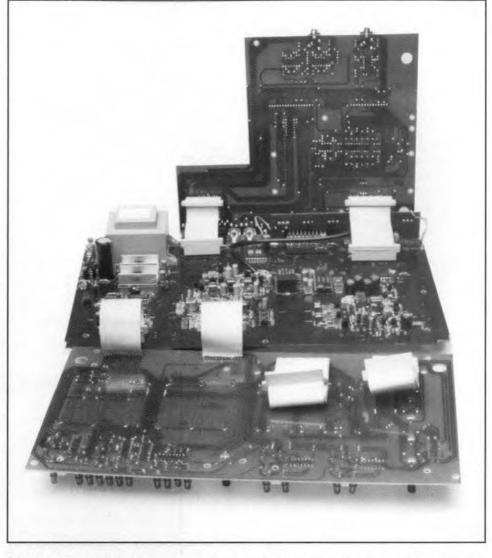

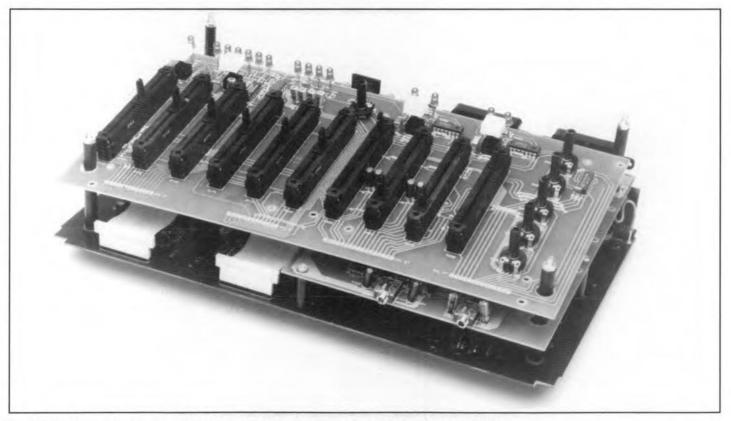

#### Front cover

The photograph shows the updated version of the EPROM emulator we published about three years ago. In the present circuit, conventional rather than surface-mount (SMD) components are used, since a number of readers. particularly those outside Europe and North America, have found difficulty in obtaining and handling SMD devices. The updated version has 64 Kbyte of RAM and is capable of emulating Types 2764 through 27512.

Copyright © 1992 Elektuur BV

# CONTENTS

## Results of our 200<sup>th</sup> issue competition p. 69

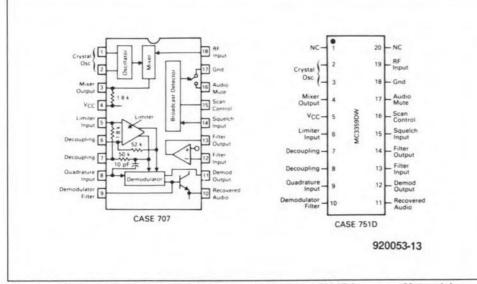

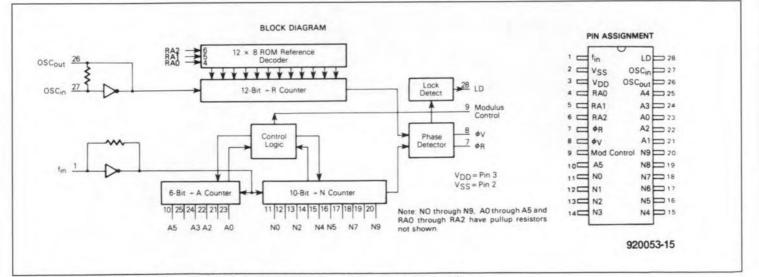

#### **AUDIO & HI-FI**

- PROJECT: A.F. digital-to-analogue converter Part 2 Design by T. Giesberts

PROJECT: Audio-video processor – Part 4 (final)

- **PROJECT**: Audio-video processor Part 4 (final) an ELV design

### COMPONENTS

53

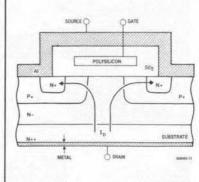

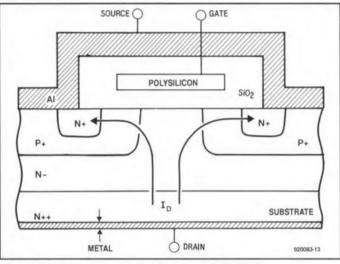

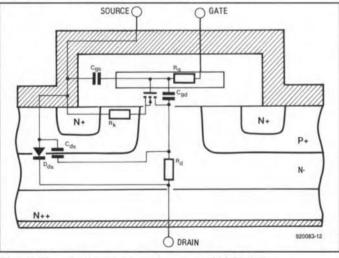

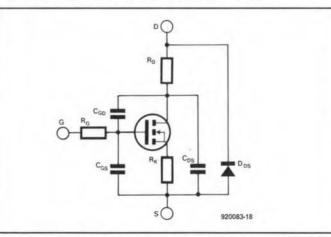

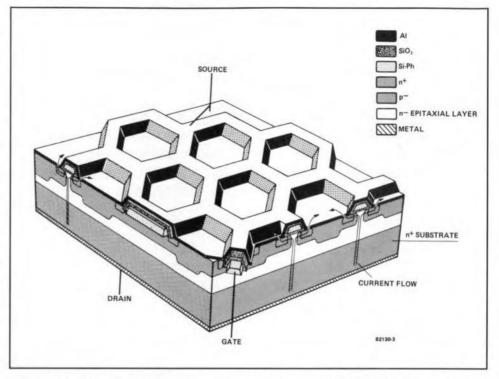

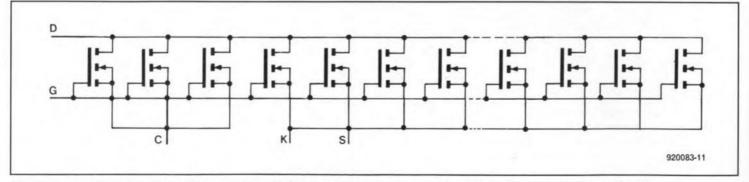

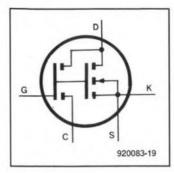

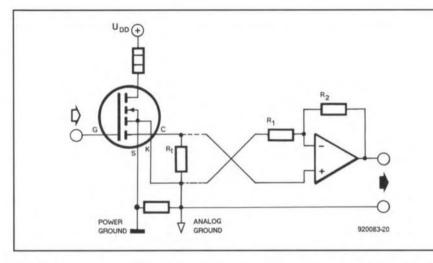

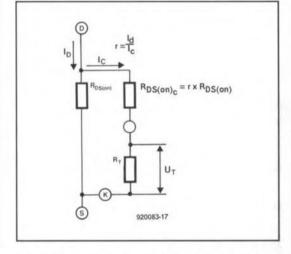

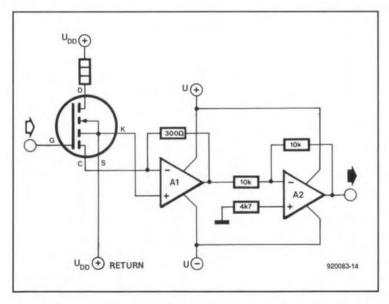

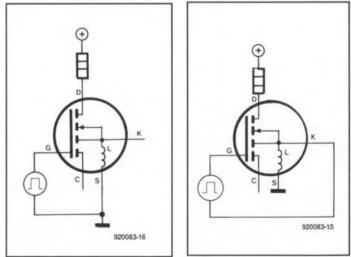

Current-sense MOSFETs by J. Ruiters

### **COMPUTERS & MICROPROCESSORS**

PROJECT: EPROM emulator II Design by B.C. Zschocke and N. Breidohr

COURSE: 8051/8032 assembler - Part 6 by Dr M. Ohsmann

#### DESIGN IDEAS

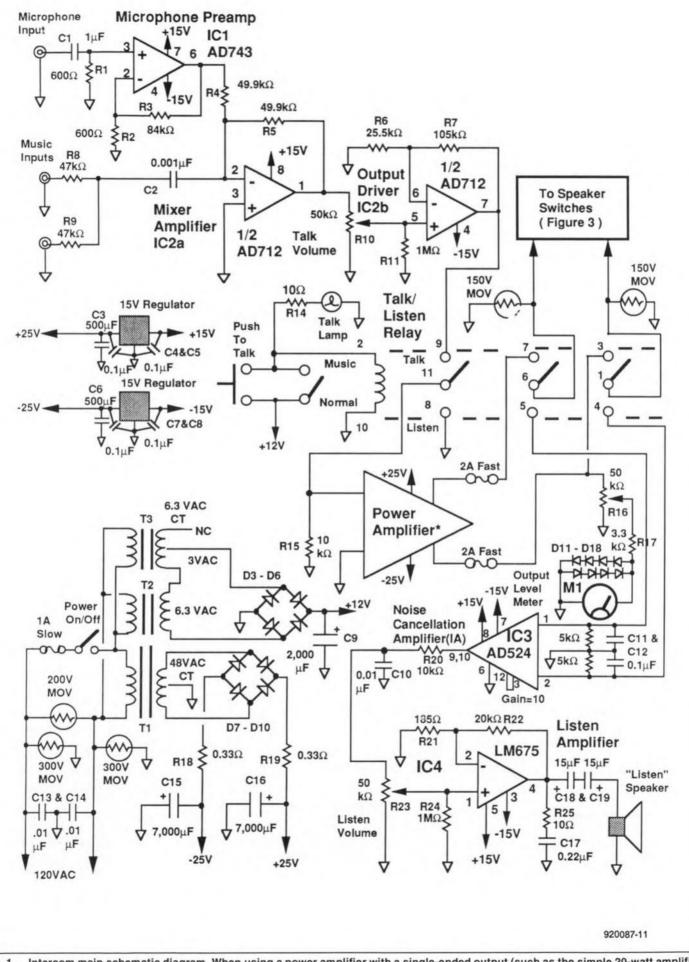

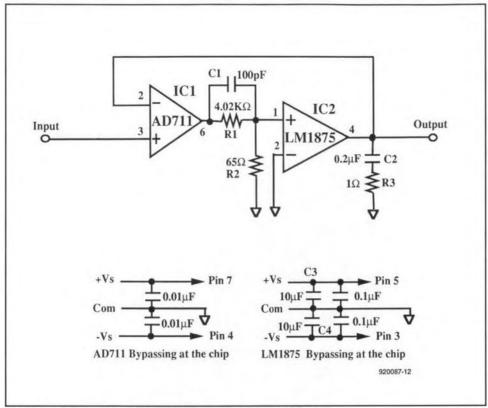

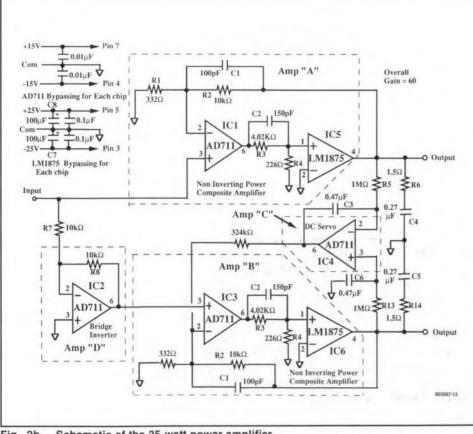

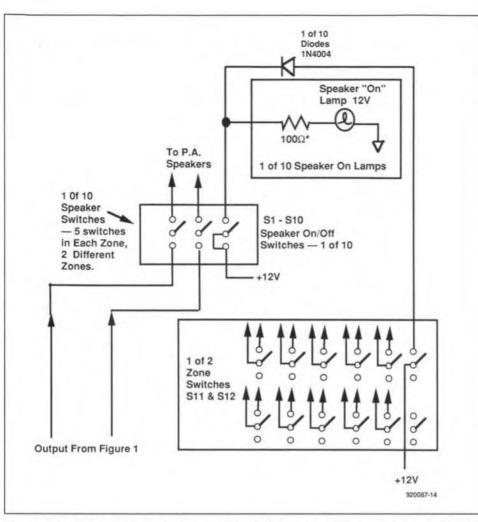

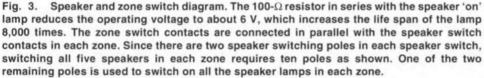

60 Replace your paging system with a high-powered intercom by Charles Kitchin (Analog Devices Inc., USA)

### GENERAL INTEREST

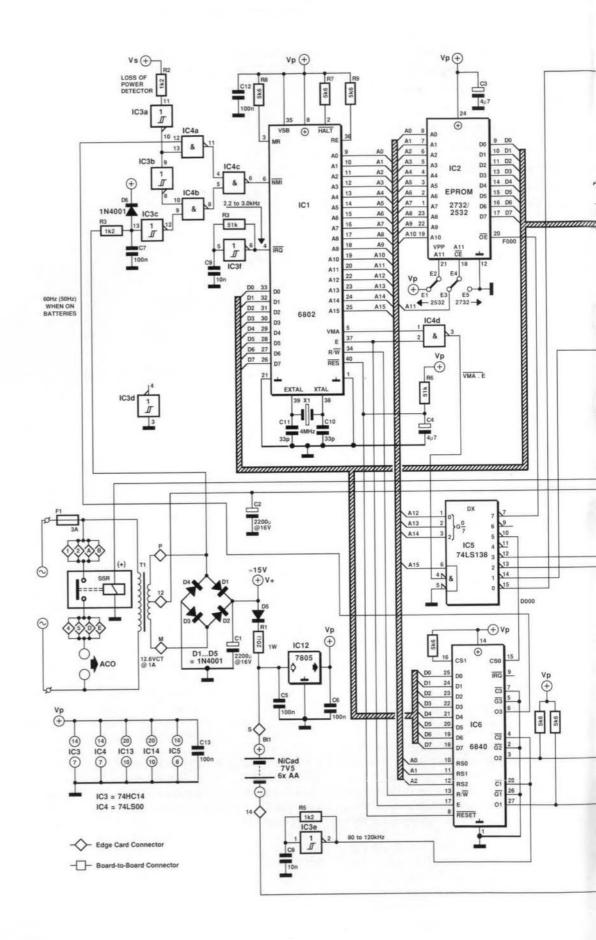

41 PROJECT: Kerber Klock IV by R.J. 'Bob' Kerber

45 Analogue opamp integrator circuits by Joseph J. Carr

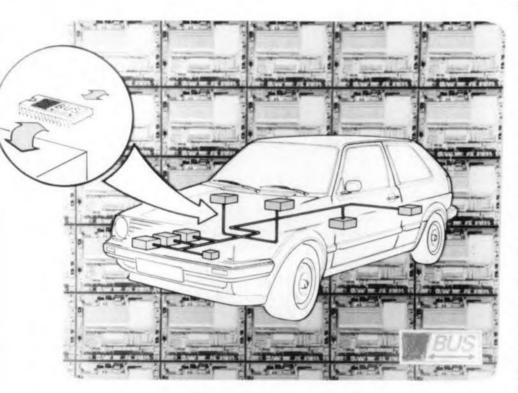

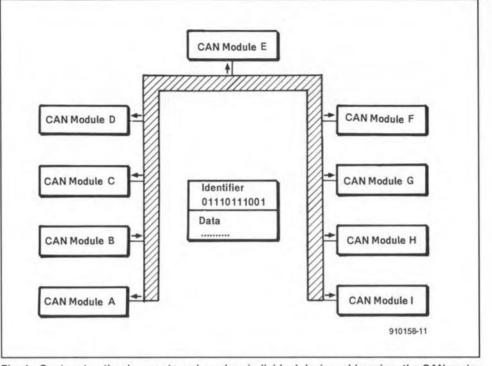

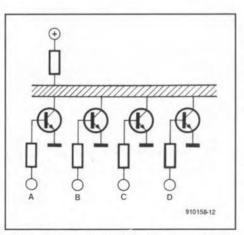

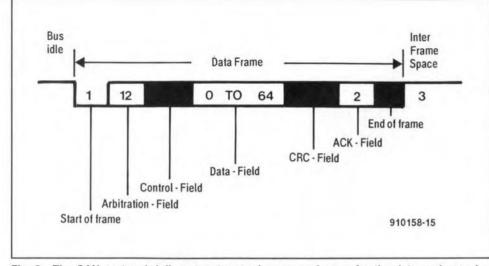

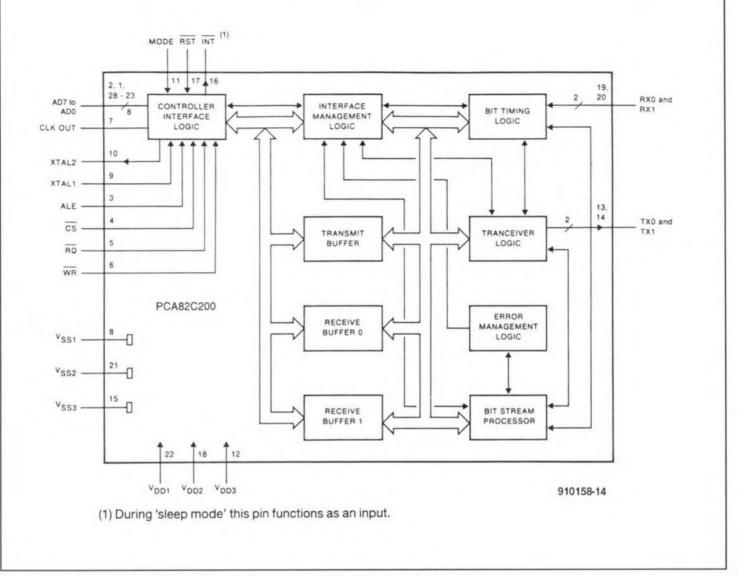

56 CAN – Controller Area Network by Achim Raab

## **RADIO, TELEVISION & COMMUNICATIONS**

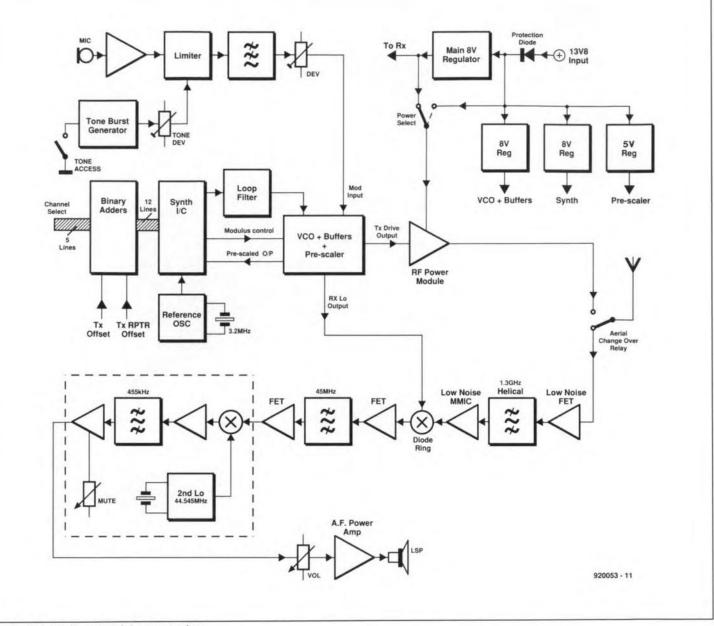

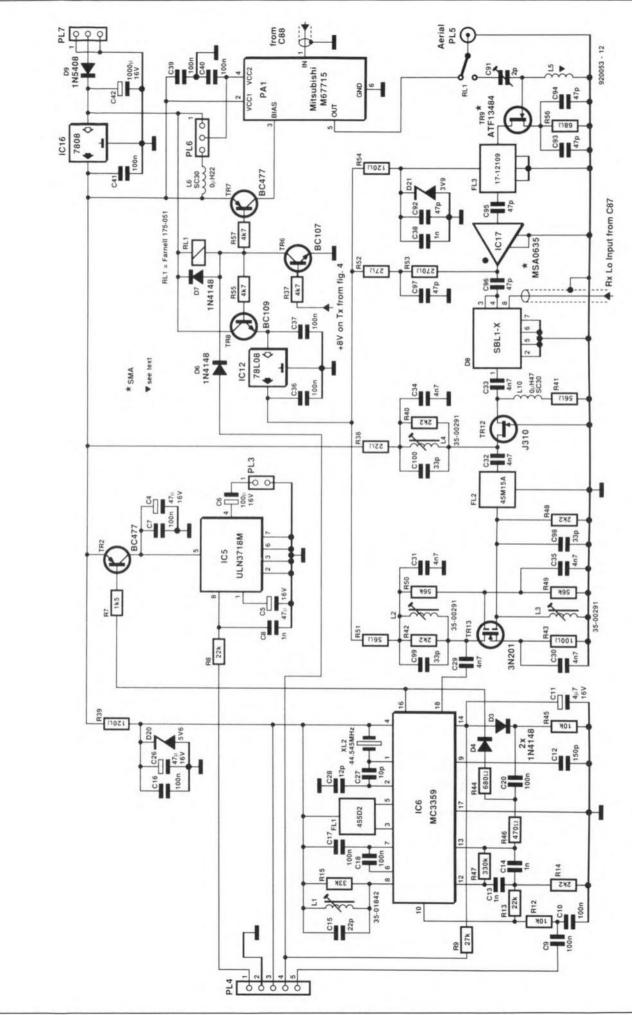

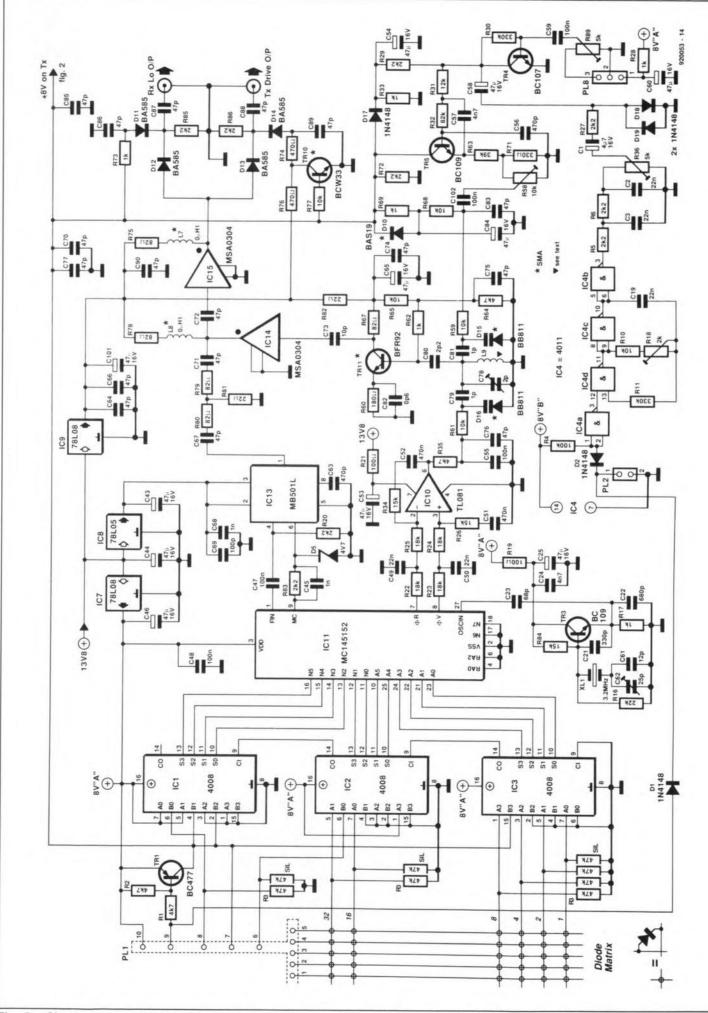

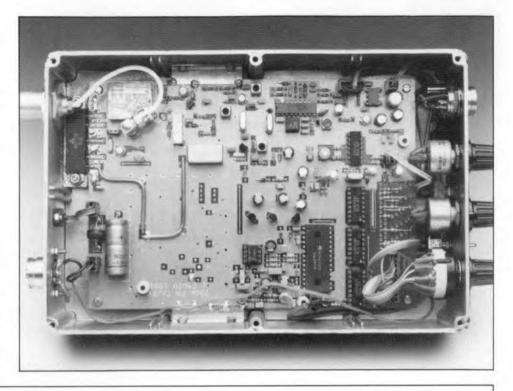

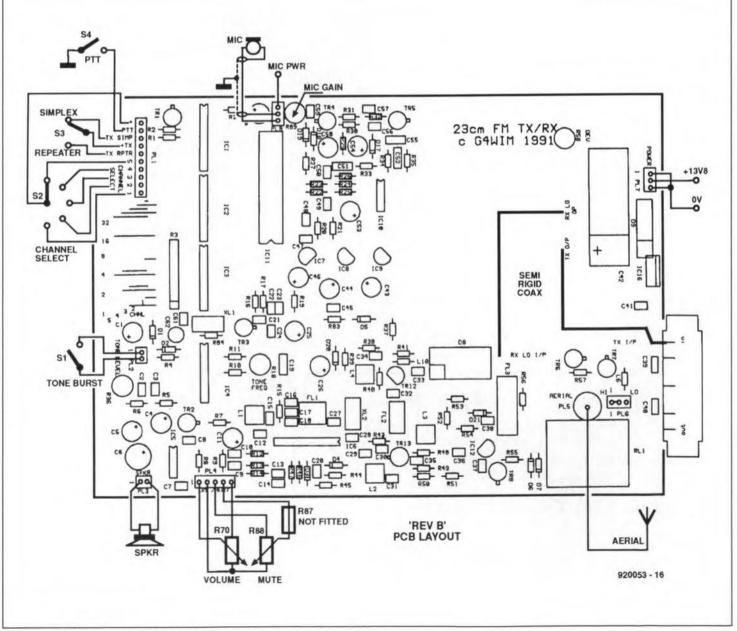

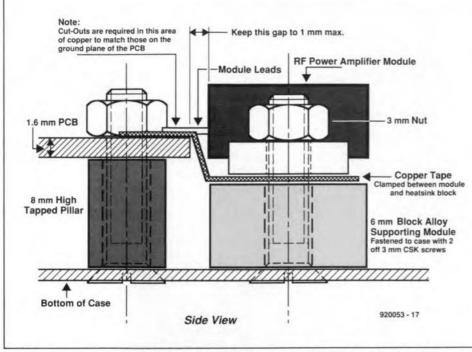

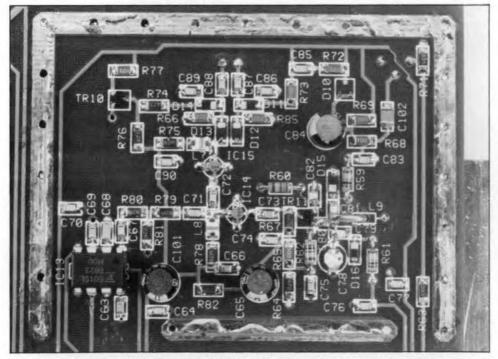

33 PROJECT: 23 cm FM transceiver by T. Forrester, G4WIM

48 PROJECT: Audio-video processor – Part 4 (final) an ELV design

65 PROJECT: An antenna evaluation and spare HF transmitter by Richard Q. Marris, G2BZQ

## MISCELLANEOUS INFORMATION

Electronics scene 11–12; Events 13; Readers' corner 69; Letters 69; Switchboard 71; Readers' services 74; Terms of Business 76; Index of advertisers 82

September 1992

Volume 18

Number 203

Audio frequency DAC - p. 21

23 cm FM transceiver - p. 33

Kerber Klock IV - p. 41

Current-sense MOSFETs - p. 53

# **EPROM EMULATOR II**

This is a revamped version of an EPROM emulator we published about three years ago. This time we propose to build the circuit with standard size components rather than SMA (surface mount assembly) components, which some of you have found difficult to obtain as well as handle. The present version of the emulator has a RAM of 64 KByte, and is capable of emulating 2764s up to and including 27512s. Also, by parallel connection of Centronics cables, extensions to bus widths of 16 bits or 32 bits are easier than before.

## Design by B.C. Zschocke and N. Breidohr

A EPROM emulator replaces the EPROM in a computer system (for which a program is to be developed) by a RAM that behaves like an EPROM. The advantages are well-known: the contents of the RAM can be overwritten as many times as you like, and the data transfer from the PC (running an assembler) to the target system is much faster. Errors in the object program are thus easily and quickly corrected, because it is no longer necessary to remove the EPROM, erase it, and reprogram it.

### MAIN SPECIFICATIONS

- Emulates EPROMs 2764 through 27512

- Connected to Centronics port

- Auto-reset function

- 8-, 16- or 32-bit configuration

No driver software required; use is made of existing system utilities (MS-DOS, Windows, ST and Amiga)

The data transfer from the PC to the emulator described here does not require special file formats like Intel-Hex, Tektronics or Motorola. Instead, standard system utilities can be used to output the previously prepared binary file via the Centronics port.

## Application range

The present emulator replaces the byte-organized EPROMs with a capacity of 8 KBytes (2764) to 64 KBytes (27512). The now obsolete 2-KByte and 4-KByte EPROMs Types 2716 and 2732 may also be emulated with the aid of a specially prepared adaptor board. Up to four emulators may be connected in parallel to 'attack' systems with a bus width of 32 bits. The EPROM data may be furnished by any computer system with a Centronics port. The STROBE pulses supplied by the computer have four functions: (1) they indicate that the data is stable and valid; (2) they enable the emulator; (3) they clock three-state counters IC7, IC8 and IC9; and (4) they select a particular emulator in 16-bit or 32-bit systems.

The counter outputs address two RAM ICs with a capacity of 32 Kbyte each. The data applied to the input of the emulator is 'acknowledged', and copied directly into the RAM. The selection of the RAMs is accomplished via A15 of counter IC9, and one half of IC12. After the last byte has been stored in the RAM, the counter is switched to high-impedance output mode ('threestate'). The individual RAM addresses are then available for selection through the address buffer, and can be read via the data output buffer. The addressing of the RAM at this stage is accomplished by the host system, i.e., the computer system or (more generally) application circuit whose EPROM is emulated.

## **Circuit description**

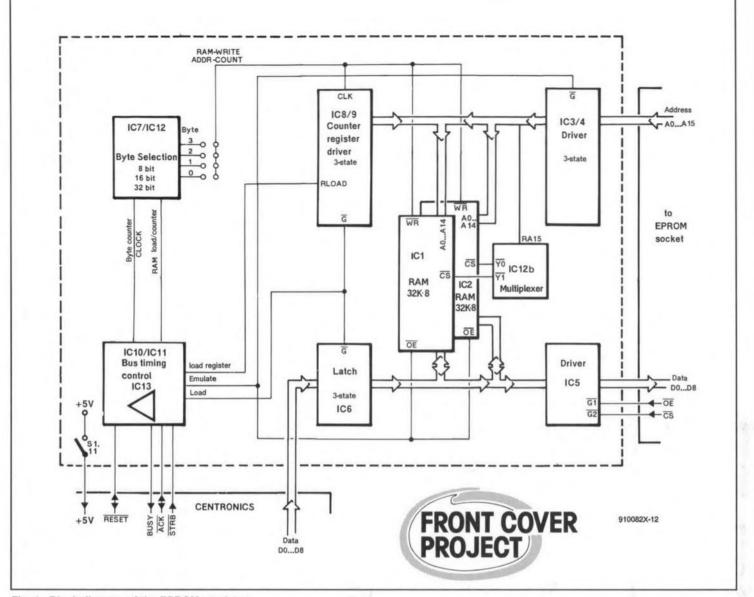

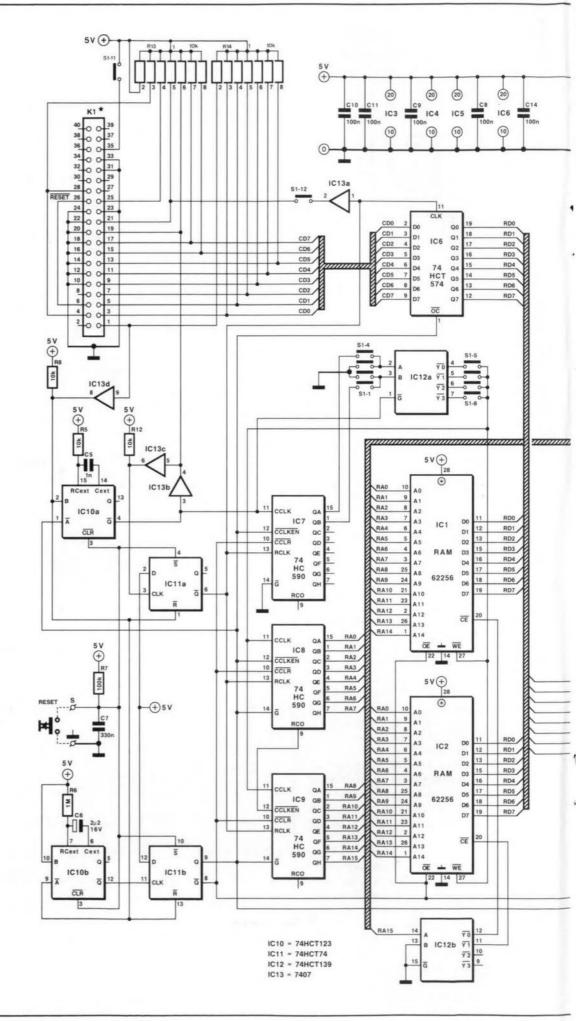

Essentially, the circuit consists of three blocks:

(1) A control section around IC10 and IC11, which serves to ensure the proper bus tim-

Fig. 1. Block diagram of the EPROM emulator.

ing on the Centronics interface, and generate a number of internal signals. This section also supplies the RESET signal for the application circuit (Auto-RESET). All signals are taken to the 'outside world' via open-collector buffers/drivers contained in IC13. One driver serves to generate the strobe signal.

(2) A byte selection circuit (IC7 and one half of IC12), which arranges the distribution of the received 8-bit data between parallel emulators in 16-bit and 32-bit applications. This circuit is required only if a 16-bit or 32-bit extension is envisaged.

(3) A RAM address and load address generator consisting of a counter (IC8 and IC9) that supplies the RAM addresses during loading, a latch (IC6) for intermediate storage of Centronics databytes, and drivers (IC3, IC4 and IC5) that interface to the EPROM socket in the application circuit. Depending on the mode of operation of the circuit (loading or emulating), either the counter/latch combination or the EPROM socket interface are in control of the EPROM addresses and data.

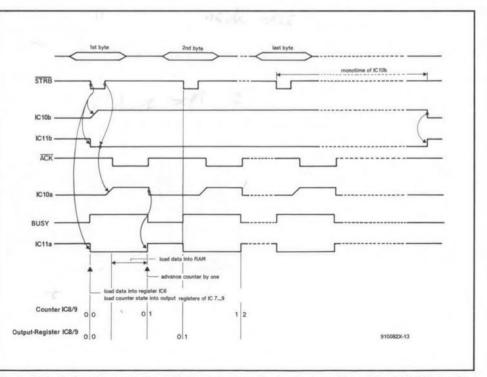

Fig. 2. This timing diagram should help you grasp the basic operation of the EPROM emulator. Note that both the positive and the negative edge of the STROBE signal are used.

Fig. 3. Circuit diagram of the EPROM emulator.

Since 64-K×8-bit RAMs are not easily obtained at reasonable prices, the present emulator is based on two 32-K×8-bit RAMs. These offer a total storage capacity of 64 KByte, and allow the emulator to mimic EPROMs up to and including the 27512. When smaller EPROMs are used, address lines A15 (27256), A15/A14 (27128) or A15/A14/A13 (2764) must be tied to ground via the appropriate jumpers (see Table 1).

## Operation in detail

The Centronics standard stipulates that data must be stable for a certain time before and after the STROBE pulse. This ensures freedom of using either the leading or the trailing edge of the strobe signal to capture data from the printer's Centronics input. In the emulator, both edges are used.

At power-up, R7 and C7 provide a defined state. Bistables IC11a and IC11b are set, while bistables IC10a and IC10b are reset. IC11b clears all counters, and switches the circuit to the emulate mode. With reference to the timing diagram of the 8-bit version (Fig. 2), the negative edge of the STROBE signal triggers IC10b, and resets IC11a and IC11b. Next, IC11b switches the circuit to load mode, and actuates the RESET line. IC11a actuates the Centronics BUSY line, and the positive edge at its output causes the counter state to be transferred to the counter register, and the Centronics databyte to be transferred to the latch. Data and address are allowed to stabilize at the respective RAM inputs while the STROBE pulse lasts. The positive edge of the STROBE pulse triggers IC10a, and actuates the RAM WRITE signal and the Centronics ACKNLG (acknowledge) signal during the monotime of IC10a. The signal edge that marks the monotime sets IC11a, and so clears the BUSY signal. At the same time, the counter is advanced one state. The first byte has been stored in RAM, and the circuit is ready to receive the next byte. A byte received within the monotime of IC10b causes this monostable to be triggered again. Otherwise, the above cycle starts again on detection of the negative edge of the STROBE pulse. If no databyte is received during the monotime of IC10b, the circuit switches to emulate mode, clears the RESET signal, switches the counters to three-state, and resets them. At this point, the RAM addressing is taken over by the application circuit.

To prepare the circuit for use in 16-bit or 32-bit applications, IC7 and one half of IC12 divide the internal RAM WRITE and counter output signals. Depending on the jumper setting, either the each first, second, third or fourth byte is copied into the latch, while the counters receive an appropriately reduced number of clock pulses. The RAMs are switched via their CS (chip select) lines, with the aid of address line A15 and the other half of IC12.

At first glance, the outputs of IC10b and IC11b behave identically. Why, then, are

EPROM EMULATOR II

| -    |                       |              |

|------|-----------------------|--------------|

| (    | COMPONEN              | TS LIST      |

|      |                       |              |

| Re   | sistors:              |              |

| 6    | 10kΩ                  | R1;R2;R4;R5; |

|      |                       | R8;R12       |

| 1    | 470Ω                  | R3           |

| 1    | 1MΩ                   | R6           |

| 4    | 100kΩ                 | R7;R9;R10;   |

|      | -                     | R11          |

| 2    | 7-way 10kΩ SIL        | R13;R14      |

|      | pacitors:             |              |

| Pite | ch 0.2 inch (5 mm):   |              |

| 1    | 470µF 16V radial      | C1           |

| 2    | 330nF                 | C2;C7        |

| 11   |                       | C3;C8-C18    |

| 1    |                       | C5           |

|      | ch 0.1 inch (2.5 mm): | ~ .          |

| 1    | 100µF 16V radial      | C4           |

| 1    | 2µF2 16V radial       | C6           |

| Se   | miconductors:         |              |

| 1    | LED, green, 3mm       | D1           |

| 2    | 62256 (<100ns)        | IC1;IC2      |

| 3    | 74HCT541              | IC3;IC4;IC5  |

| 1    | 74HCT574              | IC6          |

| 3    | 74HC590               | IC7;IC8;IC9  |

| 1    | 74HCT123              | IC10         |

| 1    | 74HCT74               | IC11         |

| 1    | 74HCT139              | IC12         |

| 1    | 7407 (74LS07)         | IC13         |

| 1    | 7805                  | IC14         |

| Mis  | scellaneous:          |              |

| 1    | 12-way DIP switch b   | olock,       |

|      | or 24-way pin heade   | er block     |

|      | with jumpers          | S1           |

| 1    | 40-way box header     | K1           |

| 1    | 34-way box header     | K2           |

| 1    | 40-way IDC socket     |              |

| 1    | 34-way IDC socket     |              |

| 1    | IDC Centronics sock   |              |

| 1    | TO-220 style heatsin  |              |

| 1    | Printed circuit board | 910082       |

1 ABS enclosure; approx. size 160×80×32mm IC sockets 28-way DIL adaptor (see Fig. 5) Approx. 50cm 36-way flatcable

both used? The timing diagram shows an unexpected, rather unwelcome, quirk of the monostable, IC10b. At the (relatively long) monotime, the time between the triggering instant and the output actuation instant is not short enough. This caused problems in a number of prototypes. The trigger signal supplied by IC10b actuates IC11b instantly, while IC11b is de-actuated again by the negative edge of IC10b. Capacitor C6 may also cause trouble if it can not be discharged quickly enough by IC10. Increasing its value must, therefore, be done with care.

LED D1 lights when the computer feeds data into the emulator. The (active low) RESET signal is taken to the application circuit via connector K2. On completion of the load activity, the emulator releases the

| S1:                      | 1                | 2     | 3       | 4     | 5      | 6      | 7       | 8       | 9   | 10 | 11     | 12 |

|--------------------------|------------------|-------|---------|-------|--------|--------|---------|---------|-----|----|--------|----|

| 8-bit                    |                  | on    | on      |       |        |        |         |         |     |    |        |    |

| 16-bit                   |                  | on    |         | on    |        |        |         |         |     |    |        |    |

| 32-bit                   | on               |       |         | on    |        |        |         |         |     |    |        |    |

| Byte-#                   |                  |       |         |       | 0      | 1      | 2       | 3       |     |    |        |    |

| Power exte               | ernal            |       |         |       |        |        |         |         | on  |    |        |    |

| Power from EPROM socket  |                  |       |         |       |        |        |         |         | -   | on |        |    |

| +5V on Ce                | entronics        | input |         |       |        |        |         |         |     |    | on     |    |

| BUSY on Centronics input |                  |       |         |       |        |        |         |         |     |    |        | on |

|                          |                  |       | (Switch | = OFF | when   | not ot | herwise | e notec | 1)  |    |        |    |

| EPROM ty                 | pe               |       |         | Ju    | mper A | 13     | Ju      | mper /  | A14 | Ju | mper A | 15 |

| 2764 (8 KByte)           |                  |       | off     |       |        |        | off     |         | off |    |        |    |

| 27128 (16                | 27128 (16 KByte) |       |         | on    |        |        | off     |         | 1   |    | off    |    |

| 27256 (32                | KByte)           |       |         | on    |        |        |         | on      |     |    | off    |    |

| 27512 (64 KByte)         |                  |       |         |       | on     |        | on      |         | on  |    |        |    |

Table 1. Jumper settings for emulator bus width and EPROM type.

RESET line, and so re-starts the application circuit, which subsequently runs its new software contained in the emulator RAM.

The emulator is powered either by the application circuit (via S1-10), or by the onboard stabilizer (via S1-9), whose input is connected to a small mains adaptor with d.c. output. Whether or not an external power supply is required is, of course, dependent on the capacity of the target system's power supply. A power supply conflict may arise when the emulator is powered by the application circuit, and this is switched off, or powered down during reset, while the 'other side' of the emulator is connected to the PC (which is still on) via a Centronics cable. If this happens, the emulator is powered via the protection diodes in the Centronics interface of the PC. This results in a supply voltage of about 3 V, which is sufficient for the RAMs to retain their data, but not for the TTL circuits to operate properly. If, in this condition, the application circuit is switched on, the emulator may go into an undefined state, which may be ended by pressing a button connected between point 'S' and ground. A better solution, however, is to power the emulator

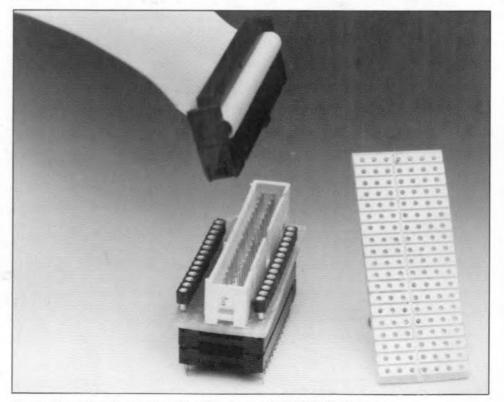

Fig. 5. Illustrating the construction of the home-made EPROM adaptor.

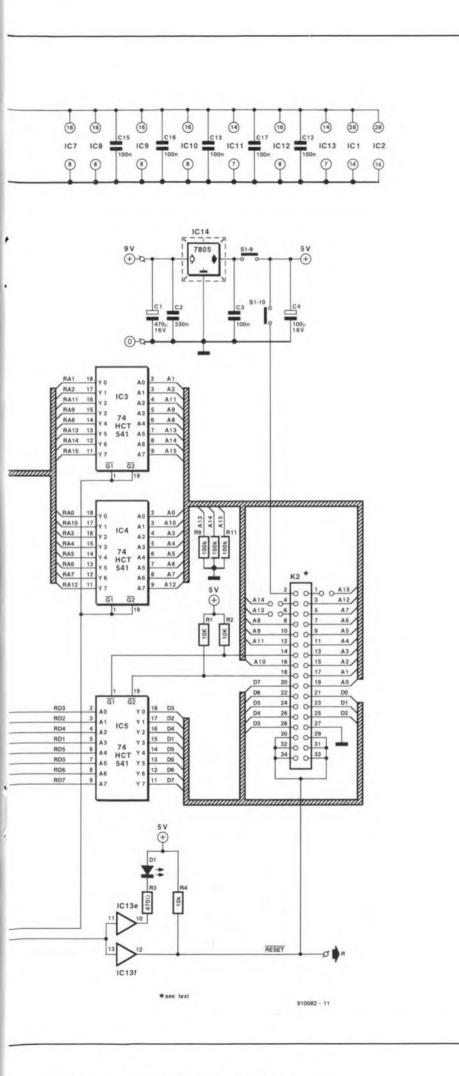

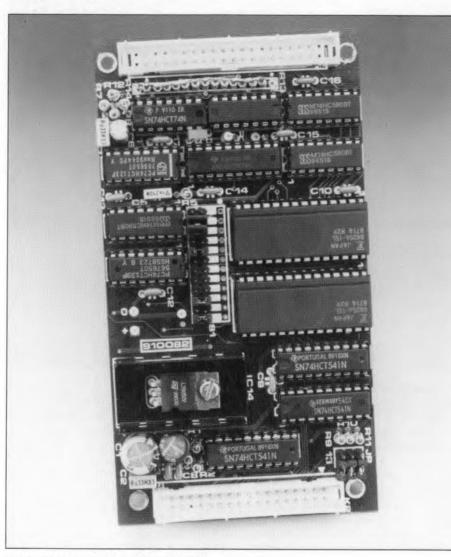

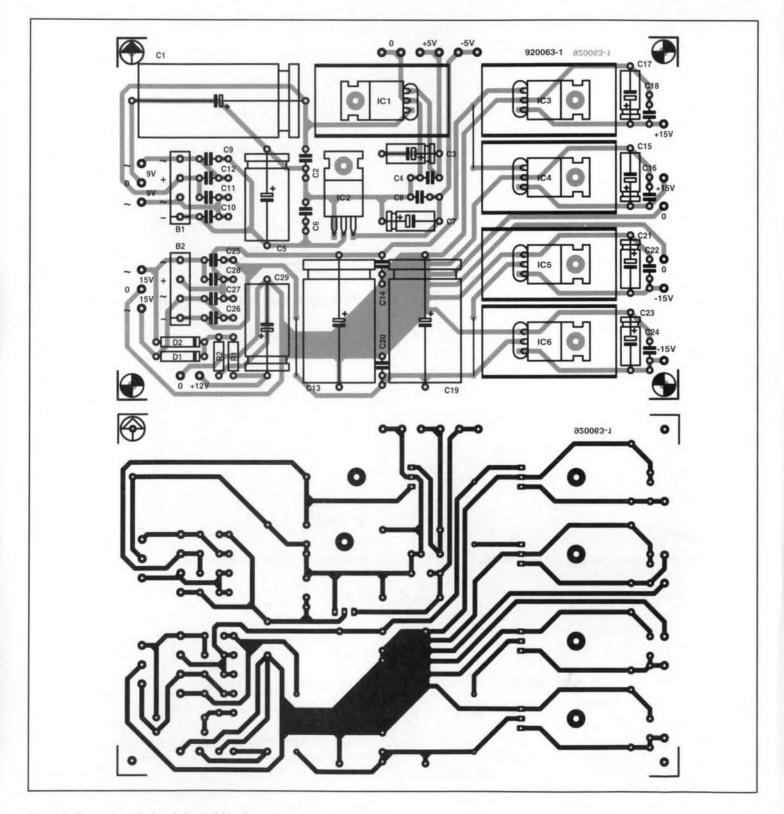

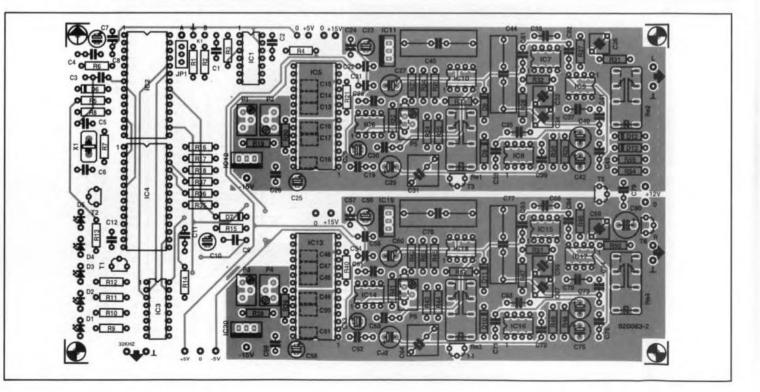

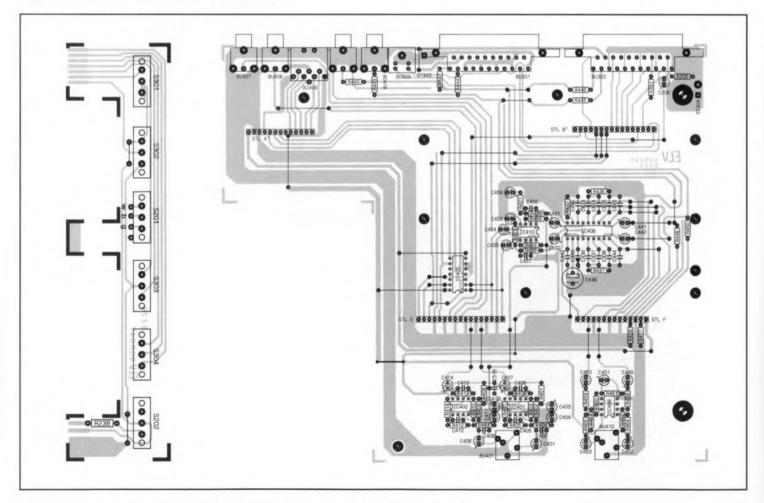

#### Fig. 6. Completed printed circuit board.

from an external source via IC14. The previously described power supply conflict may also damage the emulator, because the current sent into the application circuit via the EPROM socket may become so high that the driver ICs are destroyed.

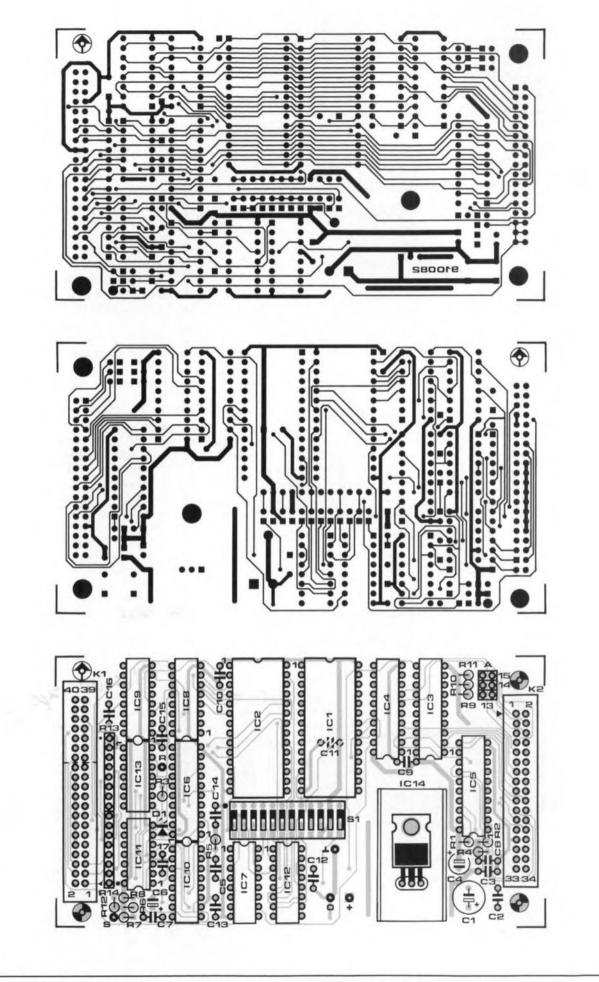

## Practical hardware

The printed circuit board designed for the EPROM emulator is a high-density doublesided, through-plated type, which is best purchased ready-made through our Readers' Services. Space is pretty tight on

the board, so keep an eye on the pitch of the capacitors. Capacitor C11 is fitted at the solder side of the board, underneath IC1.

Pin header K1 is suitable for two types of connection: its pinning is compatible with a 25-way sub-D connector (allowing ready use of IDC-style connectors), as well as with a 36-way Centronics socket. When the latter is used, make sure to remove pins 4 and 6, or cut the relevant tracks. When a 25-way sub-D connector is used, it is, unfortunately, not possible to create a 'loop-through' connection for the supply voltage. To reduce cost, a 40-way IDC socket was used on the proto-

| DOWN      | LOADING TO THE EPR                 | OW EMULATOR              |

|-----------|------------------------------------|--------------------------|

| PC/MS-DOS | COPY <filename> LPT1:/B</filename> | (/B for binary output    |

| Amiga     | COPY <filename> PAR:</filename>    | (PAR:, not PRT:)         |

| TOS       | On the ST it is sufficient to do   | uble-click on the filena |

On the ST it is sufficient to double-click on the filename shown on the desktop, and then output to 'printer'. It should be noted, however, that the TOS appends a CR/LF sequence to each file. This means that the last two bytes of a 32-Kbyte file can not be used. However a simple printer manager that does not output the CR/LF sequence should not be too difficult to write in Pascal, C or BASIC.

type - a 26-way type (for connection to a sub-D plug) is, of course, also possible.

The 16-bit and 32-bit versions of the EPROM emulator require two or four complete circuits, respectively, which are driven by a common line, for instance, via four IDC-style Centronics plugs. The jumper settings on each board may be found in Table 1. The emulators are mutually synchronized via the ACK line on the Centronics interface. The BUSY line may be connected on one board only (S1-12). In case the emulators are to be powered by a single, external, supply, this is connected to one board only, from where the supply voltage is distributed via pin S1-11 on each board. On the board from which the supply voltage is distributed, S1-9 must be closed. On all other boards, S1-9 is open. S1-10 must be closed on all boards.

#### Software

As already mentioned, special software is not strictly required. The emulator RAM can be loaded with the aid of any system utility capable of outputting binary files in binary form, via the Centronics port. This means that the EPROM emulator can be used with any computer sporting a Centronics-compatible printer port.

Users of MS-DOS PCs may want to obtain version 2.0 of EPROMSIM, a program which is available on disk through our Readers Services as item ESS129. EPROMSIM supports EPROMs up to 64 KByte, and is capable of handling the following 'intelligent' file formats:

- Intel Intellec-8;

- Tektronix hexadecimal:

- Motorola.

#### Construction

When building the circuit, remember to remove pins 4 and 6 of the Centronics socket, if used. To ensure ready access, the DIP switch array is best mounted on IC sockets. Alternatively, you may want to fit the switches at the solder side of the board, and cut a clearance in the back panel of the enclosure. The LED wires may be extended to enable the LED to be fitted in a hole in the cover panel. Further constructional points that deserve your attention are the mounting of the Centronics input socket, and the strain relief on the flatcable to the EPROM adaptor.

The EPROM adaptor is home-made. As shown in Fig. 5, it consists of a piece of stripboard, two lengths of IC pin strip, a box header and two 28-way IC sockets. The flatcable from the EPROM emulator is fitted with a 28-way IDC socket. You may want to make one adaptor for each EPROM type, and wire jumpers A13, A14 and A15 appropriately, direct on the socket. Wires 29 to 34 of the flatcable are connected to the RESET generator on the emulator board, and may also be taken to the adaptor socket to create a RESET connection for the application circuit.

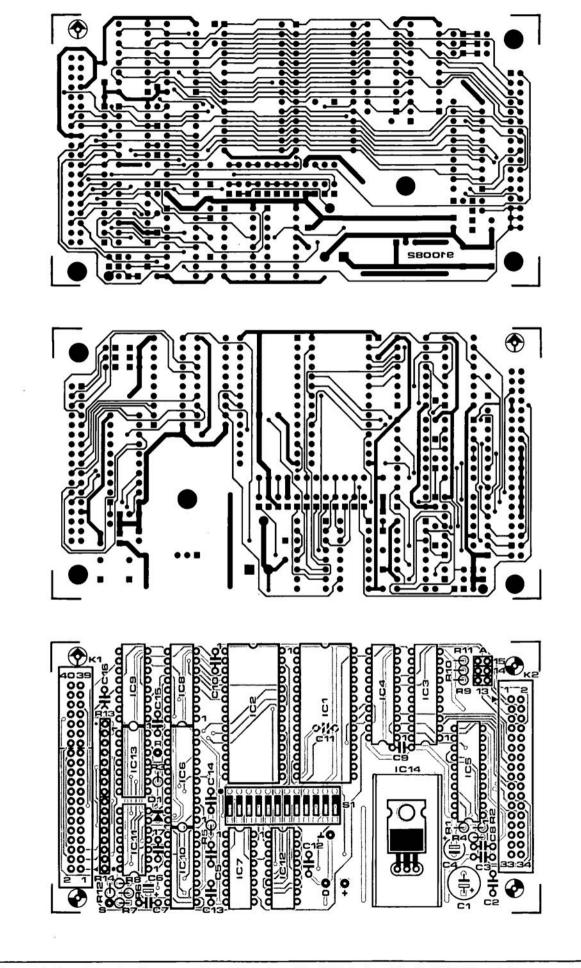

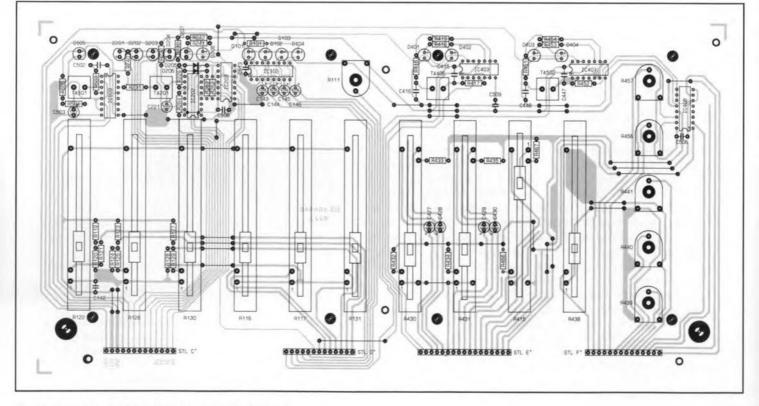

Fig. 4. Track layouts (mirror images) and component mounting plan of the PCB designed for the EPROM emulator.

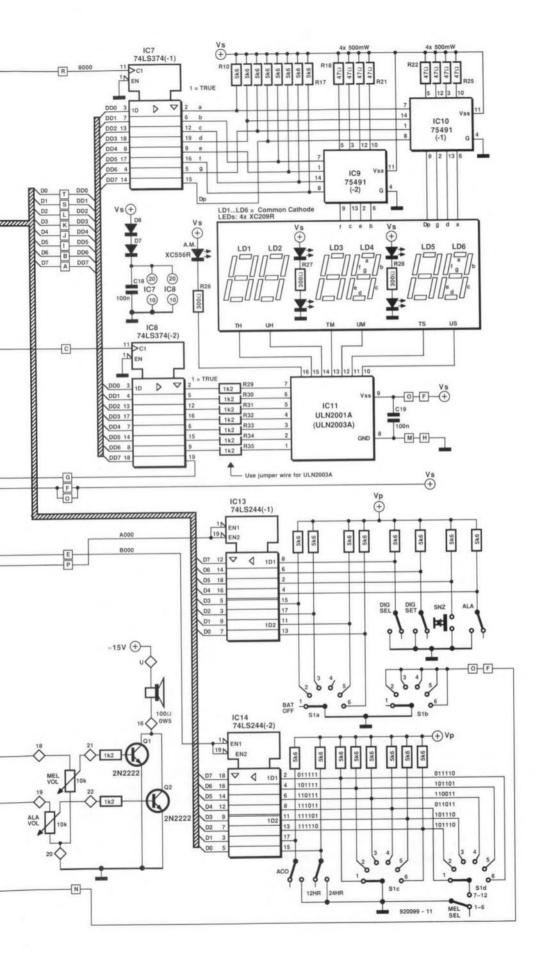

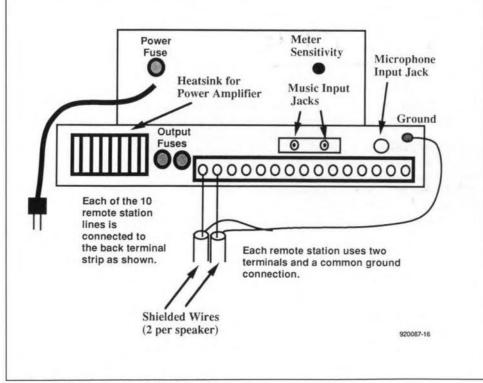

## A.F. DIGITAL-TO-ANALOGUE CONVERTER PART 2

**Design by T. Giesberts**

**B**EFORE the construction is discussed, it have a look at the test results from our two prototypes. Note that both of them were K versions using Type 5534A opamps in the output filter and buffer section. The measurements were carried out with an Audio Precision System One analyser (with FFT option), while the signals were obtained from a number of special measurement-CDs (CD-1 from CBS; Test Sample 3 and Audio Signals Disc 1 from Philips; and Digital Test from Pierre Verany). For clarity's sake, all figures illustrating the measurement results pertain to one channel (the results of the other channel were, for all practical purposes, identical).

21

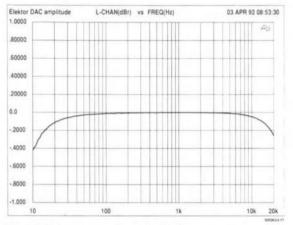

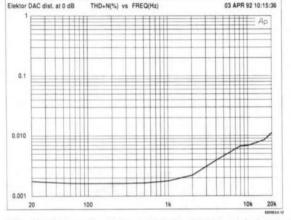

The -0.1 dB figure at 20 Hz (see Fig. 8) results from the effect of the servo control,

Fig. 8. Frequency characteristic.

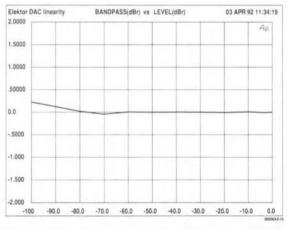

Fig. 10. Linearity deviation for signals to -100 dB.

Fig. 9. THD+noise from 20 Hz to 20 kHz at full drive.

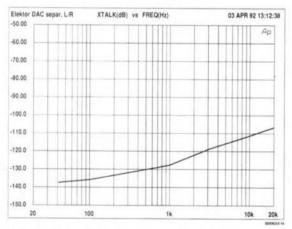

Fig. 11. Cross-talk over the audio range.

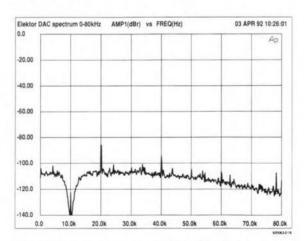

Fig. 13. Spectrum analysis of residual signals up to 80 kHz.

which acts as a high-pass filter. The 0.25 dB fall-off at 20 kHz is ensured by the analogue output filter. It would have been possible to straighten the curve here, but that would have meant a higher cut-off frequency and, consequently, worse suppression of the sampling frequency and worse phase behaviour in the pass-band (since a Cauer or Chebishev filter would then have to be used). The characteristic in Fig. 8 is virtually a Butterworth curve with a near-constant time delay in the pass-band up to 20 kHz.

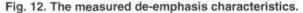

The harmonic distortion (THD+noise) characteristic is shown in Fig. 9. At frequencies below 1 kHz, the distortion is identical to that specified by Burr-Brown for their K versions: –96 dB. Above 1 kHz, the distortion increases very slightly, owing to the effect of the number of samples per period and because frequencies above 20 kHz are suppressed (a sharp cut-off filter as, for instance, recommended by Philips for measurements above 20 kHz was not used).

The linearity deviation—see Fig. 10—was measured down to –100 dB (from –70 dB to –100 dB with dithering).

The cross-talk characteristic in Fig. 11 shows that the channel separation is excellent: -105 dB

at 20 kHz and -135 dB at 100 Hz indicate that the curve is virtually the same as the noise characteristic of the converter.

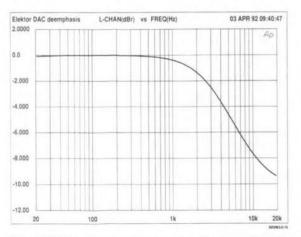

The de-emphasis characteristic in Fig. 12 does not show its accuracy with respect to the theoretical curve, but the deviation between the two was measured at <0.15 dB over the 20 Hz to 20 kHz frequency range.

Figure 13 shows the spectrum analysis over the frequency range up to 80 kHz. The 10 kHz test signal was effectively suppressed by a band filter, so that the residual products are clearly indicated. Note the 2<sup>nd</sup> and 4<sup>th</sup> harmonics of the test signal and the mixing prod-

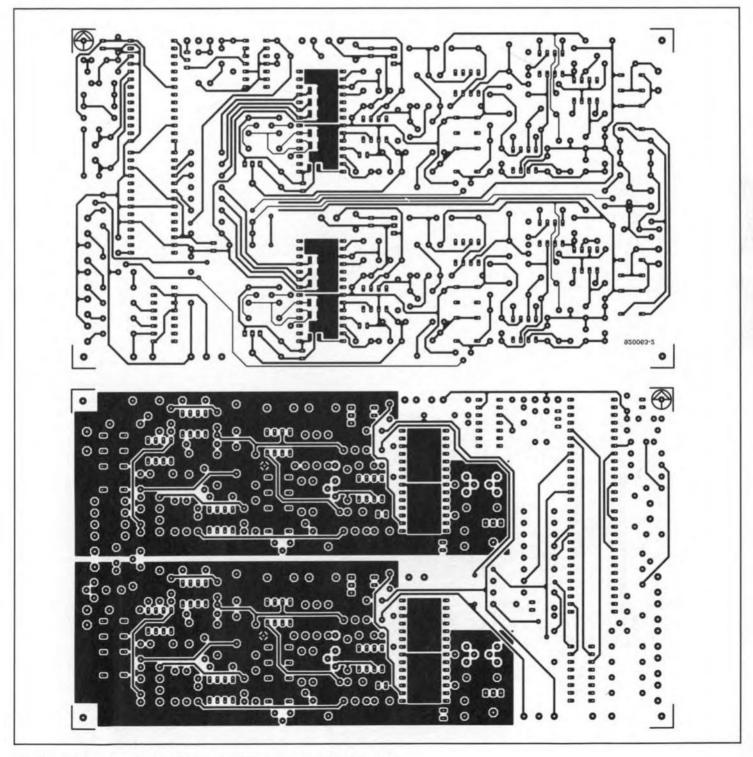

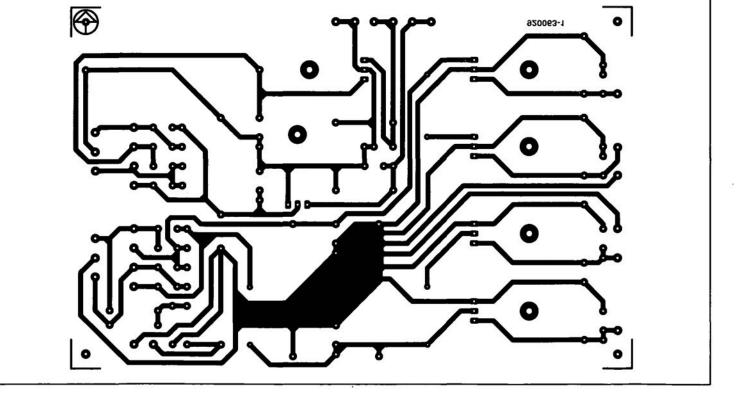

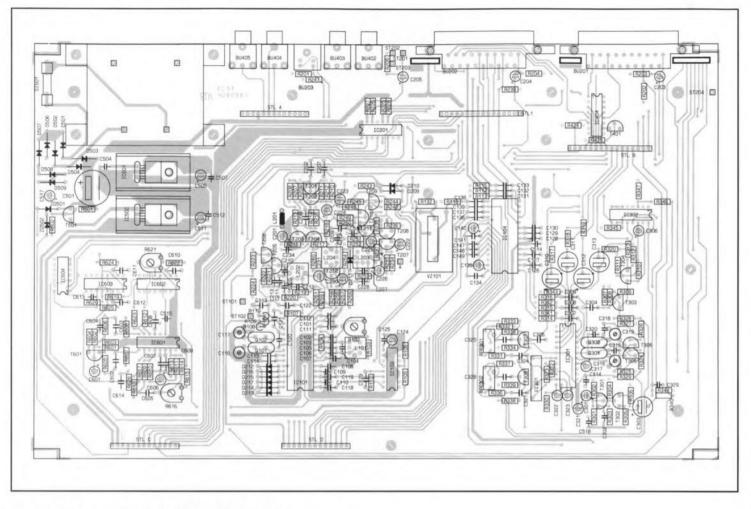

Fig. 14. The printed-circuit board for the power supply section.

uct (78.2 kHz) of the test signal and twice the CD sampling frequency (2×44.1 kHz), since the analogue filter does not have an infinite roll-off.

## Construction

It is advisable to read carefully through this section before buying any components, because the design contains some fairly expensive ICs. As far as the YM3623B and DF1700P are concerned, there is not much choice, because these devices are made in only one version. The PCM63P, however, is available in three grades: that without suffix is the cheapest, the PCM63p-J is next and the PCM63P-K is the dearest. Depending on the market area, the difference between the first and the -K version can be £10–£15. The difference between these versions lies in the accuracy (that is, without calibration). At 1 kHz and full drive, the -K version has a THD+noise figure of –96 dB; the -J version, –92 dB; and the cheapest version, –88 dB.

Type OP27 opamps are specified for the IC<sub>10</sub> and IC<sub>18</sub> positions because of their offset voltage and low noise. Faster opamps are not recommended in the servo control.

The AD844, used in the IC<sub>6</sub> and IC<sub>14</sub> positions, has properties that make it particularly suitable for use in D-A converters: good bandwidth (60 MHz at unity gain); high slew rate ( $2000 V/\mu$ s) and short settling time (100 ns to reach an accuracy of 0.1%). Moreover, it can

drive low-impedance loads (50 mA into 50  $\Omega$ ) and is reasonably priced.

23

There is a good choice as far as the remaining opamps are concerned. According to our measurements, the most suitable are the NE5534A, the LT1115, the TLE2027 and the OPA627. Although the OPA627 is much faster than the 'ordinary' 5534 and, moreover, has FET inputs, we found, in our measurements, that there is very little difference between the two. However, in listening tests, a number of people preferred the OPA627 in the output section (the opamp in the filter has less influence on the sound quality). Bear in mind that we are talking here of very small differences that become audible only on first class audio installations.

Fig. 15. Printed-circuit mother board, shown here at 80% of true size.

## PARTS LIST

#### Power supply board

Resistors: R1 = 68  $\Omega$

$R2 = 1.5 \text{ k}\Omega$

## Capacitors:

C1 = 2200  $\mu$ F, 25 V C2, C4, C6, C8, C14, C16, C18, C20, C22, C24 = 100 nF C3, C7 = 10  $\mu$ F, 10 V C5 = 220  $\mu$ F, 25 V C9–C12, C25–C28 = 47 nF, ceramic C13, C19 = 2200  $\mu$ F, 35 V C15, C17, C21, C23 = 10  $\mu$ F, 25 V

#### Semiconductors:

D1, D2 = 1N4001 B1, B2 = B80C1500 IC1 = 7805 IC2 = 7905 IC3, IC4 = 7815 IC5, IC6 = 7915

#### Miscellaneous:

Mains transformer, 2×9 V, 830 mA Mains transformer, 2×15 V, 500 mA Heat sinks for IC1, IC3–IC6 PCB Type 920063-1 (see Readers' services)

#### Mother board

Resistors:  $R1 = 75 \Omega, 1\%$   $R2 = 100 \Omega$   $R3 = 10 k\Omega$   $R4 = 4.7 \Omega$   $R5 = 18 k\Omega$   $R6 = 270 \Omega$   $R7, R25, R44 = 1 M\Omega$   $R8, R14 = 2.2 \Omega$  $R9-R13 = 470 \Omega$

$R15 = 22 M\Omega$ R16, R17, R18, R35, R36, R37 = 47  $\Omega$ R19, R20, R38, R39 =  $330 \text{ k}\Omega$ R21, R40 = 1  $\Omega$ R22, R41 =  $1.5 \text{ k}\Omega$ , 1% R23, R42 =  $1.07 \text{ k}\Omega$ , 1% R24, R43 =  $475 \Omega$ , 1% R26, R45 =  $2.49 \text{ k}\Omega$ , 1% R27, R46 =  $931 \Omega$ , 1% R28, R29, R47, R48 = 2.43 kΩ, 1% R30. R49 =  $2.74 \text{ k}\Omega$ , 1% R31, R50 =  $49.9 \Omega$ , 1% R32, R33, R51, R52 =  $6.81 \text{ k}\Omega$ , 1% R34, R53 =  $4.99 \text{ k}\Omega$ , 1%  $R54 = 10 \Omega$  $R55 = 47 k\Omega$  $P1-P4 = 100 \text{ k}\Omega$  multi-turn preset, vertical mounting (e.g., Bourns Type 3296Y) P5, P6 = 47 k $\Omega$  multi-turn preset, vertical mounting (e.g., Bourns Type 3296Y) Capacitors: C1 = 10 nF, ceramic C2, C3, C19, C52, C79 = 100 nF C4 = 8.2 nFC5, C6 = 10 pFC7, C10, C20, C53 = 4.7 µF, 10 V, radial C8, C11, C28, C30, C38, C39, C41, C43, C61, C63, C71, C72, C74, C76, C81-C84 = 47 nF, ceramic C9 = 15 nF $C12 = 100 \, pF$ C13, C14, C15, C46, C47, C48 = 47 pF\*

C16, C17, C18, C49, C50, C51 = 100 nF\*

C21, C22, C56, C58 = 10 µF, 10 V, radial

C23, C25, C56, C58 = 10 µF, 10 V, radial

C27, C29, C40, C42, C62, C62, C73, C75 =

C24, C26, C57, C59 = 100 nF, ceramic

C31, C64 = 33 nF, polystyrene, 1%

C32, C34, C36, C65, C67, C69 = 1.5 nF,

C33, C35, C37, C66, C68, C70 = 22 pF,

47 µF, 25 V, radial

polystyrene, 1%

#### polystyrene (see text) C44, C45, C77, C78 = 2.2 μF, 160 V, MKP (= polypropylene) C80 = 220 μF, 6.3 V

#### Semiconductors:

D1-D5 = 3 mm LED, high efficiency D6, D8, D10, D12 = 1N4148 D7, D13 = BAT85 D9, D11 = zener, 3 V, 400 mW T1 = BC546BT2 - T5 = BS170T6 = BC517IC1 = 74HCU04IC2 = YM3623B (Yamaha) IC3 = 74HC239IC4 = DF1700P (Burr Brown) IC5, IC13 = PCM63P (Burr Brown) IC6, IC14 = AD844AN (Analog Devices) IC7, IC8, IC9, IC15, IC16, IC17 = NE5534A IC10, IC18 = OP27IC11. IC19 = 7805 IC12, IC20 = 7905

#### Miscellaneous:

JP1 = 3-way header with jump link

K1 = audio socket for PCB mounting (gold-plated contacts preferred)

2 audio sockets with gold-plated contacts) for analogue outputs

Re1-Re4 = 12 V miniature relay

X1 = crystal, 16 MHz

PCB Type 920063-2 (see Readers' services)

\* Surface mount type

ELEKTOR ELECTRONICS SEPTEMBER 1992

When choosing opamps, pay particular attention to the stability in the analogue section. If the chosen type is not stable at unity gain (in our tests, that was only true of the 5534), each IC *must* be provided with a compensating capacitor: in case of the 5534, a 22 pF polystyrene type between pins 5 and 8. There is provision for these on the PCB and they are shown in the circuit diagram (Fig. 5). Details of these capacitors, and where to place them, can be found in the data sheets of opamps not mentioned here.

Commence the construction with the power supply board—see Fig. 14. The only thin g that needs to be noted here is that all regulators, except IC<sub>2</sub>, must be fitted on a heat sink.

The mother board—see Fig. 15— requires rather more work. It has been designed to ensure good separation of the analogue sections of the two channels. The top of the board contains an earth plane for all analogue components: this plane (for each channel) is connected to analogue earth in only one place.

Remember that capacitors  $C_{33}$ ,  $C_{35}$ ,  $C_{37}$ ,  $C_{66}$ ,  $C_{68}$ , and  $C_{70}$  are only required if Type 5534 opamps are used.

In some case, surface-mount design (SMD) capacitors are specified, because these types can be soldered (as they should be) very close to the associated IC pins.

If a distortion meter is not available, omit  $P_1-P_4$ ,  $R_{20}$ ,  $R_{38}$  and  $R_{39}$ , because the MSBs of the converters then cannot be calibrated. Note that fitting these components and setting the potmeters to the centre of their travel may result in a worse performance than if the components had been omitted.

Presets  $P_5$  and  $P_6$  are optional and only required if it is felt that the output levels of the two channels should be absolutely equal. Even when these components are omitted, the output levels of the channels are within 0.25 dB of each other, although they may not be exactly, as preferred, 2.0 V r.m.s. The potmeters can, of course, set the level to exactly 2.0 V (if so, a 1 kHz, 0 dB, *digital* test signal must be used, *not* a digitized analogue signal: this is normally indicated on the test CD). Note that 23.7 k $\Omega$  resistors instead of the potmeters will keep the output level very close to 2.0 V.

The crystal should be insulated at its underside before it is mounted on the board.

Circuits  $IC_1$ – $IC_4$  may be fitted in an IC holder, but  $IC_5$  and  $IC_{13}$  must be soldered directly to the board. This is not only to prevent bad contacts, but also because it ensures that these devices are as close to the earth plane as possible. In our opinion, it is best to solder all directly to the board; whence our advice at the beginning of this section. If you must (for experimental purposes), only  $IC_7$ – $IC_9$  and  $IC_{15}$ – $IC_{17}$  should be fitted in IC sockets, but these should be of prime quality (with gold-plated contacts). Note, however, that even such sockets show rapidly deteriorating contacts when the ICs are replaced frequently.

Before connecting the power supply board to the mother board, connect it to the mains and check that all voltage levels are as specified. If they are, connect the two boards together via not too long wires. Place jump lead JP<sub>1</sub> as far as possible from connection A. Solder some audio sockets to the digital input (between connection B and earth) and the analogue outputs. The input can then be connected via a coaxial cable to the digital output of, say, a CD player and the outputs, via a stereo cable, to the line inputs of an amplifier (or pre-amplifier). When the mains is switched on, all should be well.

If you wish to use the converter in this form and feel that you will not need a digital selector, optical inputs and outputs, and a digital tape output (which will be described in our next issue), you can install it in a suitable enclosure now. Otherwise, wait and see the next and final instalment.

#### **Technical Data**

- Suitable for sampling frequencies of 32–48 kHz

- ×8 oversampling

- 20-bit D–A converters

- Integral de-emphasis circuit

- No capacitors in signal paths

- Servo control of d.c. setting in audio section

- Pseudo-passive GIC filter for suppressing sampling frequency

- · Separate power supplies for analogue and digital sections

| Dynamic range                                      | >100 dB                        |

|----------------------------------------------------|--------------------------------|

| Nominal input voltage,<br>(digital input)          | 500 mV into 75 $\Omega$        |

| Nominal output voltage                             | 2 V r.m.s.                     |

| Output impedance                                   | 50 Ω                           |

| Frequency range                                    | 20 Hz-20 kHz (+0 dB; -0.25 dB) |

| Signal-to-noise ratio                              | >115 dB                        |

| THD+noise (0 dB; 1 kHz)                            | <0.002%                        |

| Intermodulation distortion<br>(60 Hz; 7 kHz; 0 dB) | <0.003%                        |

| Linearity deviation<br>(signal levels to -100 dB)  | <1 dB                          |

| Channel equalization                               | Within 0.1 dB                  |

| Deemphasis deviation                               | <0.15 dB                       |

920063-2  $\odot$ 0 0 0 0 0 0 98 000 8 Ο . 0 .....  $\odot$ Ō Ο æ 0 0000 00000 0 00 Q. • 2.0 ۰. 0 8 0 6 0 0 0 0 0 0 0 0 0 0 0 0 0 0  $\odot$ 0000 good g 0000 0000  $\odot$ Ο 00 gu <u>o</u> °.°

## Digital Audio/visual system (Multi-purpose Z80 card)

#### May and June 1992

An extensive description of a modification to the memory backup circuit on the Multi-purpose Z80 card is available free of charge through our Technical Queries service.

## FM stereo signal generator

#### May 1993

Capacitors C17 and C19 should have a value of 33nF, not 3nF3 as indicated in the circuit diagram and the parts list of the multiplex generator.

## Workbench PSU

#### May 1993

The polarity of capacitor C15 is incorrectly indicated on the PCB component

## CORRECTIONS AND UPDATES

overlay (Fig. 5a), and should be reversed. The circuit diagram (Fig. 2) is correct.

Transformer TR2 is incorrectly specified in the circuit diagram (Fig. 2) and in the parts list. The correct rating of the secondary is  $2 \times 12V/5A$ . Also note that the secondary windings are connected in series to give 24 V.

## Audio DAC

#### September 1992

The polarity of capacitors C25 and C58 is incorrectly indicated on the component overlay of the D-A board (order code 920062-2), and should be reversed.

## U2400B NiCd battery charger

#### February 1993

The value of resistors R17 through R27 should be  $2.7k\Omega$ , not  $12.7k\Omega$  as stated in the parts list.

## **VHF/UHF** receiver

#### May 1993

In Fig. 4, the connections to ground of the AF amplifier outputs, pins 5 and 8, should be removed. The amplifier outputs are connected to the loudspeaker only. The relevant printed circuit board is all right.

# 8051/8032 ASSEMBLER COURSE

## PART 6: ANALOGUE SIGNAL PROCESSING AND STACK MANAGEMENT

The first subject in this month's instalment is processing analogue signals with the aid of our extension board. Next, we have a short discourse on stack management, which is quite important when it comes to dealing with subroutines. The two subjects form a basis for the next theme: interrupt processing, which is also introduced in this instalment. As usual, the programs discussed are contained on the course diskette, and can be tested straight away using the 80C32 single-board computer and its extension board (see part 3).

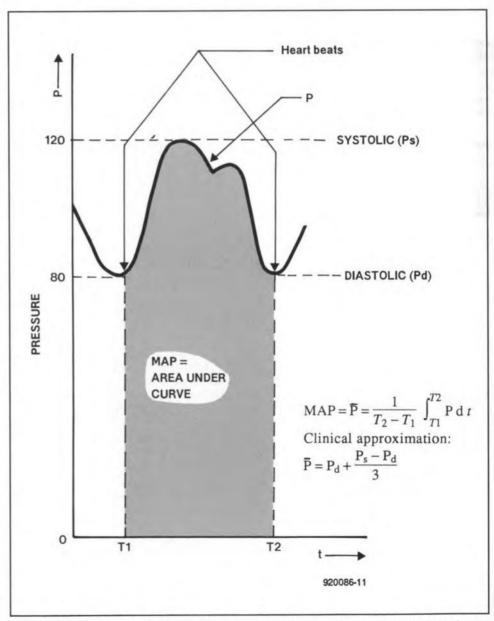

## **D-A conversion**

Many microcontroller applications are geared to processing and generating analogue signals. The SBC extension board contains a D-A (digital-to-analogue) converter which is ideal for developing such applications. This course instalment aims at showing you how this D-A converter can be used, in conjunction with the comparators on the extension board, to measure analogue values.

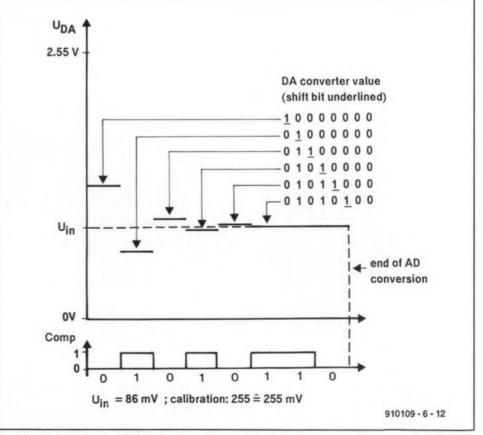

## Conversion principle

One way of converting an analogue voltage into a corresponding digital value is based on the 'ramp' principle, which is illustrated in Fig. 28. A ramp-shaped voltage is output via a D-A converter, and increased until a comparator output signals that the instantaneous value of the ramp is greater than the input voltage. The previous DAC output value is then taken to equal the input voltage. The ramp voltage is simply generated by increasing a register value from 0, and sending this value to a DAC. An example of a program that does so is XAM-PLE14.A51 on your course diskette. Since that is a relatively simple program, it will not be discussed here.

The main disadvantage of the ramp DAC principle is that it is relatively slow. In the worst case, at a resolution of 8 bits, the ramp value must be increased (and compared to the input voltage) no fewer than 255 times. Similarly, at a resolution of 12 bits, a maximum of 4,096 steps is required. Furthermore, each step should allow for the settling times of the DAC and the comparators. All in all, the ramp principle is too slow for many applications.

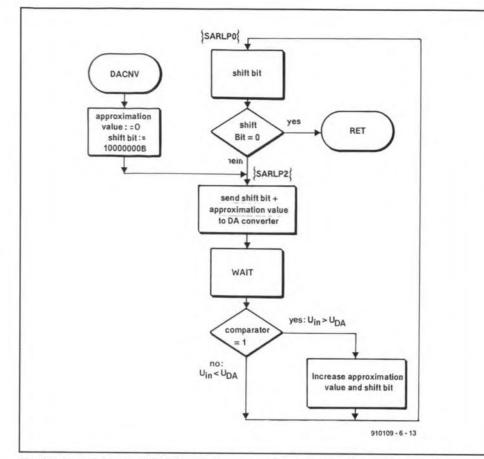

A faster DAC principle, which is also used in many DAC ICs, is called successive approximation. As shown below, it is

#### By Dr. M. Ohsmann

relatively simple to implement in software.

During the successive approximation, the bits of the value to be converted are determined one by one. This means that eight steps are required to achieve 8-bit resolution. A register is used to determine which bit is 'measured'. The individual bits of the analogue value that are already known are also contained in a register. The principle of operation and a corresponding software flow chart are given in Figs. 29 and 30, respectively. Initially, the approximation value is set to 0, and the register that stores the shift bit is set to 1000 00002. The approximation starts with bit 7. A conversion cycle consists of the following steps: first, a new DAC output value is determined. This value is the sum (here: logic OR) of the shift bit and the approximation bit set up so far. This value is output to the DAC, and compared to the input value with the aid of the comparator. If the input voltage is greater than the DAC voltage, the new approximation value equals the previously sent comparator value. This approximation value has a '1' at the position of the shift

Fig. 28. Ramp A-D conversion principle.

bit. If the input voltage is smaller than the DAC voltage, the old approximation value is retained, which means that it has a '0' at the position of the shift bit. The above sequence determines the new bit in the approximation value. Next, the shift bit

Fig. 29. Successive approximation D-A conversion principle.

Fig. 30. Flow diagram of XAMPLE15, the successive approximation D-A converter.

| LINE LOC<br>1 0000            | OBJ   |      |     |                                          | SOUR      |                                                                                                                               |       |         |        |                                                                                   |

|-------------------------------|-------|------|-----|------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------|-------|---------|--------|-----------------------------------------------------------------------------------|

| 2 0000                        |       |      |     |                                          | P.1.      | US AAMPLEI                                                                                                                    | 5.A5. | 1       |        | *********                                                                         |

| 3 0000                        |       |      |     | P1                                       | EQU       | 090H                                                                                                                          |       |         |        |                                                                                   |

| 4 0000                        |       |      |     | 7                                        |           |                                                                                                                               |       |         |        |                                                                                   |

| 5 0000                        | -     |      |     |                                          | ORG       | 4100H                                                                                                                         |       |         | ; sta: | rt address of program                                                             |

| 6 4100                        | 7B 0  | 1    | [1] | START                                    | MOV       | R3,#000                                                                                                                       | 00001 | 18      | ; mas  | k channel 1                                                                       |

| 8 4102                        | 31 2  | 4    | [2] |                                          | ACA       | LL DACNV<br>LL DYTE<br>LL BLANK<br>R3, #0000<br>LL DACNV<br>LL BYTE<br>LL BLANK<br>R3, #0000<br>LL DACNV<br>LL BYTE<br>A, #13 |       |         | ; cal. | 1 DA converter                                                                    |

| 9 4104                        | 31 4  |      | [2] |                                          | ACAL      | LL BITE                                                                                                                       |       |         | ; send | d byte and null character                                                         |

| 10 4108                       | 78 0  | 2    | [1] |                                          | MOV       | R3. #0000                                                                                                                     | 00010 | B       | · char | anal 2                                                                            |

| 11 410A                       | 31 2  | 0    | 121 |                                          | ACAL      | L DACNV                                                                                                                       | 00010 | 10      | , chai | iner z                                                                            |

| 12 410C                       | 31 4  | 4    | [2] |                                          | ACAL      | LL BYTE                                                                                                                       |       |         |        |                                                                                   |

| 13 410E                       | 31 4  | B.   | [2] |                                          | ACAI      | L BLANK                                                                                                                       |       |         |        |                                                                                   |

| 14 4110                       | 7B 0  | 4    | [1] |                                          | MOV       | R3,#0000                                                                                                                      | 00100 | B       | ; char | nnel 3                                                                            |

| 15 4112                       | 31 2  | 0    | [2] |                                          | ACAI      | L DACNV                                                                                                                       |       |         |        |                                                                                   |

| 16 4114                       | 31 4  | 9    | [2] |                                          | ACAI      | L BYTE                                                                                                                        |       |         | 1000   | 121.12                                                                            |

| 10 4110                       | 74 01 | 2    | [1] |                                          | MOV       | A,#13                                                                                                                         |       |         | ; line | a feed                                                                            |

| 10 4110                       | 74 0  |      | [4] |                                          | MOU       | L CHR                                                                                                                         |       |         |        |                                                                                   |

| 20 4110                       | 31 40 | -    | 121 |                                          | ACA1      | T. CHP                                                                                                                        |       |         |        |                                                                                   |

| 21 411E                       | 80 E  | õ    | 121 |                                          | SJMP      | START                                                                                                                         |       |         | . infi | inite loop                                                                        |

| 22 4120                       |       |      |     |                                          | oom       | D arrite                                                                                                                      |       |         |        |                                                                                   |

| 23 4120                       | D2 9: | L    | [1] | DACNV                                    | SETB      | LL DACNV<br>LL BYTE<br>A, #13<br>LL CHR<br>A, #10<br>LL CHR<br>START<br>P1.1<br>R6, #0<br>A, #080H<br>SARLP2<br>A, R7         | *     | for     | oscil  | loscope                                                                           |

| 24 4122                       | 7E 0  | 2    | [1] |                                          | VOM       | R6,#0                                                                                                                         |       | app     | roxima | tion value                                                                        |

| 25 4124                       | 74 80 | )    | [1] |                                          | MOV       | A, #080H                                                                                                                      | 2     | SHI     | FT-BIT |                                                                                   |

| 26 4126                       | 80 09 | •    | [2] |                                          | SJMP      | SARLP2                                                                                                                        | ;     | ្យបរាផ្ | b rucc | ) TOOD                                                                            |

| 27 4128<br>28 4129            |       |      | [1] | SARLPO                                   | NOV       | A, R7                                                                                                                         | 7     | get     | SHIFT  | T-BIT                                                                             |

| 29 412A                       |       |      | 111 |                                          | DDC       | A,R7<br>C<br>A<br>SARLP2                                                                                                      |       |         |        | AL 5111                                                                           |

| 30 412B                       |       |      | 121 |                                          | TN2       | A<br>SARLP2<br>A,R6                                                                                                           |       | SAL     | tt rig | pht, fill with Os                                                                 |

| 31 412D                       |       |      | [1] |                                          | MOST      | A DE                                                                                                                          |       | det     | resul  | when SHIFT-BIT<>0                                                                 |

| 32 412E                       |       |      | [1] |                                          | CLR       | P1.1                                                                                                                          |       |         |        | of conversion on scope                                                            |

| 33 4130                       | 22    |      |     |                                          | Th TD 499 |                                                                                                                               |       |         |        |                                                                                   |

| 34 4131                       | FF    |      | [1] | SARLP2                                   | MOV       | R7,A                                                                                                                          | 2     | save    | B SHIF | T-BIT in R7<br>proximation value                                                  |

| 35 4132                       | 4E    |      | [1] |                                          | ORL       | A,R6                                                                                                                          | 2     | add     | to ap  | proximation value                                                                 |

| 36 4133                       | 90 C0 | 00   | [2] |                                          | MOV       | DPTR, #0C0                                                                                                                    | HOOH  |         |        | A converter                                                                       |

| 37 4135<br>38 4137<br>39 4138 | E U   |      | 121 |                                          | MOVX      | OPTR, A                                                                                                                       | 2     | send    | i to D | A converter                                                                       |

| 39 4138                       | 78 64 |      | 111 |                                          | MUY       | 254,25                                                                                                                        |       | mar,    | c sum  | for later                                                                         |

| 40 413A                       |       |      | 121 | SARWT                                    | D.TNZ     | R2,#100<br>R2,SARWT                                                                                                           | - 1   | sett    | ling   | time                                                                              |

| 41 413C                       |       |      | 121 | SHOWL                                    | MOVX      | A. GDPTR                                                                                                                      |       | fete    | h com  | parator output                                                                    |

| 42 413D                       |       |      | [1] |                                          | ANL       | A. R3                                                                                                                         |       | sele    | ect de | sired KOMP                                                                        |

| 43 413E                       |       |      | [2] |                                          | JZ        | SARLPO                                                                                                                        | 7     | Bit=    | 0 if   | Uin <udac, bit<="" do="" not="" set="" td=""></udac,>                             |

| 44 4140                       | EC    |      | [1] |                                          | MOV       | A, R4                                                                                                                         | 5     | Bit=    | 1 if   | Uin>Udac                                                                          |

| 44 4140<br>45 4141            | FE    |      | [1] |                                          | NOV       | R6, A                                                                                                                         |       | appr    | oxima  | Uin <udac, bit<br="" do="" not="" set="">Uin&gt;Udac<br/>tion value: =sum</udac,> |

| 46 4142                       | 80 E4 |      | [2] |                                          | SJMP      | SARLPO                                                                                                                        |       |         |        |                                                                                   |

| 47 4144 48 4144               |       |      |     |                                          |           |                                                                                                                               |       |         |        |                                                                                   |

| 49 4144                       |       |      |     | COMMAN                                   | COT IN    | terface                                                                                                                       |       |         |        |                                                                                   |

| 50 4144                       |       |      |     | MON                                      | FOU       | 02008                                                                                                                         |       |         |        |                                                                                   |

| 51 4144                       |       |      |     | CCCHR                                    | EOU       | 001H                                                                                                                          |       |         |        |                                                                                   |

| 52 4144                       |       |      |     | CCBYTE                                   |           |                                                                                                                               |       |         |        |                                                                                   |

| 53 4144                       |       |      |     | ;                                        |           |                                                                                                                               |       |         |        |                                                                                   |

| 54 4144                       | 75 30 | 03   | [2] | BYTE                                     | MOV       | COMMAND,                                                                                                                      | #ccB  | YTE     |        |                                                                                   |

| 55 4147                       |       |      |     |                                          |           | MON                                                                                                                           |       |         |        |                                                                                   |

| 56 414A                       |       |      | [1] | BLANK                                    | MOV       | A, #' '                                                                                                                       |       |         |        |                                                                                   |

| 57 414C<br>58 414F            | 12 02 | 00   | [2] | CHR                                      | TTHE      | COMMAND,<br>MON                                                                                                               | #CCC3 | HR      |        |                                                                                   |

| 59 4152                       | 12 UG | 00   | 141 |                                          | END       | PION                                                                                                                          |       |         |        |                                                                                   |

|                               | SYMB  | OLTA | BLE | (13                                      | abols     | *******                                                                                                                       |       |         |        |                                                                                   |

| P1                            | :009  | 0    | ST  | ART :41                                  | 100       | DACNV :4                                                                                                                      | 120   | S       | ARLPO  | :4128                                                                             |

| CADIDO                        |       | 5    |     | P. P |           | COMMAND :0<br>BYTE :4                                                                                                         | a     |         |        | :0200                                                                             |

|                               |       |      |     |                                          |           |                                                                                                                               |       |         |        |                                                                                   |

## JOIN THE COURSE!

What you need to follow this course:

- an 8032/8052AH-BASIC single board computer as described in Elektor Electronics May 1991. The preferred CPU is a 8051 or 80C32. Alternatively, any other MCS52-based microcontroller system (but read part 1 of the course);

- a course diskette (IBM: order code ESS 1661; Atari: order code ESS 1681) containing programming examples, hex file conversion utilities, and an assembler;

- a monitor EPROM (order code ESS 6091);

- an IBM PC or compatible operating under MS-DOS, or an Atari ST with a monochrome display.

#### Appeared so far:

- Part 1: Introduction (February 1992) Part 2: First 8051 instructions (March

- 1992) Part 3: Hardware extensions for

- 80C32 SBC (April 1992) Part 4: Flags, bit addressing, PSW, conditional jumps, logic

- operators (June 1992) Part 5: Arithmetic instructions (July

- Part 5: Arithmetic Instructions (July 1992)

position is shifted to the right, and the next conversion cycle is run, until all bits are determined. In short, the bit to be determined is provisionally set, and compared to the input voltage. If this causes the approximation value to become too high, the bit is reset. If the approximation value is still too low, the bit is left set.

## An A-D converter program

The program we are about to describe (Fig. 31) outputs the values of three input

voltages in hexadecimal notation. D-to-A conversion on all three channels is made possible by a subroutine called DACNV, which reads the bit position of the relevant comparator output from register R3. DACNV returns the converted value in the accumulator. The main program begins at label START, and is relatively simple. The bit corresponding to the channel number (1 of 3) is set in register R3. Next, The conversion proper, DACNV, is called. A subroutine called BYTE arranges for the value supplied by DACNV to be output (in hexadecimal form) via the V24 interface. After all three values have been sent to the terminal, the program adds a carriage return/line feed (CR/LF) sequence, and a new conversion cycle is started.

28

The D-A conversion is a bit more complex. The approximation value is stored in register R6. The shift bit is contained in register R7, and also, occasionally, in the accumulator. The sum of the shift bit and the approximation value is stored in register R4. The conversion proper starts at label SARLP2, where the accumulator contains the shift bit, and R6 the old approximation value. First, the shift bit is saved in register R7 (line 34). The sum of R6 and the accumulator is formed in line 35, and subsequently sent to the D-A converter. This comparison value is contained in R4. A wait loop, SRWT, is inserted to allow for the settling time of the DAC. The comparator output states are copied into the accumulator in line 41. Comparator output selection is achieved by masking the accumulator contents with the bit in R3 (line 42). Depending on whether the selected comparator output supplies a '1' or a '0', the corresponding new approximation value is formed in R6. The jump to label SARLP0 prepares for the next conversion step. The shift bit is loaded into the accumulator, and shifted to the right (lines 28 and 29). If the result is an accumulator content of 0, the conversion is finished. If not, the program continues at label SARLP2.

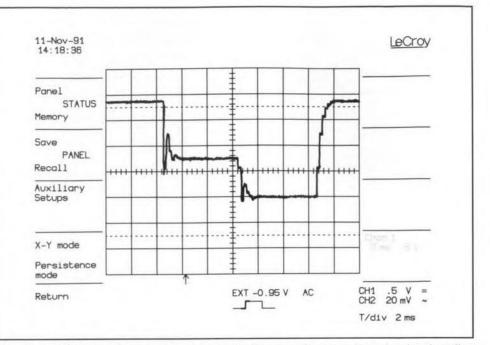

To enable us to trace the conversion steps with the aid of an oscilloscope (or by listening to the loudspeaker), port bit P1.1 is set during the conversion time. Figure 32 shows the signal reproduced by a digital storage oscilloscope. On completion of the D-A conversion, the value in RT6 is copied into the accumulator.

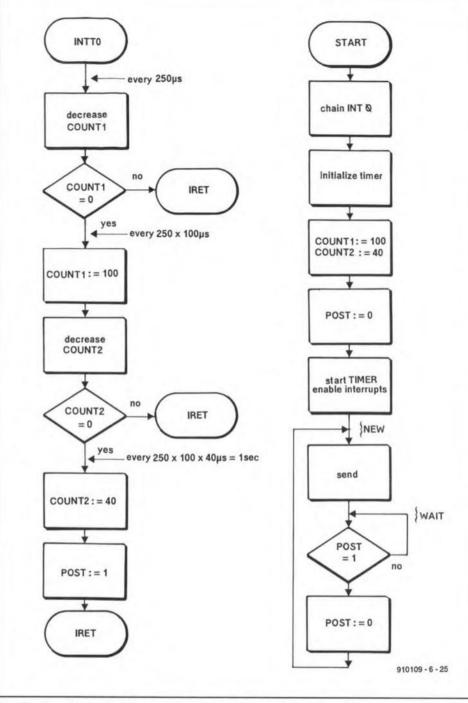

The advantages of the successive approximation principle are evident: only eight loop iterations are required. A fast DAC, and equally fast comparators, enable an 8051 to achieve 8-bit conversion times of 250  $\mu$ s fairly easily. The corresponding sampling rate, 4,000 samples s<sup>-1</sup>, is relatively high.

This program, like others discussed during this course, demonstrates the usefulness of subroutines. To understand how these are managed, it is necessary to have a look at the so-called stack, which is used by the 8051 to store certain data that serves to keep track of subroutine return addresses.

Fig. 32. A-to-D conversion waveform measured with an oscilloscope. Note the signal settling times.

## Stacking it up

The stack pointer, SP (at SFR address 081H), points at an address in the stack range where the return addresses of subroutines and interrupt routines are stored. The stack pointer is contained in internal RAM, and is increased by one whenever a subroutine is called. Next, the first byte of the return address is written to the address pointed at by the SP. Next, the SP is increased by one, and the next address byte is stored. This little demonstration program

loaded with a new value right at the start of the program. When a program contains 'nested' subroutines, each of these requires two bytes of the available stack memory (which is contained in internal RAM).

The situation becomes even more complex when interrupts are programmed. Here, too, each return address calls for two bytes of storage capacity. Additional memory is required to hold saved SFRs, as well as all return addresses for subroutines called up by the interrupt program. The message is clear: make sure that you have

| LINE | LOC  | OBJ      | Т   |       | SOURCE      |

|------|------|----------|-----|-------|-------------|

| 43   | 4118 | 12 41 23 | [2] |       | LCALL UPRO1 |

| 44   | 411B | 00       | [1] |       | NOP         |

| 47   | 4123 | 12 4A BC | [2] | UPRO1 | LCALL UPRO2 |

| 48   | 4126 | 00       | [1] |       | NOP         |

| 50   | 4ABC | 85 08 44 | [2] | UPRO2 | MOV 68,8    |

|      |      |          |     |       |             |

results in the following stack values:

| SP before line 43:       | 07H               |

|--------------------------|-------------------|

| Internal RAM address:    | 08 09 0A 0B 0C OD |

| Contents before line 43: | FF FF FF FF FF FF |

|                          | (preloaded)       |

| Contents after line 50:  | 1B 41 26 41 FF FF |

|                          | (2 addresses on   |

|                          | stack)            |

| SP after line 50:        | OBH               |

|                          |                   |

After a reset, the stack pointer contains the value '7' (refer back to Figs. 5 and 8), so that the stack begins at address '8' in the internal RAM, and grows upwards. This means that the stack overwrites register bank 1, and, possibly, other banks also. Register bank 1 is therefore not available for general programming, unless the SP is

sufficient stack room at all times! Users of the 8052, 8032 or 80C32 may avail themselves of the additional 128 bytes of internal RAM contained in these controllers. You may do so by programming

| MOV | SP,#080H | ;upper RAM as |

|-----|----------|---------------|

|     |          | stack         |

This gives a stack space of 128 bytes, which should be enough for most applications.

#### Saving data on to the stack

It often happens that a certain byte (SFR or accumulator) is to be put away safely, and retrieved a little later. This is achieved by

| -      | (MSB)    | (LSB)                                                                                                                                                                                          |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L      | EA X ET2 | ES ET1 EX1 ET0 EX0                                                                                                                                                                             |

| Symbol | Position | Function                                                                                                                                                                                       |

| EA     | IE.7     | disables all interrupts. If EA = 0, no<br>interrupt will be acknowledged. If EA<br>= 1, each interrupt source is<br>individually enabled or disabled by<br>setting or clearing its enable bit. |

| -      | IE.6     | reserved                                                                                                                                                                                       |

| ET2    | IE.5     | enables or disables the Timer 2<br>overflow or capture interrupt. If ET2<br>= 0, the Timer 2 interrupt is disabled                                                                             |

| ES     | IE.4     | enables or disables the Serial Por<br>interrupt. If ES = 0, the Serial Por<br>interrupt is disabled.                                                                                           |

| ET1    | IE.3     | enables or disables the Timer 1<br>Overflow Interrupt. If ET1 = 0, the<br>Timer 1 Interrupt is disabled.                                                                                       |

| EX1    | IE.2     | enables or disables External Interrup<br>1. If EX1 = 0, External Interrupt 1 is<br>disabled.                                                                                                   |

| ETO    | IE.1     | enables or disables the Timer (<br>Overflow Interrupt If ETO = 0, the<br>Timer 0 Interrupt is disabled.                                                                                        |

| EX0    | IE.0     | enables or disables External Interrup<br>0. If EX0 = 0, External Interrupt 0 is<br>disabled.                                                                                                   |

|        |          | 910109 - 6 - 17                                                                                                                                                                                |

.

Fig. 34. Functions of individual bits in the interrupt enable register, IE.

| -      | (MSB)    | (LSB)                                                                                                    |

|--------|----------|----------------------------------------------------------------------------------------------------------|

| L      | X X PT2  | PS PT1 PX1 PT0 PX0                                                                                       |

| Symbol | Position | Function                                                                                                 |

| -      | IP.7     | reserved                                                                                                 |

| -      | IP.6     | reserved                                                                                                 |

| PT2    | IP.5     | defines the Timer 2 Interrupt priorit<br>level. PT2 = 1 programs it to the<br>higher priority level.     |

| PS     | IP.4     | defines the Serial Port Interrup<br>priority level. PS = 1 programs it to<br>the higher priority level.  |

| PT1    | IP.3     | defines the Timer 1 interrupt priority<br>level, PT1 = 1 programs it to the<br>higher priority level.    |

| PX1    | IP.2     | defines the External Interrupt<br>priority level, PX1 = 1 programs it to<br>the higher priority level,   |

| PTO    | IP,1     | defines the Timer 0 Interrupt priority<br>level, PT0 = 1 programs it to the<br>higher priority level,    |

| PXO    | IP.0     | defines the External Interrupt (<br>priority level, PX0 = 1 programs it to<br>the higher priority level. |

|        |          | 910109 - 6 - 19                                                                                          |

Fig. 36. Bits in the Interrupt Priority register, IP.

the instructions

| PUSH | ACC | ;save accu on to |

|------|-----|------------------|

|      |     | stack            |

|      |     | ;instructions in |

|      |     | between          |

| POP  | ACC | ;fetch accu from |

|      |     | stack            |

The PUSH instruction stores the indicated byte (direct addressing) on to the stack. Subsequently, the SP is automatically increased by one. The POP instruction fetches ('pops') the last PUSHed byte from the stack. Since storing (PUSHing) consumes stack space, the PUSH instruction should be used with care, since only limited space is available. The PUSH and POP in-

| Interrupt | Interrupt address | Link Index | Link Jump |  |

|-----------|-------------------|------------|-----------|--|

| IE0       | 0003H             | 1          | 4003H     |  |

| TFO       | 000BH             | 2          | 4006H     |  |

| IE1       | 0013H             | 3          | 4009H     |  |

| TF1       | 001BH             | 4          | 400CH     |  |

| RI+TI     | 0023H             | 5          | 400FH     |  |

| TF2+EXF2  | 002BH             | 6          | 4012H     |  |

Fig. 33. Interrupt 'detours' contained in the system monitor program, EMON51.

structions are often used within subroutines to rescue SFRs, which are then available again unchanged at the end of a subroutine. sible to external events. Such an event might be the arrival of a measurement value that is to be processed as fast as possible.

## Interrupts

Interrupts are used whenever it is necessary for a program to respond as quickly as posInterrupts from various sources can occur at any time during the program execution, which makes their programming and debugging complex, if not problem-

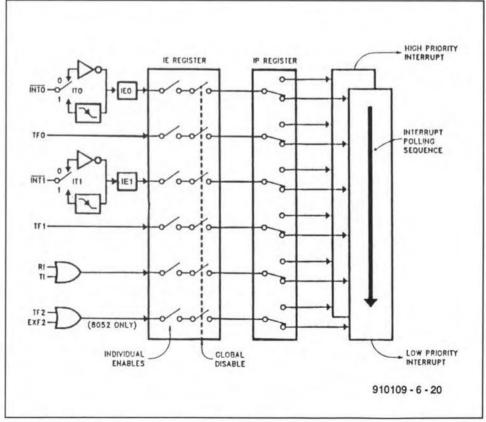

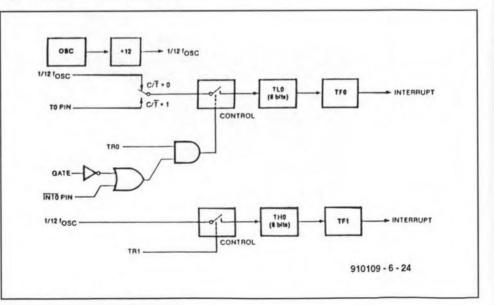

Fig. 37. 8051 interrupt control system structure.

**ELEKTOR ELECTRONICS SEPTEMBER 1992**

atic. Beginners are, therefore, well warned against the many pitfalls that lurk in interrupt-controlled microcontroller systems.

30

The interrupt capabilities of the 8051 family are briefly discussed below. External interrupts are applied via IC input pins INT0 and INT1 (pins 12 and 13). On the 80C32 SBC, these two pins receive inverted signals that arrive via connector pins c3 and c5, and IC12. The user can select the interrupt mode beforehand: an interrupt occurs (1) on a signal edge only (positive edge on INT0), or (2) when INT0 = '1' (static logic level).

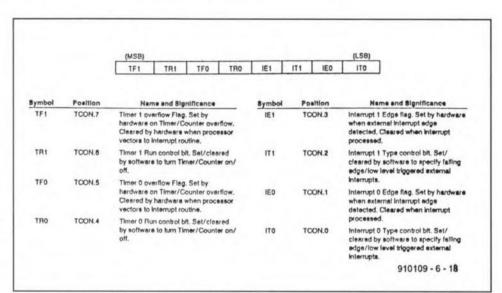

Further interrupt sources are Timer Flag0 and Timer Flag1 (TF0 and TF1), Receiver Interrupt (RI) and Transmitter Interrupt (TI). The 8052 and 8032 controllers have two more interrupt sources: Timer2 and external interrupt line EXF2. When an interrupt occurs, the processor executes a kind of LCALL instruction, which results in a jump to the address associated with the interrupt. Interrupt sources and associated addresses are listed in Fig. 33.

It will be noted that the interrupt addresses are normally in the memory reserved for EPROMs, and, therefore, not easily changed. Fortunately, the monitor EPROM (EMON51) provides so-called links, which are described in the file EMON51.DOC. The links allow interrupts to be called and relocated as required. For instance, the monitor causes interrupt IE0 to jump to address 4003H of the program memory, which is RAM. After a reset, the monitor loads this address with a jump to an internal interrupt routine. By calling the monitor subroutine LINK, you can change the jump address to point to your own interrupt. All that is required to set up this 'detour' is to have your interrupt address ready in the DPTR, and the index in the accumulator, before calling LINK. It should now be clear why we start our course programs at 4100H instead of 4000H: the lower page, 4000H to 40FFH, is used by the monitor.

The organization of the interrupts is arranged by the SFRs IE (interrupt enable; address 0A8H) and IP (interrupt priority; address 0B8H). Interrupts can be enabled or disabled selectively by setting or resetting the appropriate bits in IE, as shown in Fig. 34. Bits ITO and IT1 (see Fig. 35) determine whether the external interrupts are level-triggered (bit='0') or edge-triggered (level='1'). Both bits are contained in the timer-control SFR, TCON, at address 088H (ITO = TCON.0; IT1 = TCON.2). For a quick test, use the following little program (not on your course disk):

| IE    | EQU 08AH     | ;new: interrupt<br>enable SFR |

|-------|--------------|-------------------------------|

| :     |              |                               |

|       | ORG 4100H    | ;program start<br>address     |

|       | MOV IE,#0FFH | ;all interrupts               |

|       |              | on                            |

| FREVR | SJMP FREVR   |                               |

|       | END          |                               |

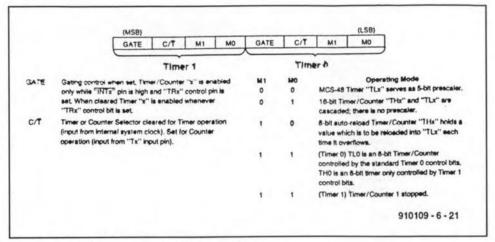

Fig. 38. Bits in the Timer-Mode register, TMOD.

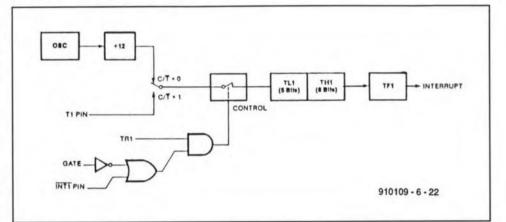

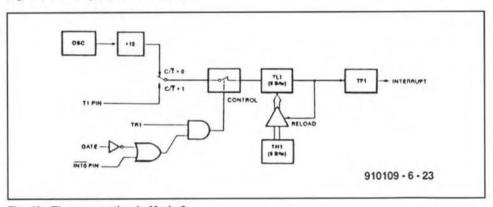

Fig. 40. Timer operation in Mode 2.

Assemble and run this program, and see what happens if you generate an interrupt by applying a +5 V pulse to connector pin c3 or c5. Can you explain what happens?