THE INTERNATIONAL ELECTRONICS MAGAZI JULY 1992 UK £2.95

FREE in this issue: Greenweld's sale supplement

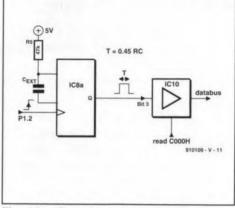

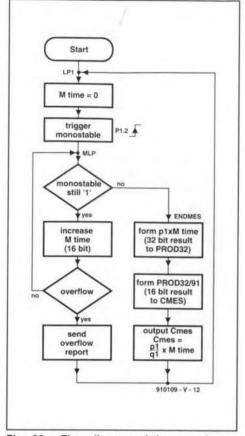

# BUMPER SUMMER ISSUE With over 50 construction projects

# Audio-frequency DAC

**Opto-card for multi-purpose bus**

Mark 2 QTC 80+40 loop

**Fuzzy** logic

Dealing with noise and interference

RS232 tester

In next month's issue (among others):

- 23 cm FM transceiver Replace your paging

- system with a high-power intercom

- A.F. digital-to-analogue converter Part 2

- 8051/8032 assembler course Part 6

- The applicable and constructable fictions of electronics

- Flash EPROMs

- CALSOD II: designing loudspeaker boxes by computer

- Current-sense MOSFETs

- EPROM emulator II

#### Front cover

This month we publish the first part of an a.f. digital-toanalogue converter that can be built into existing equipment or be used as a stand-alone unit. It is eminently suitable for use with the CD player we published earlier this year. Twenty-bit converter ICs, ×8 over-sampling and highquality analogue stages are used to translate accurately the digital output of CDs. DAT recorders or radio broadcasts into the desired , analogue information.

Copyright © 1992 Elektuur BV

# CONTENTS

# July 1992 Volume 18 Number 202

| AUDIO & HI-FI                              |     | Three-phase simulator                  | 76       |

|--------------------------------------------|-----|----------------------------------------|----------|

| Audio/video processor - Part 3             | 17  | Touch 'on', auto 'off' controller for  |          |

| A.F. digital-to-analogue converter         | 24  | battery operated equipment             | 77       |

| Digital volume control                     | 62  | in the second second second            |          |

| Scanner for all solid-state preamplifier   | 67  | RADIO, TELEVISION AND                  |          |

| Stereo protector against d.c.              | 68  | COMMUNICATIONS                         | 1 Cale   |

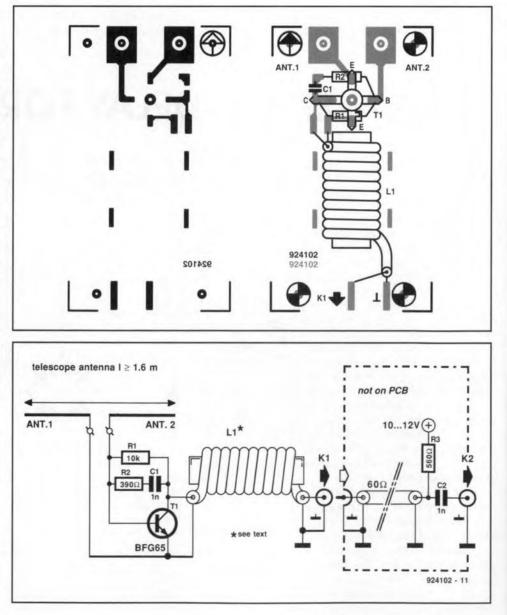

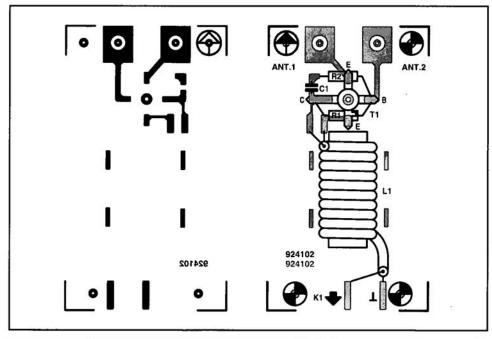

|                                            |     | Wideband active telescopic antenna     | 46       |

| COMPONENTS                                 | 300 | Infra-red headphone transmitter        | 47       |

| Elements of passive electronic components: |     | Infra-red headphone receiver           | 47       |

| Part 3 – The capacitor                     | 30  | CB-to-SW down converter                | 49       |

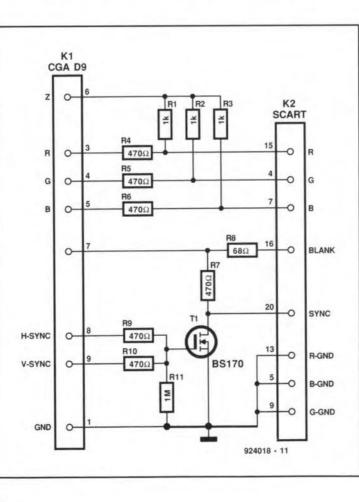

|                                            |     | CGA-to-SCART adaptor                   | 51       |

|                                            |     | Video enhancer                         | 73       |

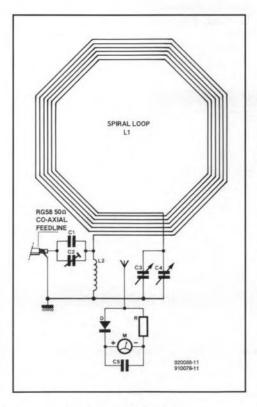

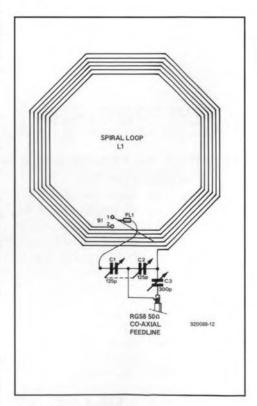

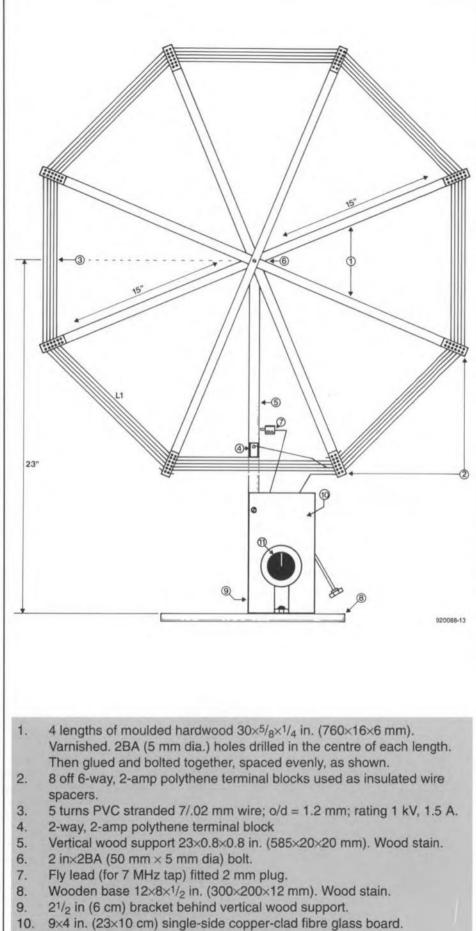

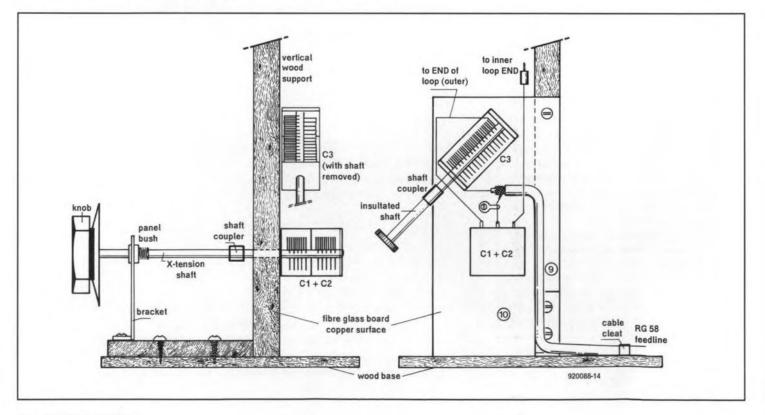

| COMPUTERS & MICROPROCESSO                  |     | Mark Two 80/40 QTC loop antenna        | 88       |

| Opto card for universal PC I/O interface   | 14  | FM tuner - Part 5 (final)              | 91       |

| 8051/8032 assembler course - Part 5        | 40  | Kalundborg 10 MHz frequency reference  | 100      |

| Power-on delay for Atari ST                | 45  | Preamplifier for Kalundborg frequency  |          |

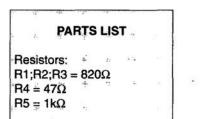

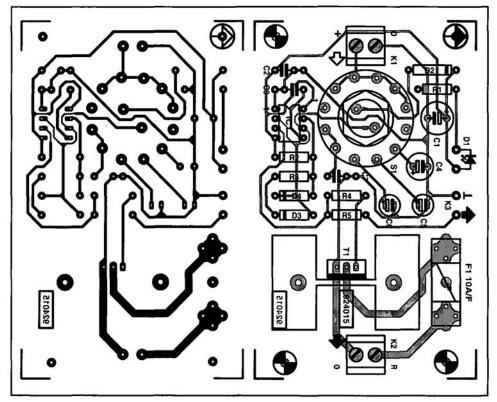

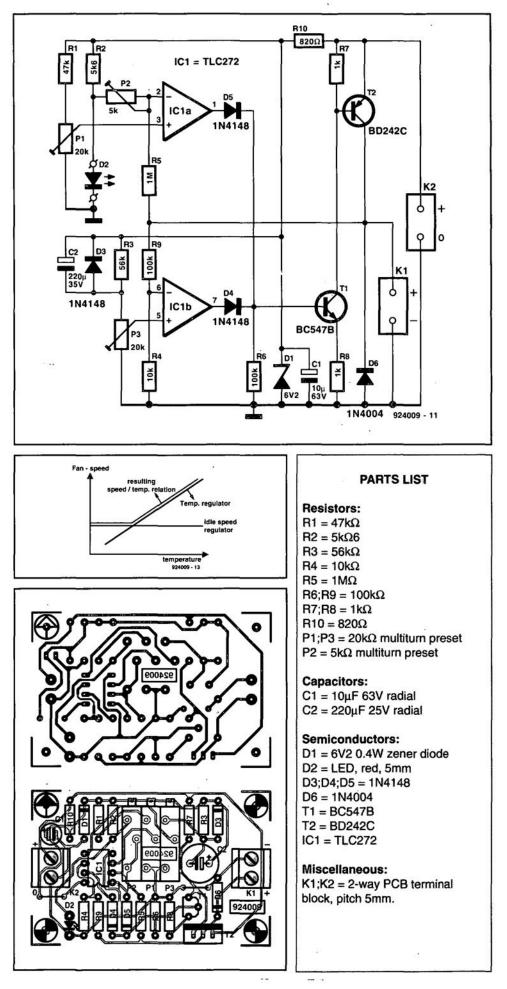

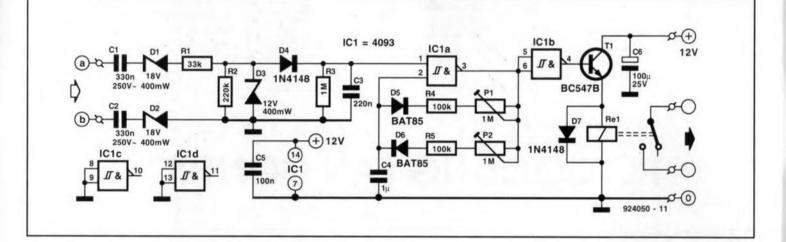

| PC fan control                             | 59  | reference                              | 101      |

| PC cooling fan control                     | 65  |                                        |          |

| RS-232 quick tester                        | 84  | SCIENCE & TECHNOLOGY                   | I market |

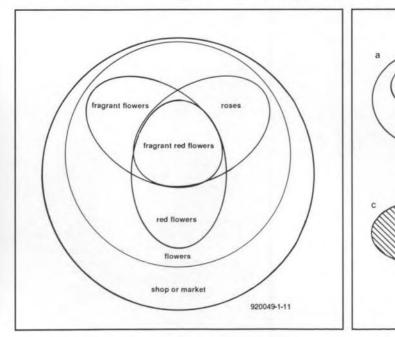

|                                            |     | Fuzzy logic: an introduction           | 80       |

| GENERAL INTEREST                           |     | A virtual component: half-capacitance  |          |

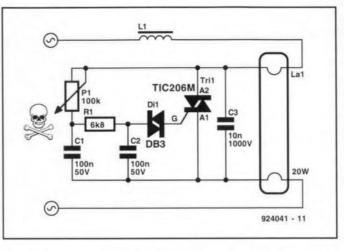

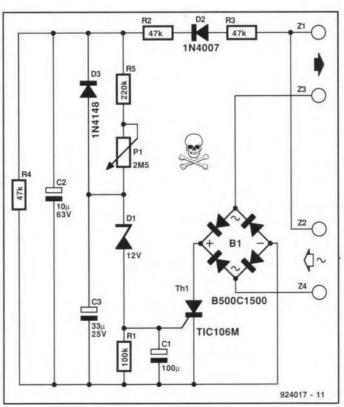

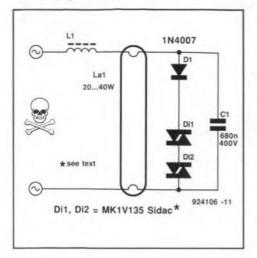

| Dimmer for neon tubes                      | 45  | from Heaviside                         | 96       |

| Metal detector                             | 48  |                                        | 0.00     |

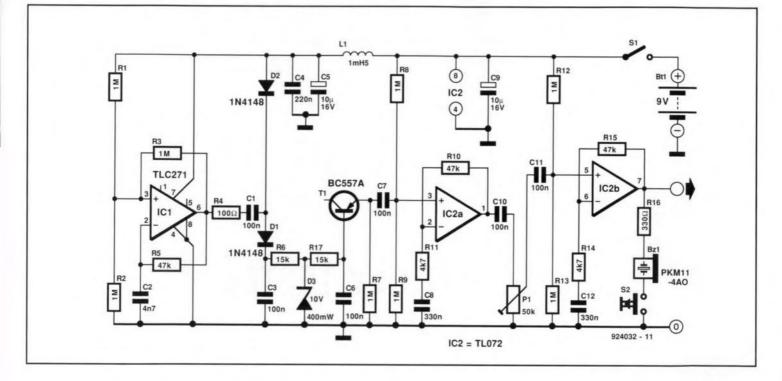

| Telephone monitor                          | 50  | TEST & MEASUREMENT                     |          |

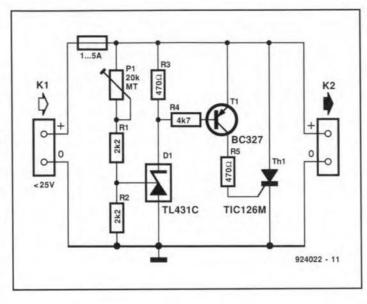

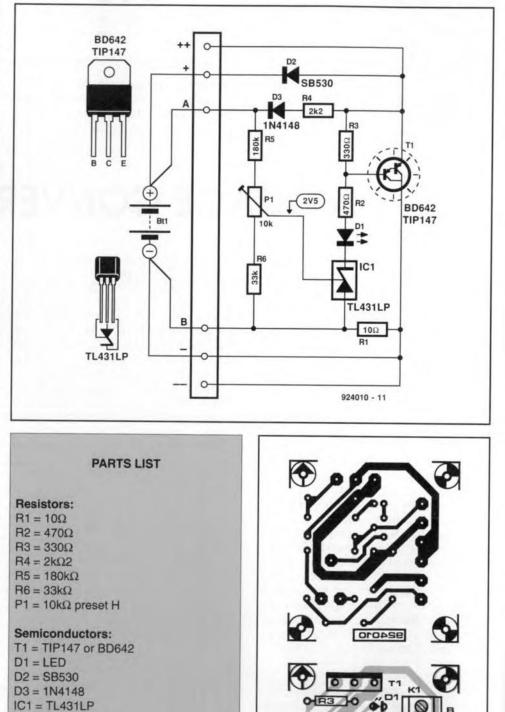

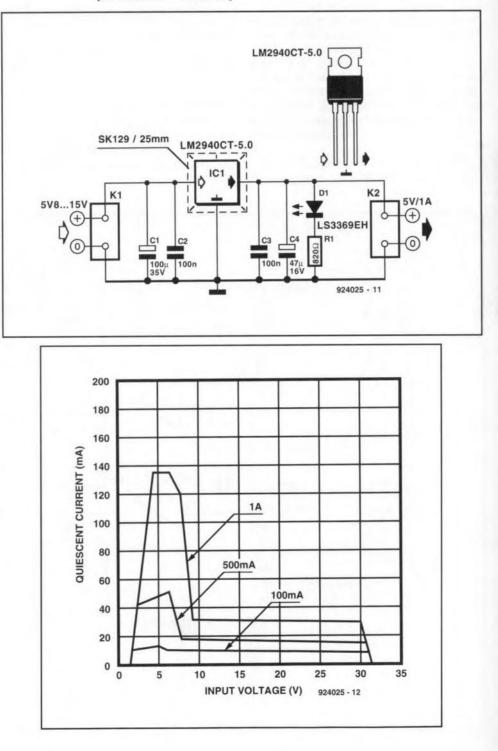

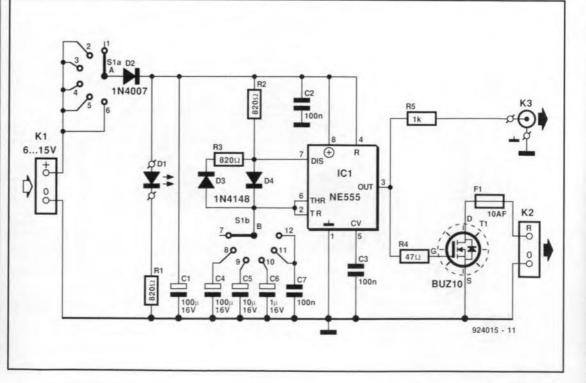

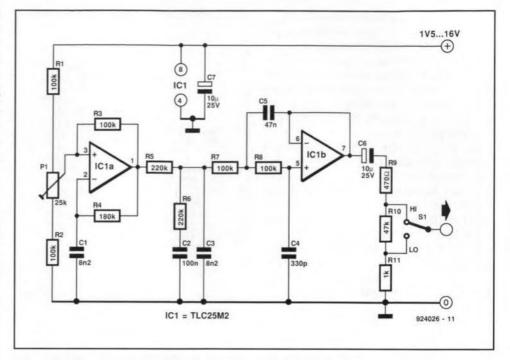

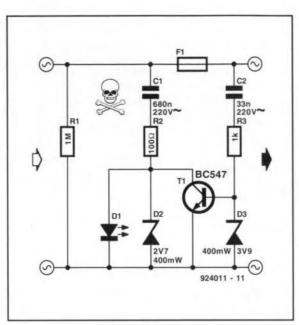

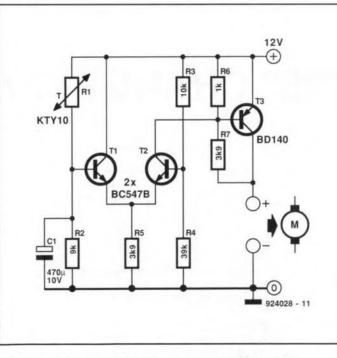

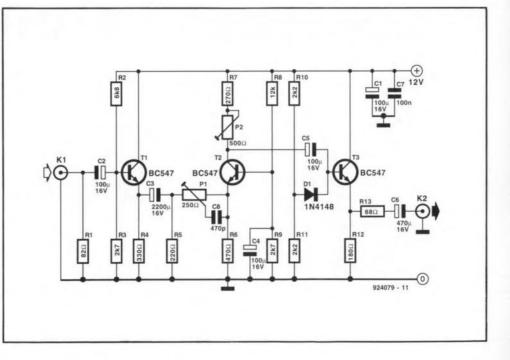

| Water pump control for solar power system  | 56  | Dealing with noise and interference in |          |

| Halogen lamp protector                     | 60  | electronic instrumentation circuits    | 20       |

| Extra brake light                          | 61  | Pulse generator                        | 29       |

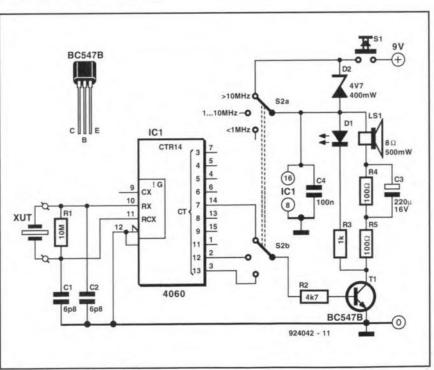

| Super starter for cars                     | 63  | Acoustic crystal tester                | 33       |

| Starter for model aircraft                 | 64  | Power supply tester                    | 58       |

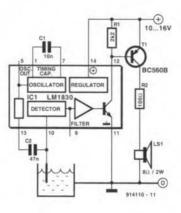

| Telephone gong                             | 66  | Audible fluid level indicator          | 63       |

| Bounce-free change-over switch             | 66  | Simple signal generator                | 64       |

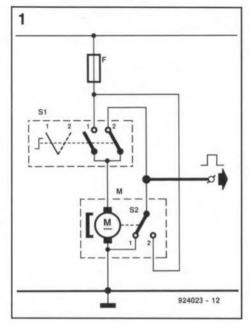

| Front-to-rear wiper coupling               | 75  | Fuse monitor                           | 65       |

| Sidac neon tube starter                    | 76  | Frequency probe                        | 67       |

| Rev counter for diesel engines             | 78  | Continuity tester                      | 71       |

|                                            |     | Noise generator                        | 72       |

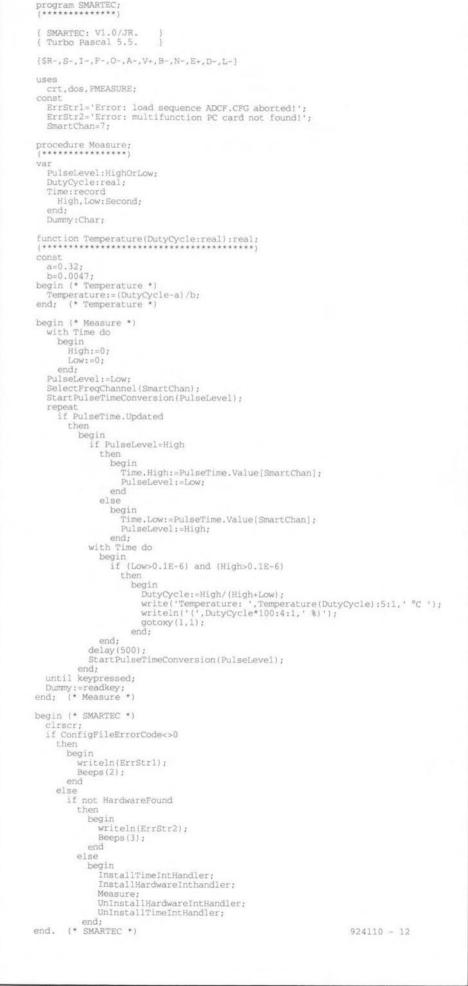

| POWER SUPPLIES &                           |     | Smartec temperature sensor             | 78       |

| BATTERY CHARGERS                           |     | Differential temperature indicator     | 98       |

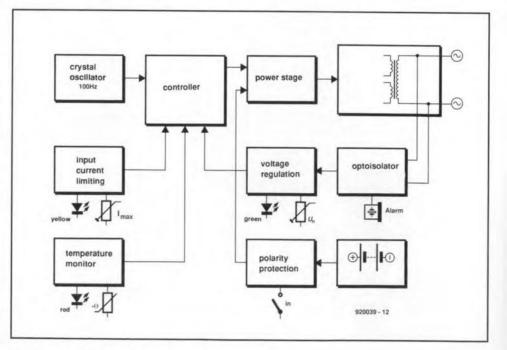

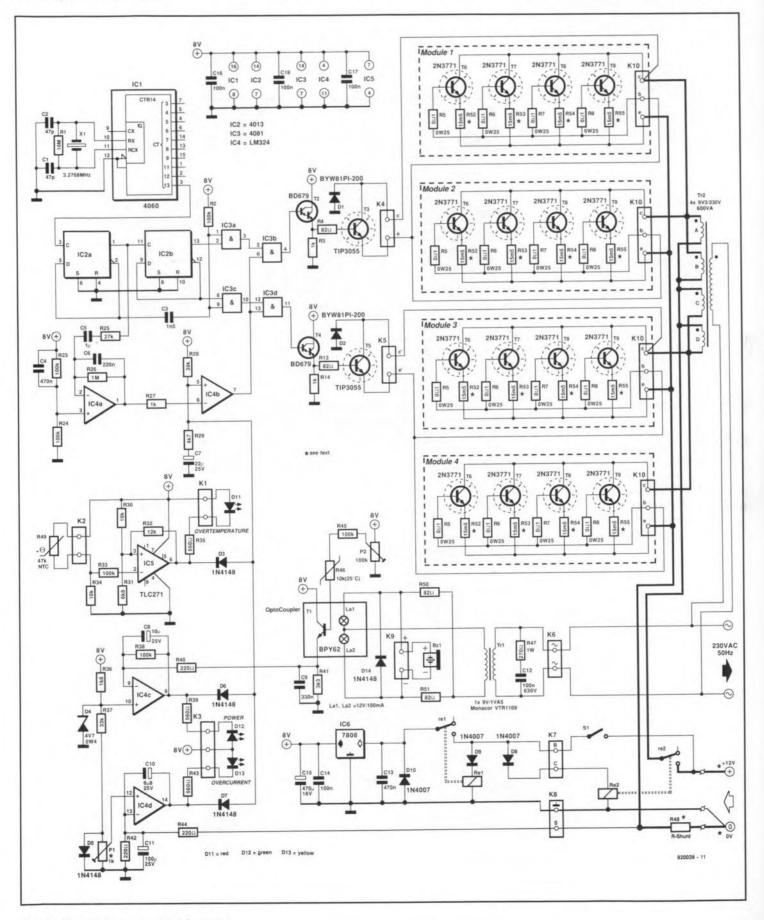

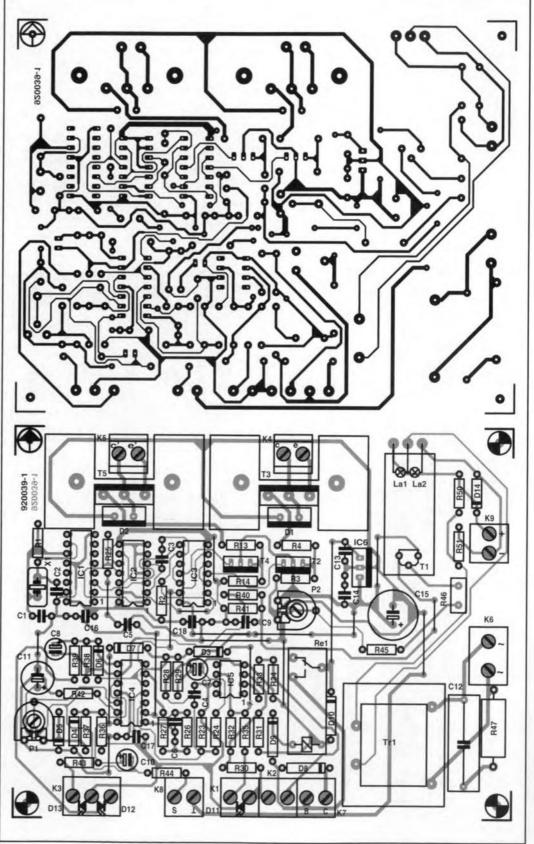

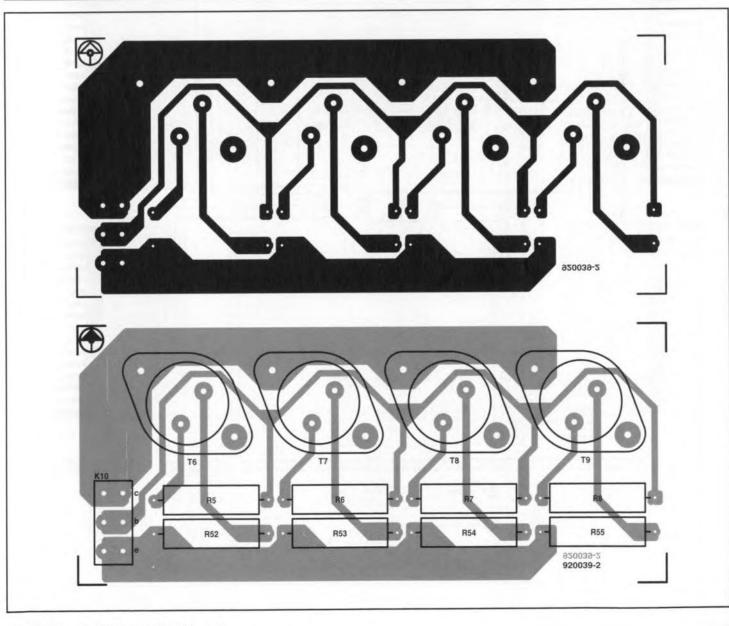

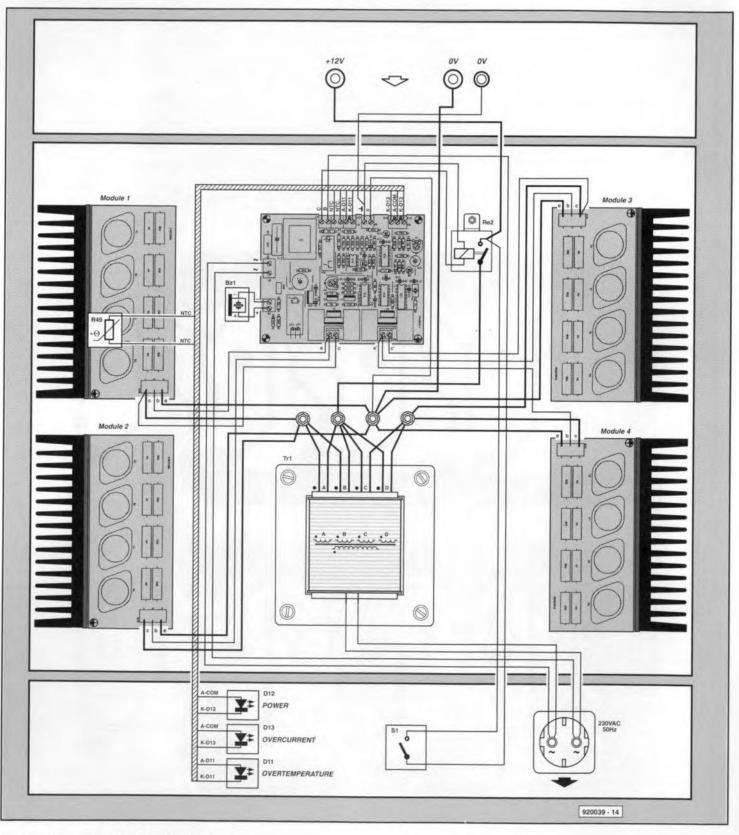

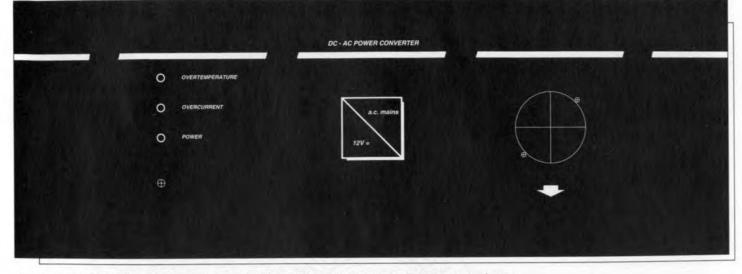

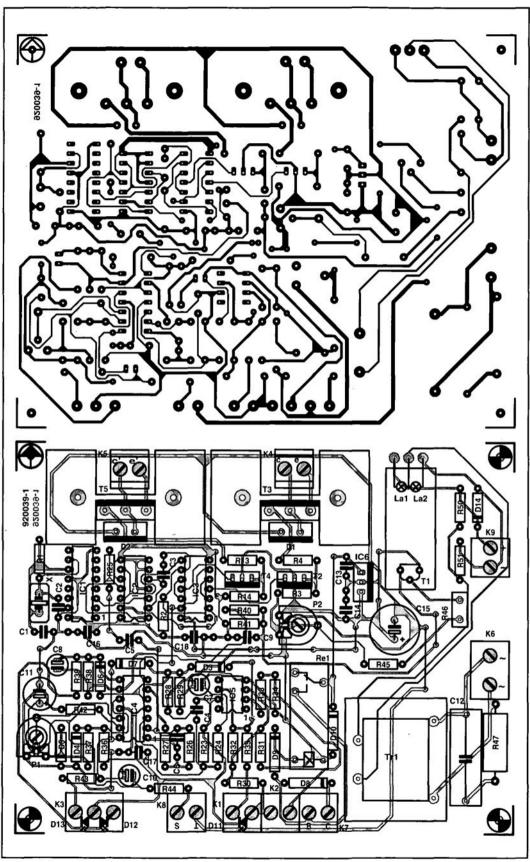

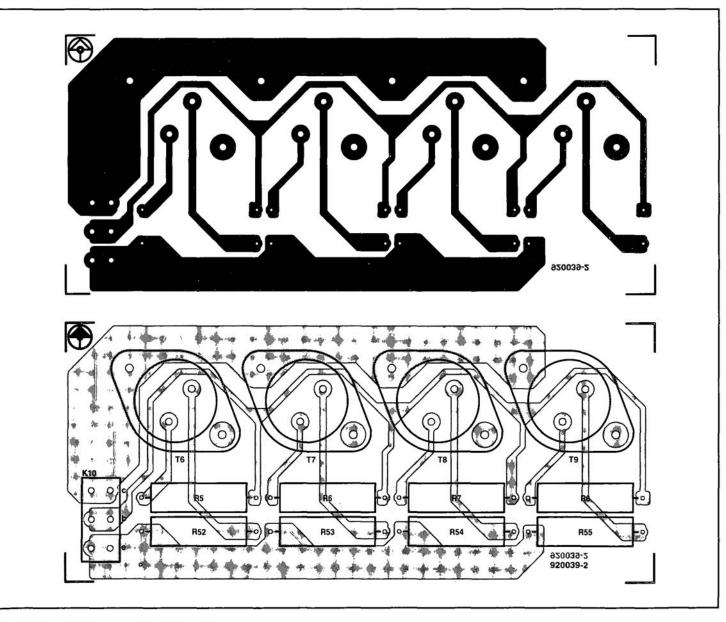

| 12 VDC-to-240 VAC inverter                 | 34  |                                        | NIDE .   |

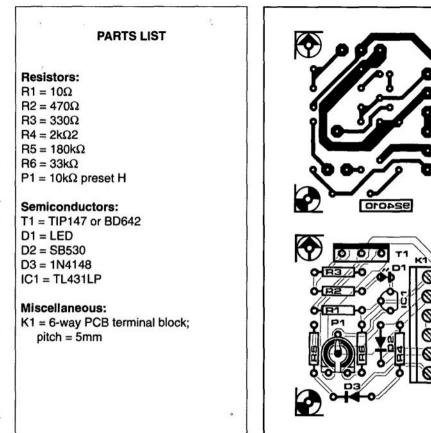

| Low-drop regulator I                       | 50  | MISCELLANEOUS INFORMATIO               | DN       |

| Crowbar protection                         | 51  | Electronics scene                      | 11       |

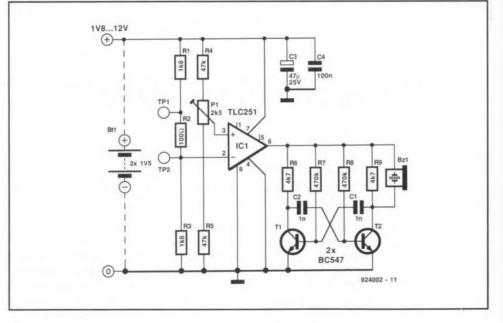

| Low-battery indicator                      | 52  | Events                                 | 13       |

| Voltage converter I                        | 53  | Readers' corner                        | 99       |

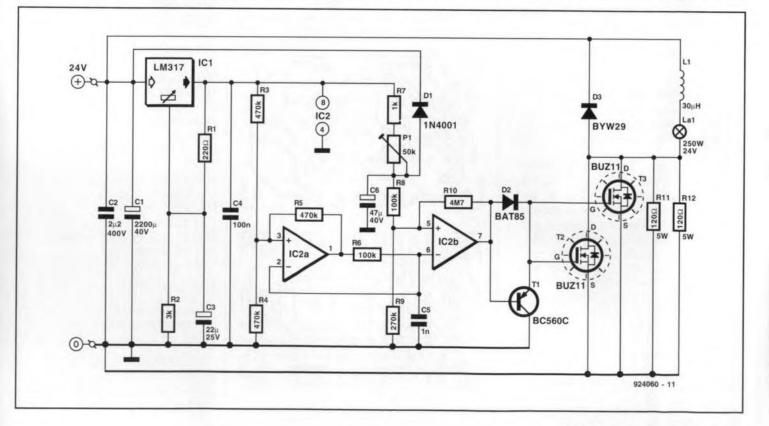

| Battery regulator for solar power system   | 54  | Readers' services                      | 102      |

| Low-drop regulator II                      | 55  | Terms of business                      | 104      |

| Simple power supply concept                | 69  | Index of advertisers                   | 114      |

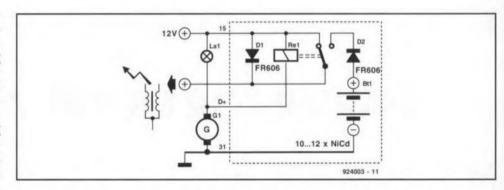

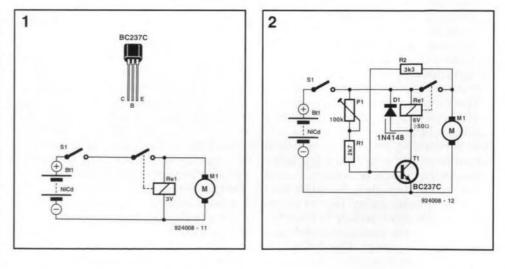

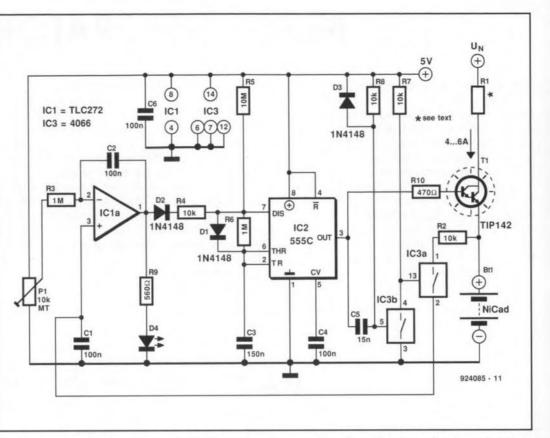

| Experimental fast NiCd battery charger     | 70  |                                        |          |

| 240 VAC-to-110 VAC converter               | 72  |                                        |          |

| Voltage converter II                       | 74  |                                        | A. IP    |

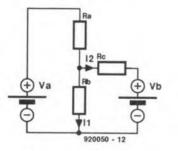

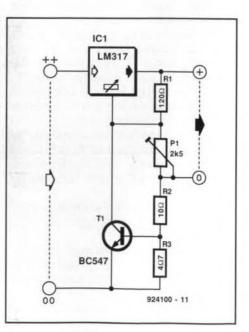

| Current limiting for LM317 regulator       | 74  |                                        |          |

|                                            |     |                                        |          |

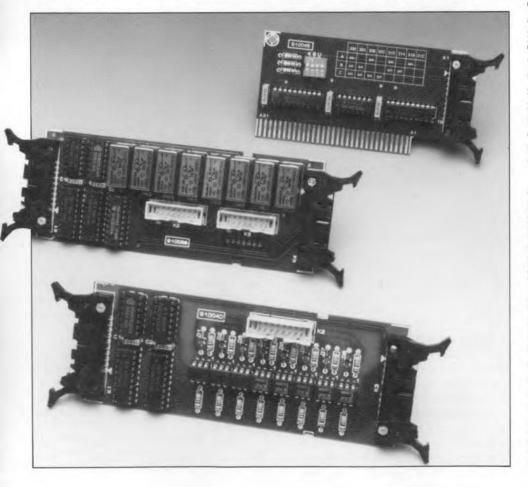

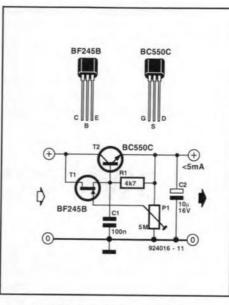

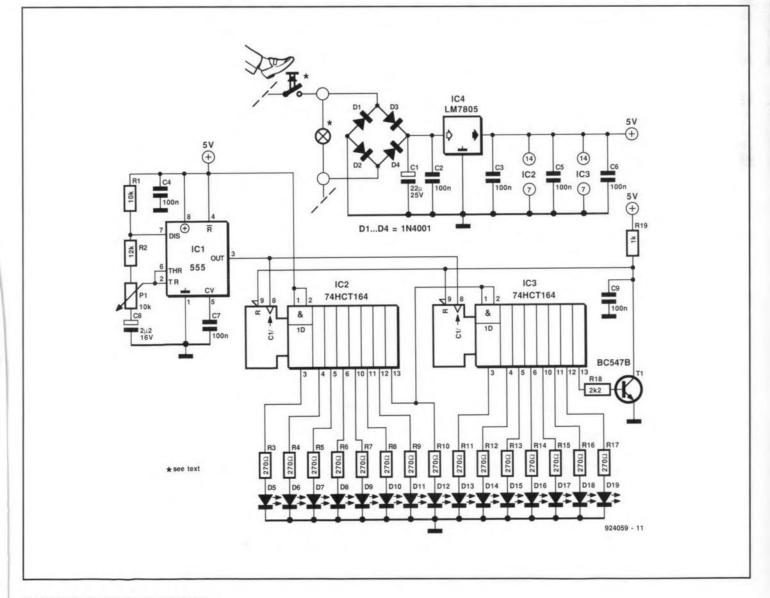

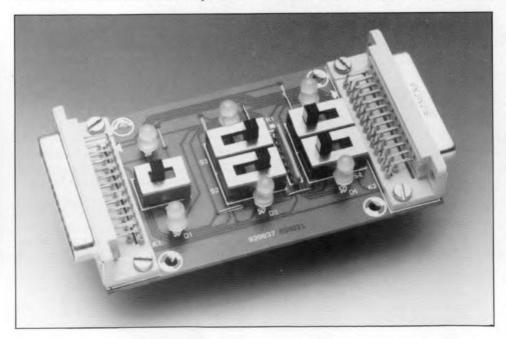

# OPTO CARD FOR UNIVERSAL PC I/O INTERFACE

Whenever an interface is connected to a circuit with a supply voltage higher than 5 V, there is the risk that an error during experimenting, or a faulty component, will cause serious damage to the computer system. The opto card described here has been designed to afford complete electrical isolation between the computer and the (cruel) outside world, which is the only way to prevent system down time and expensive repairs caused by incompatible signal levels.

Design by J. Ruiters

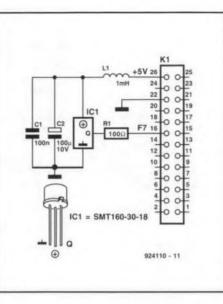

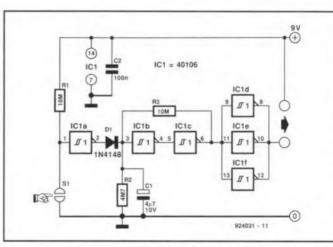

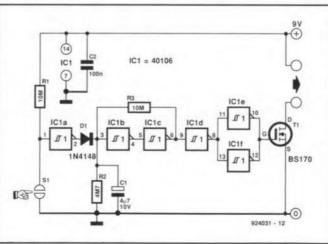

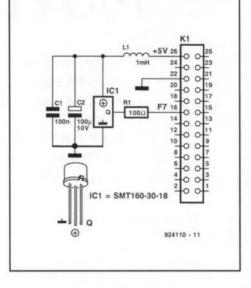

**I**N this article we present the second extension card for the Universal I/O Interface For IBM PCs, described in Ref. 1. While the relay card for this bus (Ref. 2) offers electrically isolated outputs, the present opto card is designed to process input signals in the safest possible way. By the way, the multi-purpose Z80 card described elsewhere in this issue may also be used as a controller for the universal bus.

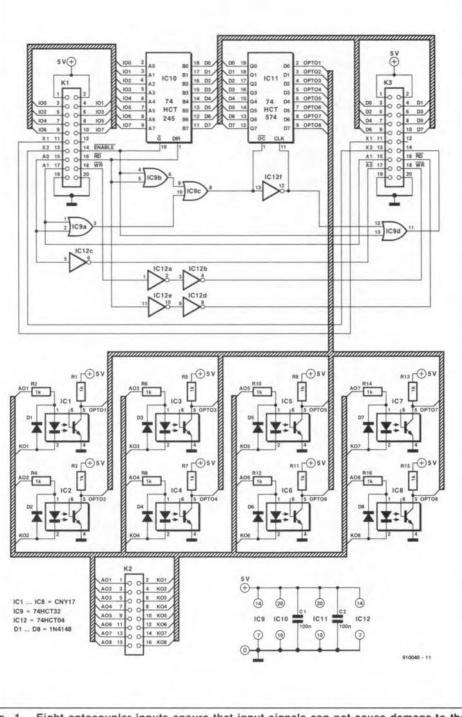

#### Eight optocouplers

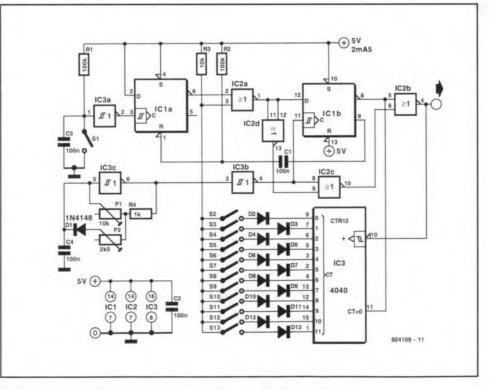

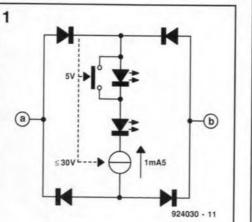

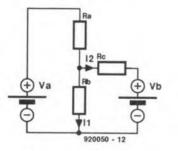

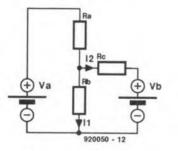

The circuit diagram of the opto card is given in Fig. 1. If you compare it with the circuit diagram of the relay card, you will find quite a few similarities. That is not surprising, because the functions of the two cards are closely related, one being a parallel output device (relay card), the other a parallel input device (opto card). The address decoding

logic, for instance, is identical, consisting of a number of gates and a bidirectional buffer. With reference to Fig. 1, we are talking of IC9, IC10 and IC12. How the card is addressed, that is, how it complies with the rules of extension card addressing that apply in the universal bus system, will be reverted to below.

The opto card is actuated when bus signals A0, A1,  $\overline{\text{RD}}$  and  $\overline{\text{ENABLE}}$  go logic low. Consequently, bus buffer IC10 is enabled, and data is conveyed towards connector K1, i.e., towards the PC. At the same time, the  $\overline{\text{OC}}$  input of data latch IC11 is pulled low, which enables the latch outputs. The data on the databus is clocked into the latches on the negative (falling) edge of the  $\overline{\text{OC}}$  signal. This means that data applied to the optocoupler inputs is captured right at the start of a read cycle of the computer system, which ensures that data is stable on the bus during the actual read operation.

The eightfold optocoupler input circuit is all plain sailing. The only parameters to keep in mind are a couple of maximum specifications. To begin with, the input voltage is limited to 'low voltage' (in most countries, this is defined as 42 V a.c., or 60 V d.c.). This limitation is not caused by the optocouplers, but rather by the printed circuit board and a few other components. When designed to handle the 240 V (110 V) mains voltage at the input, the PCB would have become much larger to meet the relevant safety requirements. A further point to note is the specification of the series resistors with the optocouplers (R2, R4, R6, R8, R10, R12, R14 and R16). The indicated resistors (1 kΩ, 0.25 W) may be used when the input voltage is between 2 V and 15 V d.c. Each optocoupler is protected against reverse voltages by a diode connected in anti-parallel. If voltages greater than 15 V d.c. are applied to the inputs, the

series resistors have to be increased accordingly, or resistors with a higher permissible dissipation must be used. The latter solution is not very elegant because of the larger size and the heat developed. The resistor values are calculated such that the LED current is a few milli-ampères at the given input voltage.

The construction of the opto card is entirely straightforward, and therefore not discussed further.

#### The bus system

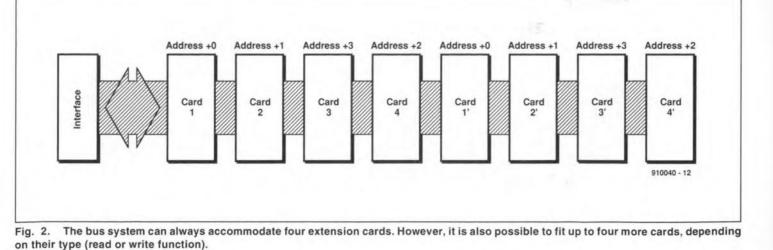

As shown in Fig. 2, the address of any extension card connected to the universal bus system is determined by its position in the chain of extension cards. Unconventionally, DIP switches, jumpers and the like are not used. Apart from the beautifully simple and inexpensive hardware, the advantage of this system is mainly that you can not make address setting errors because there is nothing to set: the card address is determined by its physical position in the system. Note, however, that you must not confuse the bus-IN and bus-OUT connectors. Remember, the incoming A0 signal is inverted on every extension card, and swapped with A1 on the bus-OUT connector. This is done to enable any extension card to be selected when both A0 and A1 are logic low, although the actual address to be supplied by the PC to select a particular card is determined by the number of cards connected ahead of that card.

Those of you who have recalled from the earlier articles that the bus system has only four addresses may be surprised to see eight extension cards in Fig. 2. This is simple to explain. Any bus address can be read from, or written to. In other words, there are four 'read' addresses, and four 'write' addresses, which makes a total of eight. This difference is of no consequence as long as you do not wish to use more than four cards, which can then be chained via linking cables without problems. The difference between reading and writing is not in order until you use more than four cards. Let us assume that you wish to hook up four relay cards and four opto cards. This requires the positions with the same card number, e.g., 1 and 1', to be occupied by one relay card (write only) and one opto card (read only). You can not fit two

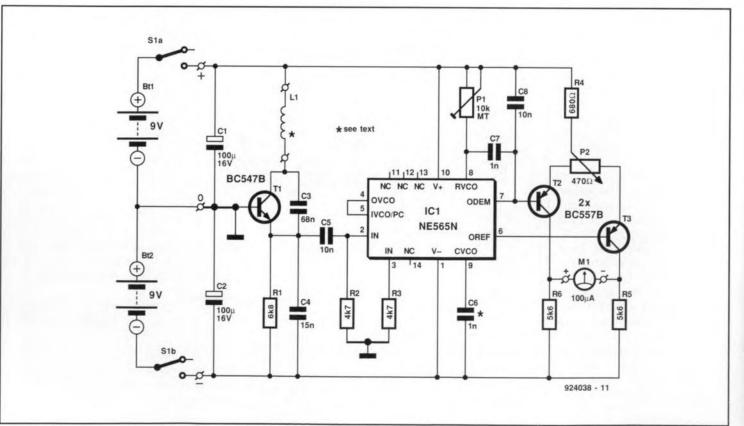

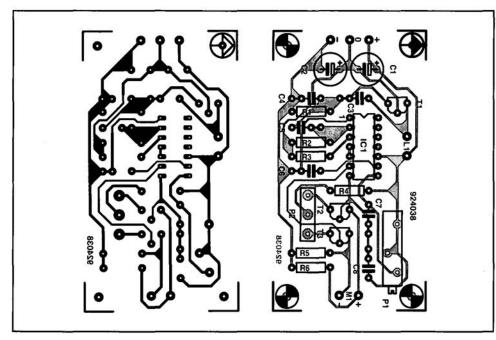

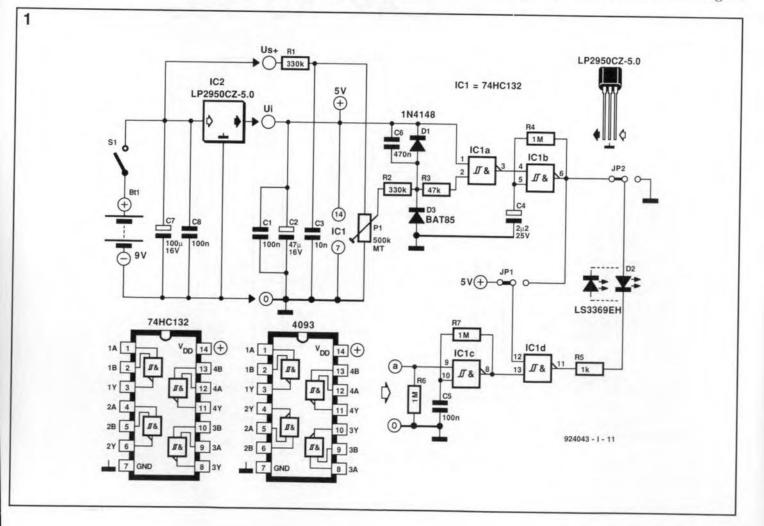

Fig. 1. Eight optocoupler inputs ensure that input signals can not cause damage to the computer.

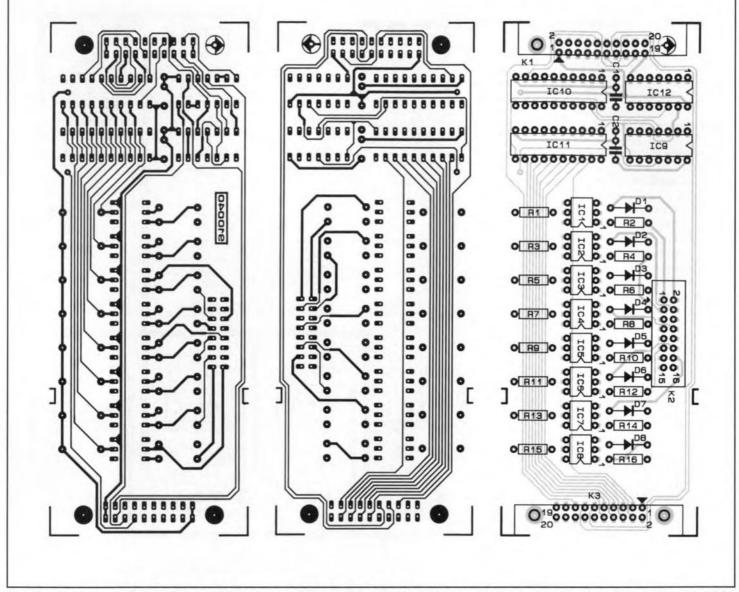

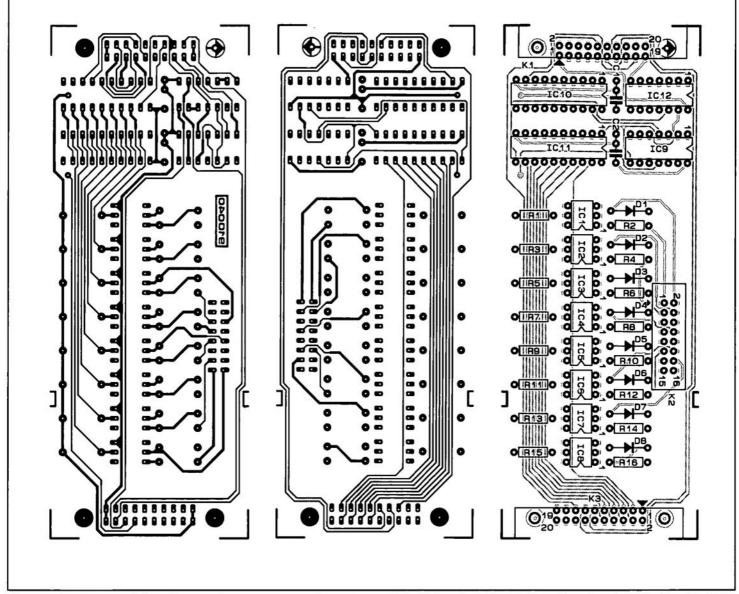

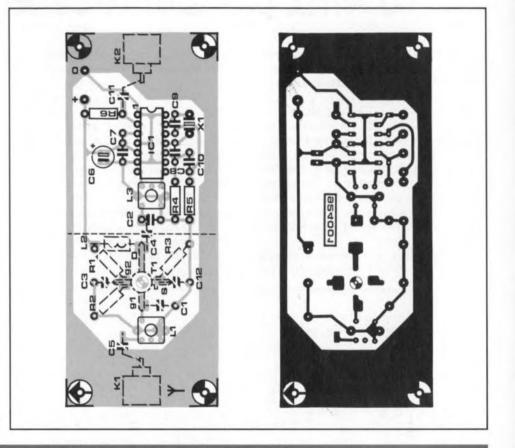

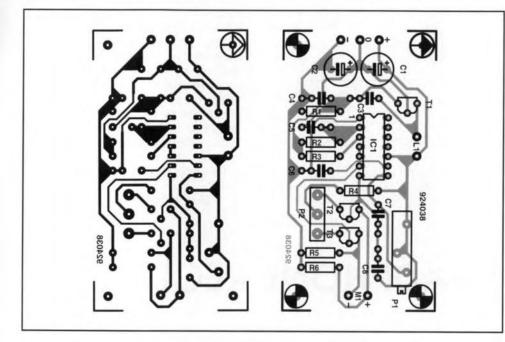

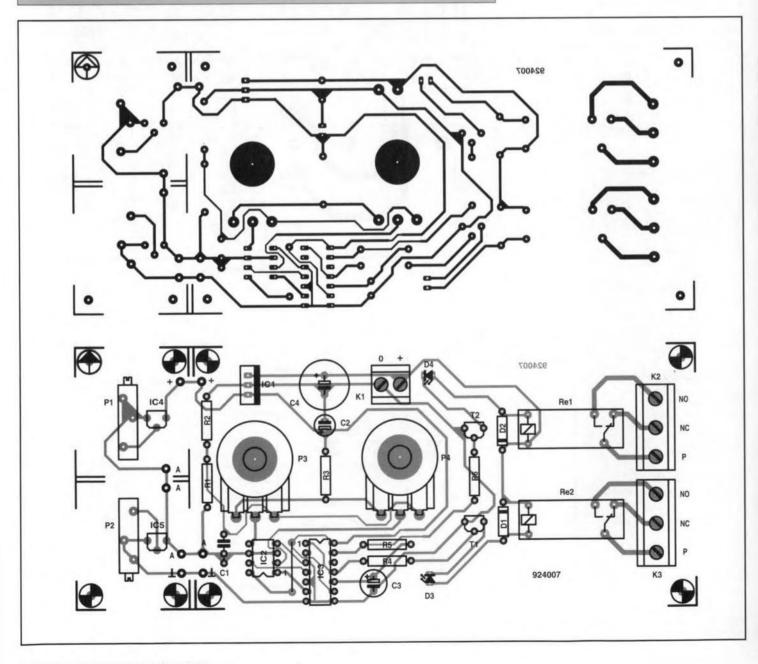

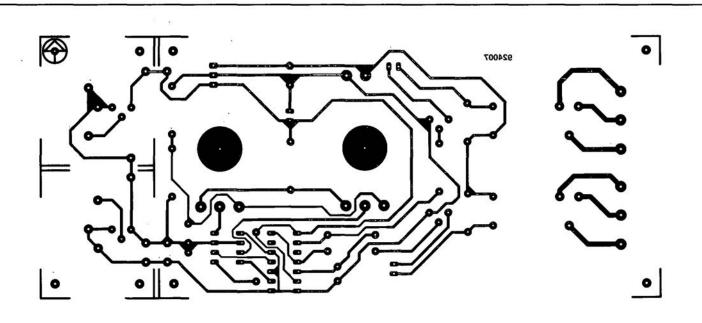

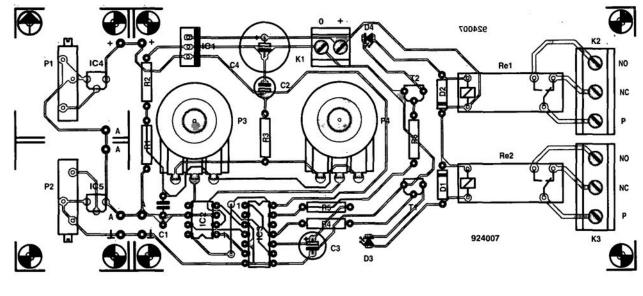

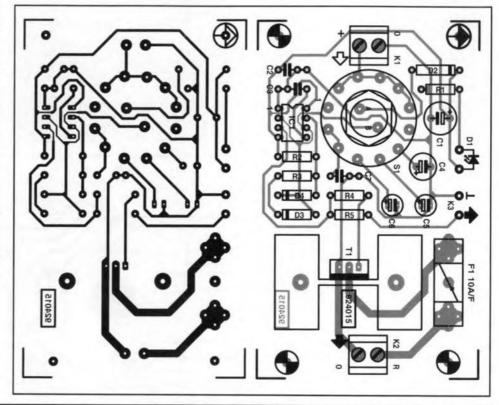

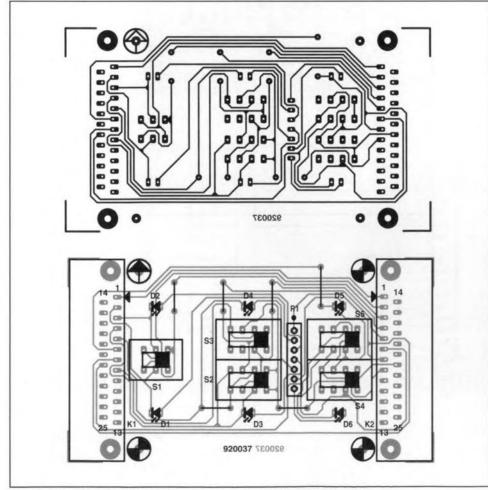

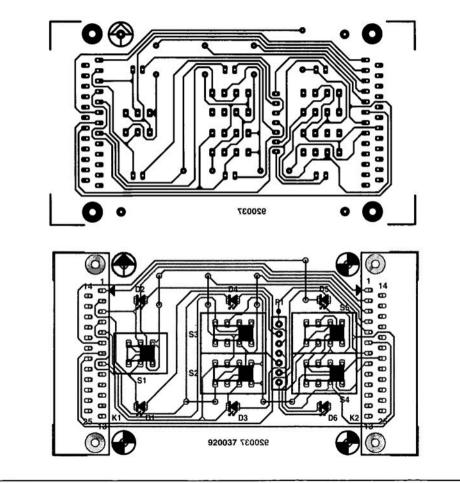

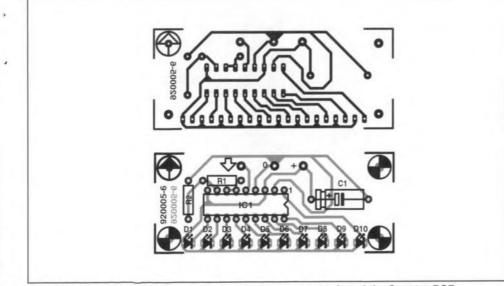

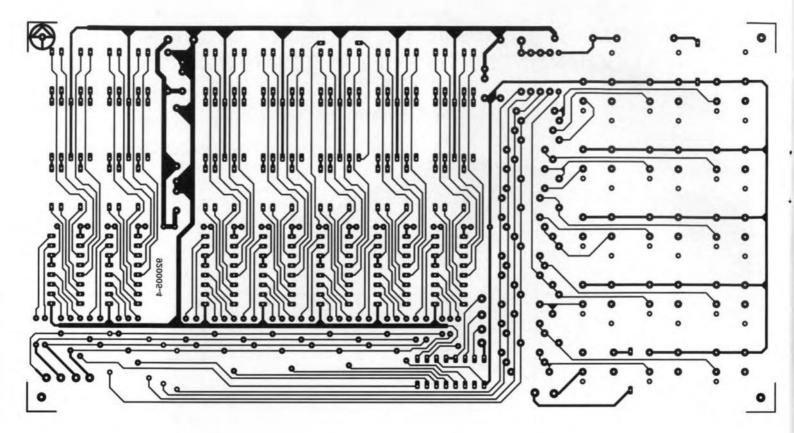

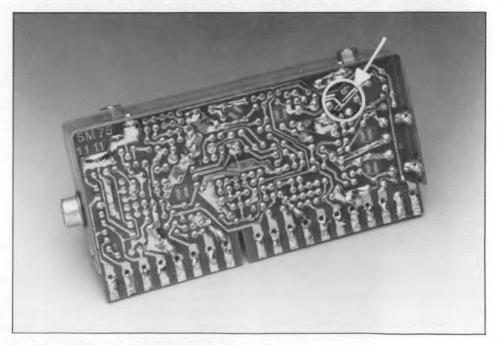

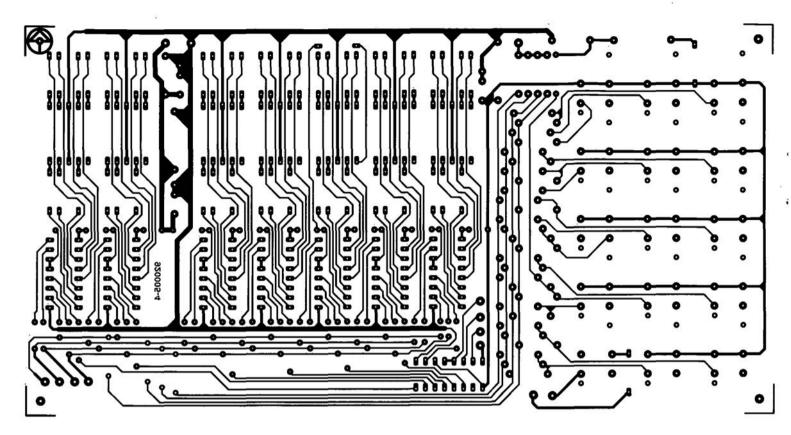

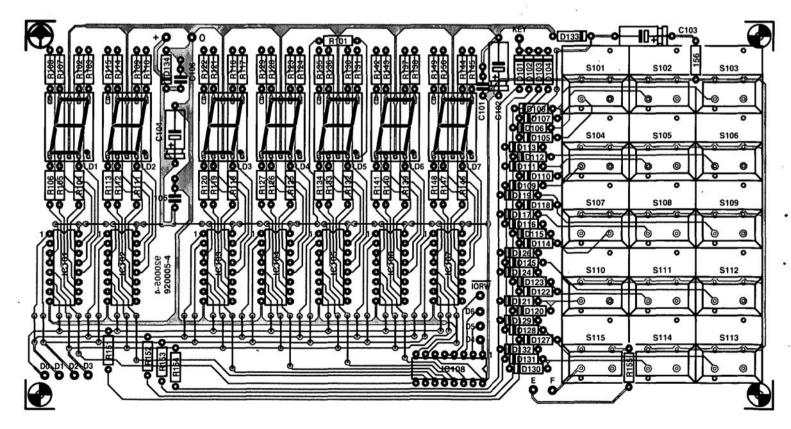

Fig. 3. Track layouts (mirror images of the component side and the solder side) and component mounting plan of the double-sided PCB for the opto interface.

cards with 'write' functions, or two cards with 'read' functions, in a position with the same card number. If you still do so, the computer will forever be unable to 'see' the card with the accented (') number. Fortunately such an 'impossible' connection will not damage the hardware, because the first card addressed in the chain keeps the EN-ABLE signal for the rest of the chain logic high, whereby all other extension cards are disabled.

A different kettle of fish are extension cards with read *and* write functions (we have not published any of these, but you may have ideas ...). Such cards must always be fitted in one of the first four positions, but as far as possible towards the end of the chain. If a 'read/write' card is fitted in position '1', and three relay cards in positions '2', '3' and '4', it would appear that you can not fit an opto card up to position 2'. That will not work, however, since there is first card 1', but that position is blocked by card 1. The upshot is that first four positions must always be occupied by cards that can only be read from or written to. This leaves the next positions available for cards with the double 'read/write' function.

Summarizing the above:

- the address occupied by the card is determined by its physical position in the chain;

- at every address, a distinction is made between reading and writing;

- if an address is used for writing or reading only, the corresponding accented position may be occupied by a card with the complementary function only.

#### **References:**

**1.** "Universal I/O interface for IBM PCs". *Elektor Electronics* May 1991.

2. "Relay card for universal bus". *Elektor Electronics* November 1991.

### COMPONENTS LIST

| Re | sistors:                             |            |

|----|--------------------------------------|------------|

| 16 | 1kΩ                                  | R1-R16     |

| Ca | pacitors:                            |            |

| 2  | 100nF                                | C1;C2      |

| Se | miconductors:                        |            |

| 8  | 1N4148                               | D1-D8      |

| 8  | CNY17                                | IC1-IC8    |

| 1  | 74HCT32                              | IC9        |

| 1  | 74HCT245                             | IC10       |

| 1  | 74HCT574                             | IC11       |

| 1  | 74HCT04                              | IC12       |

| Mi | scellaneous:                         |            |

| 2  | 20-way header w<br>latches, angled F |            |

|    | connections                          | K1;K3      |

| 1  | 16-way box head                      | ler K2     |

| 1  | Transparent plas<br>enclosure Type 2 |            |

| 1  | Printed circuit bo                   | ard 910040 |

Fig. 3. Track layouts (mirror images of the component side and the solder side) and component mounting plan of the double-sided PCB for the opto interface.

cards with 'write' functions, or two cards with 'read' functions, in a position with the same card number. If you still do so, the computer will forever be unable to 'see' the card with the accented (') number. Fortunately such an 'impossible' connection will not damage the hardware, because the first card addressed in the chain keeps the EN-ABLE signal for the rest of the chain logic high, whereby all other extension cards are disabled.

A different kettle of fish are extension cards with read *and* write functions (we have not published any of these, but you may have ideas ...). Such cards must always be fitted in one of the first four positions, but as far as possible towards the end of the chain. If a 'read/write' card is fitted in position '1', and three relay cards in positions '2', '3' and '4', it would appear that you can not fit an opto card up to position 2'. That will not work, however, since there is first card 1', but that position is blocked by card 1. The upshot is that first four positions must always be occupied by cards that can only be read from or written to. This leaves the next positions available for cards with the double 'read/write' function.

- Summarizing the above:

- the address occupied by the card is determined by its physical position in the chain;

- at every address, a distinction is made between reading and writing;

- if an address is used for writing or reading only, the corresponding accented position may be occupied by a card with the complementary function only.

#### **References:**

**1.** "Universal I/O interface for IBM PCs". *Elektor Electronics* May 1991.

2. "Relay card for universal bus". *Elektor Electronics* November 1991.

### COMPONENTS LIST

| Re | sistors:                                    |          |

|----|---------------------------------------------|----------|

| 16 | 1kΩ                                         | R1-R16   |

| Ca | pacitors:                                   |          |

| 2  | 100nF                                       | C1;C2    |

| Se | miconductors:                               |          |

| 8  | 1N4148                                      | D1-D8    |

| 8  | CNY17                                       | IC1-IC8  |

| 1  | 74HCT32                                     | IC9      |

| 1  | 74HCT245                                    | IC10     |

| 1  | 74HCT574                                    | IC11     |

| 1  | 74HCT04                                     | IC12     |

| Mi | scellaneous:                                |          |

| 2  | 20-way header with s<br>latches, angled PCB | side     |

|    | connections                                 | K1;K3    |

| 1  | 16-way box header                           | K2       |

| 1  | Transparent plastic<br>enclosure Type 222 ( | (Heddic) |

| 1  | Printed circuit board                       | 910040   |

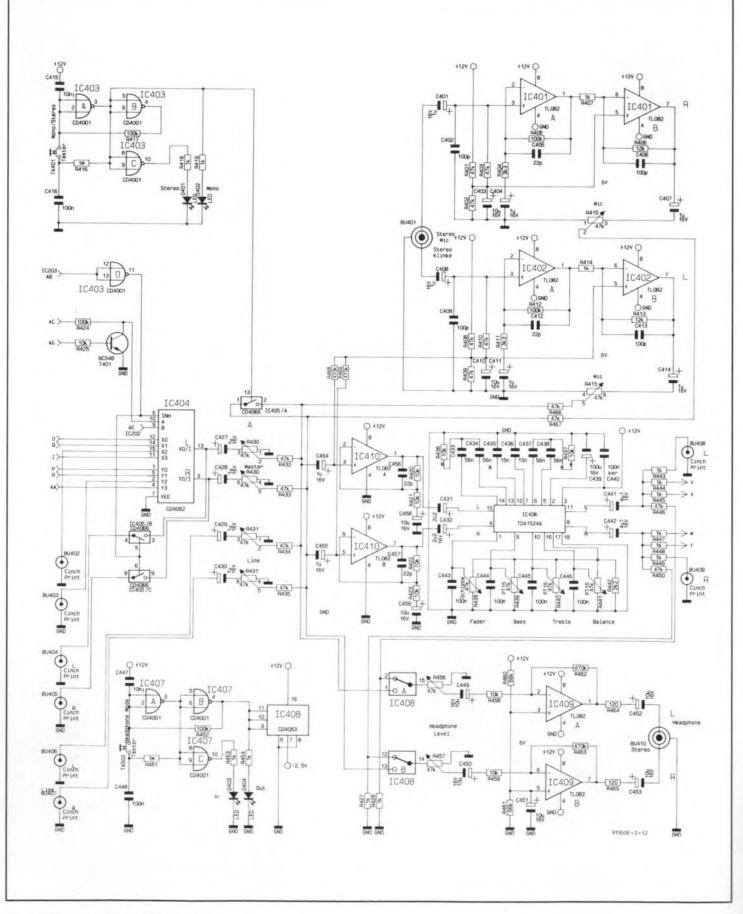

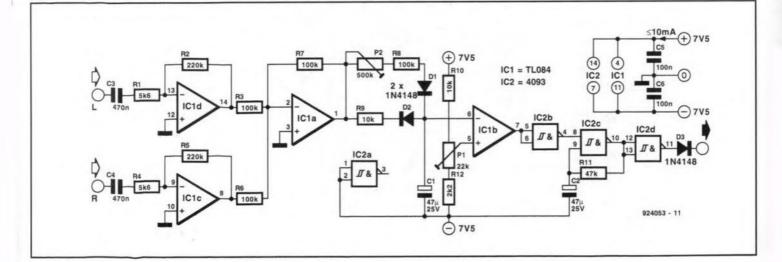

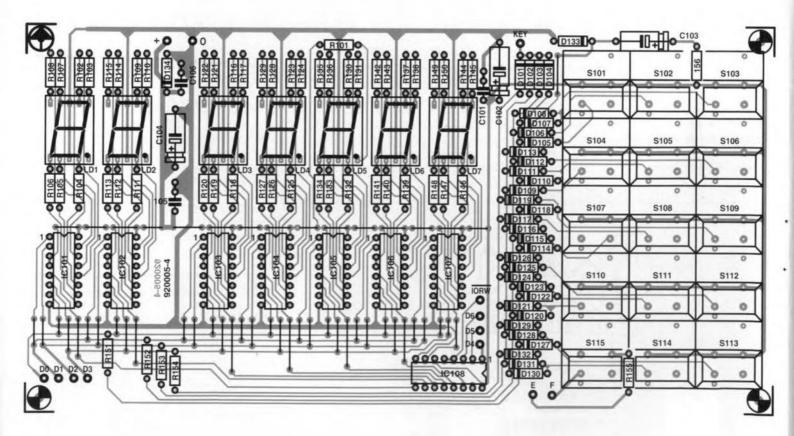

# AUDIO-VIDEO PROCESSOR TYPE AVP300 – PART 3

#### An ELV design

### Synchronization circuit

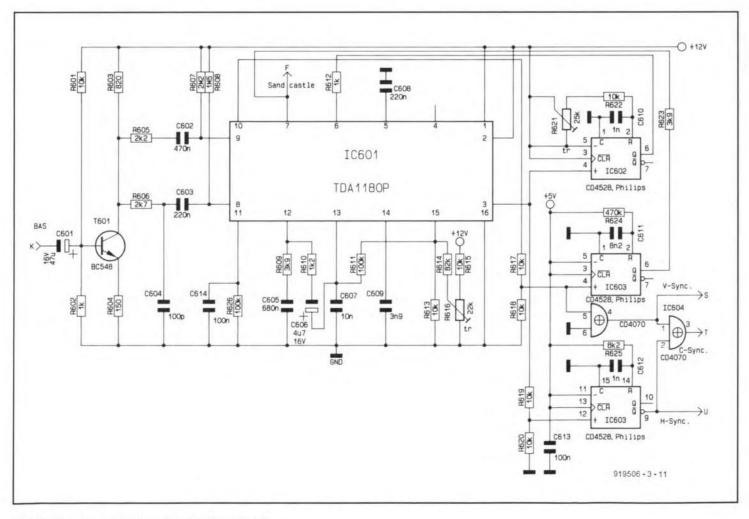

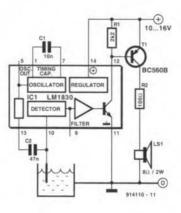

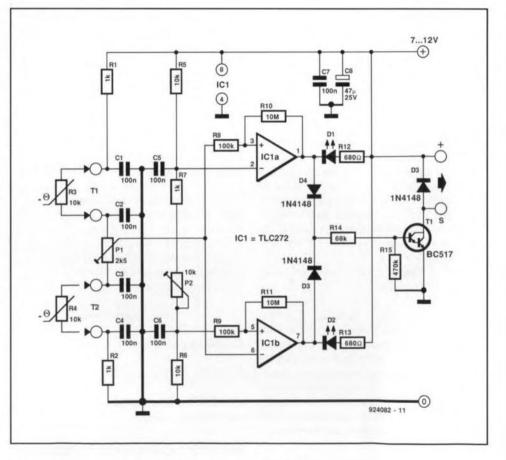

THE signals in a number of circuits of the processor must be matched to the input signal to prevent a wandering or distorted picture. The circuit responsible for this is the sync(hronization) circuit, whose diagram is shown in Fig. 6.

The sync circuit is based on sync separator IC<sub>601</sub>. This circuit is fed with the VBS signal via  $T_{601}$  and provides three output signals: a sandcastle pulse at pin 7; a square wave at pin 3, whose first transition (leading edge) determines the onset of the horizontal sync pulse; and the vertical sync pulse at pin 10.

The signals at pin 3 and pin 7 are not yet suitable for further use. The sandcastle pulse contains as yet no information on the vertical blanking that is essential for colour demodulator  $IC_{101}$  (Fig. 4). Also, a signal that merely determines the onset of the horizontal sync pulse is not enough for further processing of the video signal. To make it into a

#### true sync signal, a fly-back pulse is required. In fact, three pulses are needed: a horizontal and a vertical blanking pulse ( $12\mu$ s and 1.9 ms respectively) and a horizontal sync pulse of 4.7 $\mu$ s. These pulses are generated by mono-

stables  $IC_{602}$ ,  $IC_{603a}$  and  $IC_{603b}$  respectively. The horizontal blanking pulse generated by  $IC_{603a}$  (pin 6) is superimposed on to the sandcastle pulse via  $R_{623}$ . The modified sandcastle pulse has exactly the right shape to ensure correct functioning of  $IC_{101}$ .

The reason for  $IC_{602}$  being fed directly by the sync separator, whereas both  $IC_{603a}$  and  $IC_{603b}$  are fed via potential dividers, is that  $IC_{602}$  operates from the 12 V supply line and the other two from the 5 V line.

Gate  $IC_{604b}$  combines the horizontal and vertical blanking pulses into a composite sync signal. Note that the vertical blanking pulse is applied to the gate via XOR gate  $IC_{604a}$ , because this signal is difficult to load owing to the impedance  $R_{617}$ - $R_{618}$ .

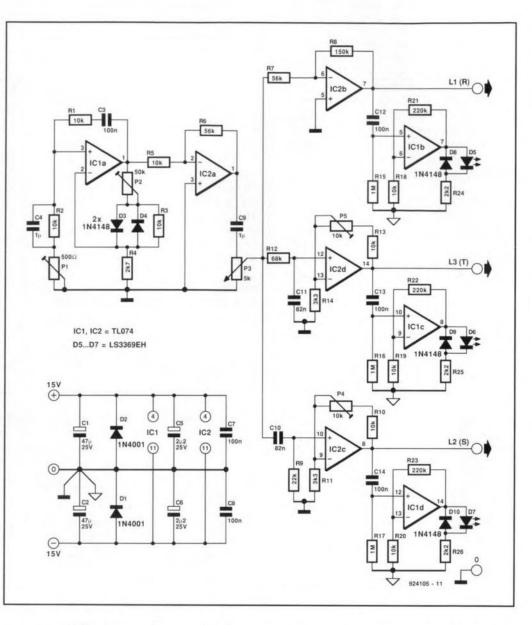

### Audio frequency circuits

To enable background music or a commentary to be added to the audio signal, the processor is equipped with a mixer and tone control.

The input of the audio circuits shown in Fig. 7 enables up to three signals to be mixed: the audio signal associated with the selected video source (master), a randomly selected audio signal (line) and a signal from a stereo microphone.

Selection of the master signal is facilitated by an input selector switch, consisting of analogue multiplexer IC<sub>404</sub>, and two electronic switches, IC<sub>405b</sub> and IC<sub>405c</sub>. The multiplexer selects four of the five possible audio signals, while the electronic switches take care of the fifth. Three audio signals are available from the SCART connectors in Fig. 3 and connector BU<sub>301</sub> in Fig. 5. The other two arrive from the S-VHS connector and the BNC socket.

#### Fig. 6. Diagram of the synchronization circuit.

The line signal at sockets  $BU_{406}$  and  $BU_{407}$  is connected directly to the line control potentiometers on the mixer.

The level of the microphone signal is well below that of the line and master signals and is, therefore, amplified in IC<sub>401</sub> (left-hand) and IC<sub>402</sub> (right-hand).

The mixer consists of three linear stereo slide potentiometers, whose wipers are connected to the relevant left-hand or right-hand line via a summing resistor. The use of linear potentiometers may not seem right, but their wipers are loaded by the summing resistors in a manner that results in traditional logarithmic volume control.

Since not many video signals carry stereo sound, the audio circuit can be switched to mono by closing electronic switch IC<sub>405a</sub>,

Fig. 7. Diagram of the audio circuits.

which is controlled with switch  $TA_{401}$  and a bistable,  $IC_{403}$ . The left-hand and right-hand signals from the mixer are then interconnected; their sum is seen by the remainder of the circuit as a mono signal.

The signal is then applied to two non-inverting opamps,  $IC_{410a}$  and  $IC_{410b}$  and from these to control amplifier  $IC_{406}$ . The control amplifier enables the volume, bass and treble, and the balance to be adjusted. The control range of the bass frequencies can be enlarged by using R<sub>436</sub>, R<sub>437</sub>, C<sub>434</sub> and C<sub>438</sub> (marked with an asterisk). Without these components, the bass range is the traditional  $\pm 20$  dB. The output of  $IC_{406}$  is available at output sockets  $BU_{408}$  and  $BU_{409}$ .

The headphone amplifier enables the signal before and after the control amplifier to be listened to, depending on the position of electronic switches  $IC_{408a}$  and  $IC_{408b}$ . These switches are controlled by push button  $TA_{502}$ and the circuit based on  $IC_{407}$ . The signals from the two sections of  $IC_{408}$  are applied to potentiometers  $R_{456}$  and  $R_{457}$ , with which the volume and balance of the signal to the headphones can be adjusted. The signal to the headphone is amplified in dual opamp  $IC_{409}$ .

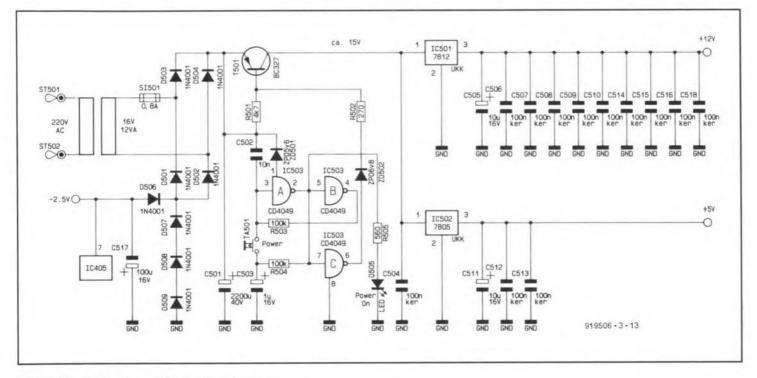

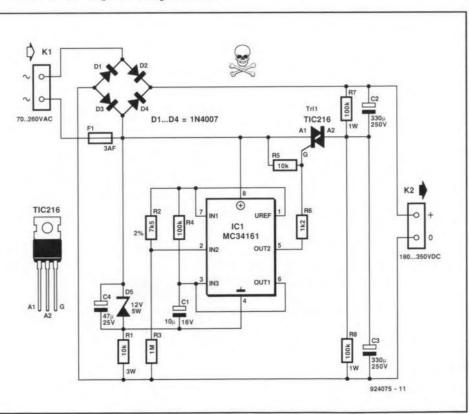

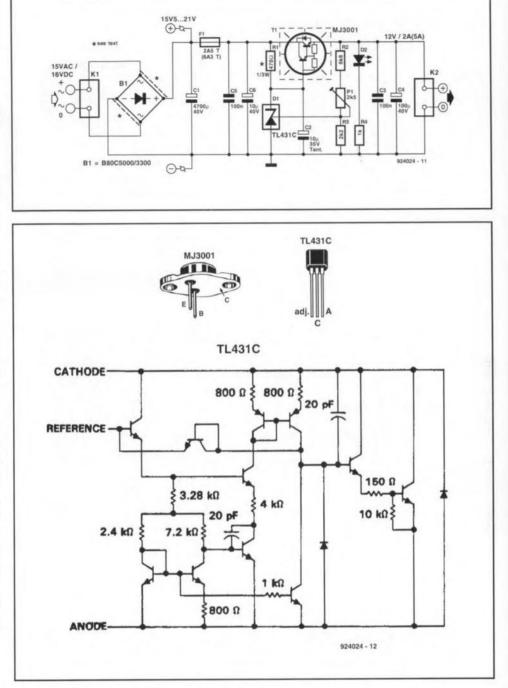

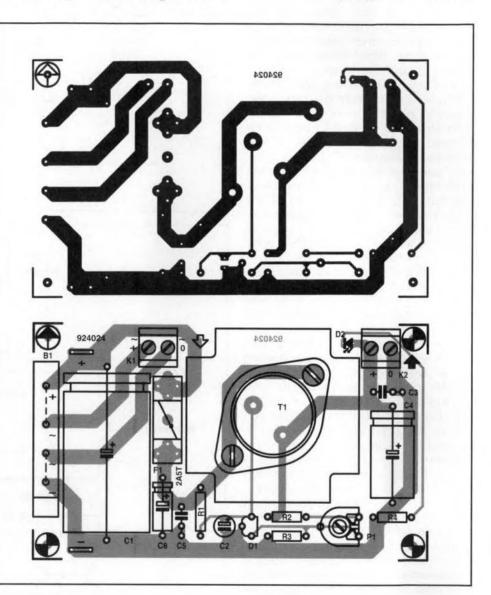

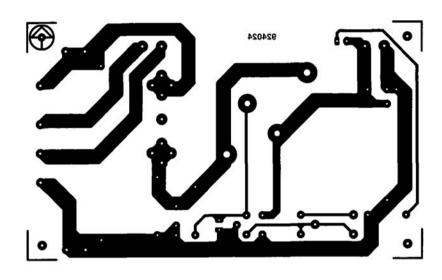

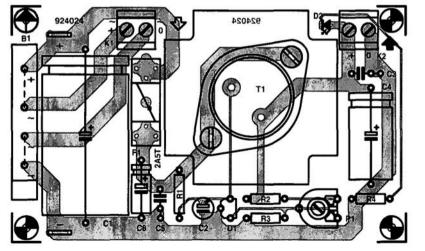

### Power supply

The circuit of the mains-operated power supply is shown in Fig. 8. The rectifier may look unfamiliar, but it is a straightforward bridge, whose negative connection is not directly to earth, but via three diodes. The drop across these diodes is used as an auxiliary negative supply (–2.5 V) for electronic switches  $IC_{405}$ and  $IC_{408}$ . Transistor  $T_{501}$  serves as the on/off control; it is operated by push button  $TA_{501}$  and the circuit based on  $IC_{503}$ . That IC is fed by the potential across  $C_{501}$  to ensure that it can always be powered. That voltage is too high, however, and it is, therefore, lowered by zener diode  $ZD_{501}$ . The output of  $IC_{503c}$  is additionally protected against too high voltages by zener diode  $ZD_{502}$ .

The circuit following switching transistor  $T_{501}$  is traditional: two three-terminal regulators ensure stable output voltages of 5 V and 12 V. The capacitors following the regulators are decoupling devices used at miscellaneous positions in the circuits.

The next and final instalment, dealing with the construction and calibration, will appear in our September issue (there is no August issue).

Fig. 8. Circuit diagram of the power supply.

# DEALING WITH NOISE AND INTERFERENCE IN ELECTRONIC INSTRUMENTATION CIRCUITS

# SHIELDING, FILTERING AND USING LOW NOISE AMPLIFIERS

Many electronic instrumentation and data acquisition circuits must deal with low-level signals in the presence of strong interfering signals. If the signal level is small enough, even the noise produced by amplifiers and passive components can obscure the desired signal. In this article we will look at several strategies for solving problems with low signal level amplifier systems. These techniques include use of a low noise amplifier (LNA), filtering, circuit shielding, input leads shielding (including professional quard shielding techniques) and isolation of the circuit from the power mains.

20

By Joseph J. Carr

### Noise, etc.

Noise can be defined as any unwanted signal, even though a somewhat narrower definition is sometimes sought in textbook treatments of the subject. But in the context of this article, *noise* can mean the internal 'hiss-like' noise generated in any amplifier, the atmospheric noise in radio receivers, 50 or 60 Hz hum picked up from the power mains, and interference from nearby sources of electromagnetic radiation (e.g., radio stations or other RF devices). Noise signals mix with, and either distorts or obscures the desired signals.

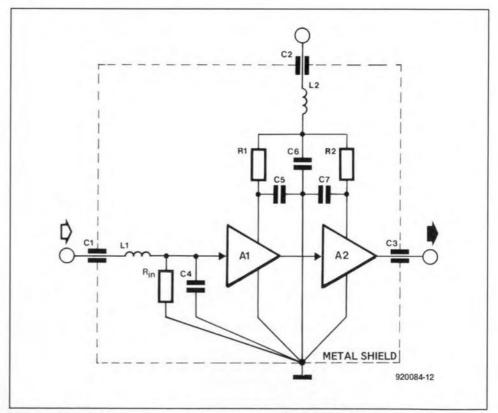

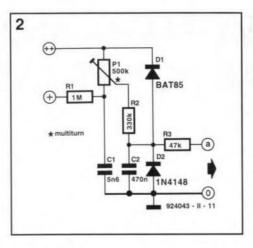

Fig. 2. Generic electronic circuit showing use of shielding and filtering to eliminate noise interference.

Several different forms of noise signal can be recognized: white noise, impulse noise and interference noise.

White noise supposedly contains all possible frequencies, so gets its name from analogy to white light, which contains all colours. Such noise is also called *gaussian noise*, although in reality it is neither 'white' nor 'gaussian' unless there are no bandwidth limits placed on the system. True white noise has a bandwidth from d.c. to daylight, and beyond. In practical electronic circuits, however, there are bandwidth limitations, so the noise is actually pseudo-gaussian 'pink' or even 'orange' noise. True gaussian noise can be eliminated absolutely by low-pass filtering, because it by nature integrates to zero, given sufficient time. Bandwidth-limited noise, however, does not integrate to zero, but to a low value. The effect of low-pass filtering on pink noise is therefore not total reduction.

An analogy to pseudo-gaussian or pink

noise is the 'hiss' heard between stations on an FM broadcast band receiver. Much of the noise in instrumentation systems is due to thermal sources, and has an RMS value of:

$$U_{\rm n} = \sqrt{4 \, K \, T \, B \, R} \tag{1}$$

Where:

$U_{\rm n}$  is the noise signal in volts (V); K is Boltzmann's constant (1.38 × 10<sup>-23</sup> joules per Kelvin);

T is the temperature in Kelvin (K);

*B* is the bandwidth in hertz (Hz);

R is the circuit resistance in ohms ( $\Omega$ ).

Noise can be generated in a passive component such as a resistor by virtue of its resistance. According to Eq. (1), in a circuit with a 1,000 Hz bandwidth and a resistance of 100 k $\Omega$ , there is 0.6 microvolts (µV) of noise created by molecular motion due to temperature. Although this signal may appear to have a very low amplitude, keep in mind that many signals found in practical systems have the same order of magnitude. For example, in medical electronics, the electroencephalograph (EEG) machine records minute scalp potentials generated by the human brain's electrical activity, and may have components as low as 1 to 2 µV, with peak amplitudes in the 10 to 100 µV range. In that application, 0.6 µV represents a significant artifact, especially when amplified 5,000 to 10,000 times, as is common practice in EEG machines.

Part of the solution to this type of problem is to keep circuit impedances in the early stages — i.e., those stages that most of the gain follows — very low so that the resistance term in Eq. (1) is reduced to a minimum practical value. Additionally,

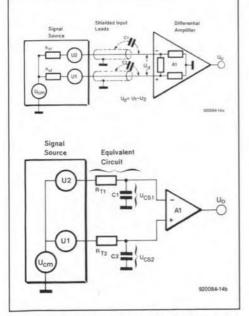

Fig. 4. a) Typical circuit for a differential input amplifier circuit showing sources of resistance and capacitance in the circuit; b) equivalent circuit.

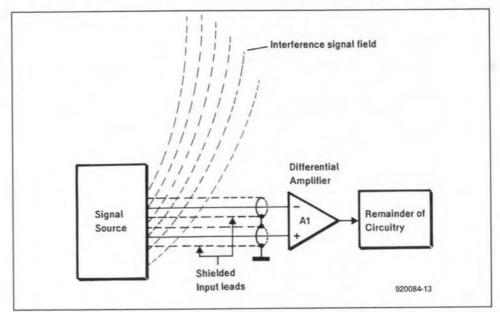

Fig. 3. Generic instrument using a signal source and differential input amplifier. The shielding prevents external interference signal fields from invading the circuit — or does it?

low-pass filtering, bandpass filtering or other methods might be employed to keep the bandwidth term low.

There are several sources of noise that are peculiar to solid-state amplifiers: *shot noise*, *Johnson noise*, and *flicker noise*. In some amplifiers these noise sources can add up to a significant amplitude. Although low-pass filtering offers relief, it is better to specify a low-noise amplifier for the earliest stages in the system.

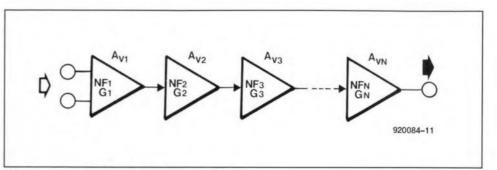

Friis' equation uses the noise factors (i.e. ratio of input to output signal-to-noise ratio) to show us that low noise amplifiers in the input stages provide most of the noise relief for the entire system. It is for this reason that satellite communications or TV earth stations use Low Noise Amplifiers (LNA) as preamplifiers on the dish antenna. Similarly, analogue instrumentation and data acquisition amplifiers use a single LNA in the front-end, and then ordinary amplifiers throughout the rest of the circuit. The Friis equation for a cascade chain of amplifiers such as Fig. 1 is:

$$NF_{\text{total}} = NF_1 + \frac{NF_2 - 1}{G_1} + \frac{NF_3 - 1}{G_1}G_1 + \frac{NF_n - 1}{G_1G_2G_3 + G(N - 1)}$$

(2)

Where:

*NF*<sub>total</sub> is the noise factor of the entire cascade chain;

$NF_1$ ,  $NF_2$ , etc. are the noise factors of the individual stages;

$G_1$ ,  $G_2$ , etc. are the gains of the individual stages.

Thus, we can use a single, usually premium low noise amplifier device for the first stage, and regular amplifiers for all others.

Low noise operational amplifiers are a good choice, but are sometimes rather expensive. A low cost alternative for many uses is the CA3130, CA3140 or CA3160 device in the 8-pin metal can package (not the mini-DIP!). Use a flexible heatsink of the type used for TO-5 metal transistor packages on the op-amp package, and operate the device from  $\pm 5$  V dual polarity d.c. power supplies. This treatment (heatsinks and low power supply voltages) will mimic low-noise operation.

21

#### Other noise problems

Impulse noise is due to local electrical disturbances such as arcs, lightning bolts, electrical motors and so forth. Part of this same general type is general electromagnetic interference (EMI) problems. Such interference is usually caused by nearby radio transmitters, or other RF sources. It is not usually possible to force the transmitter off the air, even when it is an amateur operator, because they are licensed by the Government to be there ... while you are not.

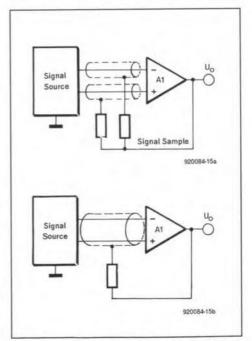

Fig. 5. a) Simple guard shield drive circuit for twin shields; b) same circuit for single shield circuits.

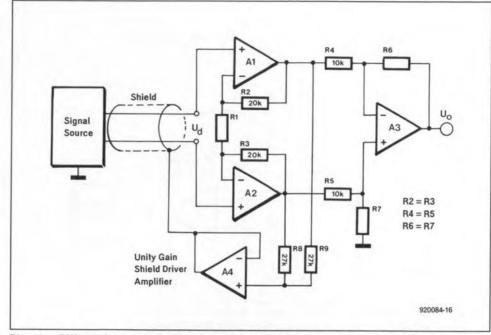

Fig. 6. Differential instrumentation amplifier, based on operational amplifiers, using an active guard shield driver (amplifier A4).

From an engineering point of view, your equipment might be very expensive and quite good, and still be very poor from an EMI point of view. The purpose of any electronic equipment is twofold: a) it must respond to proper signals, and b) it must reject improper signals. It is point 'b)' where most improperly designed equipment fails most significantly.

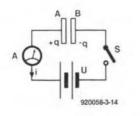

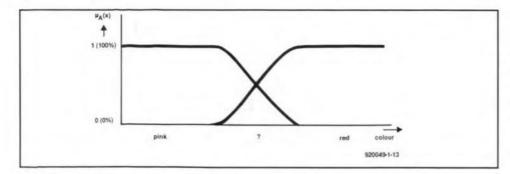

Shielding and filtering of signal lines is the key to EMI problems. Figure 2 shows a generic circuit with several of the possible correction types used. First, note that the entire instrument is built inside of a shielded metal box, and the box is grounded. Points of entry and exit are passed through feedthrough 'EMI filter' capacitors. Feedthrough capacitors C1 through C3 have values of 50 pF to 2 nF (0.002 µF), depending on the circuit impedance and which capacitor is specified. For example, the signal line capacitors C1 and C3 will have smaller values, while power supply capacitor C2 should be larger than 1 nF (0.001 µF).

Each stage in Fig. 2 is isolated from other stages by a resistor, and has its own decoupling capacitor (C5 and C7). The main power bus is decoupled (C6), and has a series radio frequency choke (L2) to prevent RF that gets past C2 from interfering with the operation of the circuit. The input leads are similarly filtered with L1 and C4. The input resistance  $(R_{in})$  of the amplifier and capacitor C4 also form a low-pass filter with a frequency response that rolls off at a -3 dB/octave rate from the -3 dB point defined by:

$$F = \frac{1}{2 \pi R_{\rm in} C_4} \tag{3}$$

Where: F is the frequency in hertz (Hz)  $C_4$  is in farads (F)  $R_{in}$  is in ohms ( $\Omega$ )

Not all of the techniques of Fig. 2 are needed, or even appropriate, in all circuits. Their inclusion was meant to show the

Dual shielding combines twin-shield and single shield concepts.

possibilities, rather than form a recommendation for all applications. Select those that are appropriate, or practical, for your particular application.

# Suppressing local interfering signals

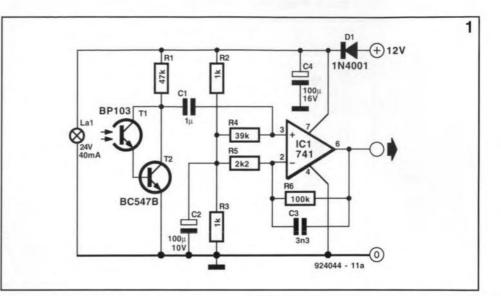

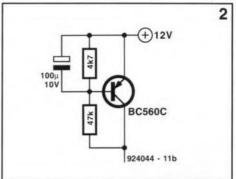

Local interfering signals are created by other electrical devices close to the circuit being operated, and by the 50/60 Hz electrical power mains in the building. Consider Fig. 3, where a low-level signal source is connected to an amplifier at the input of a larger circuit. The signal source might be a sensor such as a Wheatstone bridge strain gauge, an electro-optical detector. Alternatively, it may be a biopotential such as the EEG brain wave signal or electrocardiograph (EEG) heart signal. The common factor shared by these signals is that they produce low level signals, and often must operate in a high interference environment.

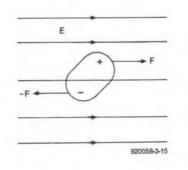

A common solution to these problems is to use a differential amplifier at the input of the circuit. One of the properties of the differential amplifier is that its common mode rejection ratio (CMRR) tends to suppress interfering signals from the environment. It does this job because the inverting (-) and non-inverting (+) inputs offer equal gain, but are of opposite polarity. If identical signals are applied to the two inputs simultaneously, the net output voltage will be zero.

When a differential amplifier is used in a situation where it is connected to an external signal source through wires, those wires are subjected to strong local signals such as the 50/60 Hz a.c. fields from nearby power line wiring. Fortunately, in the case of the differential amplifier the field affects both signal equally, so the induced interfering signal is canceled out by the common mode rejection property of the amplifier.

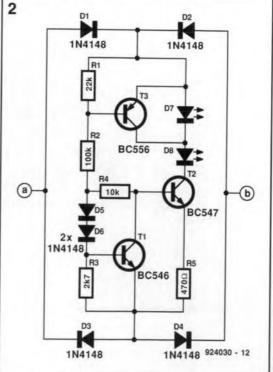

# Guard shielding

Unfortunately, the cancellation of interfering signals by the input amplifier CMRR is not total. There may be, for example, imbalances in the circuit that tend to deteriorate the CMRR of the amplifier. These imbalances may be either internal or external to the amplifier circuit. Figure 4a shows a common sensor interface scenario, similar to Fig. 3: a differential amplifier connected to shielded leads from the signal source,  $U_{in}$ . Shielded lead wires offer some protection from local fields, but there is a problem with the standard wisdom regarding shields: it is possible for shielded cables to manufacture a valid differential, but erroneous, signal voltage from a common mode signal!

Figure 4b shows an equivalent circuit that demonstrates how a shielded cable pair can create a differential signal from a common mode signal. The cable has capacitance between the centre conductor and the shield conductor surrounding it. In addition, input connectors and the amplifier equipment internal wiring also exhibits capacitance. These capacitances are lumped together in the model of Fig. 4b as C1 and C2.

There are also resistances in the circuit. The signal source resistances  $R_{S1}$  and  $R_{S2}$  are generally low, but in some cases (e.g., EEG, ECG, pH electrodes, optoelectronic sensors, etc.) they may be quite high. In addition, there are also input impedances, both differential and unbalanced to ground (see Fig. 4a).

As long as the sum circuit resistances are equal, and the two capacitances are equal, there is no problem with circuit balance. But inequalities in any of these factors (which are commonplace) creates an unbalanced circuit in which common mode signal  $U_{\rm cm}$  can charge one capacitance more than the other. As a result, the difference between the capacitance voltages,  $U_{\rm CS1}$  and  $U_{\rm CS2}$ , is seen as a valid differential signal by the amplifier.

A low-cost solution to the problem of shield-induced artifact signals is shown in Fig. 5a. In this circuit, a sample of the two input signals are fed back to the shield, which in this situation is not grounded. This type of shield is called a *guard shield* circuit. Either double shields (one on each input line) as shown in Fig. 5a or a common shield for the two inputs as in Fig. 5b, can be used.

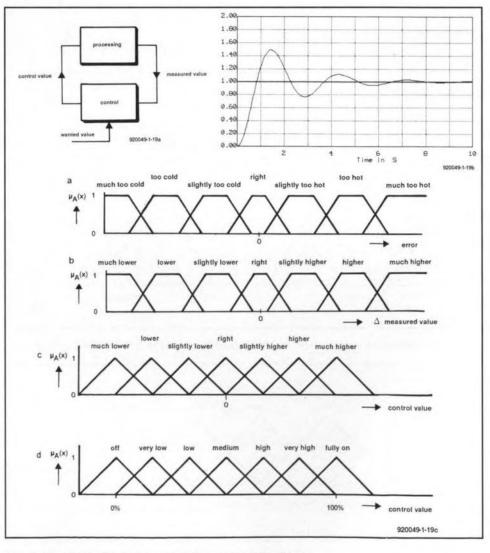

An example of guard shielding for the standard three op-amp instrumentation amplifier, a very common differential frontend for electronic instrument circuits, is shown in Fig. 6. The instrumentation amplifier consists of A<sub>1</sub>, A<sub>2</sub> and A<sub>3</sub>, with associated resistors. If R<sub>2</sub>=R<sub>3</sub>, R<sub>4</sub>=R<sub>5</sub> and R<sub>6</sub>=R<sub>7</sub>, the voltage gain of the circuit is given by:

$$A_{\rm v} = \left(\frac{40k\Omega}{R1} + 1\right) \left(\frac{R6}{10k\Omega}\right) \tag{4}$$

(All resistance in kilo-ohms)

In Fig. 6, the gain can be set by selecting values for R1 and R6, which implies also a value for R7 (which is equal to R6). Variable gain control is provided by making R1 variable. Keep R1 away from zero ohms, however, or the gain will get very high very quickly.

In the circuit of Fig. 6, a single shield covers both input signal lines, but it is possible to use separate shields. In this circuit a sample of the two input signals is taken from the junction of resistors R8 and R9, and fed to the input of a unity gain buffer/driver 'guard amplifier' (A4). The output of A4 is used to drive the guard shield.

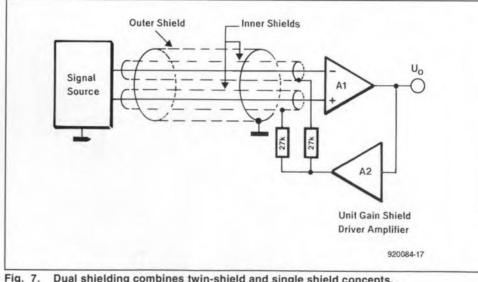

Perhaps the most common approach to guard shielding is the arrangement shown in Fig. 7. Here we see two shields used: the input cabling is double-shielded insulated wire. The guard amplifier drives the inner

Fig. 8. Shielded LC EMI filter for the a.c. power mains (wiring shown common in North America).

shield, which serves as the guard shield for the system. The outer shield is grounded at the input end in the normal manner, and serves as an electromagnetic interference suppression shield.

#### Power line noise

Another potential source of interference is noise and EMI signals arriving on the a.c. power mains. I can recall digital instrumentation and computers in a medical school building that acted in a schizophrenic manner until it was identified that the a.c. power mains were the source of the problem.

A humorous event while this problem existed came about when the medical (M.D.) and medical sciences (Ph.D and D.Sc) students took the standard multiple choice national examination in human physiology. They used a 'mark-sense' answer sheet on which they use a pencil to darken the letter corresponding to the printed candidate answer they believe is correct. These papers were then taken to an optical scanner that input the answers to a computer. While the scanning was going on one year, some ac power line switching equipment started operating, sending high voltage transients over the mains. The result was that the entire freshman class of medical and sciences students flunked the national exam!

Where sensitive scientific instruments are used, one might want to consider designing the ac electrical power mains system to be either isolated from the building system, or having a separate system that keeps a separated neutral and ground conductor all the way back to the service entrance of the building.

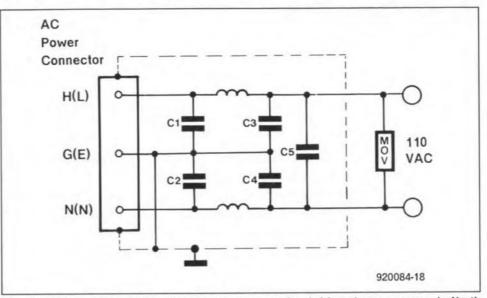

Figures 8 and 9 show methods for dealing with severe power mains noise. In Fig. 8 we see an L-C power line filter wired in the North American standard manner. These filters are shielded low-pass filters, and are mounted inside of equipment as close as possible to the point where a.c. enters the cabinet. Some filters are available molded into the a.c. chassis connector. Exterior to the filter is a *Metal Oxide Varistor* (MOV) device used to suppress a.c. line transients above the normal peak a.c. voltage (some high voltage transients can reach 2000 V for 30  $\mu$ s).

The transformer in Fig. 9 performs two functions. First, it isolates the equipment electrical system from the mains electrical system. Second, it frequency limits the system to prevent high frequency transients and pulses from passing into the equipment. It is my opinion, shared by many other engineers, that no computerized or other digital equipment - and many types of analogue equipment - should be operated in a noisy environment without one of these transformers. If the equipment is lifesupport, or life-saving, as it often is in medical applications, then it is probably engineering malpractice to design a piece of equipment without the transformer.

Fig. 9. Line isolation transformer used with digital instruments, analogue instruments and computers to eliminate high voltage transients, mains voltage fluctuations and other problems. This transformer is manufactured by Topaz in the USA.

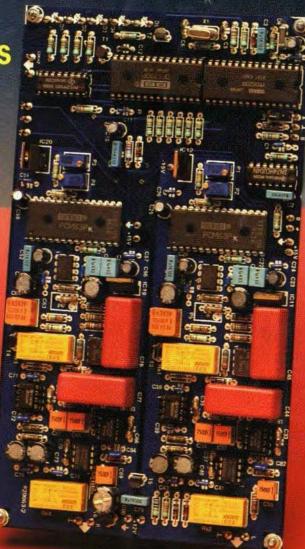

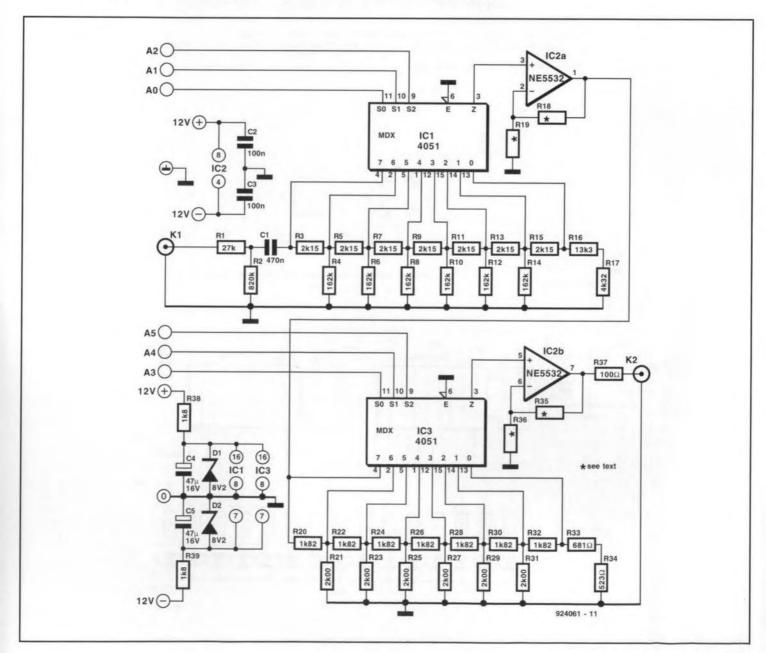

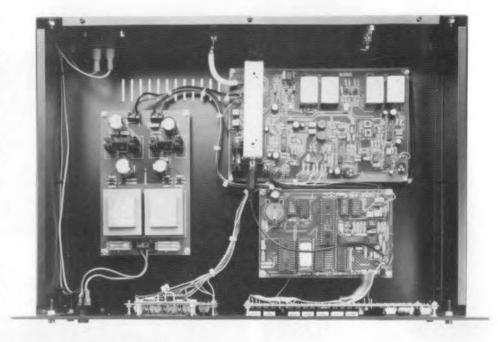

# A.F. DIGITAL-TO-ANALOGUE CONVERTER

# PART 1

Design by T. Giesberts

Twenty-bit converters, ×8 oversampling and high-quality analogue stages are used to translate the digital output of CDs, DAT recorders or radio broadcasts into the desired analogue information as accurately as possible. The converter is a stand-alone unit that is eminently suitable for use with the CD player published earlier this year.

DURING the past decade, digital techniques have assumed an increasingly important role in audio engineering. Hailed, somewhat exaggeratedly, as 'perfect' and 'ideal', quite a few improvements have been found necessary since those early years in appliances using these techniques. No doubt, others will be found indispensable over the next few years. There is also a growing band of audio pundits who foresee the end of both the CD and DAT before the year 2000.

Be that as it may, at present, the CD player is the second most important unit in the audio chain (world-wide, the compact cassette is still way ahead as the most popular music medium). It is well known that the output sections of that unit play a vital role in producing a near-perfect reproduction of the original sound. Unfortunately, a CD player cannot be upgraded as easily as a record player in the past. Then, a better quality tone arm or styles could be added without any trouble. In a CD player, the only improvements possible are in the digital or analogue sections and they are not so easily implemented. There are, of course, two other possibilities: buy a new CD player or an add-on digital-to-analogue converter-DAC. Neither of these is a simple solution, although in the case of the add-on unit, it should be borne in mind that it can be used with a number of different appliances.

Furthermore, there are not that many commercially available stand-alone DACs on the market, probably owing to their high price: at present this can vary from a few hundred to a few thousand pounds. A buildyourself design was until now not really feasible owing to the non-availability of certain parts and components. The design presented costs about one third of a commercially available unit with near-identical specifications: £250–£400.

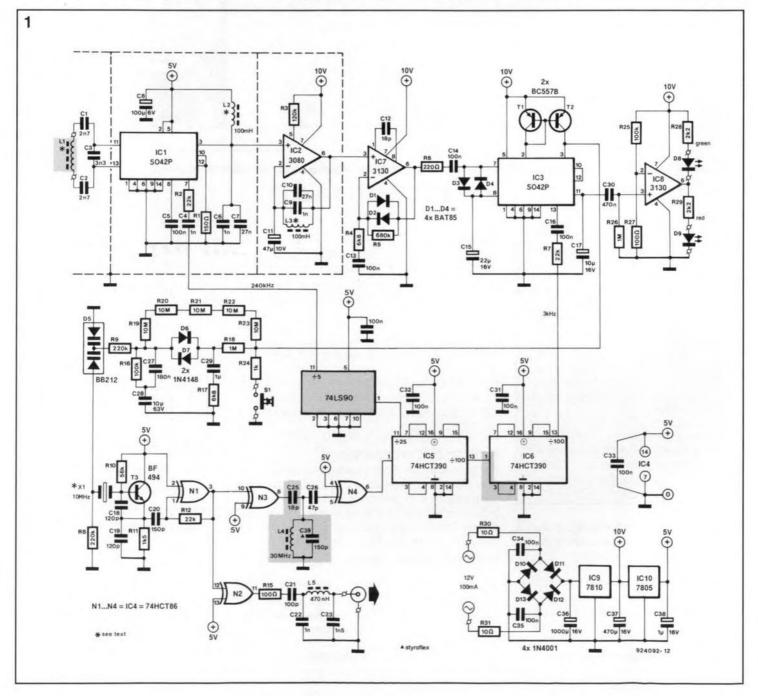

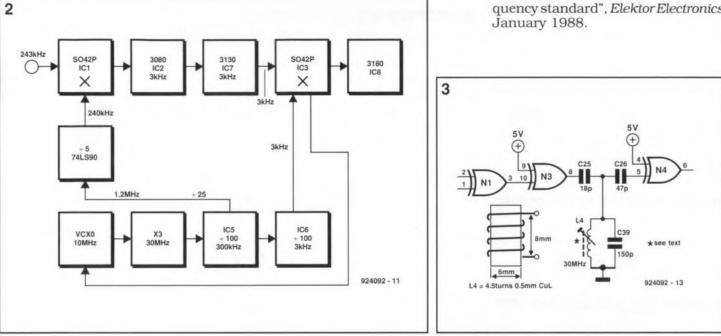

### The design

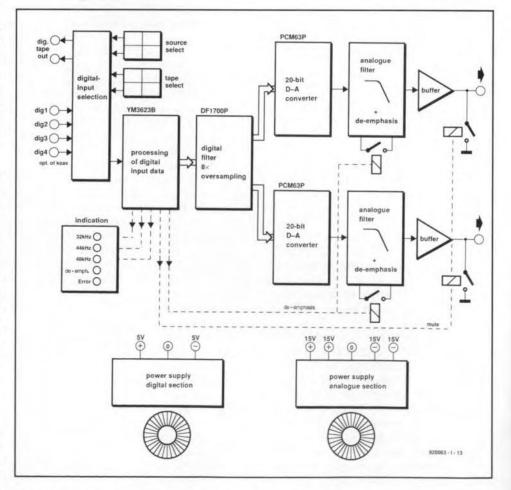

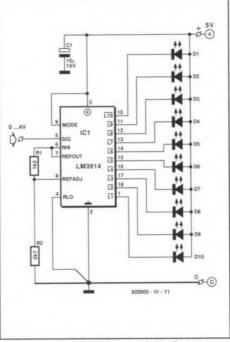

The digital-input selection in the block schematic in Fig. 1 accepts four digital signal sources, which may be connected by fibreoptic or coaxial cable. The tape select stage enables any one of the four signals to be applied to the digital tape output.

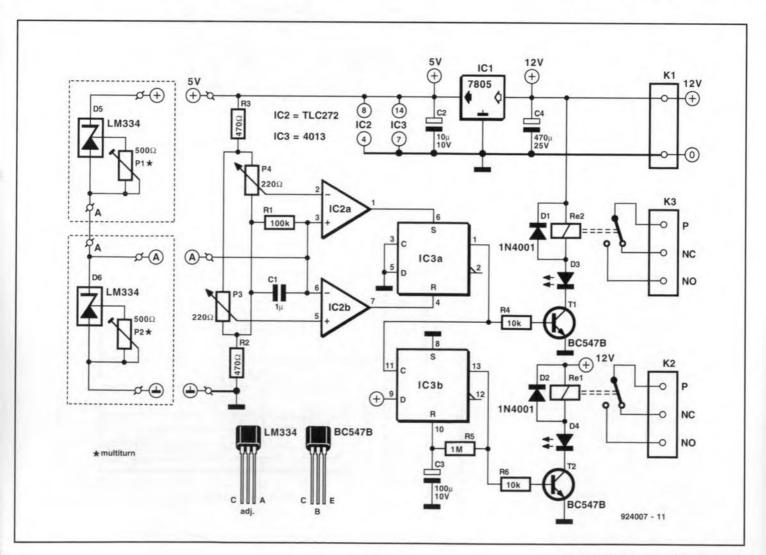

Fig. 1. Block diagram of the digital-to-analogue converter.

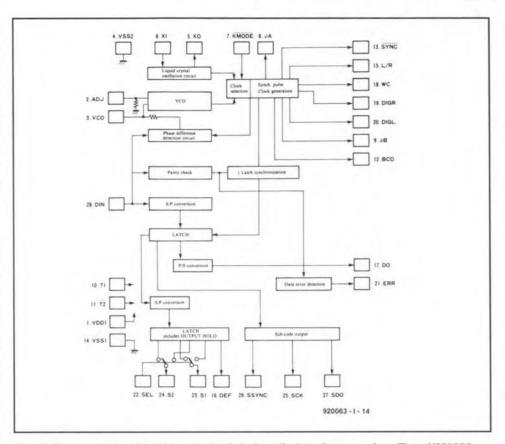

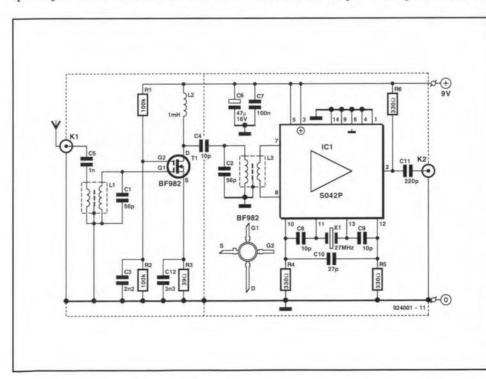

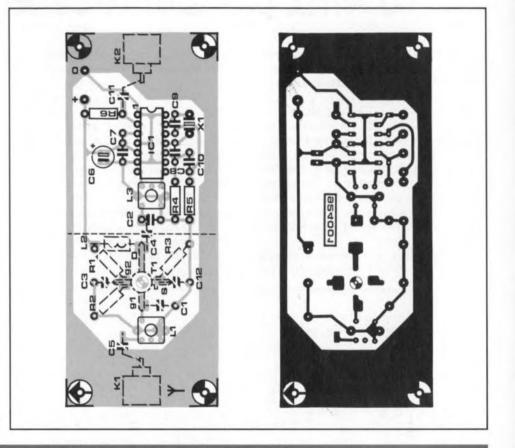

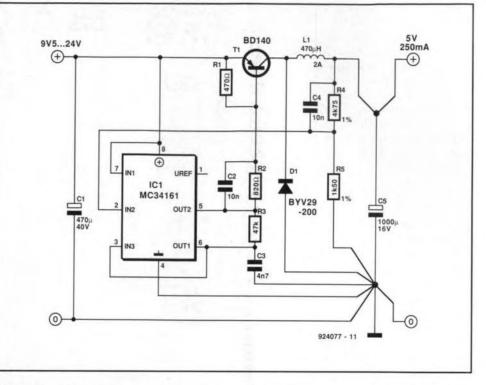

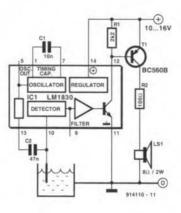

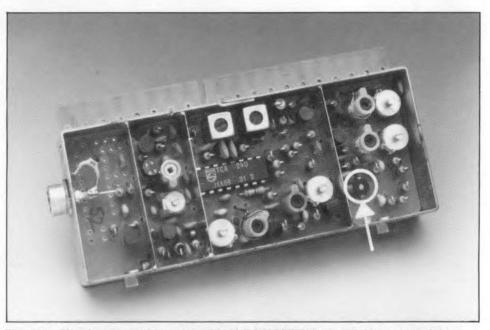

The selected input signal is applied to a special Yamaha IC Type YM3623. The circuit of this chip is shown in Fig. 2. Its PLL (phase-locked loop) produces a clock from the input signal for the subsequent stages. The range of the PLL is wide enough to enable the processing of all current sampling frequencies. In the absence of an input signal, the IC's crystal oscillator generates a stable frequency for the digital filter and the actual DAC stages.

The most important task of this chip is, however, the analysis of, and error detection (Philips-Sony format) in, the audio data of the incoming signal before this is applied to the digital filter.

Basically, the data provided by the IC could be processed directly by the DAC, but that would create problems in the analogue section, because the sampling frequency mustbe sufficiently suppressed there without introducing amplitude and phase errors in the audio range. That introduction is combated by oversampling, which involves the computation by a digital filter of intermediate steps that cause the sampling frequency to be shifted upwards artificially. The more intermediate steps, the higher the sampling frequency, and the easier the design of the analogue filters.

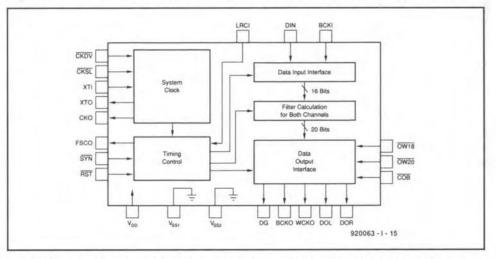

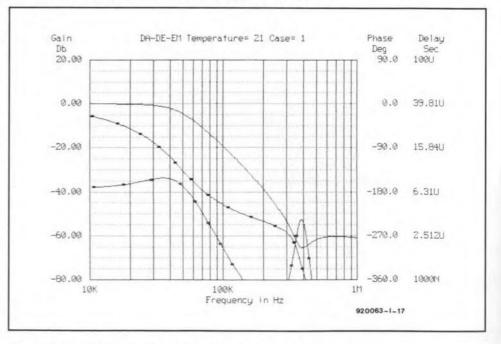

The digital filter, a Burr-Brown Type DF1700 dual channel type, provides ×8 oversampling, which means that each sample is converted into eight discrete levels. These levels make possible smaller steps than the various original levels. The ×8 oversampling converts the input data frequency of 44.1 kHz (with CD reproduction) to 352.8 kHz. This means that a third-order filter can be used in the analogue section, which reduces filter phase non-linearities.

The interposition of additional steps and the computation of the intermediate values increase the resolving power at the output of the digital filter compared with that of the 16-bit input. If a converter with an accuracy of more than 16 bits is used, the increased resolving power is retained in the conversion, so that in the present design, the converter processes 20 bits. This is, by the way, the maximum resolution the DF1700 can provide at its output. The pass-band ripple of the DF1700 is <0.00005 dB.

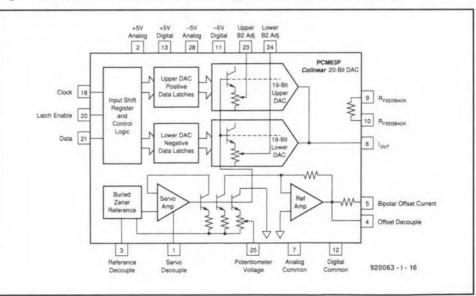

Although one-bit converters are currently in fashion, they do not really give satisfactory results for top-of-the-range equipment. In the present design, a 20-bit monolithic IC Type PCM63P from Burr-Brown was chosen. Burr-Brown supplies many manufacturers of CD players and currently this chip is their top multibit converter.

The PCM63P—see Fig. 4—contains two 19bit converters: one each for the positive and negative halves of the signal. This design has the advantage that it prevents bipolar zero distortion (traditional DACs usually switch the most significant bit around the bipolar zero, which may give rise to glitches and non-linear distortion). To ensure exact synchronization of the two converters, they use the same *R*-2*R* ladder network and the same reference voltage. Because of the 20-bit conversion, the harmonic distortion is low:

Fig. 2. Block schematic of Yamaha's digital audio interface receiver Type YM3623.

Fig. 3. Block schematic of Burr-Brown's Type DF1700 dual-channel digital filter.

Fig. 4. Block schematic of Burr-Brown's 20-bit monolithic audio DAC.

-96 dB at full drive (K version).

The analogue output section consists of a very fast current-to-voltage converter following the DAC and a third-order low-pass filter in which no opamps are used. Its design is known as a Generalized Impedance Converter—GIC. In this, an opamp configuration to ground acts as a second-order frequency-dependent passive element. This has the advantage that the audio signal does not have to pass through an opamp.

The analogue signal is fed to the output via a buffer stage. Relays short-circuit the output when a high level of noise is present or when the de-emphasis circuit is switched in, if the input signal makes that necessary.

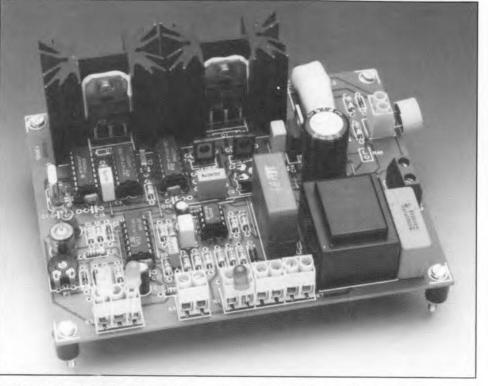

The design of the power supply ensures complete separation of the digital and analogue sections, and it, therefore, used two transformers. No fewer than ten regulator ICs ensure optimum supply quality.

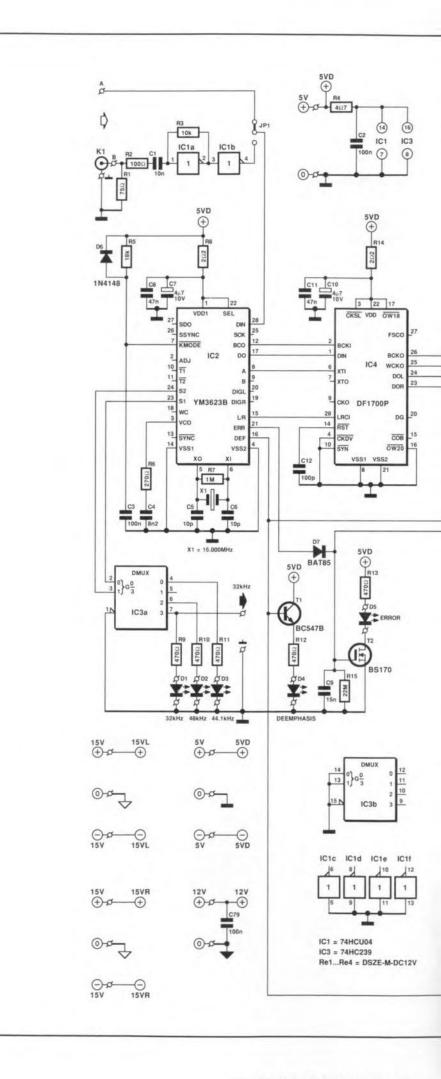

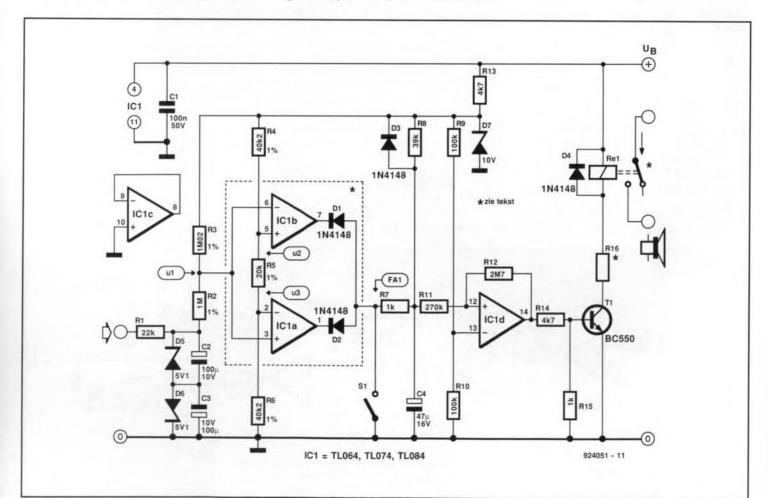

### The circuit

The digital signal from the CD player, DAT recorder, or DCC (digital compact cassette) player enters the circuit in Fig. 5 via K<sub>1</sub>. Resistor R<sub>1</sub> ensures correct termination of the coaxial input cable to obviate possible reflections. The bi-phase signal is enhanced by two inverters, IC<sub>1a</sub> and IC<sub>1b</sub>. With the aid of R<sub>2</sub> and R<sub>3</sub>, the former is arranged as an analogue amplifier that raises the 500 mV signal six-fold. Inverter IC<sub>1b</sub> produces a pure TTL signal with improved transitions (edges). The signal is then applied to the Digital Audio Interface Receiver—DIR—IC<sub>2</sub>.

When the digital input selector (to be published shortly) is used, the input signal is applied from that selector to A—resistors  $R_1$ ,  $R_2$ , and  $R_3$ , capacitor  $C_1$  and  $IC_1$  can then be omitted.

The YM3623B requires only few external components. Crystal  $X_1$  provides a stable output frequency in the absence of input data; the internal PLL is then switched off. Capacitor  $C_4$  and resistor  $R_6$  form, the integrator network for the VCO—voltage-controlled oscillator—of the internal PLL. The values of these components have been chosen to ensure that the 32–48 kHz frequency range is scanned with the minimum of phase jitter. Network  $R_5$ - $C_3$ - $D_6$  resets the clock switch-over circuit in the IC at power-on. The supply line is decoupled by  $R_8$ - $C_7$ - $C_8$ .

Note that the crystal frequency is usually chosen to give an oscillator frequency of exactly 44.1 kHz (after scaling). In practice, it transpired that that created a lot of interference in the PLL, since both operate at about the same frequency. Therefore, a crystal frequency that is not a multiple of the sampling frequency was chosen. This does not detract from the operation of the circuit, because the oscillator is in any case used only as an emergency frequency source for the internal logic of the IC and subsequent circuits in the absence of in put data. The crystal frequency may be 16–20 MHz.

The YM3623B provides, apart from the audio data, also additional information contained in the bi-phase signal. For instance,

Fig. 5. Circuit diagram of the audio-frequency digital-to-analogue converter.

27

#### **AUDIO & HIFI**

28

outputs  $S_1$  and  $S_2$  carry the current sampling frequency. That information is made visible with the aid of IC<sub>3a</sub> on one of three LEDs: 32 kHz; 44.1 kHz; 48 kHz.

The copy bit contained in the information is not made visible, because it is not used by any manufacturer.

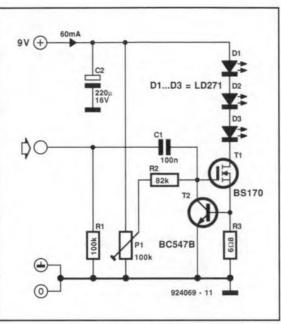

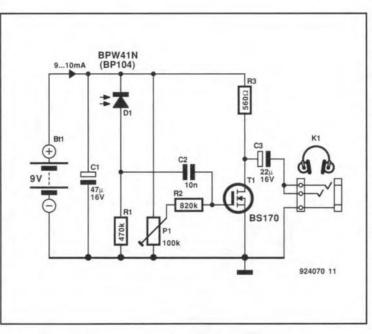

The ERR(or) output indicates when an error has been detected in the data input. The signal available at this pin is lengthened sufficiently by pulse stretcher  $R_{15}$ - $C_9$ - $D_7$  to switch on  $T_2$  switching, so that  $D_5$  lights. The ERR signal is also used to energize relays  $Re_2$  and  $Re_4$  via  $T_5$ , whereupon the analogue outputs are switched off. Transistors  $T_2$  and  $T_5$  are MOSFET types to keep the switching currents on the printed-circuit board low.

The DEF output signals the presence of preemphasis on the input, whereupon the deemphasis network and  $T_1$  are switched on via Re<sub>1</sub> and Re<sub>3</sub>. As soon as  $T_1$  conducts,  $D_4$ lights.

Subsequently, the audio signal is fed from pin 17 of IC<sub>2</sub> to digital filter IC<sub>4</sub>. This IC needs clocks to function correctly: one is derived from the bi-phase signal and is available at pin 8 of IC<sub>2</sub>, while the other is the timing signal for writing serial data and is available at pin 12 of IC<sub>2</sub>. It also needs a multiplex signal that indicates whether the current data are for the left-hand or right-hand channel; this signal is fed from pin 15 of IC<sub>2</sub> to pin 28 of IC<sub>4</sub>.

The supply lines to the filter are decoupled by  $R_{14}$ - $C_{10}$ - $C_{11}$ .

After the filter has translated each data word into eight new values, the DACs can be driven by these data (DOR=Data Out Right; DOL=Data Out Left). Again, some control signals are needed: bit clock (BCKO) and word clock (WCKO).

The *RC* networks inserted into the lines from the filter to the DACs filter out any RF interference and noise signals.

As an aside, assuming that a CD signal is input, the system clock from  $IC_2$  to  $IC_4$  is 16.9344 MHz—the L/R clock is, of course, 44.1 kHz. The clock (BCO) for writing serial data is 2.8224 MHz. The BCKO clock and WCKO clock between the digital filter and the DACs are 8.4672 MHz and 352.8 kHz respectively. It is clear that these are all RF signals, and it is imperative to keep them and their harmonics—away from the analogue section.

Presets  $P_1$  and  $P_2$  ( $P_3$  and  $P_4$ ) enable the setting of the MSB—most significant bit of each 19-bit converter in IC<sub>5</sub> and IC<sub>13</sub>. Precision test equipment is required for this, however; if that is not available, the presets can be omitted. The ICs are available in three versions indicated by (a) no letter after the type number (least expensive); (b) a J after the type number; (c) a K after the type number (most expensive).

Since the divorce of the analogue and digital sections comes about in the DACs, attention must be paid to the power supply. As already stated, the supplies for the two sections are completely separate. All supply connections are decoupled independently. Moreover, on the relevant printed-circuit board, the earth connections for the two

Fig. 6. Circuit diagram of the power supply for the DAC.

Fig. 7. Theoretical response of the analogue output filter.

sections have been kept separate.

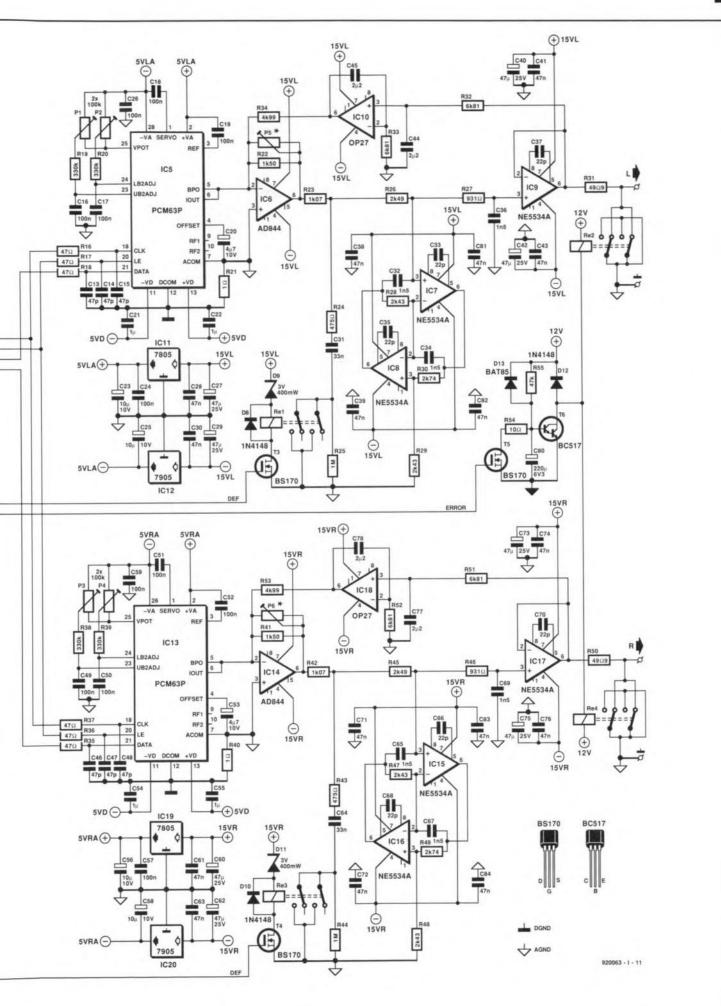

The output of the converters is applied to a current-to-voltage converter,  $IC_6$  and  $IC_{14}$ , for the left-hand and right-hand channel respectively. These are needed, because virtually all converters provide an analogue output current rather than a voltage. Undistorted conversion of the voltage waveform (analogue signal with superimposed steps of the sampling frequency) requires an IC with a very high slew rate. That requirement is met by Analog Devices' Type AD844, an opamp with a bandwidth of 60 MHz and a slew rate of no less than 2000 V/µs.

The output filter is a third-order pseudo passive design, that is, there are no active components in the signal path. It consists of  $R_{23}+R_{26}$  followed by the GIC configuration of IC<sub>7</sub> and IC<sub>8</sub>, which is followed in turn by passive section  $R_{27}-C_{36}$ .

The de-emphasis network is entirely passive and consists of  $R_{23}$ - $R_{24}$ - $C_{31}$ . It is switched into circuit by relay  $Re_1$  as soon as this is energized, whereupon  $R_{25}$  is short-circuited (left-hand channel).

Finally, buffers IC<sub>9</sub> (left-hand) and IC<sub>17</sub> (right-hand) provide a high load for the low-pass filter on the one hand, and sufficient current for driving a (pre)amplifier at the output of the converter.

The impedance of the analogue outputs is 50  $\Omega$  (R<sub>31</sub> and R<sub>50</sub>). Resistors R<sub>31</sub> and R<sub>50</sub> also make it possible for the mute relays, Re<sub>2</sub> and Re<sub>4</sub>, to short-circuit the outputs to earth without detriment. Energizing of these relays is delayed by the circuit based on T<sub>6</sub>. This gives the entire circuit time to settle in after power-on before any relays are energized. In the case of error indications, the mute relays are de-actuated off via T<sub>5</sub>.

There is a wide choice of opamps for the low-pass filter and buffer stages. Ten different models were tried in the prototypes, but their performance was more or less uniform. The parts list (next instalment) gives an NE5534A, which was the least expensive of the ten. Note also, that there are commercial CD players costing over £1000 that also use the NE5534A.

It will have been observed that the entire analogue section is DC coupled and also that there is no output capacitor. To ensure that the direct voltage at the output is always exactly zero, a servo control,  $IC_{10}$  and  $IC_{16}$  respectively, has been added between the output of the buffer opamp and the noninverting input of the current-to-voltage converter opamp. Although the off-set current of the DACs is virtually zero, this arrangement ensures that very-low-frequency signals, as well as the off-sets of the various opamps, are nullified.

The servo control is an integrator that monitors the output voltage of the buffer, on the basis of which it adjusts the direct voltage of the *I-U* converter so that the output voltage remains zero. The control has absolutely no effect on signals in the analogue circuits above 10 Hz. To ensure purity of the signal in the servo control, which is after all a sort of high-pass filter with low cut-off frequency, all capacitors are MKP (metal-plated polypropylene) types.

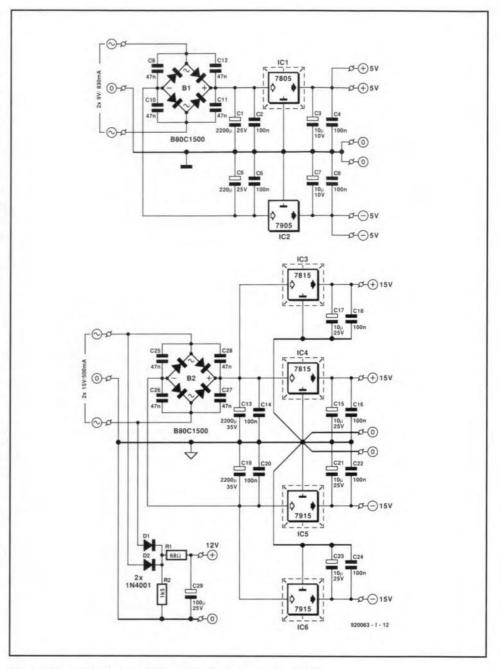

The power supply—see Fig. 6—is clearly in two parts. That for the digital section delivers  $\pm 5$  V (B<sub>1</sub>, IC<sub>1</sub>, and IC<sub>2</sub>). In that for the analogue section, rather more components are used, because it was thought important to give the left-hand and right-hand channel its own regulation. Bridge rectifier B<sub>2</sub> is followed, therefore, by two positive and two negative regulators. A 'star' earthing point obviates any problems with earth currents.

There is a separate 12 V supply, provided by  $D_1$  and  $D_2$ , for the mute relays. The value of capacitor  $C_{29}$  has been kept small to ensure that the mute relays are de-energized the instant the power is switched off.

Each of the supplies uses its transformer. It is, of course, possible to use one with split secondaries, but that will have to be wound to order. In the prototypes, toroidal transformers were used, which keep the stray field to an absolute minimum.

The second and final part of this article, describing the construction of the converter, will be published in our September issue (there is no August issue).

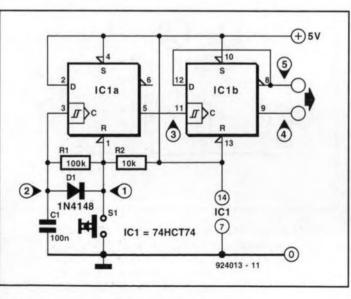

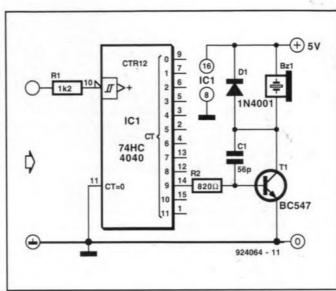

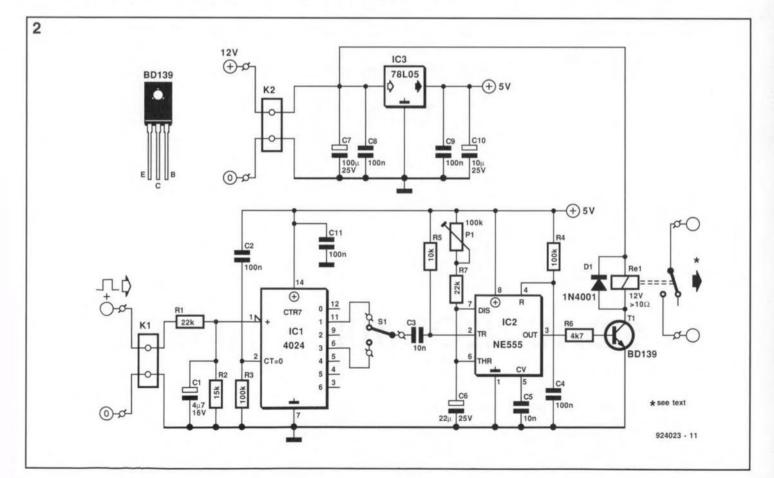

# **PULSE GENERATOR**

THIS pulse generator can provide up to to 12 pulses at its output, depending on the setting of hexadecimal switches  $S_2$ - $S_{13}$ .

The (rectangular) pulses are generated by  $IC_{3c}$ ; with circuit values as shown, their p.r.f. (pulse repetition frequency) is a few kHz.

The output of the generator is taken to one input of NOR gate  $IC_{2c}$  via buffer/inverter  $IC_{3b}$ .

When switch  $S_1$  is operated, bistable IC<sub>1a</sub> receives a clock pulse, whereupon a logic 1 is passed to the D input (pin 12) of IC<sub>1b</sub> via IC<sub>2a</sub>. The other input of IC<sub>2a</sub> is low because counter IC<sub>3</sub> is disabled via its reset input. At the next leading clock transition (edge), the bistable is set, so that IC<sub>3</sub> and, via IC<sub>2b</sub>, the pulse output are enabled.

When the relevant number of pulses has been output, junction  $R_3$ - $S_2$  goes high, whereupon the output of IC<sub>2a</sub> goes low and IC<sub>1b</sub> passes a logic 0 from its D input to pin 9 (Q output). IC<sub>1a</sub> is reset via C<sub>1</sub>, so that S<sub>1</sub> can be operated again, and the counter is reset via pin 8 of IC<sub>1b</sub> ( $\overline{Q}$  output). Also, pin 8 disables gate IC<sub>2b</sub>, so

that no more pulses can appear at the only 2.5 mA. output.

The generator draws a current of

(A.N. Other - 924109)

**ELEMENTS OF PASSIVE ELECTRONIC COMPONENTS**

# PART 3: THE CAPACITOR

#### by Steve Knight, B.Sc.

THE history of the modern capacitor goes back to antiquity when the Greeks made a study of electrification of amber by friction. After that, very little more about the subject of electrostatics emerged until the middle of the eighteenth century when, in 1746, the Dutch physicist Pieter van Musschenbroek (1692-1761) discovered, by accident, the principle of the capacitor in the form of the celebrated Leyden jar. Having received a powerful electric shock from his experiments, arising from an attempt to electrify water in a bottle, van Musschenbroek confessed that he would not take such another shock 'for the kingdom of France'. Many modern experimenters have, no doubt, uttered words to the same effect when carelessly handling circuits boards containing charged capacitors.

30

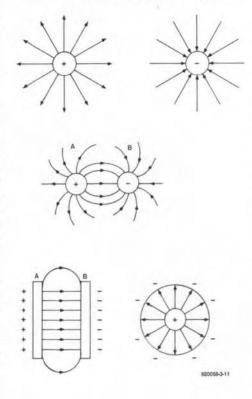

We have seen in the previous parts of this article that inductance and inductive effects depend upon the magnetic field; here we shall see that capacitance and capacitive effects depend upon the electric field. The existence of an electric field depends itself on the presence of electric charges. When the charges are removed, the field vanishes. The nature of the field and the direction taken by the electric flux is a function of the magnitude of the charges and their distribution.

The fundamental electric charge, e, resides in the electron, which carries a charge of -1.6×10-19 coulomb (C). Electrons may be added to a body so as to give that body an excess of electronics; the body then exhibits a negative electrostatic charge. In the same way, electronics may be removed from a body, giving it a deficit of negative charges; the body is then positively charged. In normal circumstances, bodies have neither an excess nor a deficit of electrons and are uncharged, neutral, or at 'earth' potential. So the general mass of the earth is a permanently neutral body and materials may carry charges in the form of an excess or a deficit of electronics with respect to earth. There should be no confusion here with the 'excess' or 'deficit' of charge carriers in semiconductor materials, where the crystal remains electrically neutral.

As the Greeks established, without being aware of what they were handling, the removal from, or the addition to, a body of electrons may be accomplished by purely mechanical means, as when a piece of amber is rubbed with silk, or, more practically for our purposes today, by applying a potential difference between conducting materials.

A field of electric force, like a magnetic field, may be represented in magnitude and direction by drawing lines of force in the region surrounding the charged body or between charged bodies, the line densities being an

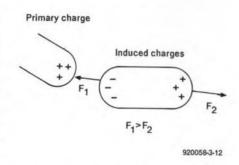

indication of the field strength. The relationship between these convenient though imaginary lines and the field strength E (a vector) is that the tangent to a line at any point gives the direction of E at that point and the number of lines per unit cross-sectional area (that is, the flux density, D, in C m-2) is proportional to the magnitude of E. A number of typical and idealized fields for isolated and adjacent charges is shown in Fig. 1. Unlike the magnetic field, electric lines of force do not form closed loops. but are taken to emanate from positive charges and terminate on equal and opposite negative charge. When, therefore, a charged body is brought into proximity of an uncharged body, an induced charge of opposite sign appears on the near surface of the body, resulting from the line termination points. Hence, a net attraction is set up between the bodies because unbalanced forces act on the induced surface charges as illustrated in Fig. 2: a phenomenon known to the Greeks when their charged pieces of amber attracted wisps of straw.

It was believed at one time that a metallic body could not be given a charge by frictional means as could bodies of non-conducting or insulating materials; however, provided that the metal is supported or held by an insulating substance, such conductors

Fig. 1. Some typical electrostatic field configurations using the concept of lines of force.

can be charged just as well as anything else. In metals, only the negative charge is free to move; the positive charge is as immobile as it is in glass or any other insulator.

Fig. 2. A charged body attracts an uncharged body because unbalanced forces act on the induced charges disposition.

## The electric field

To get a proper understanding of the phenomenon of capacitance, we need a proper appreciation of the field concept. In both magnetic and electric systems, energy is stored in the field, not in the component parts producing the field. Before Faraday's time, the force acting between charged particles was thought of as a direct and instantaneous interaction between the particles, and Faraday himself always thought of the field in terms of lines of force. This concept still provides us with a convenient way of visualizing field patterns as we have seen, but it is really necessary to think in terms of charge acting on a field or of a field acting on a charge, and not as charge acting upon charge as the action-at-a-distance concept would have us suppose. Look at Fig. 1c for a moment; suppose particle A carrying the positive charge suddenly moved to the left; how soon after this would the charge on particle B learn that A has moved and that the force of attraction it has so far experienced decreases? If actionat-a-distance were true, the information would be transmitted instantaneously to particle B, but this does not accord with commonplace experience. Moving charges in the aerial system of a radio transmitter, for example, establish an electromagnetic field and so influence electrons in a distant receiving aerial system, but only after a finite time, determined by the distance travelled and the speed of light.

When the flux density, D, changes, the electric force E changes proportionally and there is a constant relationship for a field established in air: the ratio D/E is designated  $\varepsilon_0$ . This is the *permittivity* of free space or the free space constant. Its value is found ex-

Fig. 3. The potential between conductors carrying equal charges falls as the conductors approach one another.

perimentally to be 8.85×10-12 F(arads) m-1.

### Capacity

There is a limit to the charge that may be placed upon a conductor. If an attempt is made to exceed this limit, a discharge will take place from the surface of the conductor to some nearby earthed or neutral point, sometimes as a spark or a fine corona or brush discharge into the surrounding air. Any conductor, therefore, has a certain ability or 'capacity' for holding a charge. Can we now obtain a practical definition of capacity and is it possible to increase the capacity of a given conductor so that more charge may be added before an 'overflow' occurs?

When a positive charge is added to a conductor, the potential of the conductor is raised relative to a neutral plane. This 'rise' in potential is measured in a negative sense for a negatively charged conductor; in both cases, the potential U is found to be proportional to the charge q coulombs; hence, q=CU, where C is a constant of proportionality. This constant, that is, the capacity of the

Fig. 4. Charging the basic capacitor.

Fig. 5. Forces act on a molecular dipole and tend to align it with the electric field.

conductor, is called the *capacitance*. The m.k.s. unit of capacitance is the coulomb/volt, more commonly called the *farad* (F), named in honour of Michael Faraday. Thus, one farad = one coulomb/volt; that is, 1 coulomb of charge raises the potential of unit capacitance by one volt. The farad is a very large unit, and in practice the microfarad,  $\mu$ F (10<sup>-6</sup> F), the nanofarad, nF (10<sup>-9</sup> F), and the picofarad, pF (10<sup>-12</sup> F) are used, although memory back-up values of several farads are now commonplace.

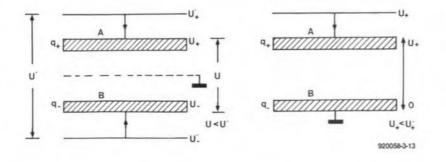

How might the capacity of an inductor be increased? What follows is true for conductors of any shape, but to make the explanation easier, it is assumed that a conductor in the form of an isolated metal plate, A, carries a positive charge,  $q_+$  coulomb, giving it a positive potential. In Fig. 3a, this potential is represented by the line  $U'_{+}$ . The line marked U represents a neutral plane or earth line. Suppose a second metal plate, B, carrying a negative charge,  $q_{-}$  coulomb, also isolated, has a corresponding potential,  $U'_{-}$ , represented by the line  $U'_{-}$ . The potential difference between the plates is clearly  $U'=U'_+-U'_-$  and this is proportional to the charge on either plate.

Let the two plates now approach each other; the charge on the plates will be unaffected, but what happens to their potentials? If a positive charge is brought near to an isolated conductor, the potential of that conductor will be lowered, since a negative charge will be induced on it; in the same way, the proximity of a negative charge will raise the potential. This, the potential of the positively charged plate A, will be lowered by the nearby presence of the negatively charged plate B from  $U'_+$  to some lower value  $U_+$ . Similarly, the potential of plate B will be raised from  $-U'_{to some higher value}$  $-U_{-}$ . These new potentials are shown in the figure: the changes are indicated by the vertical arrows.

The same effect can be produced if a single plate, carrying, say, a positive charge  $Q_+$ , is approached by an isolated neutral plate as shown in Fig. 3b. Lines of force from the charge on A will terminate on the inner surface of plate B and an induced negative charge will be established there. The inner plate surfaces now carry equal but opposite charges. The induced charge on B produces its own field and, in the same way

as described above, the potential of A consequently falls. Hence, the 'capacity' of A has been effectively increased by the presence of plate B. We conclude that the potential difference between two conductors that carry constant, equal charges of opposite sign is reduced as the conductors are brought closer together.

31

Devices that operate on these principles are capacitors; perhaps their old name of 'condenser' was not so inappropriate when it is considered that the electric field is concentrated by such means and so made capable of storing additional electrostatic energy.

### The parallel plate capacitor

The parallel plate is the most basic of all capacitor designs: all other varieties are simply adaptations of it. Suppose two parallel plates are connected into a circuit as shown in Fig. 4. Starting with plates A and B uncharged, let a voltage be applied by the closing of switch S. A positive charge +q then appears on the left-hand plate and a negative charge -q on the right-hand one, so that finally the potential difference between the plates is equal to the applied voltage, U. The plates are then charged.

For these charges to be established, there must have been a movement of electrons around the circuit; that is, a current must have flowed in the direction A to B for the time during which the equalization of the voltages was attained. This *displacement* current can be detected on an ammeter wired in series with the circuit. If the battery is switched off, the charge on the plates persists, as does the potential U across the plates. Thus, the capacitor stores electrical energy. It should be noticed particularly that q coulombs is the quantity of charge on *either* plate; it must not be taken as the net charge on the capacitor, which is *zero*.

If the plates are now connected together by a piece of wire, the capacitor will discharge; a momentary displacement current follows from plate *B* to plate *A* to restore the neutral condition of the plates and reduce the terminal voltage to zero. No current passes *through* the capacitor; there is simply a movement of electrons away from the positive plate and towards the negative plate; and these return in the opposite direction when the device is discharged.

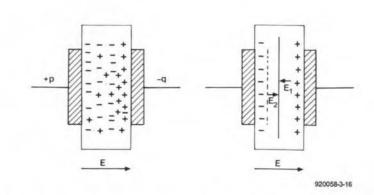

### Effect of a dielectric

When a slab of insulating material is placed in the space between the plates of a capacitor, it is found that the capacitance is increased. This comes about because the molecules of the dielectric, as the insulator is called, have what are known as electric *dipole moments* which may be permanent in some material and tend to align themselves with an applied electric field, as illustrated in Fig. 5. The dipoles have random orientations in the absence of an external field, but experience a torque tending to align them with the field when this is applied. Complete alignment does not occur, because of therCOMPONENTS

32

mal agitation of the molecules, but the alignment increases as the field is increased or the temperature falls. Molecules that do not have permanent dipole moments will, nevertheless, acquire them when subjected to an electric force. The field tends to separate the negative and positive charges on the molecule, so creating an induced dipole that will tend to alignment only when the field is present.

When a slab of dielectric is introduced between the plates of a capacitor, assumed to carry a fixed charge q, the effect of dipole alignment is to separate the centre of positive charge of the slab slightly from the centre of negative charge. The dielectric, although remaining electrically neutral, becomes polarized. The overall effect is the appearance of positive charges on one surface of the slab and of negative charges on the other. These charges must be equal in magnitude; within the slab itself, there is no displacement of electrons and no transfer of charge over large distances. As Fig. 6 shows, the induced surface charges will always be established in such a way that the electric field they themselves set up,  $E_1$ , will oppose the applied field. The resultant field in the dielectric,  $E_2$ , is then the (vector) sum of E (the applied field) and  $E_1$ , and this is always smaller than E. We conclude that, owing to the presence of a dielectric in a field, induced surface charges tend to weaken the original field. This weakening shows itself as a fall in the potential between the plates; hence, the capacitance, for a constant q, must be increased.

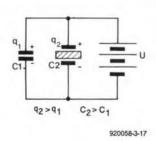

Faraday first investigated the effect of a dielectric on the capacitance of a conductor. In an experiment similar to that shown in Fig. 7, two capacitors were charged to the same potential, U, by the battery. Unlike the argument made earlier, in this system U does not change, so the charge q on the capacitor with the dielectric must increase above that on the air-spaced capacitor, which Faraday found was so. Thus, since q is greater for the same potential and C=q/U, the capacitance must increase through the introduction of a dielectric. If we give the capacitance with dielectric the symbol  $C_d$  and that without a dielectric  $C_a$ , the ratio  $C_d/C_a$  is called the dielectric constant or, more generally, the relative permittivity, Er. The dielectric con-

Fig. 6. (a) The applied field *E* separates the centre of +ve charge from that of -ve charge. (b) The surface charges set up a field  $E_1$  which opposes the applied field *E*. The resultant field  $E_2=E-E_1$  is thus weaker than *E*.

stant is unity for air spacing (strictly, for a vacuum), which, as we have noted, has a free space permittivity  $\varepsilon_0$ . The *absolute permittivity* when a dielectric is used is  $\varepsilon_0\varepsilon_r$ . Hence, the capacitance of any capacitor can be expressed as  $C = \varepsilon_0 \varepsilon_r L$ , where L depends on the form of construction and has the dimensions of length. For a parallel plate capacitor, L is A/d, where A is the plate area and d the plate separation.

### **Energy and losses**

When a capacitor is charged to potential U, energy is stored in the electric field established between the plates. When the capacitor is discharged, the field energy is returned to the external circuit in some way, often as a spark that generates heat and light. For a perfectly efficient capacitor, there would be no energy loss and all the charge put into the system would be returned by it. In a dielectric, work is done in turning the molecular dipoles, and if the capacitor is charged and discharged periodically, this process causes heat to be generated in the dielectric which represents energy loss; this loss can be represented as a small resistance in series (or a large resistance in parallel) with a loss-free component. It is usual to express such a loss in terms of the angle by which the lead of the current on the voltage falls short of 90°.

The energy stored in a capacitor is potential

Fig.7. The principle of Faraday's experiment to show that a dielectric increases the capacitance.

energy, which is dependent on the potential difference set up across the plates; in an inductor, it is comparable with kinetic energy associated with the movement of electrons in a wire. It is easily shown that the energy stored in a capacitance C is given by  $CU^2/2$  joules.

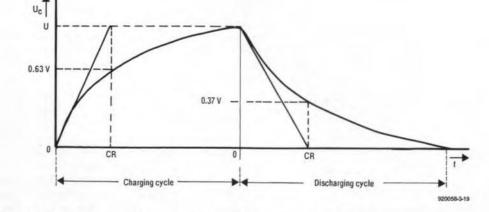

### Time constant

Since current is the rate of change of charge, i=dq/dt, the charge on a capacitor cannot change instantaneously, because that would require an infinite current and hence an infinite rate of change of voltage. This does not accord with experience. In effect, since the capacitance is constant, the voltage across a capacitor must momentarily remain the *same* before *and* after any abrupt change in the

Fig. 8. The meaning of time constant for the charging and discharging of a capacitor through a resistor.

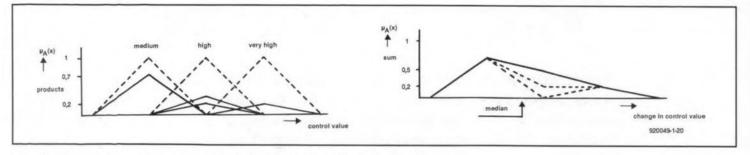

circuit conditions. This concept is of great value in predicting the behaviour of a circuit at some particular instant of time, such as the closing or opening of a switch. We can use it here in a very brief study of the capacitor as a timing element, where the charging cycle is restricted by the use of a series resistance—see Fig. 8.