THE INTERNATIONAL ELECTRONICS MAGAZINE APRIL 1992 UK £1.90

## NS

# **Top-of-the-range FM tuner**

Comb generator AD232 converter Generic array logic 2 metre receiver Red-light diode lasers Super sign Review of Pulsar

In next month's issue (among others):

- NICAM decoder

- Z80 card

- Review of Analyser III

- Digital short-range radio

- I<sup>2</sup>C display

- GAL programmer

- Elements of passive electronic components

- The NICAM system

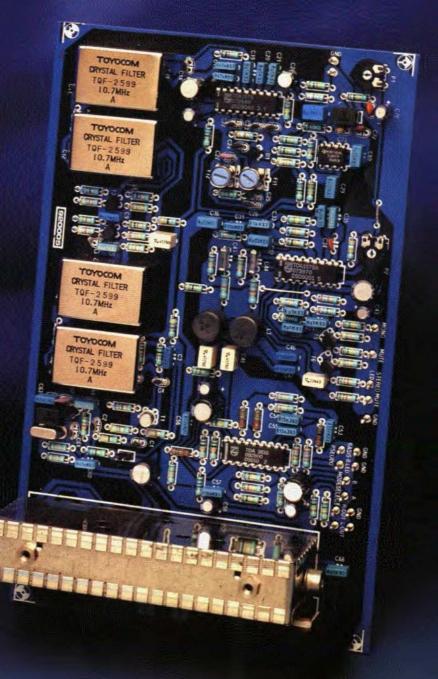

## Front cover

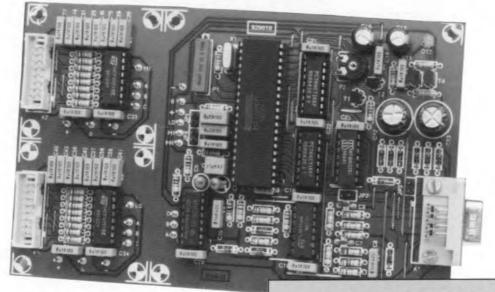

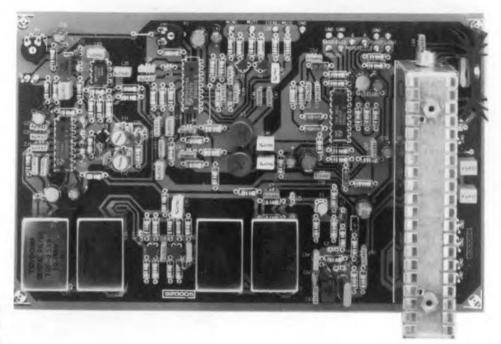

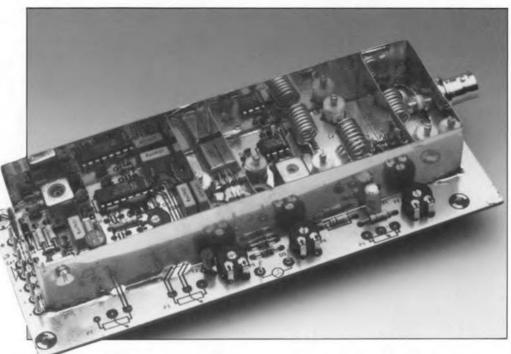

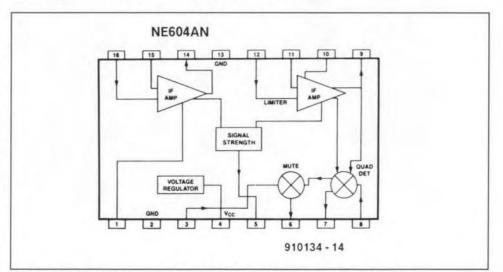

The FM tuner described in a series of articles that started last month has specifications that challenge those of the best commercial tuners available. Shown is the finished main tuner board. The (ready-made) tuner module used prevents problems with building and adjusting the RF circuitry. CONTENTS

## APPLICATION NOTE

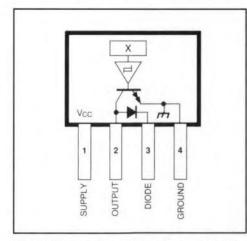

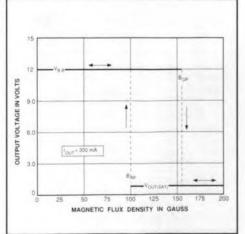

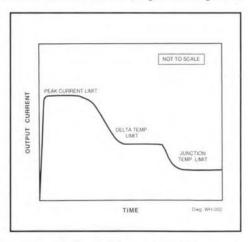

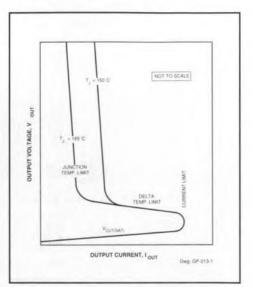

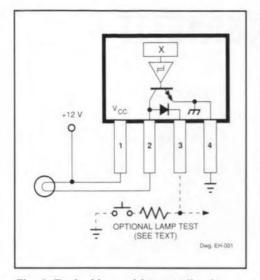

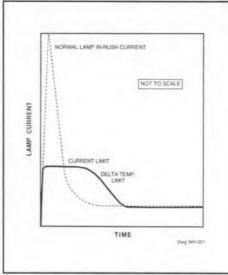

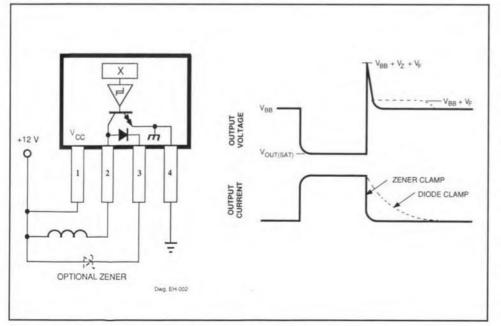

56 Lamp/solenoid driver Type UGQ5140K A Sprague application.

## AUDIO & HI-FI

## General information in 'Readers corner'

## COMPONENTS

64

| 24 | General array logic (GAL)                     |

|----|-----------------------------------------------|

|    | based on an original article by D. Gembris    |

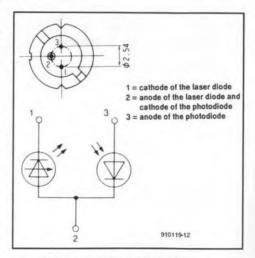

| 34 | Red-light diode lasers                        |

|    | based on an original article by S. von Fehren |

|    | COMPUTERS & MICROPROCESSORS                   |

48 COURSE: 8051/8032 assembler – Part 3 by Dr. M. Ohsmann

## DESIGN IDEAS

38 Super sign by Dr. K. A. Nigim

## GENERAL INTEREST

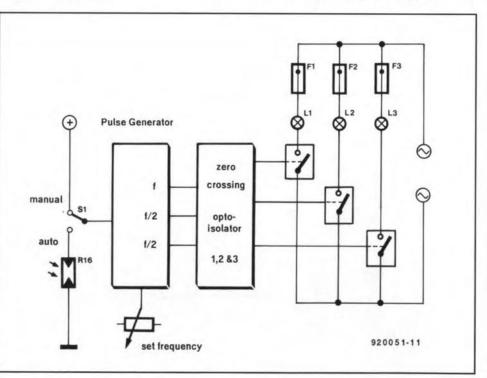

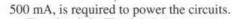

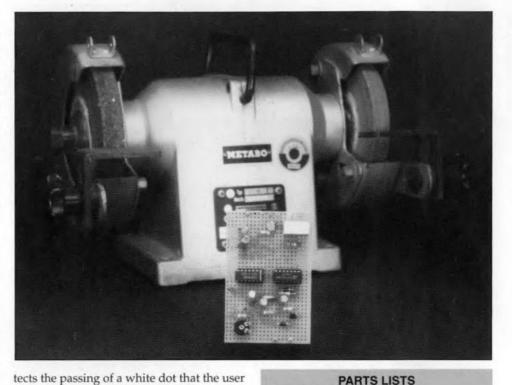

54 PROJECT: Motor speed limiter Design by K. Walraven

## INTERMEDIATE PROJECT

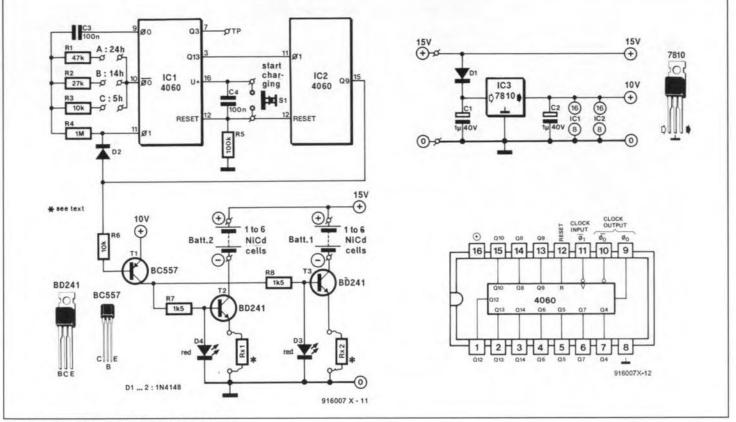

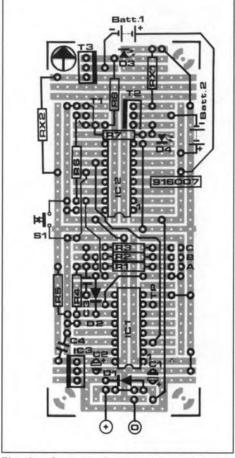

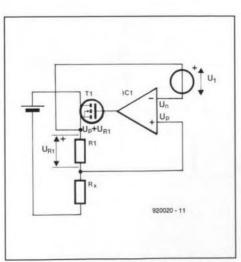

28 Automatic NiCd charger Design by L. Pijpers

## RADIO, TELEVISION & COMMUNICATIONS

- PROJECT: Comb generator Design by J. de Belie

PROJECT: FM tuner - Part 2

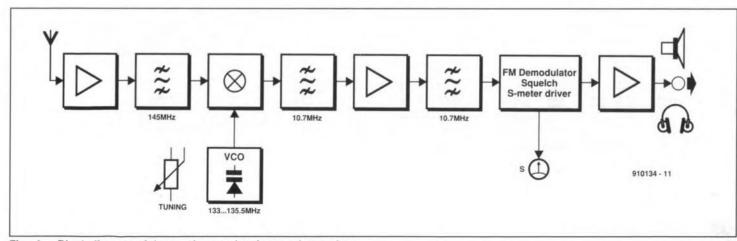

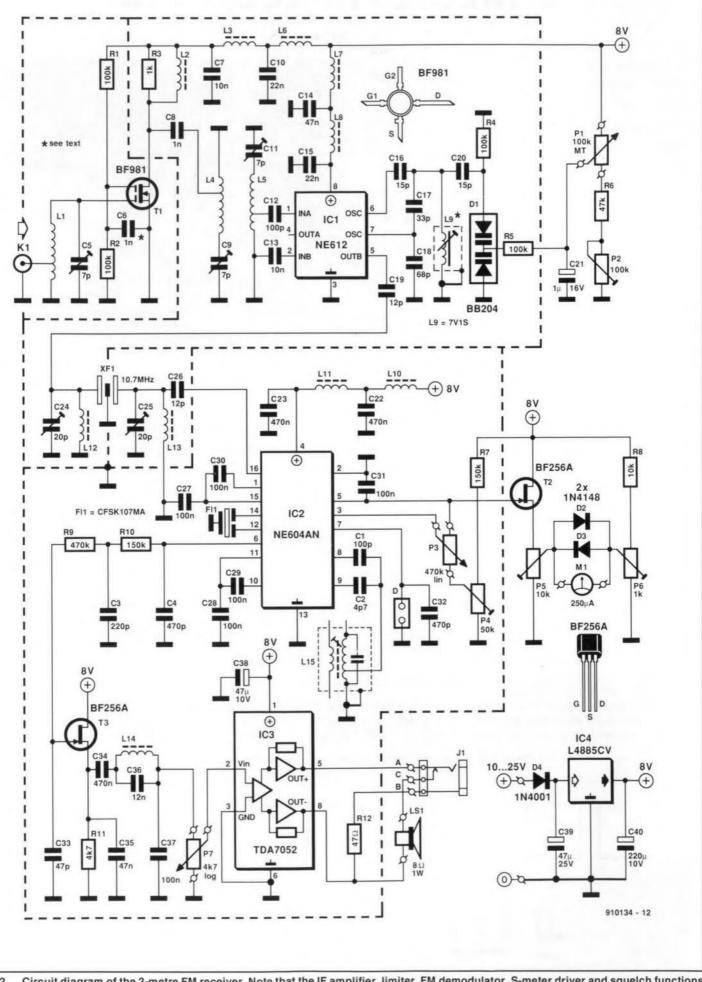

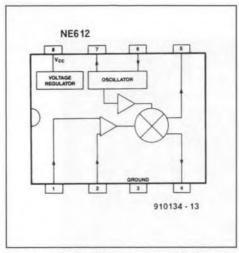

- 43 Design by H. Reelsen 43 PROJECT: 2-metre FM receiver

- Design by J. Barendrecht and L. Lemmens

## SCIENCE & TECHNOLOGY

31 Understanding waveform harmonics by Dr. K. A. Nigim

## TEST & MEASUREMENT

- PROJECT: AD232 converter Design by Ing. B.C. Zschocke and A. Arnold

PROJECT: LCD for Inductance/capacitance meter

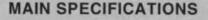

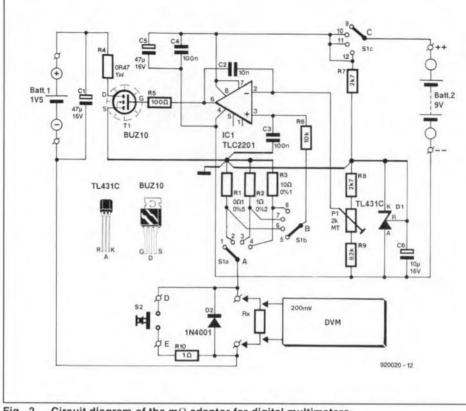

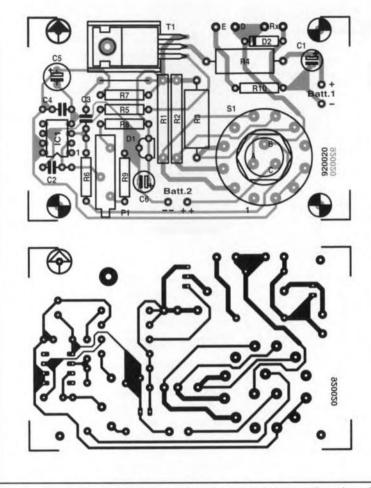

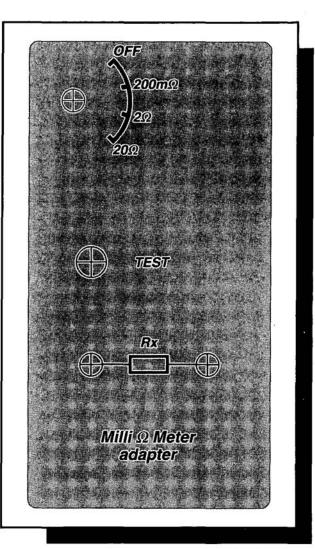

- 58 Design by L. Pijpers58 PROJECT: Milli-ohm measurement adaptor

- Design by Ing. B.C. Zschocke

## MISCELLANEOUS INFORMATION

Electronics scene **11–13**; Events **13**; New Books **61**; Guidelines for Authors & Translators **62**; Readers' corner **64**; Letters **65**; Switchboard **65**; Terms of Business **68**; Readers' services **69**; Index of advertisers **74**  April 1992 Volume 18 Number 199

Red-light diode lasers - p. 34

AD232 converter - p. 17

8051/8032 assembler course - Part 3 p. 48

Copyright © 1992 Elektuur BV

MEMBER OF THE AUDIT

BUREAU OF CIRCULATIONS

# COMB GENERATOR

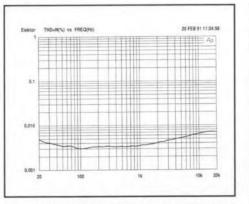

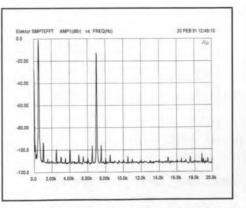

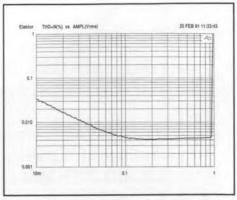

The name of the test instrument described here is based on the frequency spectrum it produces. The circuit will be particularly valued by owners of (ex-surplus trade) spectrum analyzers, because it produces hundreds of harmonics of 1 MHz or 10 MHz, of which the first 45 or so have the same output level within 3 dB.

## Design by J. de Belie

**I**NSERTING a filter between the output of the comb generator and the input of a spectrum analyser allows you to ascertain, and, if necessary, adjust, the filter characteristic. Similarly, the comb generator allows the frequency characteristic of an ex-surplus trade spectrum analyzer to be checked.

## **Basic operation**

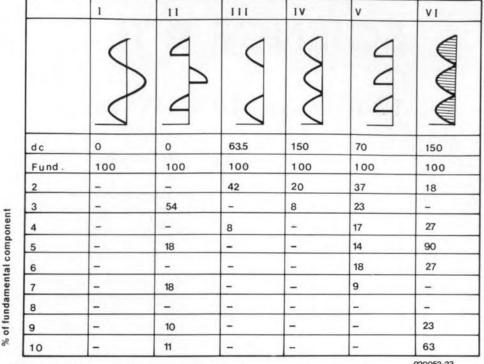

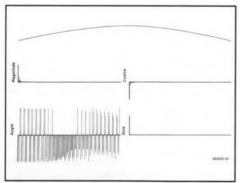

A comb generator is basically a circuit that generates a very short pulse periodically. Its operation is predicted (or, if you like, confirmed), by Fourier analysis.

Assuming that a purely digital pulse is generated with a duty factor of 1% ( $t_{on}/t_{off}=0.01$ ), the amplitudes of the harmonics are weighted to (sin *x*)/*x* (sine roll-off). This means that

- the amplitude of the first couple of harmonics will be 1% of that of the original pulse;

- the amplitude does not drop to:

- -1 dB up until the 26th harmonic;

- -2 dB up until the 37th harmonic;

- -3 dB up until the 44th harmonic;

- -5 dB up until the 55th harmonic;

- -10 dB up until the 74th harmonic.

The attenuation will be infinite (in principle) at the 100th harmonic, and multiples thereof. In practice, the deviation from the theoretical model is small (for a change), in particular in the HF section of the present generator.

## **Circuit description**

The recently introduced family of AC (Advanced CMOS) logic devices allows very fast pulses to be generated at relatively high output power levels. Here, the fundamental generator frequencies are 1 MHz (HF mode) and 10 MHz (VHF mode).

## HF pulse generator

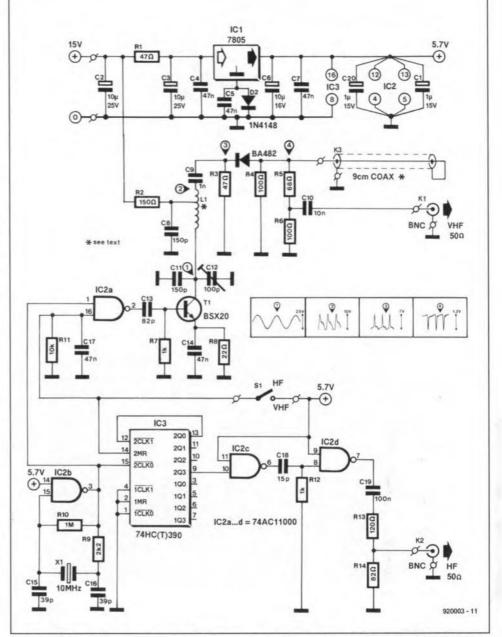

With reference to the circuit diagram in Fig. 1, when switch S1 is set as shown, the VHF part of the circuit is disabled via gate IC2a. One section of dual decade ripple counter IC3 divides the 10-MHz clock signal by 10. The 1-MHz output signal is buffered

by an ACL gate, IC<sub>2</sub>c, to make sure that the signal edges are sufficiently steep. The output of the buffer is loaded with an *R*-*C* network that results in 7.6-ns long 'low' levels of the 1-MHz (1  $\mu$ s) output signal. A further ACL gate, IC<sub>2</sub>d, is used to provide sufficient drive power at the HF output, K<sub>2</sub>. Capacitor

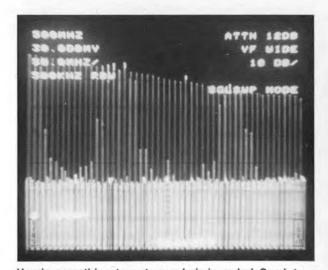

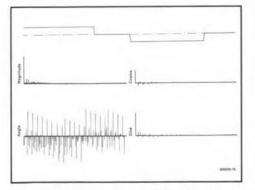

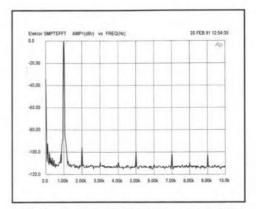

Here's something to put your hair in order! Comb-type output spectrum from DC to about 1 GHz (VHF mode).

C19 in combination with resistors R13 and R14 provides a termination impedance of about 50  $\Omega$ .

The use of AC logic means that the duty factor of the output signal depends to a small extent on the supply voltage and the ambient temperature. Fortunately, this does not seem

to be a problem for the first tens of harmonics, whose level was found to remain virtually constant. Here, a slightly higher than normal IC supply voltage is used (5.7 V) to keep duty factor reduction as small as possible. Remember, the speed of the gates increases with the supply voltage, so that the duty factor would become smaller; this in turn would cause a lower pulse level.

The -3 dB roll-off frequency of the HF section lies at about 50 MHz. The first minimum occurs at about 130 MHz. The output level, about -25 dBm, will be sufficient for most applications (in RF design, 0 dBm equals 1 mW into 50  $\Omega$ ).

The level of the multiples of the second harmonic may deviate by a maximum of  $\pm 3$  dB. This effect may be reduced to a minimum by decoupling the 74AC11000 supply pins. If necessary, relocate C1 (a 1-µF tantalum capacitor) from its normal position on the board to the underside, where it is soldered directly across the supply pins of the 74AC11000.

### VHF pulse generator

When VHF mode is selected with switch S1, divider IC3 is disabled to prevent subharmonics occurring in the output spectrum. The clock buffer is followed by a fast switching transistor Type BSX20 (T1), which is operated in class C. The transistor stage produces a 10-MHz output signal with a power of about 50 mW. The transistor drives the pulse shaper proper via an inductor, L1.

An old trick is rehashed to generate a pulse with a very short, accurately defined, length. Here, 1 ns  $(1 \times 10^{-9} \text{ s})$  is required. The pulse shaper is formed by a short-circuited length of 50- $\Omega$  coax cable plus a fast diode. The length of the coax cable is calculated from

$$\frac{1}{2} \cdot 0.6 \cdot 3 \times 10^8 \cdot 1 \times 10^{-9} = 0.09 \text{ m}.$$

in this equation, the factor 0.6 is the velocity factor of the coax cable, and  $3 \times 10^8$  is the speed of light in a vacuum.

A number of diodes were tried out in position D1. Remarkably, the inexpensive and fairly common Type BA482, a VHF band switching diode, was found to give the best results.

The output level of the VHF section is about -20 dBm. This level drops by -2 dB at about 200 MHz, and by -8 dB at about 400 MHz. The first minimum occurs at about 1 GHz, the second at 2 GHz, etc. This means that no further filters are required to prevent base line shift when the comb generator is used with the popular HP8551 spectrum analyser.

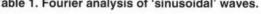

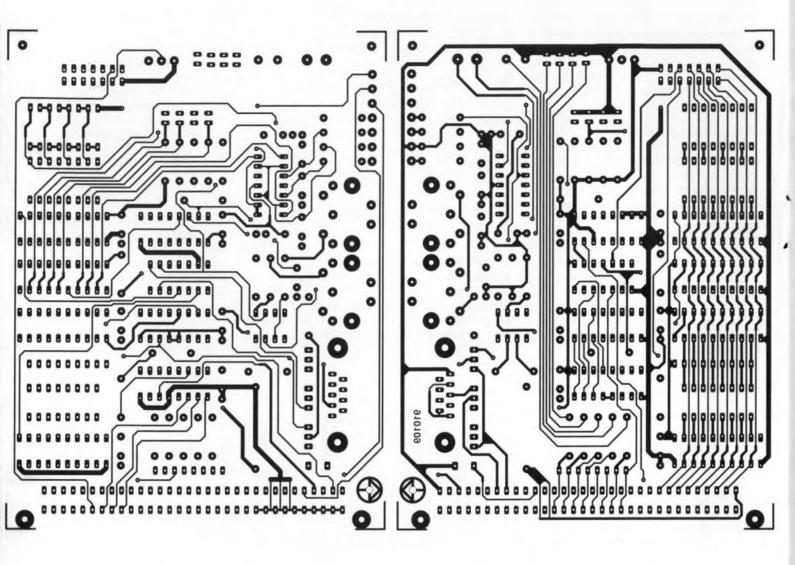

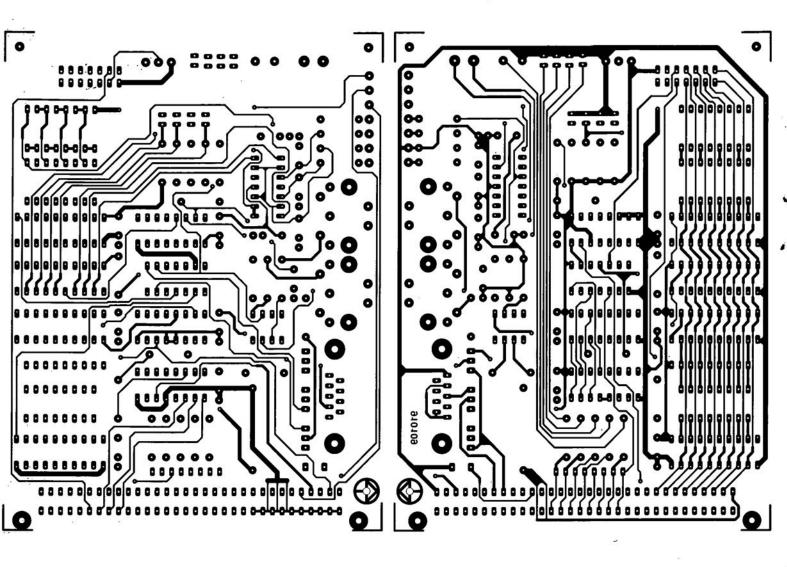

## Construction

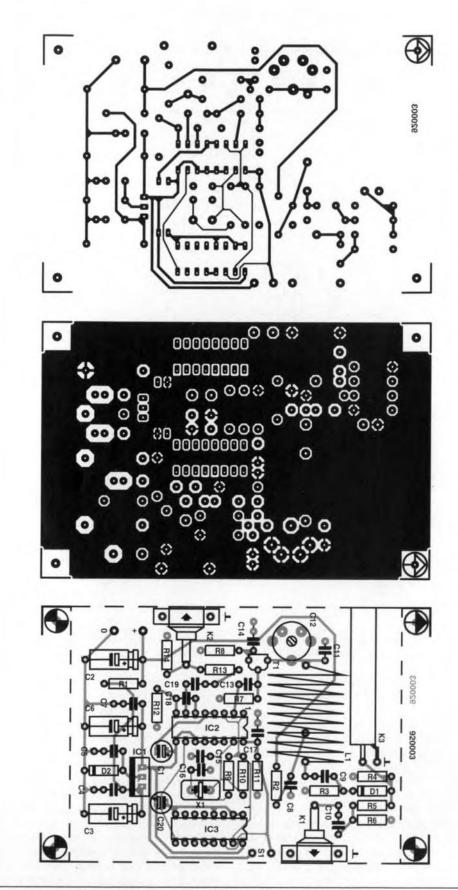

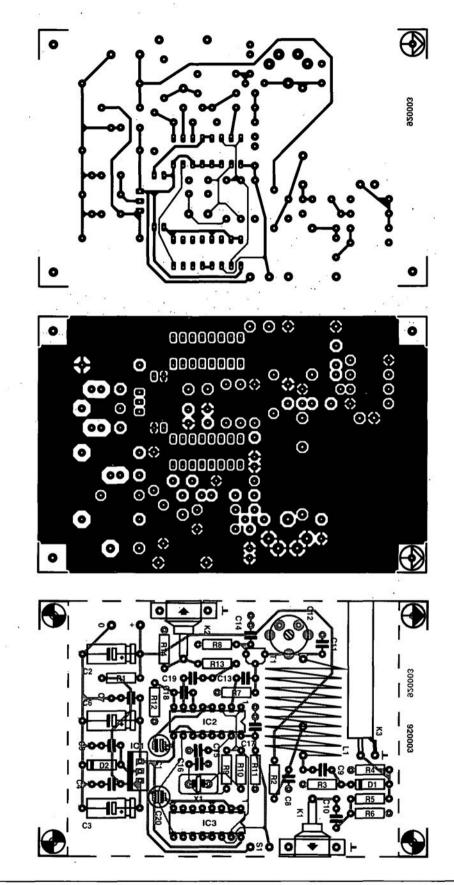

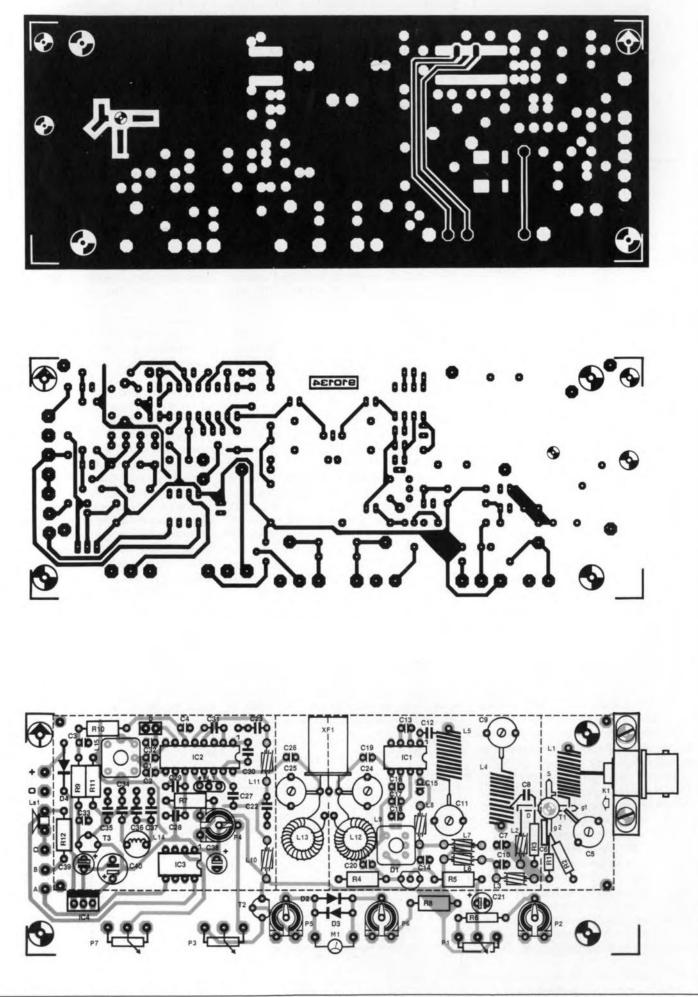

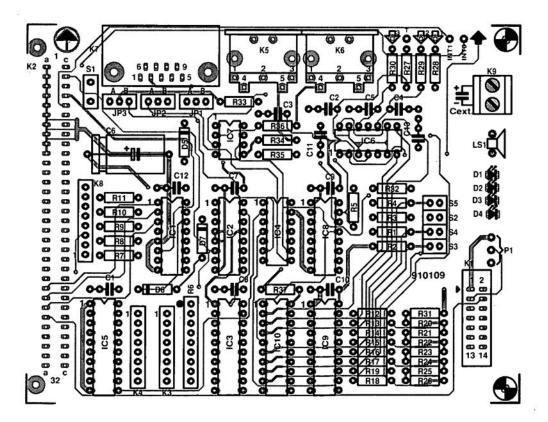

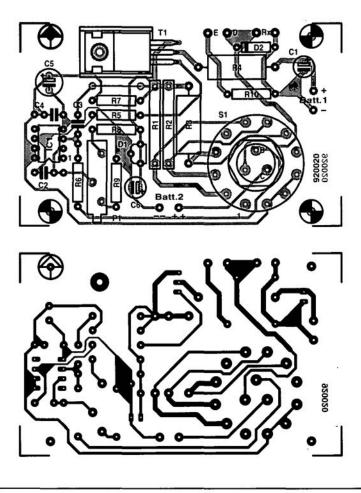

The repeatability of the circuit is pretty good when constructed on the printed circuit board shown in Fig. 2. All parts are fitted with the shortest possible lead lengths. The metal film resistors are preferably from the SFR25 series (Philips Components). All nonelectrolytic capacitors are ceramic types, al-

Fig. 1. Circuit diagram of the comb generator. The 1-ns pulse shaper in the VHF section is formed by a piece of coax cable and a fast switching diode.

though MKT or polycarbonate will also work for the larger values (47 nF and 100 nF).

Do not use sockets to fit the ICs, and take care not to overheat the trimmer and the quartz crystal when soldering. The centre pins of the BNC sockets, K1 and K2, are soldered directly on to the board, and the threaded parts of the shafts are secured to the PCB with a clamp.

The coax stub is cut to a length of 9 cm. One end is short-circuited, the other soldered to the points marked 'K3' on the PCB (the coax braid is soldered direct to the PCB ground plane).

The inductor, L1, consists of 9.5 turns of 1 mm dia. (SWG20) silver-plated wire. The inductor has an internal diameter of about 21 mm, and is conveniently wound on a tube lighting starter. Wind the 9.5 turns closespaced, and remove the former you have used. Next, draw out the coil, and spread the turns evenly (introductory photograph). A tap is made at 3 turns from one side. Solder the inductor on to the PCB, and correct the spacing if necessary. Make sure that the turns can not touch the ground plane at the component side of the board, and fix them with a small amount of candle wax.

The circuit must be screened all around by a 25-mm high piece of tin-plate. The shape of the screen is indicated by the dashes on the printed circuit board. Drill an 8-mm hole to enable the coax stub to pass through, and two 9-mm holes for the BNC sockets. Solder the screen securely to the board with the aid of a powerful soldering iron. The screen and the PCB together form a box, for which a lid is easily made from a 75×95-mm piece of tin plate (bend approx. 2.5-mm at the four edges to enable it to be clamped on to the screen on the PCB). The lid is drilled to hold the HF/VHF switch. The positive power supply connection is preferably made via a 1-nF feedthrough capacitor fitted into one of the sides of the box. The unit thus made may be fitted into another, larger, enclosure that may also contain the 15-V power

Fig. 2. Double-sided printed circuit board design for the comb generator.

supply. Alternatively, you may want to fit the PCB into a diecast (Eddystone) enclosure, from which the BNC sockets protrude.

The unit must be powered by a regulated 15-V source. A 'classic' supply based on the 7815 will be adequate for this purpose. Current consumption is smaller than 50 mA.

## Adjustment

The adjustment of the comb generator is straightforward, and involves only one trimmer. Connect a spectrum analyzer to the VHF output, and peak C12 for highest signal level. Lacking a spectrum analyzer, connect

|     | COMPONEN                                                                |           |

|-----|-------------------------------------------------------------------------|-----------|

| Re  | sistors:                                                                |           |

| 2   | 47Ω                                                                     | R1;R3     |

| 1   | 150Ω                                                                    | R2        |

| 2   | 100Ω                                                                    | R4;R6     |

| 1   | 68Ω                                                                     | R5        |

| 2   | 1kΩ                                                                     | R7;R12    |

| 1   | 22Ω                                                                     | R8        |

| 1   | 2kΩ2                                                                    | R9        |

|     | 1MΩ                                                                     | R10       |

| 1   | 10kΩ                                                                    | R11       |

| 1   | 120Ω                                                                    | R13       |

| 1   | 82Ω                                                                     | R14       |

| Ca  | pacitors:                                                               |           |

| 1   | 1µF 15V tantalum                                                        | C1        |

|     | 10µF 25V                                                                | C2;C3     |

| 5   | 47nF ceramic                                                            | C4;C5;C7; |

|     |                                                                         | C14;C17   |

| 1   | 10µF 16V                                                                | C6        |

| 2   | 150pF ceramic                                                           | C8;C11    |

| 1   |                                                                         | C9        |

| 1   | 10nF ceramic                                                            | C10       |

| 1   | 100pF trimmer                                                           | C12       |

| 1   | 82pF ceramic                                                            | C13       |

| 2   |                                                                         | C15;C16   |

| 1   |                                                                         | C18       |

| 1   | 100nF ceramic                                                           | C19       |

| 1   | 1µF 16V radial                                                          | C20       |

|     | luctor:                                                                 |           |

| L1  | Made from 1-mm dia. (<br>silver-plated wire; for c<br>details see text. |           |

|     |                                                                         |           |

| Se  | miconductors:                                                           |           |

|     | BA482                                                                   | D1        |

| 1   | 1N4148                                                                  | D2        |

| 1   | BSX20                                                                   | T1        |

| 1   | 7805                                                                    | IC1       |

| 1   | 74AC11000N                                                              | IC2       |

| 1   | 74HC(T)390                                                              | IC3       |

| Mis | scellaneous:                                                            |           |

| 2   | BNC socket                                                              | K1;K2     |

|     | cm RG58 50Ω coax, vel                                                   |           |

| 1   | miniature on/off switch                                                 | S1        |

| 1   | 10MHz quartz crystal                                                    | X1        |

| 1   | Printed circuit board                                                   | 920003    |

an oscilloscope via a 10:1 probe to the collector of T1 (test point '1'). Adjust C12 for best sine shape and highest amplitude of the waveform. In most cases, this adjustment will be entirely satisfactory, although the trimmer may have to be set to a slightly larger capacitance afterwards to compensate the probe capacitance.

Finally, for advanced users: if you require a smaller frequency interval, change the divisor (IC3; VHF output), or (better) change the crystal frequency. In most cases, it will also be necessary to change the pulse duration appropriately; if this is not done, the output level will almost certainly drop. Note, however, that although increasing the pulse duration keeps the output power at the old level, it lowers the maximum usable frequency.

Fig. 2. Double-sided printed circuit board design for the comb generator.

supply. Alternatively, you may want to fit the PCB into a diecast (Eddystone) enclosure, from which the BNC sockets protrude.

The unit must be powered by a regulated 15-V source. A 'classic' supply based on the 7815 will be adequate for this purpose. Current consumption is smaller than 50 mA.

## Adjustment

The adjustment of the comb generator is straightforward, and involves only one trimmer. Connect a spectrum analyzer to the VHF output, and peak C12 for highest signal level. Lacking a spectrum analyzer, connect

|         | COMPONE                 | 15      |           |  |

|---------|-------------------------|---------|-----------|--|

| Re      | sistors:                |         |           |  |

| 2       | 47Ω                     | R1;R    | 3         |  |

| 1       | 150Ω                    | R2      |           |  |

| 2       | 100Ω                    | R4;R    | 6         |  |

| 1       | 68Ω                     | R5      |           |  |

| 2       | 1kΩ                     | R7;R    | 12        |  |

| 1       | 22Ω                     | R8      |           |  |

| 1       | 2kΩ2                    | R9      |           |  |

| 1       | 1MΩ                     | R10     |           |  |

| 1       | 10kΩ                    | R11     |           |  |

| 1       | 120Ω                    | R13     |           |  |

| 1       | 82Ω                     | R14     |           |  |

| Ca      | apacitors:              |         |           |  |

| 1       | 1µF 15V tantalum        | C1      |           |  |

|         | 10µF 25V                | C2;C    | 3         |  |

| 5       | 47nF ceramic            | C4;C    |           |  |

| 2       |                         | C14;    | C17       |  |

| 1       | 10μF 16V                | C6      |           |  |

| 2       | 150pF ceramic           | C8;C    | 11        |  |

| 1       | 1nF ceramic             | C9      |           |  |

| 1       | 10nF ceramic            | C10     |           |  |

| 1       | 100pF trimmer           | C12     |           |  |

| 1       | 82pF ceramic            | C13     |           |  |

| 2       | 39pF ceramic            | C15;    | C16       |  |

| 1       | 15pF ceramic            | C18     |           |  |

| 1       | 100nF ceramic           | C19     |           |  |

| 1       | 1µF 16V radial          | C20     |           |  |

| In      | ductor:                 |         | ·         |  |

| L1      | Made from 1-mm dia      | . (SWG2 | 20)       |  |

|         | silver-plated wire; for |         |           |  |

|         | details see text.       |         |           |  |

| Se      | miconductors:           |         |           |  |

|         | BA482                   | D1      |           |  |

| 1       | 1N4148                  | D2      |           |  |

| 1       | BSX20                   | T1      |           |  |

| 1       | 7805                    | IC1     |           |  |

| 1       | 74AC11000N              | IC2     |           |  |

| 1       | 74HC(T)390              | IC3     |           |  |

| Mi      | scellaneous:            | •       |           |  |

|         | BNC socket              |         | K1;K2     |  |

| 2       | cm RG58 50Ω coax, v     |         | actor 0.6 |  |

| 2       |                         | 1       | 04        |  |

| 2       | miniature on/off swite  | n       | S1        |  |

| 2<br>10 |                         |         | X1        |  |

an oscilloscope via a 10:1 probe to the collector of T1 (test point '1'). Adjust C12 for best sine shape and highest amplitude of the waveform. In most cases, this adjustment will be entirely satisfactory, although the trimmer may have to be set to a slightly larger capacitance afterwards to compensate the probe capacitance.

Finally, for advanced users: if you require a smaller frequency interval, change the divisor (IC3; VHF output), or (better) change the crystal frequency. In most cases, it will also be necessary to change the pulse duration appropriately; if this is not done, the output level will almost certainly drop. Note, however, that although increasing the pulse duration keeps the output power at the old level, it lowers the maximum usable frequency.

## AD232 CONVERTER

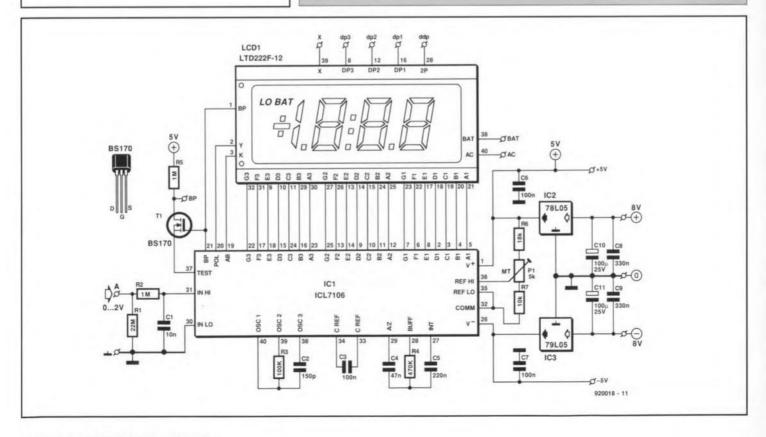

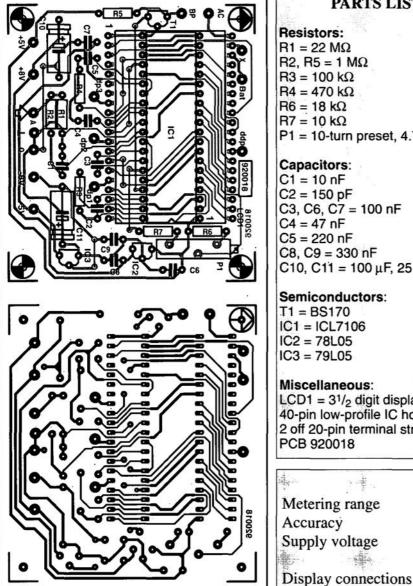

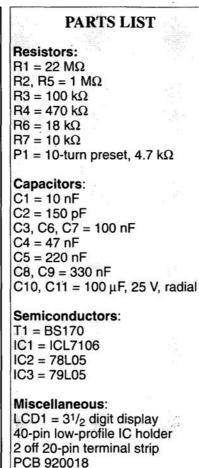

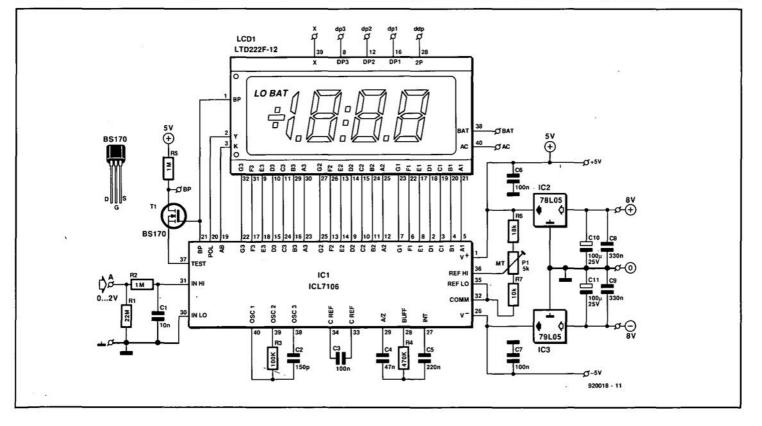

The well-known ICL7106 A-D converter IC has been with us in many generations of digital multimeter. A special version of it, the ICL7109, offers the same accuracy, comes at a low price also, but sports a parallel interface instead of a 7-segment driver. The ICL7109 requires only a handful of components to

build a versatile measuring box with an RS232 interface that is easy to manage thanks to some hardware tricks. Software for IBM PCs and compatibles is available to control this unit, which is basically a multiplexed A-D converter with an RS232 interface.

## Design and software by Ing. B.C. Zschocke and A. Arnold

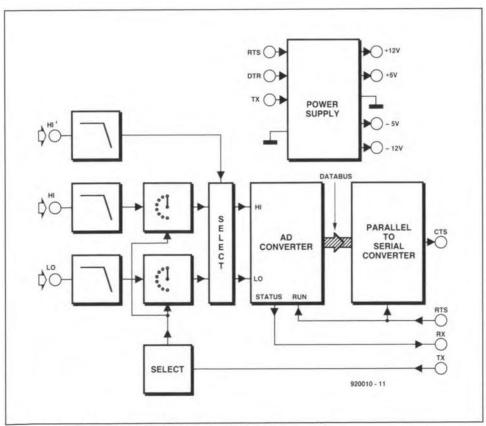

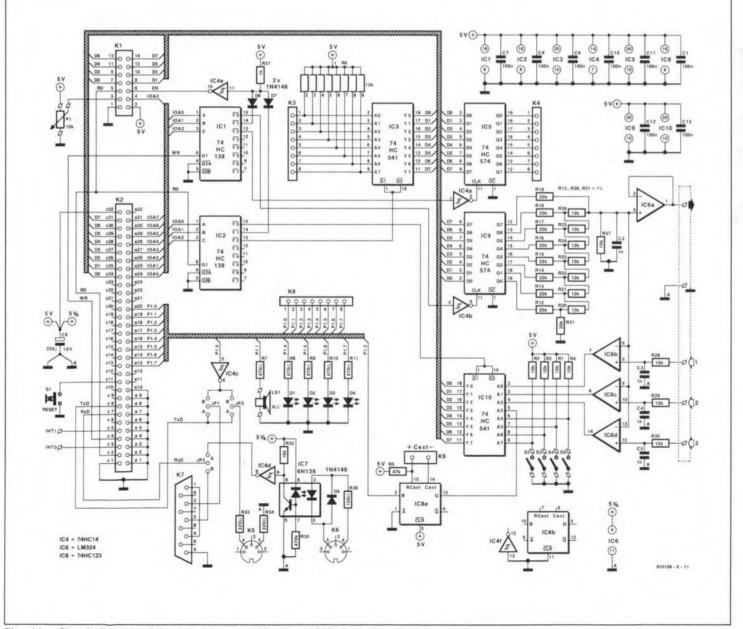

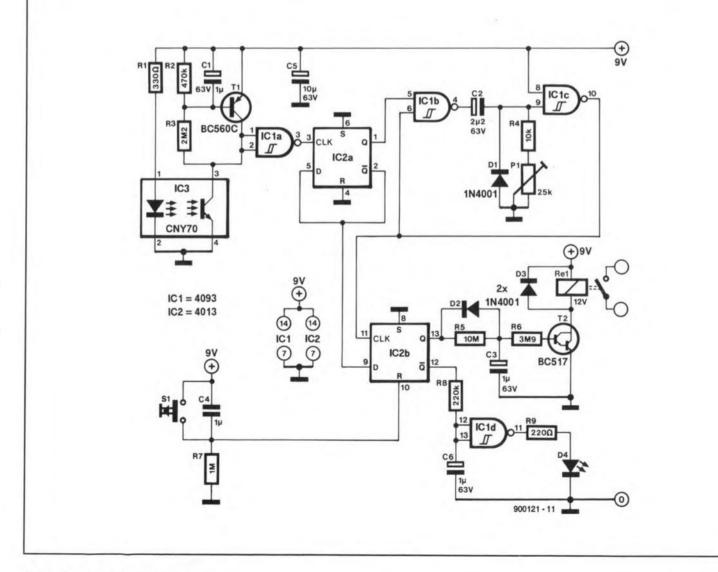

**T**HE concept of the circuit is illustrated in the block diagram in Fig. 1. At the left are three input blocks with low-pass filter characteristics, marked HI', HI and LO. The HI and LO blocks represent eight input channels, each of which can be selected individually by the block marked 'select'. The part behind the input selection circuitry

Fig. 1. Block diagram of the RS232-controlled A-D converter.

**ELEKTOR ELECTRONICS APRIL 1992**

## MAIN SPECIFICATIONS

- · For every PC with a serial port

- · 16-channel input multiplexer

- 12-bit A-D converter

- Powerful graphics-based menu-driven control software

- Based on inexpensive ICs

- · Powered by PC

allows switching between the HI' (direct) input and the switchable inputs.

The A-D (analogue-to-digital) converter behind the input circuitry supplies its digital output data to a parallel-to-serial converter via a parallel bus. Unusually, the output information of the format converter is connected the CTS (clear to send) handshaking line of the RS232 port, rather than the RxD (received data) line. This arrangement results in a much simpler control of the measuring box than would be possible if the RxD line were used.

The circuit is powered by the RS232 port on the PC. The power supply block shown in the diagram provides a regulated output voltage of  $\pm 5$  V for the converter, and  $\pm 12$  V (approximately) for the serial interface.

## Connection problems

The serial (RS232) interface is used here because the parallel (Centronics) interface can not furnish enough current to power the RS232 A-D converter. Furthermore, in most cases it is easier to find a free serial port on a PC than a free Centronics port, while the use of longer cables is also a boon. On the down side, a serial link is much slower than a parallel link, so that relatively slow ADCs can be used only. Fortunately, this is not always a disadvantage, because slow but very accurate ADCs are inexpensive and widely available. Also, it is not always necessary to

## TEST AND MEASUREMENT

sample slowly varying measuring quantities at kHz rates.

The ICL7109 ADC used here differs from the ubiquitous ICL7106 by the digital interface only. The input circuitry is almost identical for both ICs.

Interface parameters can be a real problem when implementing an RS232 link and keeping to the standards. For instance, the link will work correctly only if the transmitter and the receiver are set to the same data format (number of data bits and start/stop bits), but also to the same data rate (in bits per second, or baud). Many of you will know the difficulties and frustrations in setting up a serial link, with obstacles such as DIP switches, configuration files, MODE commands, and long series of parameters.

Here, the RS232 link is used in a nonstandard way to avoid some of the problems mentioned above. Data is conveyed via CTS, and clocked by another handshaking line, RTS (ready to send). Four good reasons can be given for this choice:

- The control software determines when and how fast data is conveyed. It is not necessary to configure the serial port. This is particularly attractive when the interface is used for several different peripherals.

- Conveying data via a 'standard' RS232 link requires either special interfacing circuits with internal or external oscillators, or complex discrete alternatives.

- The AD232 board can be linked to interfaces that are not fully RS232 compatible, or directly to a microcontroller.

- The component count is quite low.

## Details

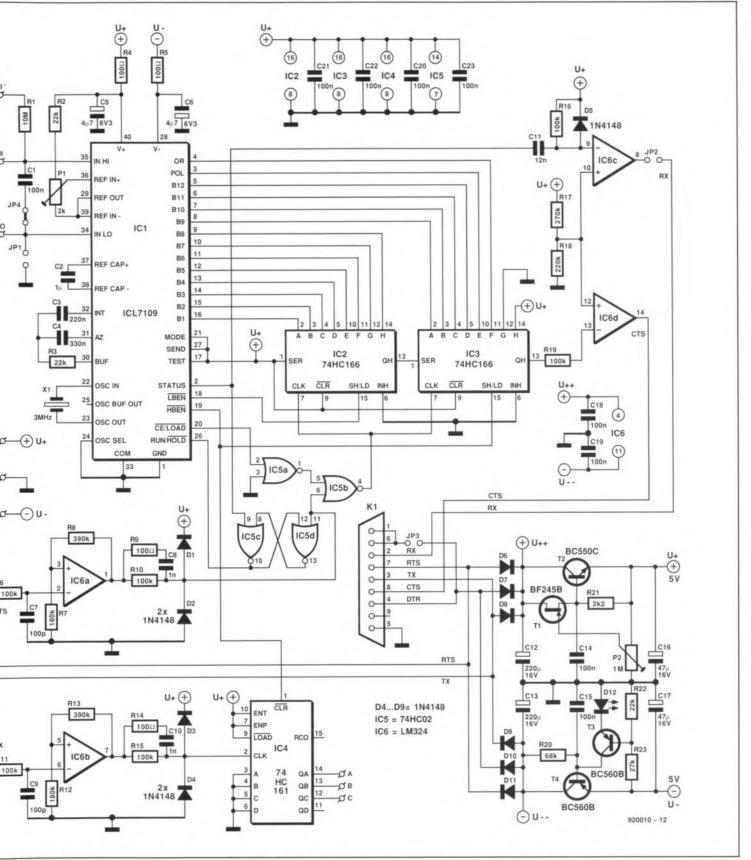

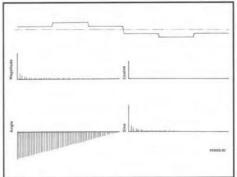

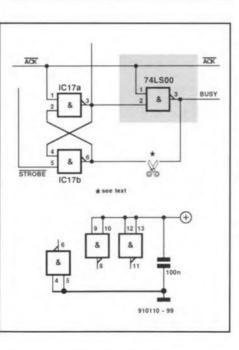

The circuit diagram is given in Fig. 2. A quadruple opamp, IC6, forms the RS232 interface. Circuits IC4, IC7 and IC8 form a simple input multiplexer. IC1 is the ADC proper. The two 74HCT166s, IC2 and IC3, form a 16-bit shift register for the parallel-toserial conversion. The four XOR gates in the 74HC02 package, IC5, control the timing of the A-D conversion, and generate a clock signal for the shift registers.

The power supply takes its input voltage from the RS232 interface in the PC, and provides the stabilized ±5 V rails for the convercircuitry. The analogue-to-digital ter conversion starts when a level transition is detected at the RTS input. Opamp IC6a makes the RTS signal TTL compatible, and its output signal causes bistable IC5c-IC5d to toggle. The high level at pin 10 of IC5 triggers the A-D conversion in IC1. When the conversion result is available, the ICL7109 supplies a LOAD signal to the shift register, IC2, via gates IC5a and IC5b. First, the high (most significant) byte is loaded into IC2, then the low (least significant) byte into IC3. The signals HBEN (high byte enable) and LBEN (low byte enable) are treated in an unusual manner here. When low, these signals switch the associated register from shifting to loading. Because HBEN and LBEN can never be low

Fig. 2. Circuit diagram of the measurement system. The two input multiplexers are optional, a

at the same time, and the clock inputs of the registers are interconnected, this results in the shift registers being in opposite mode all the time, i.e., when one loads, the other shifts. This has no significance for the loading of the high byte, while the high byte is shifted one position in IC3 during loading. Bits 7 and 8 in the high byte, which are not used by the converter, are made permanently high. This is done to bring about a

level change on the CTS line after the shifting, when the low byte is loaded. This change can be used as an interrupt request in the PC, or as a 'conversion ready' status signal when the CTS line is 'polled' (i.e., continuously monitored).

Before the software can read the content of the shift registers with the aid of 16 clock pulses on the RTS line, it is necessary to wait 1.5 clock cycles (about 30  $\mu$ s) for the LBEN

## **ELEKTOR ELECTRONICS APRIL 1992**

18

AD232 CONVERTER

19

structed on separate printed circuit boards. Note that the entire circuit is powered via the RS232 link to the PC.

signal to return to high. This time can be used, for instance, to switch the multiplexer to the right channel.

The function of the bits in the datastream is shown in Table 1. The first clock pulse sets bistable IC5c-IC5d. This causes the RUN input to return to logic high, whereupon the A-D converter starts a new conversion cycle. The bistable is reset by a high level on the status line of IC1 (pin 2). The high level at the serial input of the low-byte shift register ensures that the output returns to high (-12 V on the CTS line) after the value has been read.

## The ICL7109

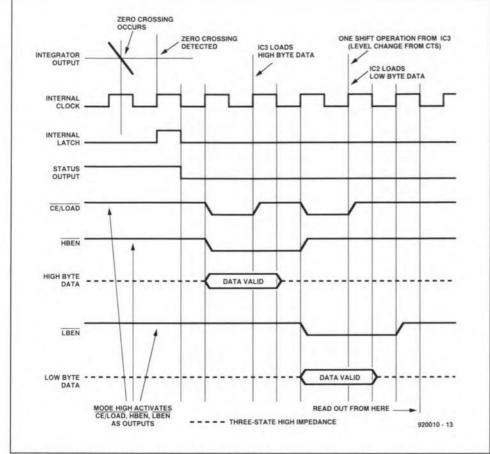

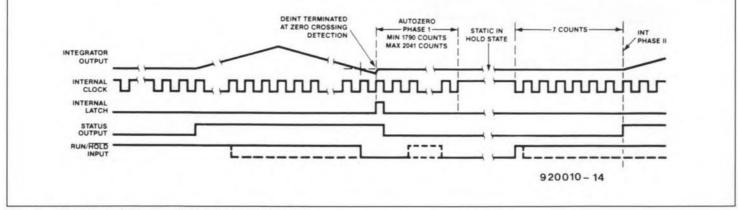

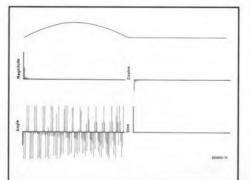

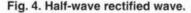

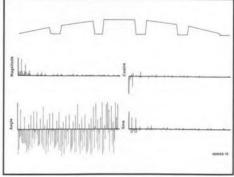

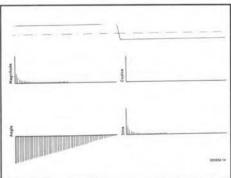

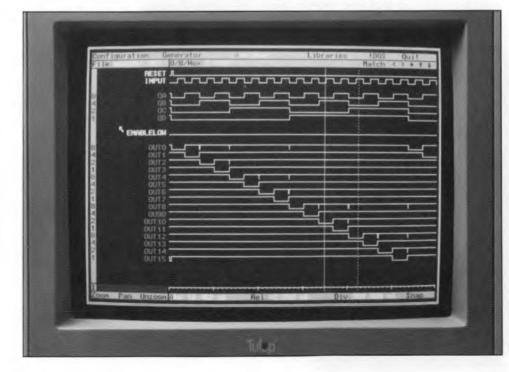

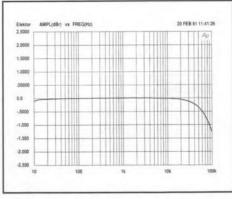

The ICL7109 is a low-cost 12-bit dual-slope A-D converter with additional polarity and overflow outputs. Figs. 3 and 4 shed light on

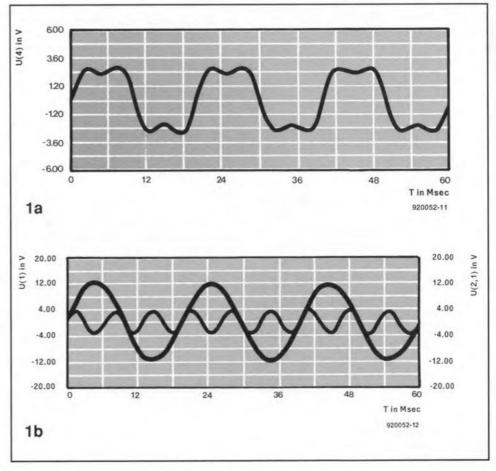

the operation of the digital part of the converter. First, Fig. 4: the upper signal represents the voltage at the capacitor (C3; the component numbers in brackets refer to the actual circuit). Below, some signals of the ICL7109, the internal clock, the clock signal of the output latch, the status output and the RUN/Hold input.

The conversion is started when a high level appears at the RUN input. During the

### **ELEKTOR ELECTRONICS APRIL 1992**

Fig. 3. Timing diagram of the data and command transfer protocol used.

conversion, the status output is held logic high. First, the integrator capacitor (C3) is charged with a current,  $I_c$ :

$I_{\rm c} = (U_{\rm HI} - U_{\rm LO})/{\rm R3}.$

This takes 2,048 internal clock cycles (oscillator frequency divided by 58). Subsequently, C3 is discharged with a constant current,  $I_{d}$ , that is proportional to the input voltage:

$$I_{\rm d} = U_{\rm ref}/R_3.$$

During the discharging, the number of internal clock pulses is counted. The first leading edge of the internal clock that occurs after the capacitor voltage drops below 0 V causes the counter state to be transferred to the output register. Next, the status output changes from high to low, and so indicates the end of the conversion. Thus, we have: counter state =  $2,048 U_{in}/U_{ref}$ .

If the RUN input remains high during the conversion, a new conversion cycle is started after the auto-zero phase. Conversely, if RUN remains low, the new conversion starts 7 internal clock pulses after a new high level is present.

Figure 3 illustrates the handshaking of the ICL7109 with the external circuits, when the Mode and Sense inputs are held logic high. To the signals shown in Fig. 4 are added LOAD, HBEN, LBEN and the data lines. A low level on HBEN signals the presence at the output of the high byte of the counter state and the status signals Overrun and Polarity. The high byte can be copied on the leading edge of the LOAD signal. The subsequent transfer of the low byte is similar.

| Clock on RTS | Function       |

|--------------|----------------|

| 1            | Overrun (OR)   |

| 2            | Polarity (POL) |

| 3            | B12            |

| 4            | B11            |

| 5            | B10            |

| 6            | B9             |

| 7            | High           |

| 8            | B8             |

| 9            | B7             |

| 10           | B6             |

| 11           | B5             |

| 12           | B4             |

| 13           | B3             |

| 14           | B2             |

| 15           | B1             |

| 16           | High           |

The input of the ICL7109 may be considered symmetrical within the bounds of the supply voltage, and has an input resistance of the order of a few giga-ohms. To make sure that sufficient charge reserve is available for the switches in the analogue part of the converter, the voltage source to be measured must be buffered by a low-loss capacitor. This means that capacitor C1 must be connected in parallel with the two inputs when measurements are made without the multiplexer. This is achieved by fitting jumper J4. For measurements on symmetrical voltages, the voltages (with reference to ground) at the two inputs must lie within the bounds of the supply voltage of the ICL7109. For asymmetrical measurements, the LO input can be tied to ground by fitting jumper J1. Resistor R1 prevents discharging via the measured voltage source.

## More inputs, more channels

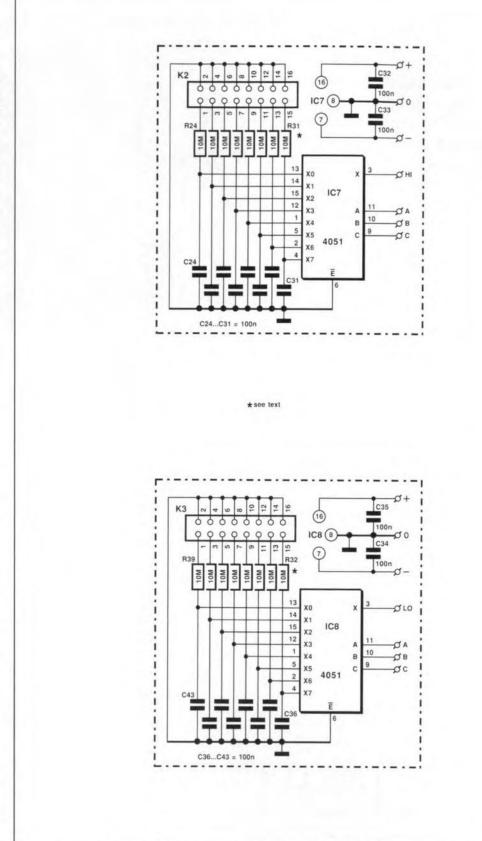

A multiplexer is provided for those of you who want to measure more than one voltage source. The multiplexer consists of IC7 for the selection of the Hi line, and IC8 for the se-

Fig. 4. ICL7109 analaogue-to-digital conversion timing.

lection of the Lo line. Both are controlled by IC4, which counts the clock pulses on the Tx line. To select a channel, the software puts certain characters on the Tx line, such that the total number of clock pulses corresponds to the desired channel (see the programming example 'setchannel' listed in Fig. 5). The set baud rate is irrelevant, but the (rarely used) parity function must be taken into account. To ensure a fixed starting configuration, the counter is automatically reset to channel 1 after each conversion.

When the multiplexer is used, capacitor C1 must be disconnected from the input (J4 is not fitted), and the ground reference must be raised (J1 is not fitted). Capacitors C24-C31 and C36-C43 then take over the function of C1.

|     | COMPONEN                                | TO EIOT        |

|-----|-----------------------------------------|----------------|

| Re  | sistors:                                |                |

| 17  | 10MΩ                                    | R1;R24-R39     |

| 3   | 22kΩ                                    | R2;R3;R22      |

|     | 100Ω                                    | R4;R5;R9;R14   |

|     | 100kΩ                                   | R6:R10:R11:R15 |

|     |                                         | R10;R19        |

| 2   | 180kΩ                                   | R7;R12         |

| 2   | 390kΩ                                   | R8;R13         |

| 1   | 270kΩ                                   | R17            |

| 1   | 220kΩ                                   | R18            |

| 1   | 68kΩ                                    | R20            |

| 1   | 2K122                                   | R21            |

| 1   | 27kΩ                                    | R23            |

| 1   | $2k\Omega$ multiturn preset             | P1             |

| 1   | $1M\Omega$ multiturn preset             | P2             |

| Ca  | pacitors:                               |                |

| 19  | 100nF                                   | C1;C14;C15;    |

|     |                                         | C18-C43        |

| 1   | 1μF                                     | C2             |

|     | 220nF                                   | C3             |

| 1   | 330nF                                   | C4             |

| 2   | 4µF7 6V3 tantalum                       | C5;C6          |

|     | 100pF                                   | C7;C9          |

| 2   | 1nF                                     | C8;C10         |

|     | 12nF                                    | C11            |

|     | 220µF 16V radial                        | C12;C13        |

| 2   | 47μF 16V radial                         | C16;C17        |

|     | miconductors:                           |                |

|     | 1N4148                                  | D1-D11         |

|     | green LED                               | D12            |

|     | BF245B                                  | T1             |

|     | BC550C                                  | T2             |

|     | BC560B                                  | T3;T4          |

|     | ICL7109                                 | IC1            |

|     | 74HC166                                 | IC2;IC3        |

|     | 74HC161                                 | IC4            |

|     | 74HC02                                  | IC5            |

| 1   | LM324                                   | IC6            |

| 2   | 4051                                    | IC7;IC8        |

| 379 | miconductors:                           |                |

| 1   | 9-way PCB-mount ferr<br>sub-D connector | nale<br>K1     |

| 2   | 16-way pin header                       | K2;K3          |

| 1   | 3-MHz quartz crystal                    | X1             |

| 1   | Printed circuit board                   | 920010         |

| 1   | Control program on di                   | sk ESS1691     |

| CONST                                                     |                    |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------|--------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PosOver=MaxInt;<br>NegOver=-MaxInt                        | ; ( va<br>; ( di   | alue for pos.<br>itto neg. over           | overflow }<br>rflow }                                                                                                                                                                                                                                                                                                                                                                                               |

| /AR<br>SIOAdr:Word;                                       | ( e.               | be assigned<br>.g. COM1: SIO<br>COM2: SIO | with 8250 base address )<br>Adr:=\$3f8 ]<br>Adr:=\$2f8 ]                                                                                                                                                                                                                                                                                                                                                            |

|                                                           |                    |                                           | )                                                                                                                                                                                                                                                                                                                                                                                                                   |

| set channel for                                           | next convers       | sion: )                                   |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROCEDURE                                                 | SetChannel (       | Channel:Byte)                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PulseBytes:ARRA                                           | Y[15] OF H         | Byte=(0,14,51                             | ,21,85); { -> 1 - 5 pulses to TX }                                                                                                                                                                                                                                                                                                                                                                                  |

| PROCEDURE                                                 | WaitTx;            |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| { wait until tr<br>REPEAT UNTIL Po<br>END;                |                    |                                           | free }                                                                                                                                                                                                                                                                                                                                                                                                              |

| BEGIN<br>IF Channel>5 TH<br>BEGIN                         | EN (2              | characters r                              | equired? )                                                                                                                                                                                                                                                                                                                                                                                                          |

| WaitTx; Port[<br>WaitTx; Port[<br>Waittx;                 |                    |                                           | ne1-5];                                                                                                                                                                                                                                                                                                                                                                                                             |

| END<br>ELSE IF Channel<br>BEGIN                           | >0 THEN { 1        | character re                              | quired? }                                                                                                                                                                                                                                                                                                                                                                                                           |

| WaitTx; Port[<br>WaitTx;                                  | SIOAdr]:=Pu        | lseBytes[Chan                             | nel];                                                                                                                                                                                                                                                                                                                                                                                                               |

| END<br>ELSE;                                              | { no ;             | pulse for Cha                             | nnel 0 )                                                                                                                                                                                                                                                                                                                                                                                                            |

| END;<br>Read value from s                                 | hift regist        | ers, Call only                            | y when conversion is ready !!)                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                           | leadAD:Integ       |                                           | ·                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BEGIN                                                     |                    |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8B/\$16/>SIOAdr/                                          | 1 mov              | dx,[SIOAdr]                               | <pre>; DX at SIO-Port } ; and on ModemCtrl there ; ; to switch address ; ; clear shift accu ; ; l4 data +2 dummy clocks ; ; shift to CTS ; ; send pulse via RTS ; ; RTS high ; ; DTR complementary low ; ; set lines ; ; short wait loop, ; ; to allow levels ; ; to settle ; ; and restore ; ; DTR complementary high ; ; reset lines ; ; ensure ; ; mailest pulse length ; ; pass dummy after 7 clocks ; ; </pre> |

| BE/>0002/                                                 | mov                | si,2                                      | ; to switch address )                                                                                                                                                                                                                                                                                                                                                                                               |

| B5/\$10/                                                  | ( mov              | ch,16                                     | ; 14 data +2 dummy clocks }                                                                                                                                                                                                                                                                                                                                                                                         |

| B1/\$04/                                                  | [ mov<br>[@read:in | cl,4<br>al,dx                             | ; shift to CTS }<br>; send pulse via RTS }                                                                                                                                                                                                                                                                                                                                                                          |

| 324/\$FD/                                                 | and                | al,0fdh                                   | ; RTS high )                                                                                                                                                                                                                                                                                                                                                                                                        |

| EE/                                                       | or al,             | dx,al                                     | ; set lines )                                                                                                                                                                                                                                                                                                                                                                                                       |

| 51/<br>109/251F4/                                         | { push             | cx                                        | ; short wait loop, }                                                                                                                                                                                                                                                                                                                                                                                                |

| SE2/SFE/                                                  | 1 loop             | \$                                        | ; to settle )                                                                                                                                                                                                                                                                                                                                                                                                       |

| \$0C/\$02/                                                | ( pop<br>( or      | al,2                                      | ; and restore )                                                                                                                                                                                                                                                                                                                                                                                                     |

| 324/\$FE/<br>SEE/                                         | and out            | al, 0feh<br>dx, al                        | ; DTR complementary high )<br>; reset lines )                                                                                                                                                                                                                                                                                                                                                                       |

| 551/                                                      | ( push             | CX                                        | ; ensure )                                                                                                                                                                                                                                                                                                                                                                                                          |

| 889/>\$1F4/<br>SE2/\$FE/                                  | { nov              | \$                                        | ; smallest pulse length }                                                                                                                                                                                                                                                                                                                                                                                           |

| \$59/<br>\$80/\$FD/\$0A/                                  | f pop<br>cmp       | cx<br>ch,10                               | )<br>; pass dummy after 7 clocks }                                                                                                                                                                                                                                                                                                                                                                                  |

| 574/SOA/<br>503/SD6/                                      | i je               | enuse                                     | DV to MederStatus                                                                                                                                                                                                                                                                                                                                                                                                   |

| SEC/                                                      | { add in           | dx,si<br>al,dx<br>al,cl                   | ; read status bits )                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                           | ( shl<br>( cmc     | al,cl                                     | ; shift CTS bit into carry )<br>; observe Inverting )                                                                                                                                                                                                                                                                                                                                                               |

| SD1/\$D3/                                                 | f rcl              | bx,1                                      | ; shift into result )                                                                                                                                                                                                                                                                                                                                                                                               |

| 32B/\$D6/<br>SFE/\$CD/                                    | { sub { @nuse:dec  | dx, si<br>ch                              | ; DX back to ModemCtrl )<br>; outer loop counter )                                                                                                                                                                                                                                                                                                                                                                  |

| \$75/\$D4/                                                | jnz                | @read                                     | <pre>; shift into result } ; DX back to ModemCtrl } ; DX back to ModemCtrl } ; outer loop counter } } ; shifted once too many } ; change sign } ; overrun set? ; ; yes&gt; ; ; polarity negative? }</pre>                                                                                                                                                                                                           |

| 1001 AF 11 AT 01                                          | I YOT              | DILL TON                                  | , change sign /                                                                                                                                                                                                                                                                                                                                                                                                     |

| 75/\$0D/                                                  | t test             | @Over                                     | ; overrun set? )<br>; yes> }                                                                                                                                                                                                                                                                                                                                                                                        |

| SF6/\$C7/\$10/<br>S74/\$16/                               | test               | bh,10h<br>GWErg                           | <pre>; polarity negative? ) ; no&gt;result o.k. )</pre>                                                                                                                                                                                                                                                                                                                                                             |

| 80/\$F7/\$10/                                             | 1 xor              | bh,10h                                    | ; yes: clear Pol-Flag }                                                                                                                                                                                                                                                                                                                                                                                             |

| SEB/\$0F/\$90/                                            | i neg<br>( jmp     | @WErg                                     | ; and form 2's complement }                                                                                                                                                                                                                                                                                                                                                                                         |

| F6/\$C7/\$10/<br>575/\$06/                                | (@over:test        | bh,10h<br>CONeg                           | <pre>; negative overrun? ) ; ves&gt; )</pre>                                                                                                                                                                                                                                                                                                                                                                        |

| BB/>PosOver/                                              | mov                | bx, PosOver                               | ; constant pos. overflow }                                                                                                                                                                                                                                                                                                                                                                                          |

| BB/>NegOver/                                              | (@ONeg:mov         | bx, NegOver                               | <pre>; overrun set? ) ; yes&gt; } ; polarity negative? } ; no&gt;result o.k. } ; yes: clear Pol-Flag } ;and form 2's complement } } ; negative overrun? } ; yes&gt; } ; constant pos. overflow } ; constant neg. overflow } ; function result = BX }</pre>                                                                                                                                                          |

| END;                                                      | (energemov         | CLOBULC/DA                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| check if a valid                                          | result is a        | available: }                              |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                           | D232_Ready:        | Boolean;                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BEGIN<br>AD232_Ready:=Po<br>SND;                          | rt[SIOAdr+6        | AND 16<>0;                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Initialisation o                                          | f AD232. No        | timeout; end                              | less loop created when AD232 is not foun                                                                                                                                                                                                                                                                                                                                                                            |

| AR                                                        | AD232_Init;        |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dummy:Integer;<br>BEGIN<br>Port[SIOAdr+4];<br>Delay(100); | =2;                | { only DTR                                | low )<br>oltage to stabilize )                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                           | 232 Ready:         | ( wait for fi                             | rst result                                                                                                                                                                                                                                                                                                                                                                                                          |

| REFERT UNTIL AT                                           |                    | man w and the                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |

Fig. 5. A 'bare bones' control program for the converter (Pascal with in-line assembler).

## TEST AND MEASUREMENT

22

The multiplexers also allow symmetrical measurements to be made within the bounds of the converter's supply voltage. When asymmetrical measurements are performed, the inputs of multiplexer IC9 must be tied to ground, for instance, by fitting jumpers on header K3.

Unfortunately, the 4051 and the high converter input resistance of the converter introduce an offset voltage that differs from channel to channel. Although the asymmetrical construction reduces the effect of the offset to a minimum, it can not be eliminated completely. For very accurate measurements, this means that the multiplexer must either not be used, or replaced by one with better specifications. For 'everyday' use, however, a correction in software of the measured voltage with the aid of a zero calibration is perfectly adequate.

## RS232 level changer

The four opamps in IC6 are used as voltage level converters. Actually, they function as inverting switches, and so provide the inverting function defined in the RS232 standard. Diodes D1-D4 and resistors R10 and R15 limit the signal to +5 V and ground. *R*-C combinations R9-C8 and R14-C10 ensure that the input capacitances formed by IC5 and IC4

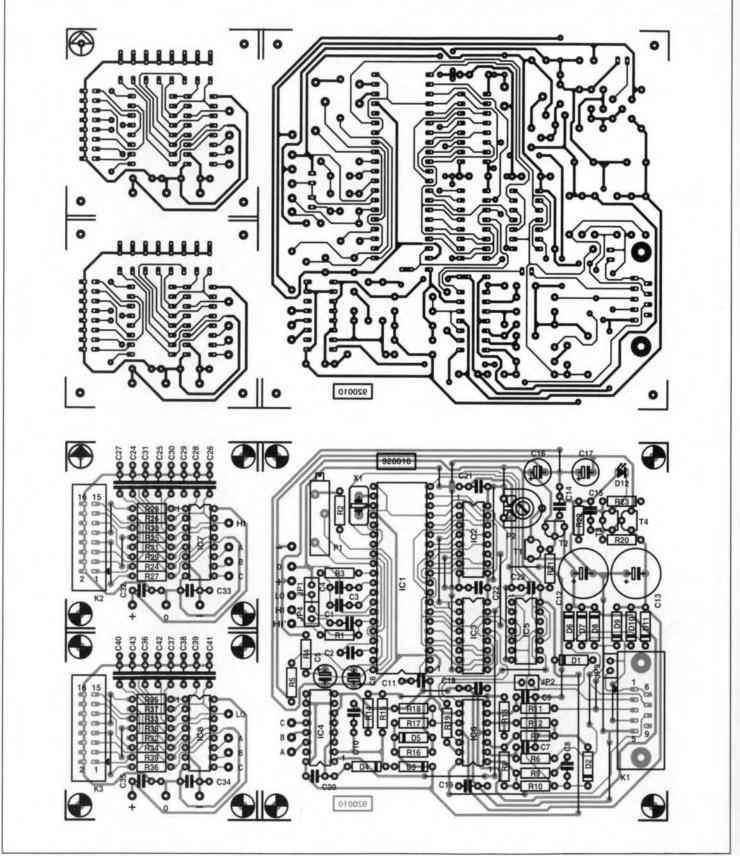

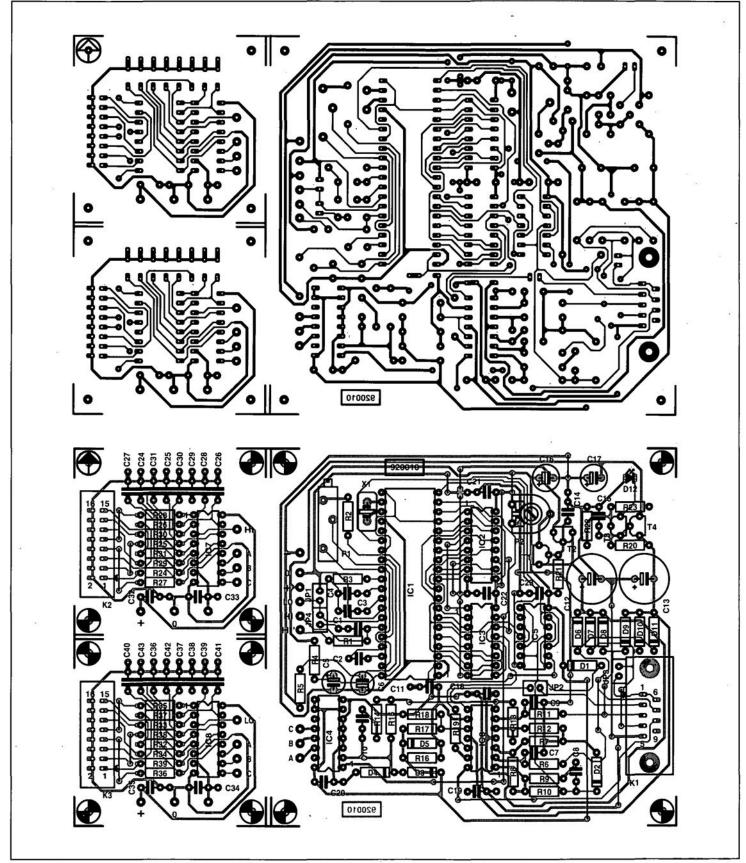

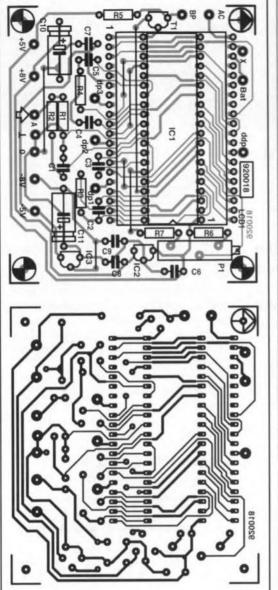

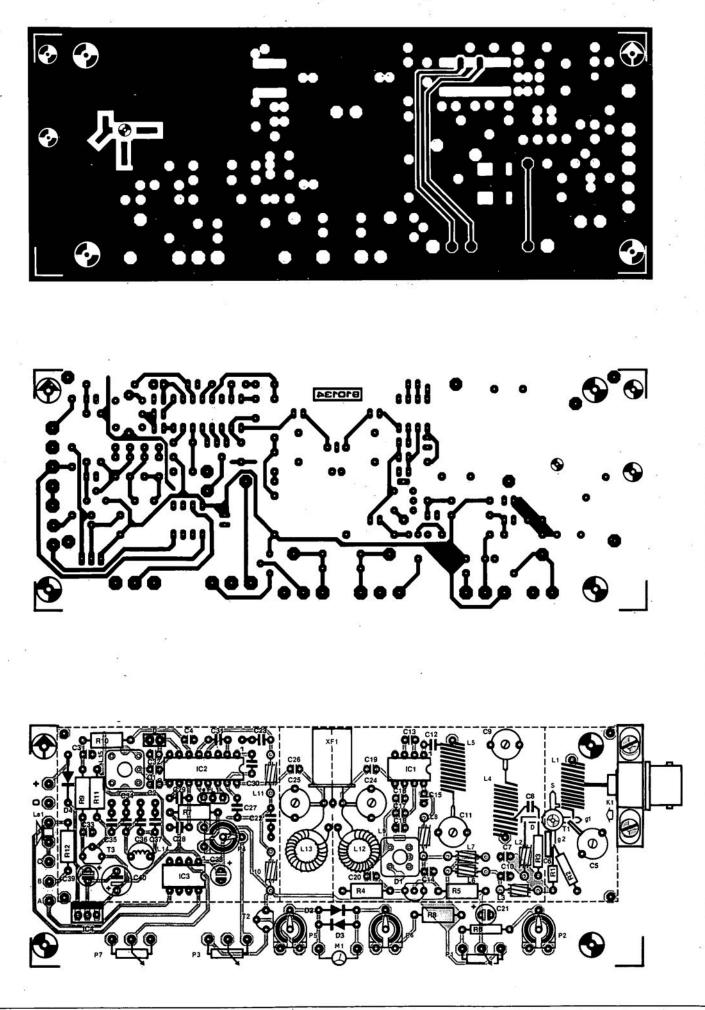

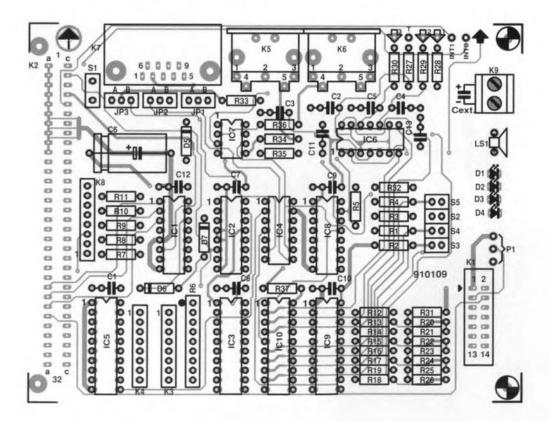

Fig. 6. Single-sided printed circuit board (track layout and component mounting plan) for the AD232.

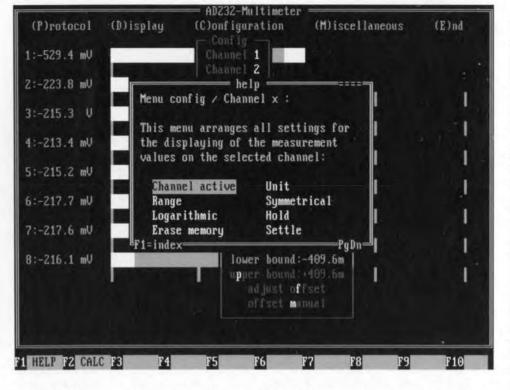

This program is completely menudriven, runs in colour, accepts mouse as well as keyboard control, and is written to run on IBM PCs and compatibles, from XTs to 486based machines. A colour video card (EGA or VGA) is not strictly required, although you will miss a lot of the presentation graphics' power when you have monochrome video only.

#### Installation

The program can be run from floppy disk or hard disk. When it is run from floppy disk, make sure the write protection is removed, because the program writes a configuration file on the disk. An installation proper is not required—simply copy all files to your working disk, or to the hard disk.

### Running the program

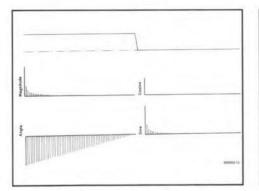

The AD232 control program is started by typing MULTI from the DOS prompt. First, go the (M)iscellaneous option, and select the serial port to which the AD232 board is connected. On leaving this menu, the voltmeter should work, indicating the voltages on all eight channels by means of horizontal bars and an absolute readout. (see Fig. 7). When fewer than eight channels are used, the screen is automatically enlarged.

### **Options** (configuration menu)

The channel settings are not limited to switching on and off. Measuring ranges, multipliers and units (mV; V, etc.) can be taken into account in the graphics readout. The bar that indicates the magnitude of the measured voltage can be asymmetrical or symmetrical, and linear or logarithmic. Use 'symmetrical' for measured quantities that can go positive and negative. The menu also includes program options for offset calibration and a smoothing (delta) factor to stabilize the display.

### Protocol

Apart from being shown on the screen in the form of horizontal bars, the measured values may also be sent to a file or an output device such as a printer. All output is in straight ASCII to a simple protocol, which makes further processing by other software easy.

#### Extras

All screen elements (text, highlighted text, borders, background) can be displayed in a number of user-selectable colours (VGA/EGA). Irrespective of your whereabouts in the program, a scientific (UPS compatible) desktop calculator and context sensitive help are always to hand. The help texts used in the program are stored in a file called MULTI.HLP, which is generated by adding WINHELP.TXT and MULTI-HLP.TXT on the diskette, as explained in README.DOC. All files and menus are in English.

need not charge via R10 and R15, and so reduce the effects of the relatively low slew rate of the opamps. Opamp IC6c is not strictly required for the correct function of the circuit. However, fit jumper J2 if you wish to feed the 'end of conversion' signal to your PC via the RxD line (for use with an appropriate interrupt routine).

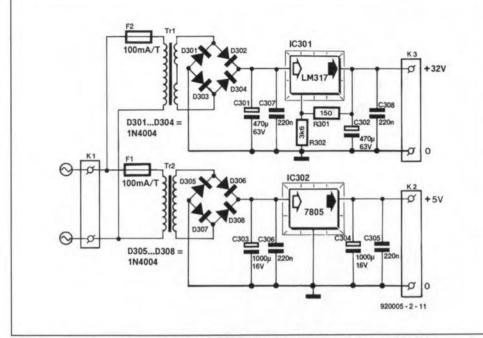

## Power supply

As already mentioned, the AD232 board is powered by the RS232 port of the computer it is connected to. The minimum requirement for this to be achieved is that the PC holds one RS232 line at +12 V and another at -12 V. Since the TxD line is at -12 V when it is not active, the +12 V supply will have to be supplied by the RTS and/or the DTR line. Diodes D6-D11 and capacitors C12 and C13 add and buffer the line levels to provide two discrete regulators with their input voltages. The voltage across the capacitors is also used to power the quadruple opamp. By omitting jumper JP3, the loading of the interface can be made as small as possible, if it can not supply enough current.

The voltage regulators in the ±5 V supply are low-drop, high efficiency, types built from discrete components. The negative regulator consists of a pseudo-zener diode with a series transistor formed by T3 and a green LED, D12. Adjustment of the negative output voltage is not necessary because the A-D converter has a fairly large negative voltage range. Not so with the positive supply, where the pinch-off voltage of a FET serves as the reference. Although this voltage is reasonably stable, it has a fairly high device tolerance, and needs to be adjusted with the aid of P2. To save on parts, protection against overvoltage as a result of an incorrect adjustment is not provided. This means that the wiper of P2 must be turned to ground before calibrating the AD232 board.

The +5-V voltage must be adjusted with the nominal load connected.

## Construction and adjustment

The single-sided PCB designed for the circuit is shown in Fig. 6. The construction will be mostly plain sailing. The multiplexers are built as separate units, and connected to the ADC proper in accordance with the component overlay. The HI' input serves for initial tests without the multiplexer. It is important to ensure adequate screening of all signal lines—remember, the high input resistance makes the circuit sensitive to noise. Hum suppression will be optimum when a quartz crystal of 2.969600 MHz is used. Unfortunately, this is not a standard frequency, whence the use of a 3-MHz crystal here.

The adjustment of the ADC by P1 depends on the application. In principle, the fine adjustment can be done by programming. The external circuitry around the ADC is designed for a maximum input voltage of about 400 mV. For other voltages, R3 must be changed:

### $R_3 = U_{max}/20 \,\mu A.$

The reference voltage,  $U_{ref}$ , should be a little higher than  $U_{max}/2$ , because the converter produces an overflow when  $U_{max} \ge 2U_{ref}$ .

Connect the AD232 board to the PC, and advance preset P2 slowly until the positive regulator supplies +5 V.

## The software package

Although the routines listed in Fig. 5 can be expanded into a full-blown control program for the AD232 board, you will be pleased to know that such a program is available on a disk supplied that can be ordered through our Readers Services (order code 1691).

## TEST AND MEASUREMENT

22

The multiplexers also allow symmetrical measurements to be made within the bounds of the converter's supply voltage. When asymmetrical measurements are performed, the inputs of multiplexer IC9 must be tied to ground, for instance, by fitting jumpers on header K3.

Unfortunately, the 4051 and the high converter input resistance of the converter introduce an offset voltage that differs from

channel to channel. Although the asymmetrical construction reduces the effect of the offset to a minimum, it can not be eliminated completely. For very accurate measurements, this means that the multiplexer must either not be used, or replaced by one with better specifications. For 'everyday' use, however, a correction in software of the measured voltage with the aid of a zero calibration is perfectly adequate.

## RS232 level changer

The four opamps in IC6 are used as voltage level converters. Actually, they function as inverting switches, and so provide the inverting function defined in the RS232 standard. Diodes D1-D4 and resistors R10 and R15 limit the signal to +5 V and ground. *R*-C combinations R9-C8 and R14-C10 ensure that the input capacitances formed by IC5 and IC4

Fig. 6. Single-sided printed circuit board (track layout and component mounting plan) for the AD232.

**GENERIC ARRAY LOGIC (GAL)**

## based on an original article by D. Gembris

In the development of Programmable Array Logic (PAL) devices, the design target was to make available to the user/designer as many 'free' logic gates on the device as possible. Lattice Semiconductor Corporation has further developed the device into the Generic Array Logic—GAL. In essence, both devices are electrically erasable CMOS memory ICs that provide the user with reconfigurable logic and bipolar performance. This makes the GAL suitable for a wide variety of applications. Note that a PAL IC can be programmed only once, whereas a GAL IC can be programmed time and again. This makes the use of GAL ICs much more cost effective than PAL ICs.

The internal design of GALs is practically identical to that of PALs: both devices have a large programmable AND matrix to which a number of fixed OR gates may be connected. The connections between the AND and OR gates are made in silicon. In contrast, a PROM (Programmable Read Only Memory) has a fixed AND matrix and programmable OR gates.

## The design

The availability of EEPROM (Electrically Erasable Read Only Memory) ICs was of fundamental importance in the development of GAL ICs. Apart from being erasable and reprogrammable, the GAL ICs from Lattice are guaranteed for a minimum of 100 erasure/write cycles with data retention up to 20 years.

To further make the user's life easy, GAL ICs have provision for an individual 'signature' of up to eight bytes. This may be used, for instance, to give the device a specific code.

Like PAL devices, GAL ICs can be protected against unwanted reading by actuating a specific cell (through the software). It must be said, however, that this protection is much more effective in PAL than in GAL devices. This is because the fusing of a link in a PAL IC is permanent, whereas in a GAL IC it can be erased, after which the device can be reprogrammed or read.

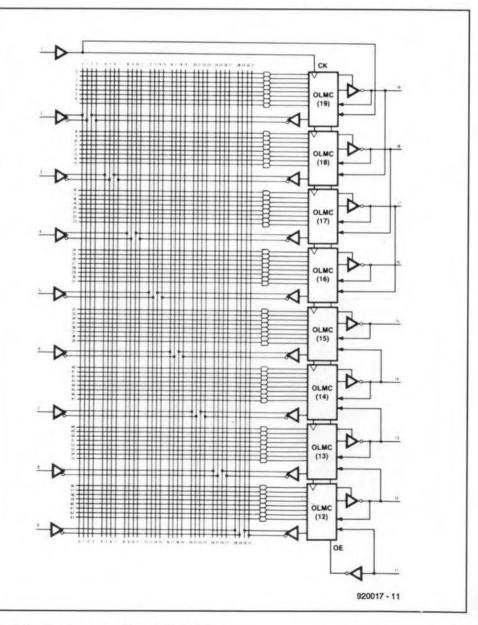

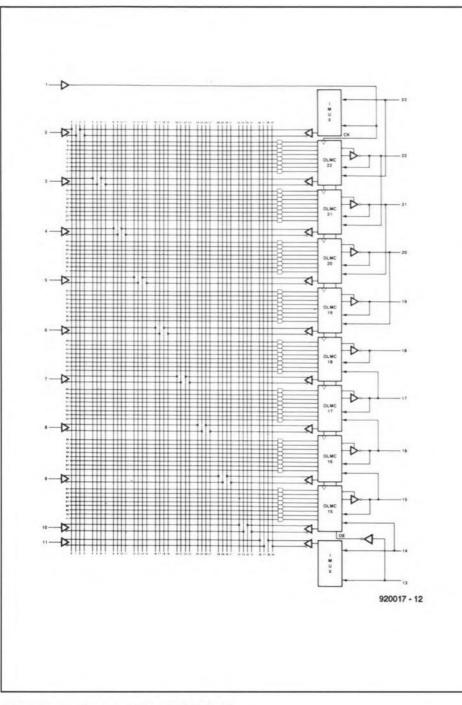

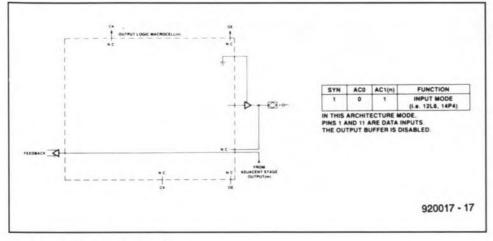

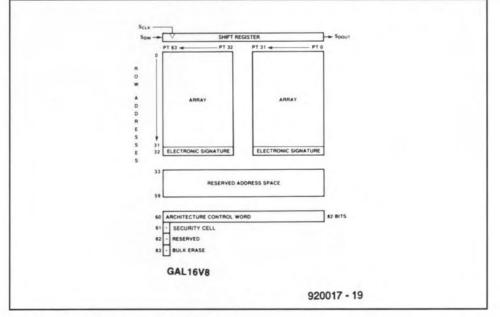

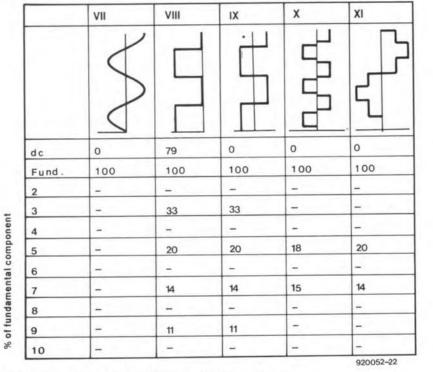

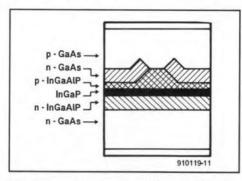

The logic diagram of a Type 16V8 GAL IC is shown in Fig. 1 and that of a Type 20V8 in Fig. 2. Each type has 8 programmable output logic macrocells (OLMCs) that allow the user to configure each output as desired. The figures in the type numbers refer to the design: the first, 16 or 20, is the number of inputs, and the second, the number of outputs.

The following data refer to the 16V8 (see Fig. 1). The eight inputs (pins 2–9) are available at the AND matrix in either original or inverted form and thus give rise to 16 columns. The other 16 columns are connected to the outputs, which are also inverted or non-inverted. There are thus a total

of 32 signals available.

When the IC is erased, there is no contact between the 64 rows (eight OR-gated rows per output) and the 32 columns. Therefore, changes at the inputs have no effect on the outputs. Only when programming is begun will the connections be restored. Each connection represents an AND gate.

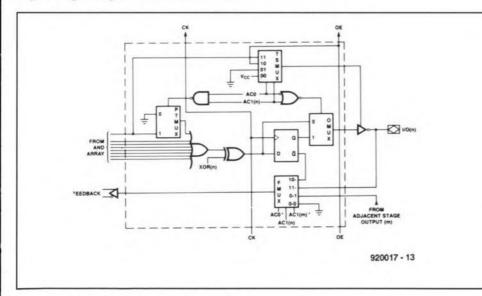

## Output Logic Macro Cells

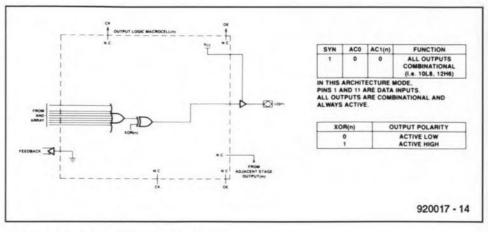

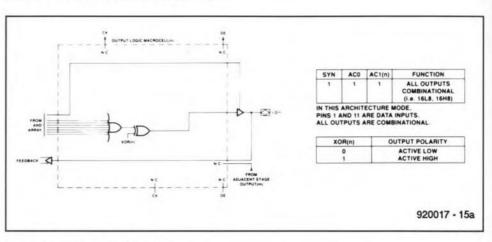

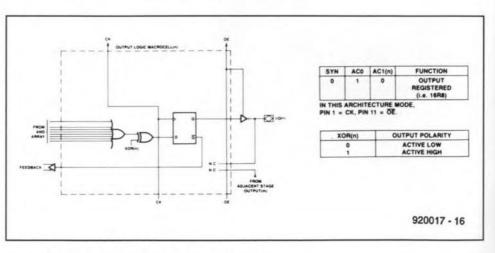

The key to the universality of GAL ICs lies in the *output logic macro cells* (OLMCs). The design of such a cell is shown in Fig. 3. The distinct configuration of an OLMC is laid down in an *Architecture Control Word* (see Fig. 10). Bits SYN, AC0 and AC1(n) determine the status of the output of the cell. The SYN and AC0 bits take effect on all outputs simultaneously, but the AC1(n) bit can be set for each output individually. Because of this, only two of the four possible configurations can be realized in a GAL IC at the same time as shown below.

Normal output—SYN=1;AC0=0; AC1(n)=0 (Fig. 4).

Three-state output with disable via a product term and output return. Of the eight rows, only the lower seven are OR-gated, while the eighth determines whether the result will be shown at the output or not. SYN=0 or 1; AC0=1; AC1(n)=1 (Fig. 5).

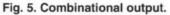

*Three-state output* with disable, output return and register. The result will be at the output only when a clock pulse is applied to pin 1

Fig. 1. Logic diagram of the 16V8 GAL IC.

Fig. 2. Logic diagram of the 20V8 GAL IC.

Fig. 3. Output Logic Macro Cell of 16V8 GAL IC.

**ELEKTOR ELECTRONICS APRIL 1992**

(CLK) and pin 11 is low. SYN=0; AC0=1; AC1(n)=0 (Fig. 6). There are two possible versions of this output (see Fig. 7)

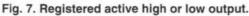

Input: SYN=1; AC0=0; AC1(n)=1 (Fig. 8).

## Programming

Apart from the supply line connections, each pin of a GAL IC has two different functions. Which function is active depends on whether the IC is being programmed (Edit mode) or operates in normal mode. The pin functions of both the 16V8 and the 20V8 are shown in Fig. 9: the inner ones give the Edit mode functions and the outer ones, the normal operating functions. In the Edit mode, which is set by applying 16.5 V DC to pin 2, the IC can be read, programmed or erased.

A GAL IC is internally divided into 64 rows, as shown in the row address map in Fig. 10. There are 36 unique row addresses available to the user when programming the device

Row addresses 0–31 each contain 64 bits of input term data. This is the user array where the custom logic pattern is programmed. Row 32 is the electronic signature word. It has 64 bits available for any user-defined purpose.

Rows 33–59 are reserved by the manufacturer and are not available to the user.