THE MAGAZINE FOR THE RADIO & ELECTRONICS EXPERIMENTALIST May 1990 £1.70

All-waveband ferrite rod antenna Transistor characteristic plotting Intro-scan for CD players Image segmentation Horn loudspeaker A-D converter

#### In next month's issue:

- Mini EPROM viewer

- Electronic load

- Automatic power down

- Four-sensor sunshine meter

- Adaptation of Atari fax for IBM PCs

- Remotely controlled stroboscope

- MIDI master keyboard

- PLL sinewave generator

- Electronic fuses

#### Front cover

Data relay satellites play a vital role in the space communications network, but they are so huge and complex that they are in danger of becoming unmanageable. The tiny detector unit shown in the photograph, designed by SIRA, a leading British research and development company, will play a vital role in a project aimed at reducing both size and complexity. Here, it is being aligned and calibrated after manufacture. The detector, developed in collaboration with British Aerospace, is part of a tracking sensor for a project known as SILEX, due to be launched by the European Space Agency in the early 1990s. The object of this is to develop optical inter-satellite communications links (ISL) that will in future be used to transfer data and commands between the data relay satellites and operational satellites in low orbit. ISLS will also be used to link pairs or groups of geo-stationary communications satellites.

Optical communications are more efficient than a conventional microwave beam, which means that satellites will not need to be so large and will be able to carry far smaller antennas than at present.

SIRA LTD, South Hill, Chislehurst BR7 5EH, England; telephone 081 467 2636.

# CONTENTS

#### LEADER

13

20

60

24

41

Copyright and the SAVE decoder

# AUDIO & HI-FI

- PROJECT: Horn loudspeaker by T. Giffard PROJECT: Intro scan for CD pla

- **PROJECT**: Intro-scan for CD players by J. Ruffell

#### **COMPUTERS & MICROPROCESSORS**

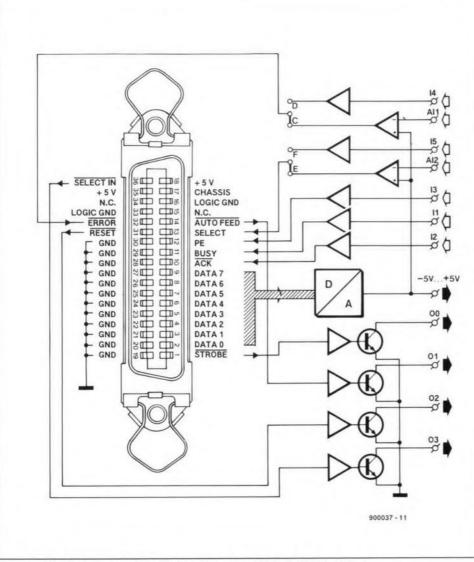

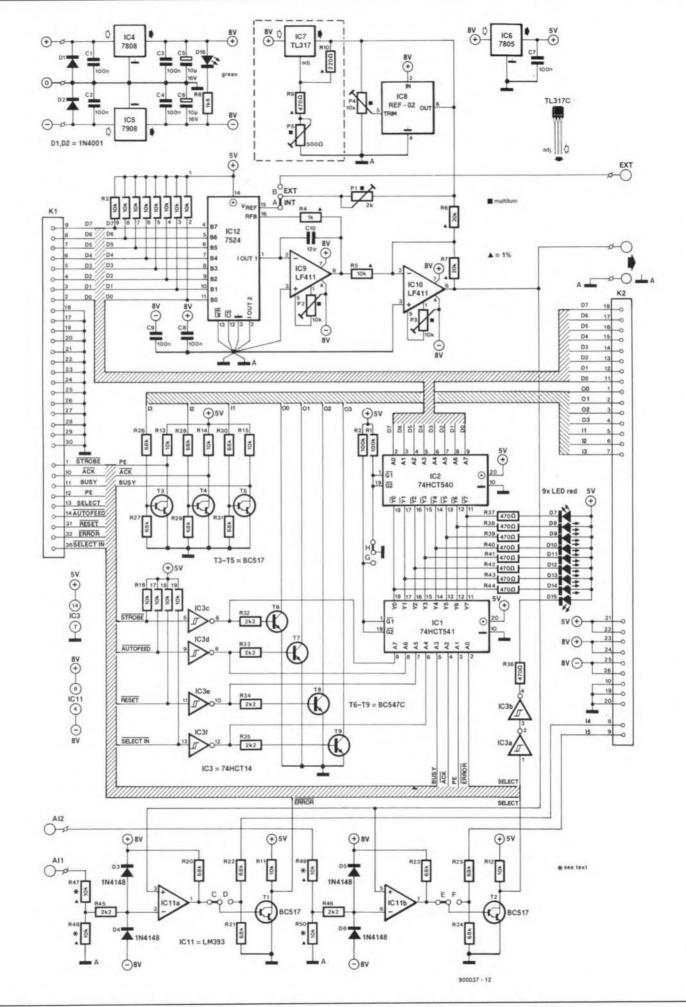

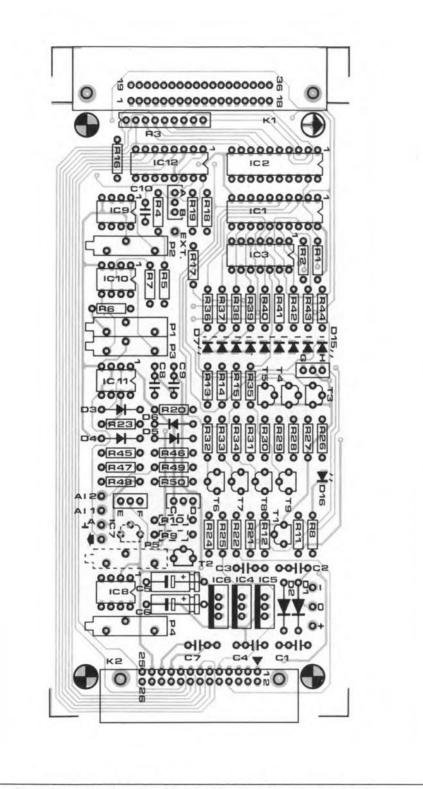

PROJECT: PC servicing card an ELV design PRÓJECT: Centronics A-D/D-A converter by J. Ruffell

#### INTERMEDIATE PROJECT

34 Acoustic temperature monitor by J. Ruffell

# **RADIO & TELEVISION**

The multi-MAC concept by J. Buiting

PROJECT: An experimental all-waveband ferrite rod antenna by Richard Q. Marris, G2BZQ

#### SCIENCE & TECHNOLOGY

46 Image segmentation by M.S. Kishore

#### **TEST & MEASUREMENT**

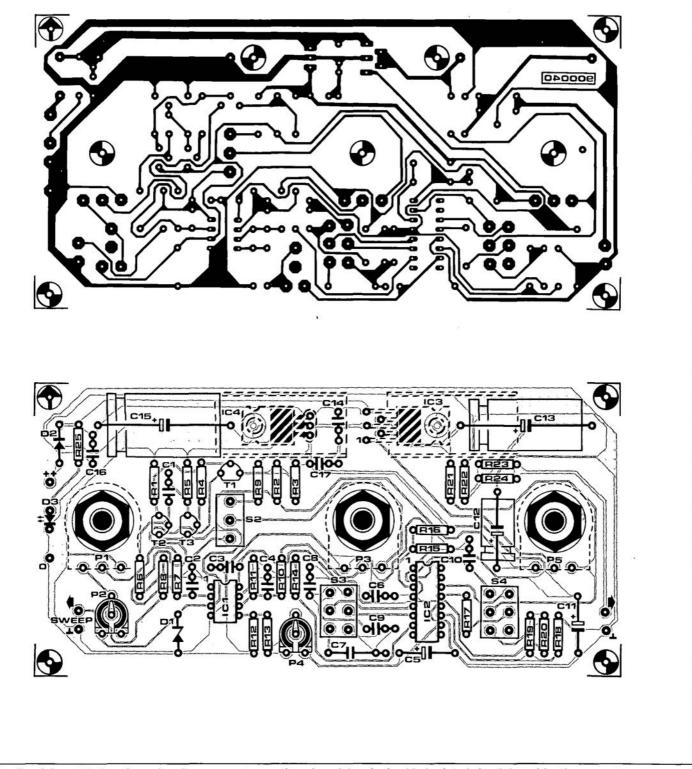

- 50 PROJECT: Budget sweep/function generator by T. Wigmore

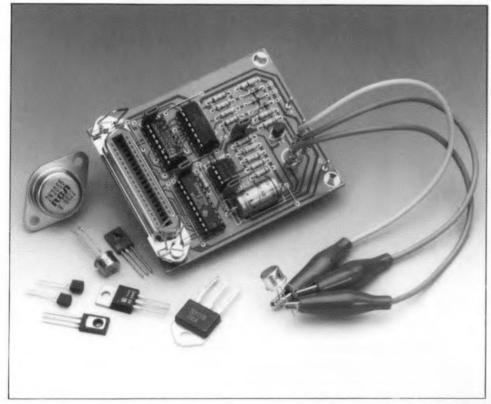

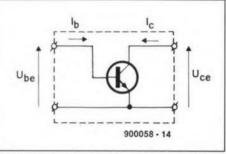

56 PROJECT: Transistor characteristic plotting

- **PROJECT**: Transistor characteristic plotting by S. Aaltonen

# MISCELLANEOUS INFORMATION

Electronics scene 14; Events 36; New books 36; Letters 63; Switchboard 63; Readers services 65; Terms 66; Buyers guide 74; Semi-display adverts 74; Index of advertisers 74

May 1990

Volume 16 Number 178

Profile of Maplin Electronics p. 55

Horn loudspeaker- p. 20

A-D/D-A converter - p. 41

Sweep/function generator - p. 50

# THE MULTI- MALCONCEPT

J. Buiting

ITT's Digit-2000 system has been designed to ensure ready integration of new TV and audio standards with existing hardware concepts. This means that a MAC decoder based on the Digit-2000 system is readily installed into an existing TV set as an upgrade. Provided the necessary control software is available, it is, of course, also possible to use the relevant chip set in a stand-alone application, which is of particular interest to the many thousands of viewers who own satellite-TV receiving equipment. This article introduces the main components that go into the making of such a C/D/D2-MAC compatible decoder.

Intermetall/ITT Semiconductors is among the world's largest producers of components for the consumer electronics market. Since 1985, the company has been involved in the development of MAC decoding systems, and it was the first semiconductor manufacturer to introduce a D2-MAC decoder chip, the DMA2270. The planned use of D-MAC on the BSB services, among other factors, prompted ITT Semiconductors to expand the DMA2270 with a multi-MAC decoding feature. The result is the C-, D- and D2-MAC compatible DMA2280, which, together with the DMA2285 MAC descrambler, forms the heart of the multi-MAC decoder for the Digit-2000 system.

An important point must be made at this stage. When we speak of a MAC decoder, we mean a circuit capable of extracting video and audio information from a signal to the MAC standard. As such, the function of the MAC decoder may be compared to that of, say, an FM decoder. Hence, the use of the word 'decoder' has in principle nothing to do with scrambling, and is really a misnomer. Just like PAL TV signals, or, for that matter, FM radio signals, MAC signals may be encrypted. Since that process has basically nothing to do with the standard of the transmission-only with the way in which the input signal is pre-processed-a separate unit, the MAC descrambler, may be used along with the MAC decoder. As already stated, the associated type numbers in this context are DMA2285 and DMA2280 respectively. The use of the DMA2285 is optional. However, bearing in mind that all BSB channels are encrypted, a MAC descrambling chip like the DMA2285 is a must for all BSB receive units.

# Digit-2000: ready for the future

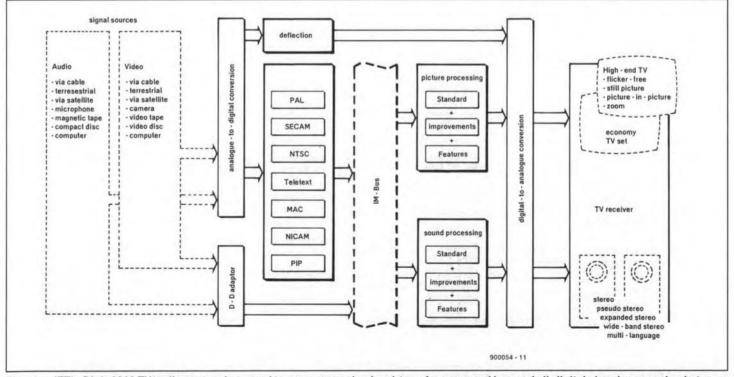

The Digit-2000 concept is illustrated in Fig. 1. Signals travel from the left (signal sources) to the right (sound/picture re-

Fig. 1. ITT's Digit-2000 TV/radio system is geared to easy expansion by virtue of a command bus and all-digital signal processing between an ADC and a DAC.

**ELEKTOR ELECTRONICS MAY 1990**

#### RADIO AND TELEVISION

16

production devices). The intermediate signal processing is entirely digital between an ADC and a DAC. Control signals for the system are conveyed via the IM bus, which is a simple 4-wire network that enables a central or external processor to communicate with the various devices (slaves) connected to the bus. The system is very flexible in that it allows new standards to be implemented readily. Take, for instance, the MAC extension: it is driven by the same ADC, is controlled by the same bus, and uses the same DAC as, say, the PAL circuitry. This means that the system allows both an economy and a topquality TV set to be produced on the basis of three main building blocks: a fast ADC, a control bus, and a fast DAC. Extensions are always possible in this system: the appropriate unit (say, a NICAM processor) is simply connected in parallel with existing circuits and addressed via the IM bus.

# MAC in a nutshell

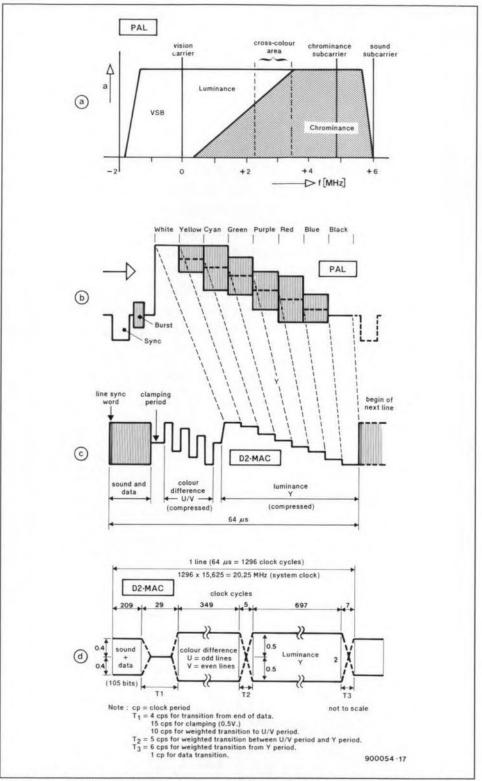

The PAL, NTSC and SECAM colour TV systems currently in use are based on frequency division, which means that the two video components and the sound component are assigned a particular part of the transmitted spectrum. In this system, it is virtually impossible to ensure perfect separation of the luminance ('brightness') and chrominance ('colour') information. Inevitably, signals of both components will encroach upon each other's part of the frequency spectrum -see Fig. 2a. The effect is the well-known moiré patterning in picture areas with relatively fast luminance transitions. The colour processor in the TV receiver mistakes these fast luminance signals in the cross-colour area between about 2.3 MHz and 3.5 MHz (PAL) for colour information, and actuates colours which are not related to the luminance information in the particular picture area.

MAC relies on time division rather than frequency division and gives nearperfect separation of the picture components. Figures 2b and 2c shows how the luminance (Y) picture components in a PAL video signal may be transferred and compressed at a ratio of 3:2 into a time slot in the MAC signal (Ref. 1). The chrominance component (compression ratio: 3:1) is transferred in a similar manner to the time slot preceding the Y period. MAC lines alternately carry the compressed U (B-Y) and V (R-Y) colour difference signals. Note that both Y and U/V are analogue levels. Compression and expansion are required to fit these signals into the available line time, which is 64 µs just as with PAL.

Each line of MAC consists of serial U/V and Y signals, reference periods and a sound/data burst (packet). The latter is digital and duobinary-encoded (Ref. 2) to reduce the bandwidth of the FM signal produced for D- and D2-MAC transmissions via satellite. D-MAC differs from D2-MAC by its higher data rate in the

Fig. 2. From PAL to MAC: time-division multiplex of picture components and sound.

sound/data burst: 20.25 MHz instead of 12.125 MHz (Fig. 2d), which allows a greater number of high-quality sound channels to be used at the expense of a slightly greater bandwidth.

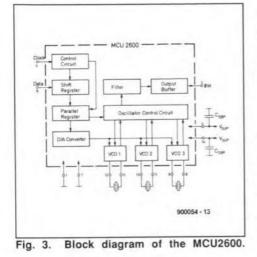

#### Clock generator MCU2600

After a necessarily brief recap on the background of MAC, the components that go into ITT's Multi-MAC concept will be discussed below with reference to block diagrams. Unfortunately, the scope of this article does not allow a full description of each device to be given; this may be found in the relevant datasheets. Time multiplexing must rely on accurate clocking of various circuits in the MAC decoder. As shown in Fig. 2d, the system clock required for a MAC signal is determined by the number of samples within the line time of 64  $\mu$ s, and the line frequency: 1,296/15,625 = 20.25 MHz.

The MCU2600 supplies the digital processors, decoders, converters, etc., that form part of the Digit-2000 TV system with the required main clock signal, which is of trapezoidal shape, with rounded corners, to avoid cross-talk and other interference. The MCU2600 may also be used for PAL, SECAM or NTSC: depending on the crystal used, the chip

#### **ELEKTOR ELECTRONICS MAY 1990**

supplies four times the chroma subcarrier frequency needed (PAL/SECAM: 17.734 MHz; NTSC: 14.318 MHz).

All three VCOs on board the MCU2600 may be selected individually, via the clock and data inputs, to form part of a PLL which is controlled by another chip, for instance, the DMA2280 MAC decoder. The PLL control (= error-) signal is applied in digital, serial, form to pin 6 of the MCU2600. The default VCO selection is VCO1.

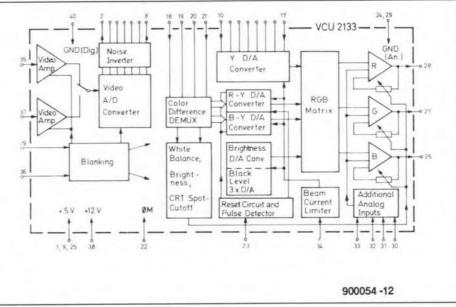

# Video coder/decoder (codec) VCU2133

The VCU2133 contains the ADC and the DAC mentioned above in the introduction of the Digit-2000 concept. The chip is provided with the baseband signal after deemphasis to the MAC standard (which is not the same as the CCIR standard for PAL). As already noted, all digital signal processors in the Digit-2000 system are located between the ADC and the DAC in the VCU2133, which provides the following functions (see Fig. 4):

- two software-selectable input amplifiers

- one fast A-D converter for the composite video signal

- one noise inverter

- one D-A converter for the luminance signal

- two D-A converters for the colour difference signals

- one RGB matrix for converting the colour difference signals and the luminance signals into RGB signals

- three RGB output amplifiers

- programmable auxiliary circuits for blanking, brightness adjustment, white balance control and picture tube alignment

- additional clamped RGB inputs for text, teletext or other analogue RGB signals

- programmable beam current clamping

The VCU2133 may be used with a variety of video circuits, including the VPU2203 PAL processor, the CVPU2233 NTSC Comb Filter Video Processor, the SPU2220 SECAM Chroma Processor, the DPU2553 Deflection Processor and the DTI2223

ELEKTOR ELECTRONICS MAY 1990

Digital Transient Improvement Processor (note: DTI is sometimes referred as CTI: colour transient improvement). The chip contains a large number of registers that are loaded and read by the central processor in the Digit-2000 system via the IM bus.

The A-D converter that follows the two video input amplifiers and the selection switch is of the flash type, which means that it is a circuit that consists of 2" comparators in parallel. For a slowly varying video signal, 8 bits are required. To achieve 8-bit picture resolution with a 7bit converter, a special operation known as 'bit enlargement' is used. During every other line, the reference voltage of the A-D converter is changed by an amount corresponding to one half of the least-significant bit (LSB). In this manner, a grey value between two 7-bit steps is converted into the next lower value during one line, and into the next higher value during the next line. The two grey values are averaged by the viewer's eye, producing the impression of grey values with 8-bit resolution. Synchronously with the changing reference voltage of the ADC, a half-bit step is added to the output signal of the Y DAC every second line. The bit enlargement is switched off for D- and D2-MAC signals by appropriate control of the registers in the VCU2133.

The ADC's sampling frequency supplied by the MCU2600 is 17.7 MHz (PAL/SECAM), 14.3 MHz (NTSC) or 20.25 MHz (MAC). The converter's resolution is ½ LSB of 8 bits. Its output signal is Gray-coded to eliminate spikes and glitches resulting from different comparator speeds, or from imperfections in the coder itself.

After having been processed in other circuits, e.g., the DMA2280, the different parts of the digitized video signal are fed back to the VCU2133 for further processing to drive the RGB output amplifiers. The luminance (Y-) signal is routed from the contrast multiplier in the DMA2280 to the Y DAC in the VCU2133 in the form of

#### ABBREVIATIONS

| ADC     | Analogue-to-Digital Con-<br>verter                               |

|---------|------------------------------------------------------------------|

| AGC     | Automatic Gain Control                                           |

| ALU     | Arithmetic Logic Unit                                            |

| BER     | Bit-Error Rate                                                   |

| BSB     | British Satellite Broad-<br>casting                              |

| CCIR    | Comité Consultatif Inter-<br>national de Radio                   |

| CCU     | Central Control Unit                                             |

| CLIMB   | Command Language for<br>Intermetall Bus                          |

| DAC     | Digital-to-Analogue Con-<br>verter                               |

| FM      | Frequency Modulation                                             |

| HD-MAC  | High-Definition MAC                                              |

| MAC     | Multiplexed Analogue<br>Components                               |

| NICAM   | Near-Instantaneous<br>Companding Analogue<br>Multiplex           |

| NTSC    | National Television<br>Standards Committee                       |

| PAL     | Phase Alternation Line                                           |

| PC      | Personal Computer                                                |

| PDM     | Pulse Duration Modulation                                        |

| PLL     | Phase-Locked Loop                                                |

| QPSK    | Quadrature Phase Shift<br>Keying                                 |

| RGB     | Red-Green-Blue                                                   |

| ROM     | Read-Only Memory                                                 |

| SECAM   | Séquentiel Couleur à<br>Mémoire                                  |

| SEEPROM | Serial Electrically Erasable<br>Programmable Read-Only<br>Memory |

| vco     | Voltage-Controlled<br>Oscillator                                 |

a parallel 8-bit signal with a resolution of  $\frac{1}{2}$  LSB of 9 bits. This range provides enough headroom for large contrast vari-

Fig. 4. Block diagram of the VCU2133 ADC/DAC.

17

#### RADIO AND TELEVISION

18

ations as well as positive and negative overshoot. The Y DAC is an R-2R ladder network which is provided with the central clock frequency (20.25 MHz for MAC).

The two digital colour difference signals, R-Y and B-Y, are transferred in a time-multiplex arrangement to save on input pins. At a clock of 20.25 MHz and a chrominance bandwidth of between 1 MHz and 2 MHz, this can be done with impunity. Like the Y DAC, the two 8-bit DACs for R-Y and B-Y are implemented as R-2R ladder networks. Although they are clocked at one quarter of the central clock frequency, the multiplex data transfer rate is 20.25 MHz (for MAC). Sixteen (four times four) bits are transferred sequentially under the control of a sync signal that co-ordinates the multiplex operations between the VCU2133 and the video processor (in this case, a DMA2280).

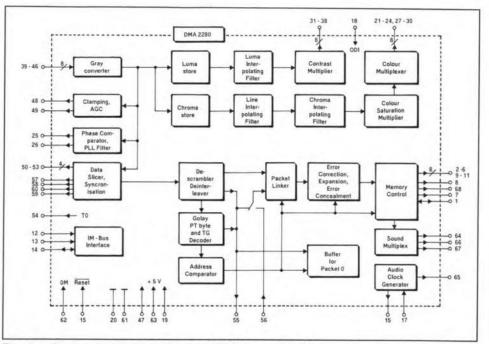

# C/D/D2-MAC decoder DMA2280

This chip forms the heart of the multistandard MAC decoder. Its tasks may be summarized as follows:

- to accept the digitized video (baseband) signal and extract from this the timecompressed chrominance and luminance information, and the sound/data packet

- to de-compress (expand) and correlate the luminance and chrominance information

- to extract audio, special data and sync words from the sound/data packet, taking account of the two different data rates (D2-MAC: 10.125 MHz; D-MAC: 20.25 MHz)

- to ensure a central clock of 20.25 MHz by providing a control voltage to the PLL in the MCU2600

- recognition of packet 0 for special purposes

- when required to provide error correction on weak input signals, and allow different slicing levels to be defined for the on-board duobinary decoder

- to provide an AGC signal for (digital) level control of the baseband input signal

to communicate with the central IM bus

- processor

The DMA2280 is the multi-MAC version of the (older) DMA2270. Its block diagram is given in Fig. 5. The DMA2280 is a complex chip by almost any standard because it handles many relatively fast digital signals at the same time. It has on-board luminance and chrominance storage circuits which enable the relevant picture components to be de-compressed (expanded) and multiplexed (chrominance only) under the control of the central clock. Furthermore, it is capable of de-interleaving and linking the packets sent in each MAC TV line. A special word recognizer with error correction capabilities ensures the recognition of the field and line syncs, which are complex digital words con-

Fig. 5. The heart of the decoder: the DMA2280 multi-MAC processor.

tained in the sound/data packet. The DMA2280 has a capability for direct interfacing with any of the teletext processors in the Digit-2000 series, such as the TPU2733.

The sound recovered from the data packets is fully decoded by the DMA2280 but left digital for demultiplexing and converting into analogue form by the AMU2485 audio processor.

provided by the All functions DMA2280 are controlled by registers, of which the content is determined by the chip itself (read-only) or the central processor. The bit-error rate (BER) register, for instance, contains a number that represents the sum of the error bits encountered in the 82 packet headers in one frame. This sum is stored in a register that can be read as bits 0-7 at address 206 by the central processor, which can take the necessary actions such as muting the audio signal when the BER parameter exceeds a certain predefined level. The

DMA2280 occupies a total of 12 addresses on the IM bus. The bits reserved for these registers control a total of over 30 programmable functions, some of which may be used to select, in turn, up to four different modes of operation. The selection between C-, D- and D2-MAC is not automatic and must therefore be accomplished by the control software.

It should be noted that the DMA2280 requires a separate sound demodulator for C-MAC, since in that case the sound is provided in 2-4 QPSK rather than duobinary FM.

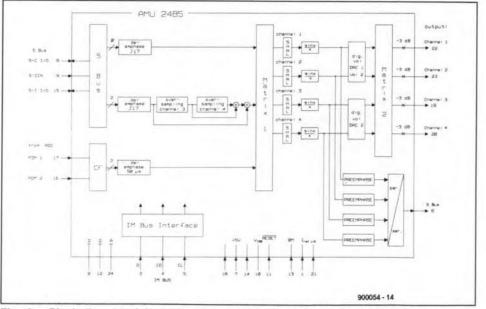

#### Audio mixer AMU2485

The AMU2485 (Fig. 6) receives the serial audio data supplied by the DMA2280 at its S-bus inputs. The S-bus is unidirectional and consists of three lines: S-clock, S-ident and S-data. The sound information is transmitted in frames of 64 bits, divided into four successive 16-bit sam-

Fig. 6. Block diagram of the audio component in the decoder, the AMU2485.

Fig. 7. Block diagram of a multi-standard MAC decoder intended for use as a set-top box. The PC-to-IMB interface is required during the development stages only.

ples. Each sample represents one audio channel. The repetition rate of the samples is equal to the sampling rate of the D- or D2-MAC signal so that up to four sound channels can be transferred simultaneously.

The AMU2485 provides a complete digital signal processor that runs its own control program from an on-chip mask-programmable ROM. Two de-emphasis filters are available: one to the CCIR J17 standard (used for MAC and NICAM transmissions) and one to the 50 µs standard (used for PDM sound broadcasts). Both de-emphasis circuits operate digitally and can be switched off if required by an appropriate register instruction.

The oversampling filters in S-bus channels 3 and 4 allow medium-quality D2-MAC sound signals (16 kHz sampling rate) to be mixed with high-quality signals (32 kHz sampling rate). The filters are third-order Cauer-type low-passes with a stop-band rejection of 40 dB.

The audio mixing feature of the AMU2485 allows any input to be routed to any output and, of course, to mix differently weighted input channels. The mixing and volume control operations on the DACs are entirely digital and run under the control of an internal ALU that receives the appropriate commands via the IM bus.

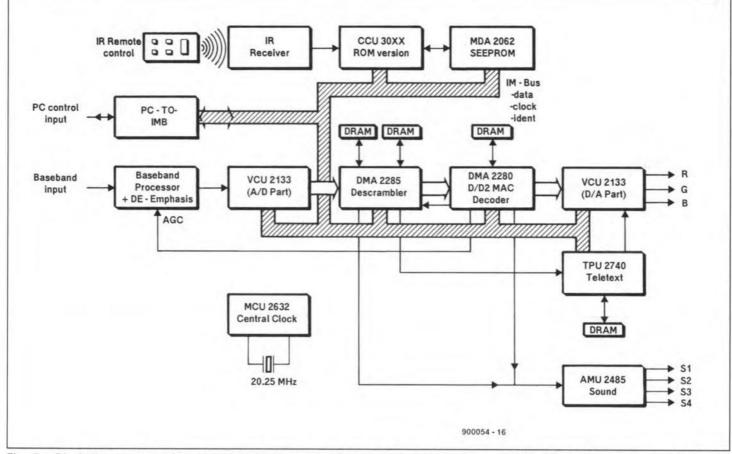

# A multi-MAC decoder

The previously discussed chips all go into the making of the MAC decoder shown in

sly discussed chips all go into inp

Fig. 7. This concept packs all the signal processing required between the baseband output of the indoor unit and the RGB drivers in the colour monitor or TV set into a single set-top decoder.

The IM bus, which has not been discussed so far, is shown as a shaded path that links the sub-circuits into a small network. The bus consists of three lines: Signal Ident (ID), Clock (CL) and Data (D). The clock frequency range is 50 Hz to 170 kHz. Ident and clock are unidirectional from the CCU to the slave devices; data is bidirectional to allow the CCU to interrogate devices by loading and examining the contents of their registers.

The block diagram in Fig. 7 shows that the decoder can be controlled either by a PC via the PC-to-IMB interface, or by a CCU which uses a SEEPROM for storing and loading user settings such as the MAC standard (C, D, or D2), sound selection or contrast. The PC is required only during the development stages of the decoder; the software that runs on it, CLIMB, allows all registers in the chips that form the decoder to be examined and, if necessary, loaded or reloaded. CLIMB allows individual chips such as the VCU2133 to be programmed in great detail, with the aim of developing machine code for the CCU.

Once debugged and tested, the system control software is burned into a ROM on board the CCU. The CCU, which may be a 65xx or 80xx-like processor, has a direct input for digital data supplied by an infrared receiver.

As shown in the block diagram, the DMA2280 works in conjunction with the DMA2285 descrambler. In addition to its normal function as a low/high level MAC decryption processor, the DMA2285 allows 16:9 format HDMAC pictures to be converted to 4:3 format. Note, however, that this feature makes the decoder described only partly compatible of HD-MAC because of the present resolution of 625 lines. Fortunately, the next generation of MAC chips --which are now being developed — will be capable of meeting the full HD-MAC specification with 1,250 lines and thus deliver virtually flicker-free wide-format pictures.

#### Source:

Datasheets AMU2485; DMA2280; DMA2285; VCU2133; MCU2600/2632; DMA2270; CLIMB V2.1. ITT Semiconductors.

ITT Semiconductors U.K. • Rosemount House • Rosemount Avenue • West Byfleet • Surrey KT14 6LB. Telephone: (0932) 336116. Fax: (0932) 336148. Worldwide Head office:

ITT Intermetall GmbH • P.O. Box 840 • D-7800 Freiburg • West-Germany. Telephone: +49 761 517-0.

#### **References:**

1. The MAC system. Elektor Electronics July/August 1987.

2. Introduction to duobinary encoding/decoding. *Elektor Electronics* January 1990.

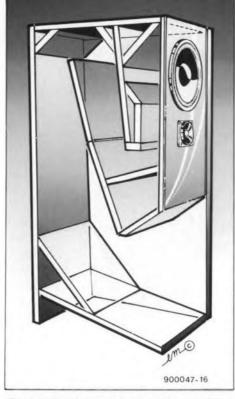

# HORN LOUDSPEAKER

### T. Giffard

Horn loudspeakers for domestic hi-fi reproduction are generally large, cumbersome and expensive boxes that are built only by real enthusiasts. It is nevertheless highly satisfying to build them, particularly the one described here which, although producing excellent sound quality, is far less expensive than usual.

Because of its high efficiency, it will produce more than enough sound pressure for most domestic purposes, even when it is driven by a low-power amplifier.

The horn loudspeaker is almost certainly the oldest type of loudspeaker, dating back to the days of Edison's wax cylinders. Then, they were the only devices to offer sound amplification, and ever since researchers like Webster, Wilson, Voigt and Klikpsch have applied their skills to the design of horn loudspeakers. Even with today's powerful amplifiers, they remain the only solution for filling large spaces with an adequate volume of sound.

In hi-fi installations, however, the horn has had to give way long ago to different types of loudspeaker construction, such as the bass reflex, the transmission line and the closed box.

Nevertheless, the domestic horn loudspeaker is not dead and for very good reasons: it has a very high efficiency, and consequently a large dynamic range, good impulse behaviour and low distortion. On the other hand, its design is usually highly

| McFarlow Type T8-60<br>McFarlow Type H25-90 |

|---------------------------------------------|

| McFarlow Type H25-90                        |

|                                             |

| about 100 litres                            |

| 92 dB (1 W/1 m)                             |

| 80 W continuous                             |

| 120 W music                                 |

| 6 dB/octave (woofer)                        |

| 12 dB/octave(tweeter)                       |

| cy 3800 Hz                                  |

|                                             |

complex, while the drive units it uses are generally (but not always) quite expensive. Moreover, it takes up a lot of space in the home.

Since it is very difficult to buy a horn speaker, the one described in this article has been designed specially for us by professional designers. The drive units and filter cost something like  $\pounds 60-\pounds 70$  per box. The construction of the enclosure is, however, not recommended for beginners in woodworking.

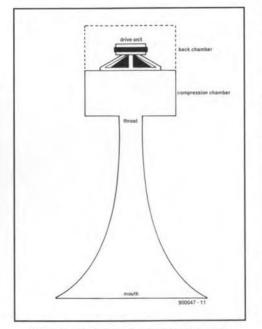

# The horn

A horn is basically an acoustic transformer. It transforms a small area diaphragm into an effective large area diaphragm without the disadvantages of increased mass, cone resonances, and so on. The radiation resistance of a large-area diaphragm is much greater than that of a small area one and thus more power is radiated for a given velocity of volume of air (sound velocity).

The basic requirements in the design of a horn are maximum acoustic power, wide frequency range, and low distortion. Once these have been determined, the drive units may be specified, after which the throat and mouth diameters and the form and length of the horn may be calculated.

Many horns are of the exponential type (others are conical or hyperbolic). The exponential behaviour of the horn ensures better coupling between drive unit and air and this increases the efficiency to almost 50%, which is an enormous improvement

Fig. 1. Basic design of a horn loudspeaker.

Fig. 2. The McFarlow woofer and tweeter.

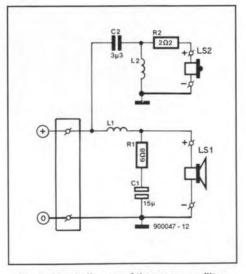

Fig. 3. Circuit diagram of the crossover filter.

ELEKTOR ELECTRONICS MAY 1990

21

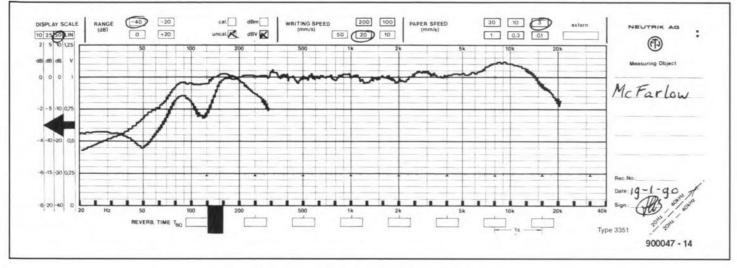

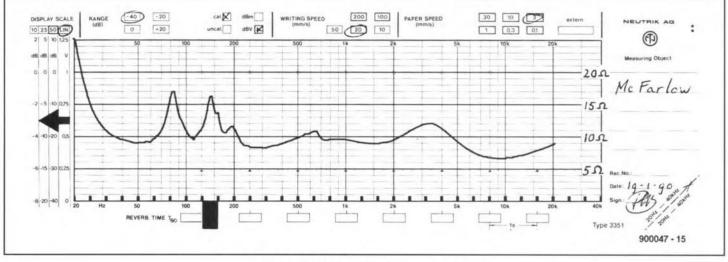

Fig. 4. Frequency characteristic of overall system.

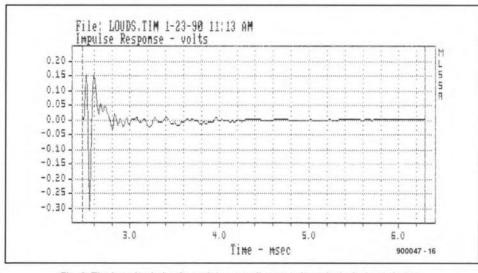

Fig. 6. The impulse behaviour of the overall system is typical of a horn design.

over the 1% of most other types.

The calculations of a horn design are not simple: every one of the many types has to be computed differently. We will not go into all of these, however, and will restrict ourselves to a general description of the operation of a typical horn system.

The modern horn speaker consists of a

**ELEKTOR ELECTRONICS MAY 1990**

drive unit and matching horn as shown in Fig. 1. The drive unit is loaded by the volume of air in the compression chamber. Since the acoustic impedance is inversely proportional to the frequency, the compression chamber and the throat effectively form a low-pass filter.

The throat provides the coupling be-

tween the drive unit cum compression chamber and the horn. The area of the throat is important for optimum coupling.

The area of the mouth of the horn determines the low cut-off frequency. A good rule of thumb here is that the circumference of the mouth must be at least equal to the wavelength of the lowest frequency to be reproduced. Depending on how many surfaces the horn will be coupled to, the area of the mouth may be reduced by a factor 2 (floor), 4 (floor plus wall) or 8 (corner of room).

The length of the horn depends on a number of factors, particularly the ripple in the frequency curve that is acceptable. Since for good low-frequency reproduction the length is of the order of metres, the horn is normally folded a couple of times. Its total volume will then remain within acceptable limits for domestic use.

Often, the drive unit is also loaded at the back by a horn or closed box so as to ensure equal acoustic loading at both sides of the diaphragm. With back-loaded horns, as used in the present design, that is not possible, because these must then radiate the higher frequencies directly. Such AUDIO & HI-FI

22

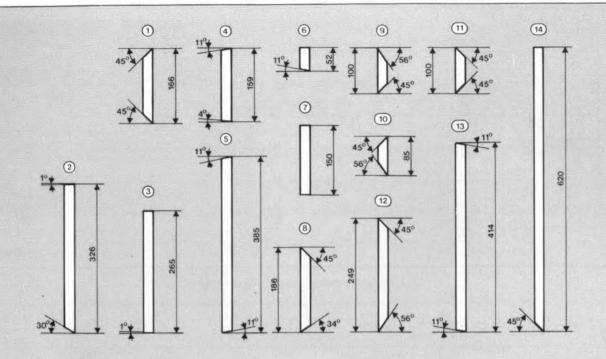

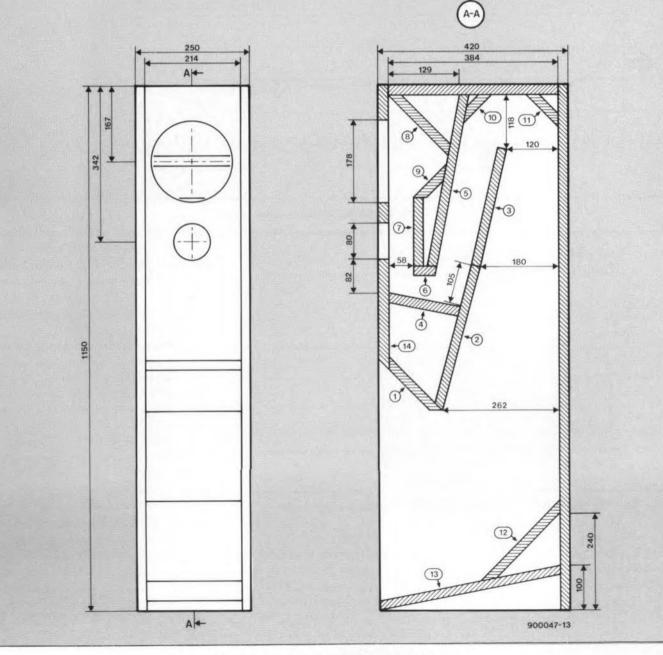

Fig. 7. Construction diagram of the horn enclosure.

Fig. 8. Artist's impression of partially completed enclosure.

| PARTS LIS    | ST (ONE ENCLOSURE)                                                       |

|--------------|--------------------------------------------------------------------------|

| Drive units  | McFarlow T8-60<br>McFarlow H25-90                                        |

| Filter       |                                                                          |

| L1           | air-core inductor 05 mH<br>wound from 1 mm dia.<br>enamelled copper wire |

| L2           | air-core inductor                                                        |

|              | 0.25 mH wound from                                                       |

|              | 0.71 mm dia. e.c.w.                                                      |

| C1           | 15 µF, 35 V, bipolar                                                     |

| C2           | 3µ3 MKT                                                                  |

| R1           | 6Ω8, 5 W                                                                 |

| R2           | 2Ω2, 5 W                                                                 |

| 18 mm chip b | board or plywood                                                         |

| rear panel   | 250×1132 mm                                                              |

| top plate    | 250×420 mm                                                               |

| front panel  | 250×602 mm                                                               |

| flank (2×)   | 420×1150 mm                                                              |

| panel 1      | 250×166 mm                                                               |

| panel 2      | 250×326 mm                                                               |

| panel 3      | 250×265 mm                                                               |

| panel 4      | 250×159 mm                                                               |

| panel 5      | 250×385 mm                                                               |

| panel 6      | 250×52 mm                                                                |

| panel 7      | 250×150 mm                                                               |

| panel 8      | 250×186 mm                                                               |

| panel 9      | 250×65 mm                                                                |

| panel 10     | 250×85 mm                                                                |

| panel 11     | 250×100 mm                                                               |

| panel 12     | 250×249 mm                                                               |

| panel 13     | 250×414 mm                                                               |

| Miscellaneou | 8                                                                        |

|              | erial as required (ex-                                                   |

|              | yrene nuggets or rock-                                                   |

| wool)        | from hoggete er roet.                                                    |

|              | ws as required                                                           |

horns, including the present, are therefore used to reproduce the low-frequency range only.

#### **Design parameters**

In the design of the present horn speaker system the most important requirement was that the mouth area should not exceed 0.125 m<sup>2</sup> so as to keep the dimensions of the enclosure within reasonable limits. The throat area and the low cut-off frequency,  $f_{c'}$  must also had to have reasonable values. The throat area is normally given a value between 0.3  $A_d$  and 1.0  $A_d$ , where  $A_d$ is the effective cone area of the bass drive unit. Since the throat area and the volume of the compression chamber determine the acoustic load, and thus the bandwidth, of the speaker system, we have chosen a ratio of 0.73 (according to the calculations of W. M. Leach).

It is often thought that in horn systems only drive units with a very low  $Q_{ts}$  (that is, with a very large magnet) may be used. This is, however, not always necessary: it depends on what bandwidth the system is required to reproduce. The bandwidth of a back-loaded horn as used in the present design is so small that a drive unit with a  $Q_{ts}$  of 0.35 is perfectly suitable.

The low cut-off frequency is that frequency at which the horn is no longer loaded, that is, produces no sound. In the present design it is set at 40 Hz. The real -3 dB point lies somewhere between  $f_c$  and the frequency determined by the mouth area. The ratio of these two frequencies must not be too large to avoid irregular behaviour of the radiation impedance between horn and room and a lumpy frequency characteristic.

The cross-sectional area,  $A_x$ , of an exponential horn at any distance x from the throat increases according to the following equation:

$$A_x = A_t e^{2mx}$$

where  $A_t$  is the throat area, e = 2.718 and m, the flare constant,  $= 2\pi f_c/c$ , where c is the sound velocity (about 345 m/s).

#### Drive units and filter

In the choice of drive units it was important, since the larger part of the frequency range is radiated direct by the drivers, to find a combination that would match the efficiency of the horn,. The choice fell on the McFarlow Type T8-60 woofer and Type H25-90 tweeter (see Fig. 2).

The woofer is a 20 cm type with a nor-

mal pressed steel chassis and a coated paper cone. It has a reasonably sized magnet (dia. = 11 cm) and an efficiency of 92 dB (1 W/1 m). It is provided with a separate aluminium front bezel that gives it a very attractive appearance. Moreover, it costs only about £30 or so.

The tweeter has an even better efficiency than the woofer, which makes some attenuation in the filter necessary. The dome is made from a type of pressed foam and the speech coil is cooled by ferro fluid. Its price is very close to that of the woofer.

The crossover filter, whose circuit is shown in Fig. 3, has been kept fairly simple. The low-pass section has an attenuation of 6 dB/octave and the high-pass section one of 12 dB/octave. Because the crossover point is rather high (3800 Hz), some impedance correction proved necessary and this is provided by R1 and C1. Resistor R2 ensures correct level matching between woofer and tweeter. The filter is easily constructed on a piece of veroboard or even on a small piece of plywood.

#### Building the enclosure

Most of the work goes into the construction of the enclosure. You can, of course, have it made, but that may increase the cost of the system quite appreciably. The construction plan is shown in Fig. 7, while Fig. 8 gives an artist's impression of a partially completed box.

The enclosure is made of 18 mm chipboard or plywood; thicker board may be used but it will then be necessary (and not easy) to match the horn to the new dimensions. Wherever possible, angles have been kept to 45° or 90°. If possible, have the dealer you buy the board from saw it to size according to the wood list.

Start with gluing the rear panel, top plate, base plate, front panel and one of the side flanks together. Then, one by one, glue the inner wedges, inclines and tails in place. It is important to stick to the correct distances between all these panels. Any gaps where panels are glued together should be filled with a good-quality (silicone) wood filler.

When the glue has set hard, drill holes for the connecting cables. At the same time, fit the crossover filter in the hollow base.

Next, fit the drive units securely in place, after which all the wiring should be completed.

Finally, fill the enclosure with suitable expanded polystyrene chips or rockwool and glue the second side flank in place.

The enclosure can then be finished externally to personal taste.

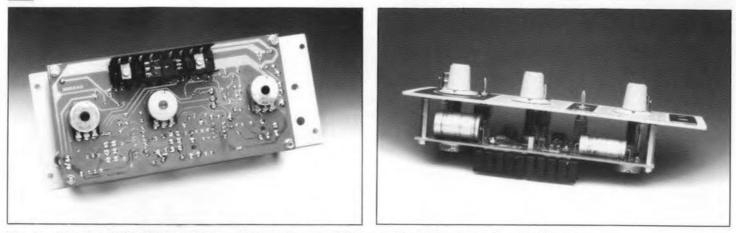

# PC SERVICING CARD

The most irritating thing about dealing with suspect or defective PC add-on cards is that they are difficult to get at for measurements with, say, an oscilloscope when they are seated in an expansion slot on the motherboard. The first and foremost requirement of a servicing card is, therefore, that it extends the bus physically, so that the card under examination is accessible from all sides without having to rebuild the inside of the computer.

A further well-known source of annoy-

#### BASIC TEST PROGRAM

```

100 REM

110 REM *** switch on servicing card ***

130 REM

130 D = INP (&H300)

140 REM

150 REM approx. 0.5 sec delay

160 FOR I = 1 TO 1000:NEXT I

170 REM

180 PRINT "TEST PROGRAM SHOULD END HERE"

190 REM

200 REM *** switch off servicing card ****

210 REM

220 OUT &H300, D

230 END

```

#### PASCAL TEST PROGRAM

PROGRAM service; USES Crt; (for Turbo4.0) CONST IOaddress = \$0300; (change as r'qd) VAR Dummy : Byte;

```

PROCEDURE switch on;

Begin

Dummy := Port [IOaddress];

PROCEDURE switch off;

Begin

Port [IOaddress] := Dummy;

End

PROCEDURE test_program; (test program for defective add-on board)

Begin

Write

('test program should');

Writeln ('end here');

End:

Begin ( main program )

switch_on;

DELAY (500);

(wait for control to finish)

test_program;

switch_off;

End.

```

Table 1. Example BASIC and Pascal programs that enable the servicing card to be controlled by the PC rather than push-button Ta1.

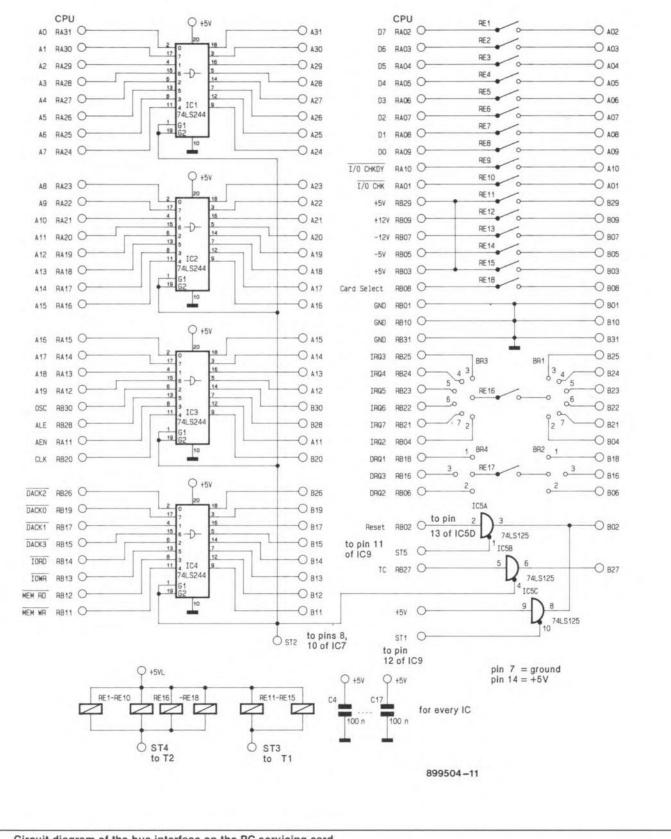

Fig. 1. Circuit diagram of the bus interface on the PC servicing card.

ance is elegantly eliminated by the present servicing card: the add-on board under examination may be removed and inserted without the need of switching the computer off and on again, and without causing hang-ups to the system. This is achieved by the servicing card decoupling the lines for the supply voltage, address-, data- and control- signals between it and the card under test.

### Operation and controls

After it has been inserted into one of the bus expansion slots on the PC motherboard, the servicing card allows the user to enable or disable the card under test in two ways.

First, the user may press a button on the servicing card. When the associated red LED lights, the card under test is enabled. Since the push-button controls a toggle function, pressing it again causes the LED to go out and the supply-, ad-

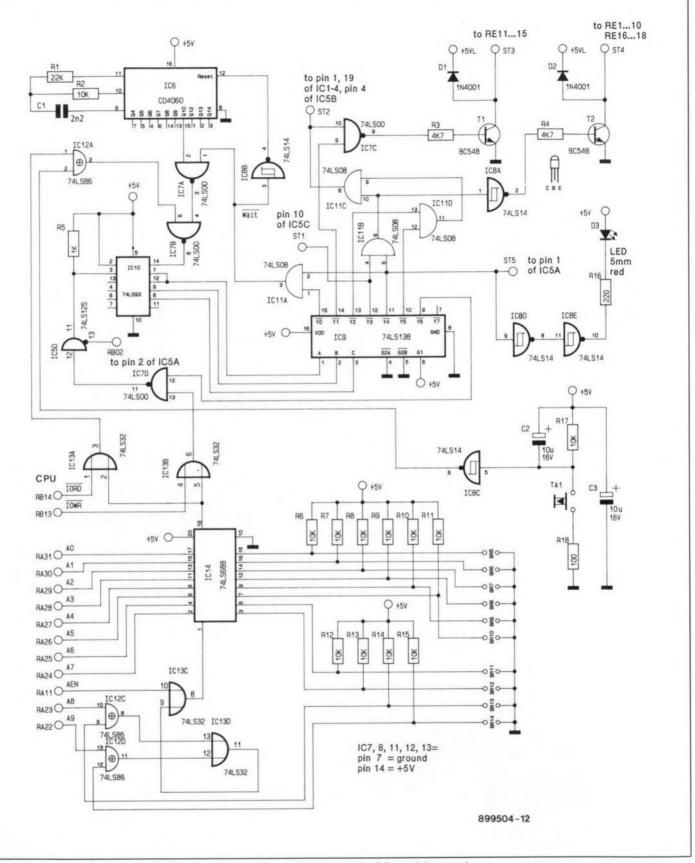

Fig. 2. Circuit diagram of the control logic and the address decoder on the PC servicing card.

dress-, data- and control- lines between the PC motherboard and the card under test to be disconnected.

The second control option lies in the use of software with basically the same function and LED indication as the 'disconnect' button. The servicing card thus allows home-made I/O cards to be tested with the aid of a small program that trans-

fers the test data obtained to the user via the PC. Table 1 gives suggestions for such programs: examples are given in BASIC and Pascal.

# Circuit description

The service card consists of three parts: a bus interface circuit, a control circuit and

an address decoder circuit. The circuit diagram of the first part, the bus interface, is given in Fig. 1, while that of the control circuit and the address decoder appears in Fig. 2.

#### Bus interface circuit

The unidirectional control lines in a PC, such as the ones that carry the address and

27

| count | output | WAIT | ST3 | ST2 | ST4 | ST1 | ST5<br>LED |

|-------|--------|------|-----|-----|-----|-----|------------|

| 0     | YO     | L    | н   | н   | н   | н   | н          |

| 1     | Υī     | н    | L   | н   | н   | н   | н          |

| 2     | ¥2     | н    | L   | L   | н   | н   | н          |

| 3     | ¥3     | н    | L   | L   | L   | L   | н          |

| 4     | ¥4     | L    | L   | L   | L   | н   | L,         |

| 5     | ¥5     | н    | L   | L   | н   | н   | н          |

#### Table 2. Overview of counter functions.

bus control signals, are applied to the circuit via bus drivers Type 74LS244, IC1– IC4. The outputs of these drivers are enabled or switched to three-state via a common control line, ST2. The PC address lines A0–A19 are buffered by IC1, IC2 and one half of IC3. The other half of IC3 buf-

| Signal   | Pin d         | esig     | nation                 | Signal |  |

|----------|---------------|----------|------------------------|--------|--|

| name     | track<br>side |          | compo-<br>nent<br>side | name   |  |

| GND      | B01           | ,        | A01                    |        |  |

| RESET    | B02           |          | A02                    | D7     |  |

| +5V      | B03           | f PC     | A03                    | D6     |  |

| IRQ2     | B04           | el o     | A04                    | D5     |  |

| -5V      | B05           | panel of | A05                    | D4     |  |

| DREQ2    | B06           | rear     | A06                    | D3     |  |

| +12V     | B07           | -        | A07                    | D2     |  |

| reserved | B08           |          | A08                    | D1     |  |

| +12V     | B09           |          | A09                    | DO     |  |

| GND      | B10           |          | A10                    |        |  |

| MEMW     | B11           |          | A11                    | AEN    |  |

| MEMR     | B12           |          | A12                    | A19    |  |

| IOWC     | B13           |          | A13                    | A18    |  |

| IORC     | B14           |          | A14                    | A17    |  |

| DACK3    | B15           |          | A15                    | A16    |  |

| DREQ3    | B16           |          | A16                    | A15    |  |

| DACK1    | B17           |          | A17                    | A14    |  |

| DREQ1    | B18           |          | A18                    | A13    |  |

| DACKO    | B19           |          | A19                    | A12    |  |

| CLK      | B20           |          | A20                    | A11    |  |

| IRQ7     | B21           |          | A21                    | A10    |  |

| IRQ6     | B22           |          | A22                    | A9     |  |

| IRQ5     | B23           |          | A23                    | A8     |  |

| IRQ4     | B24           |          | A24                    | A7     |  |

| IRQ3     | B25           |          | A25                    | A6     |  |

| DACK2    | B26           |          | A26                    | A5     |  |

| TC       | B27           |          | A27                    | A6     |  |

| ALE      | B28           |          | A28                    | A3     |  |

| +5V      | B29           |          | A29                    | A2     |  |

| OSC      | B30           |          | A30                    | A1     |  |

| GND      | B31           |          | A31                    | AO     |  |

fers control signals OSC, ALE, AEN and CLK. In a standard PC, the frequency of the OSC signal is 14.31818 MHz. The system clock, CLK, runs at 4.77 MHz since it is always one-third of the OSC frequency. Control line ALE (address latch enable) is actuated at every bus cycle, and thus indicates that the CPU is not performing a DMA access operation. A DMA cycle is indicated by a separate control line, AEN.

The terminal count (TC) control line is buffered by three-state driver IC<sub>5c</sub>.

Circuit IC4 buffers a number of control signals provided by the PC motherboard. Lines DACK0-DACK3 (DMA acknowledge) are driven by the DMA controller, which uses them to issue DMA requests. Lines IORD and IOWR control read and write operations. Their equivalents for memory access operations are MEMRD amd MEMWR respectively.

Control signals which are either bidirectional or supplied by OC (open-collector) outputs are passed via reed relay contacts. This arrangement obviates the need of complex address decoders and direction control circuits. Datalines D0– D7 are passed via reed contacts RE1–RE8, and control lines IOCHRDY and I/OCHK via reed contacts RE9 and RE10. The I/O channel check (I/OCHCK) line serves to signal parity errors in external memory areas. Such errors generate a non-maskable interrupt (NMI).

The I/OCHRDY (I/O channel ready) line enables bus cycles to be delayed. This is particularly useful for relatively slow input/output ports or memories which require the bus access time to be lengthened. Control line CARD SELECT is passed via reed relay contact RE18.

Relay contacts  $RE_{11}$ - $RE_{15}$  pass the supply voltages, +5 V, -5 V, +12 V and -12 V to the card under test.

The only fixed connection between the PC and the add-on board under test is the ground line. This ensures the presence of a reference potential the instant the add-on board is inserted, and prevents open-collector outputs being damaged.

One of interrupt request lines IRQ2– IRQ7 is passed via relay contact RE<sub>16</sub> and wire jumpers Br1 and Br3, which are fitted in accordance with the IRQ line used. This enables current to flow from, say, RB<sub>25</sub> via BR3, and on via RE<sub>16</sub> and Br1 to B<sub>25</sub>, or from RB<sub>24</sub> to B24, etc. The type of add-on board

| I/O Address | Function                          |  |  |

|-------------|-----------------------------------|--|--|

| 000н-00Fн   | DMA-Controller<br>(8237A-5)       |  |  |

| 020н-021н   | Interrupt-Controller<br>(8259-5)  |  |  |

| 040н-043н   | Timer/Counter (8253-5)            |  |  |

| 060н-063н   | System Register<br>(8255A-5)      |  |  |

| 080н-083н   | DMA-Page Register<br>(74LS670)    |  |  |

| 0А0н-0BFн   | NMI-Interrupt Register            |  |  |

| OCOH-OFFH   | Reserved                          |  |  |

| 100н-1FFн   | Front Panel Controller            |  |  |

| 200н-20Fн   | For Computer Games<br>(Game Port) |  |  |

| 210н-217н   | Additional Unit                   |  |  |

| 220н-24Fн   | Reserved                          |  |  |

| 278н-27Fн   | Second Printer                    |  |  |

| 2F8н-2FFн   | Second Serial Interface           |  |  |

| 300н–31 Гн  | Prototyping Card                  |  |  |

| 320н-32Fн   | Hard Disk-Controller              |  |  |

| 378н-37Fн   | Printer Interface (parallel)      |  |  |

| 380н-38Fн   | SDLC-Interface                    |  |  |

| ЗАОн-ЗАFн   | Reserved                          |  |  |

| 3В0н–3ВFн   | Monochrome Adaptor<br>and printer |  |  |

| 3C0н-3CFн   | Reserved                          |  |  |

| 3D0н-3DFн   | Colour Graphics Card              |  |  |

| 3ЕОн-ЗЕ7н   | Reserved                          |  |  |

| 3F0н-3F7н   | Floppy Controller                 |  |  |

| 3F8н-3FFн   | Serial Interface                  |  |  |

Table 4. PC I/O address map and reserved functions (all addresses in hexadecimal).

to be debugged determines which jumper is to be installed. Line IRQ4 is commonly used by the serial port, line IRQ6 by the floppy controller, and IRQ7 by the parallel port. This leaves IRQ2, IRQ3 and IRQ5 free for special applications and future extensions.

The use of the DMA request lines also differs from card to card. DRQ1 has the highest priority, DRQ3 the lowest.

The reset line forms a special case. Normally, it is buffered by three-state driver IC<sub>5a</sub>. When the servicing card is actuated, it automatically generates a short reset pulse for the add-on board.

Table 3. Signal assignment on the PC expansion slot.

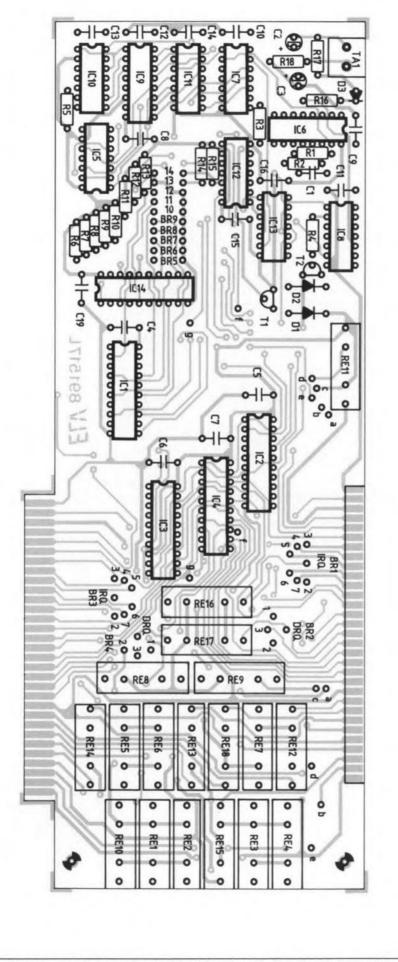

Fig. 3. Construction details of the cover plate which is attached to the circuit board.

Fig. 4. Component overlay on the double-sided through-plated printed-circuit board.

# **COMPONENTS LIST**

content of kit supplied by ELV

| Re  | sistors:            |               |

|-----|---------------------|---------------|

|     | 100Ω                | R18           |

|     | 220Ω                | R16           |

|     | 1k0                 | R5            |

| 2   | 4k7                 | R3;R4         |

|     | 10k                 | R2;R6-R15;R17 |

| 1   | 22k                 | R1            |

| Ca  | pacitors:           |               |

| 1   | 2n2                 | Ct            |

| 14  | 100n                | C4-C17        |

| 2   | 10µF 16 V           | C2;C3         |

| Se  | miconductors:       |               |

| 1   | 74LS00              | IC7           |

| 1   | 74LS08              | IC11          |

| 1   | 74LS14              | IC8           |

| 1   | 74LS32              | IC13          |

|     | 74LS86              | IC12          |

| 1   | 74LS93              | IC10          |

| 1   | 74LS125             | IC5           |

| 1   | 74LS138             | IC9           |

| 4   | 74LS244             | IC1-IC4       |

| 1   | 74LS688             | IC14          |

|     | CD4060              | IC6           |

| 2   | BC548               | T1;T2         |

| 2   | 1N4001              | D1;D2         |

| 1   | LED 5 mm red        | D3            |

| Mis | scellaneous:        |               |

| 18  | reed relay          | Ret-Reta      |

| 1   | PCB-mount push-b    | outton Tai    |

| 1   | 62-way PC expans    | ion socket    |

| 1   |                     |               |

| 100 | ) cm flexible wire  |               |

| 20  | cm silvered wire    |               |

| 1   | PC card cover plate | 0             |

#### Control circuit

This consists of a 4-bit binary counter Type 74LS93, IC10, and a binary-to-decimal decoder Type 74LS138, IC9. The oscillator in IC6, a Type CD4060, is set to operate at about 10 kHz. Its Q10 output therefore supplies a clock signal of about 10 Hz. This signal is applied to the clock input of counter IC10 via IC7a and IC7b. When the counter reaches either state 0 or state 4, the output of AND gate IC11a goes low. This freezes the counter state because NAND gate IC7a blocks the clock pulses. Actuation of push-button Tai causes IC10 to be provided with a clock pulse via ICsc, IC12a and IC7b. This causes the output of IC11a to change from low to high, re-enabling divider IC6.

A clock pulse may also be provided by an I/O read operation on part of the PC. Further details on this are given in the description of the address decoder. When state 6 is reached, the counter is reset to 0 via IC7d and IC5d. Again, this can also be accomplished by a PC I/O write operation. After the computer has been switched on, the reset pulse causes buffer IC5d is to be switched briefly to three-state. Counter IC10 is subsequently reset to 0000 by pull-up resistor R5 at pin 3. This causes the servicing card to be disabled when the PC is switched on.

The second part of the control circuitry decodes the individual counter states. This is done to ensure well-defined on / off switching of the address-, data-, controland supply- lines. Reset line ST1 is only actuated at counter state 3 and thus provides a reset pulse via IC5c. This pulse resets the servicing card to a default state. The relays that pass the data signals are actuated during counter states 3 and 4 via IC11b, IC8a and R4-T2, while the controland address-lines are passed at counter states 2-5 via gates IC116, IC11e and IC11a. In addition to these four states, the supply voltage is also actuated during state 1. The function and operation of the counter are summarized in Table 2.

#### I/O address decoder

The third part of the circuit is formed by the I/O address decoder. The servicing card occupies one address only in the PC's I/O map. All control functions are derived from the PC accessing this I/O address, i.e., data, whether read or written, is ignored.

The I/O addressing function is based on a 10-bit decoder which is set to the desired address with the aid of wire jumpers Br5–BR14. This arrangement enables the servicing card to be selected only when the I/O address supplied by the PC is equal to the address set with the wire jumpers. The outputs of XOR gates IC12c and IC12d are low simultaneously when the levels on PC address lines A9 and A8 are equal to the levels set with Br13 and BR14 respectively. Only in this condition does the output of OR gate IC13d supply a low level.

Circuit IC14, an 8-bit comparator, is enabled by a low level on the AEN line. Its output goes low if the levels of address bits A0–A7 match those provided by wire jumpers Br5–Br10.

PC bus line IOR is low when the CPU performs a read operation. This low level enables gate IC<sub>13a</sub> so that counter IC<sub>10</sub> is provided with a clock pulse. If the write line, IOW, is actuated, the output of OR gate IC<sub>13b</sub> goes low and causes IC<sub>10</sub> to be reset to 0000.

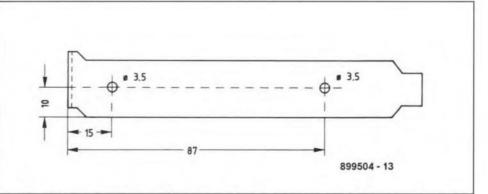

#### Construction

The complete circuit is accommodated on a double-sided, through-plated printedcircuit board of dimensions 233×104 mm. Two angled pieces of aluminium are used to secure the card to the usual cover plate required for PC add-on boards. Cutting and drilling details of this plate are given in Fig. 3.

The construction of the servicing card is straightforward. IC sockets are not used so as to eliminate the risk of bad contacts. All parts must be fitted at the lowest possible height to prevent them touching parts on an adjacent board installed in the PC. Use precision pliers to press pin pairs in the horizontal rows of the 62-way bus expansion socket a little closer together so that they can be soldered direct to the copper tracks at the long side of the board as shown in the photograph.

Use two M3×6 mm screws and nuts to secure the support bracket on the board to the cover plate.

#### Address selection

The input/output address range and the associated functions used in a standard PC are given in Table 4.

The I/O address occupied by the servicing card is set by wire jumpers Br5– Br14. As an example, suppose the servicing card is to be controlled via I/O address 300. The first digit, 3, is equal to 11<sub>2</sub> and therefore set by leaving Br13 and Br14 open. Since the all the other digits are 0, Br5–Br12 are closed.

#### Debugging

Although problems with the practical use of the servicing card should be rare if the construction is carried out with care and precision, a few hints are given to assist in faultfinding.

In case the servicing card causes the PC to crash, remove it from the expansion slot. Connect the card to an external 5-V power supply. The + is connected to bus contact B19 or B03, and ground to B01, B10 or B31. Measure the current consumption: this should be between 200 mA and 300 mA.

Actuate push-button Ta1 to check that LED D3 lights after a delay of about 0.5 s. If this does not happen, take a hard look at oscillator/counter IC6. This is normally disabled via pin 12. Pressing the button should provide IC10 with a clock pulse. As a result, pin 3 of IC11a should go high so that the counter starts to count either to state 0 or state 4 at which it disables IC6. When the counter is not actuated, the bit combination at pins 1, 2 and 3 of IC9 is either at 000 or 100. The states of outputs ST1–ST5 may be checked with reference to Table 2.

In the actuated state, the current consumption of the servicing card rises by about 70 mA. The current consumption then lies between 290 mA (typical) and 360 mA (maximum).

The operation of the I/O address decoder may be checked manually in case the relevant circuitry does not respond to the test program. The card address is assumed to be 300 as in the above example. This means that wire jumpers Br5–Br12 are installed.

Connect inputs RA24–RA31 to ground. Pin RA11 (AEN line) must be made low in any case. Address lines A8 (RA23) and A9 (RA22) are tied to +5 V. Check that pin 1 of the 9-bit comparator, IC14, is low. All other inputs must be low as well. As a result, pin 19 is low also. A brief low level at RB13 (IOWR) should cause the servicing card to switch to its default state. Make RB13 high again and briefly actuate RB14 (IORD) by making it low. Apply a couple of pulses in this way and check that they enable and disable the card via IC13a A complete kit of parts for the PC servicing card is available from the designers' exclusive worldwide distributors (regrettably not in the USA and Canada):

#### **ELV** France

B.P. 40 F-57480 Sierck-les-Bains FRANCE Telephone: +33 82837213 Fax: +33 82838180

Also see ELV France's advertisement elsewhere in this issue.

and IC13b.

If the service card does not function correctly after inserting it into the PC, it is recommended to remove it and first check the relay contacts RE1-RE17 after applying 5 V. This is simple to achieve by measuring the contact resistance between the relevant points at the both sides of the board, near the expansion bus socket. The 'on' resistance of the contacts should be of the order of a few ohms. For this test, it is necessary to select the service card and switch on the extension function. Evidently, jumpers Bri-Br4 must be closed to be able to check that the IRQ and DRQ lines are connected by the relevant relay contacts.

The correct operation of bus drivers  $IC_1-IC_4$  may be verified by applying high and low levels to the relevant control pins at the reverse side of the board. Provided the card is actuated, measurements may be made at the expansion slot.

Finally, the service card may be left in its PC slot even it is not used.

# AN EXPERIMENTAL ALL-WAVEBAND FERRITE ROD ANTENNA

**Richard Q. Marris, G2BZQ**

The ferrite rod antenna described here is a most unusual conception in as much as it covers the frequency spectrum from 125 kHz to 24 MHz (2400–12.5 metres) with continuous tuning and without wavechange switching. This is in sharp contrast to the ferrite rod assemblies usually found in MW/LW radios

The unit was designed as an external antenna for use with any all-waveband radio with external antenna requirements such as communications receivers, vintage radios, home constructed radios and HF bands of modern transistor radios. A further and novel feature is that it covers the segment between the LW and MW bands, which is now again of much interest to many enthusiasts who have built or purchased receivers covering these frequencies, and that between 2000 and 2400 metres where there is increasing activity.

The unit is coupled to the radio input

by either coaxial cable or  $300 \Omega$  flat twin feeder, which is of particular interest where end-fed long-wire antennas have to be attached. In the case of older communications and domestic receivers, it was not unusual for a 100 ft long outside wire antenna to be specified. Even if you have the real estate necessary for this, it is not going to be popular with the neighbours and local authorities.

Many successful experiments have been conducted over the entire waveband covered by the unit. The impressive results are in no small measure due to the careful selection of ferrite core material grades and sizes and the use of a 5-gang variable tuning capacitor.

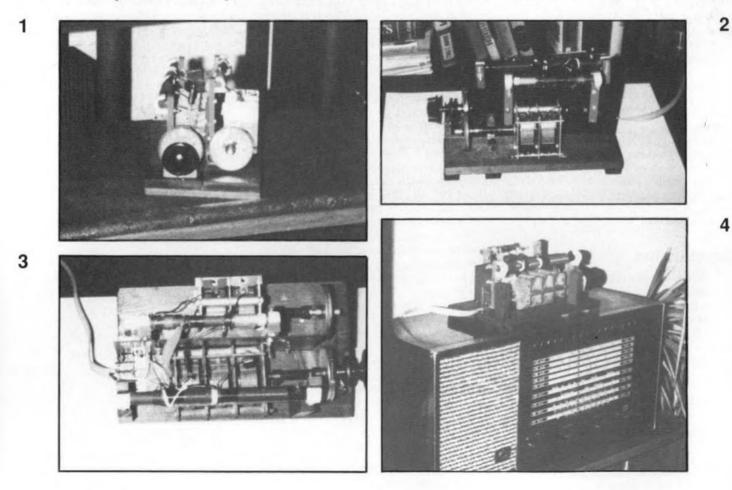

The experimental unit is seen from various angles in the photographs, in one of which (4) it is shown on top of a superb vintage Pye 9-waveband all-wave Export Receiver. This receiver is in everyday domestic use: its audio reproduction outperforms most modern AM radios. Since the unit is experimental, certain imperfections can be seen in the photographs owing to modifications carried out during the final construction, testing and evaluation, but

**ELEKTOR ELECTRONICS MAY 1990**

that's experimental work for you!

### The circuit

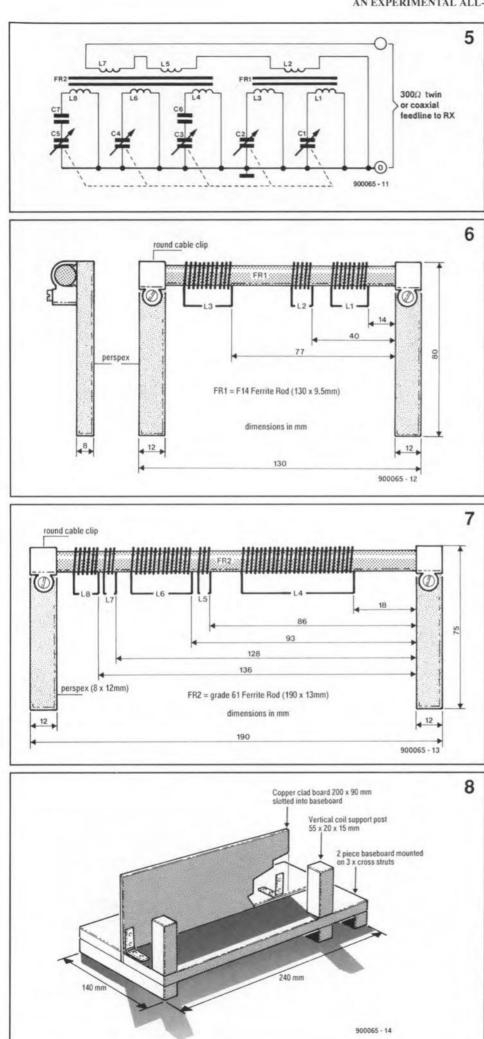

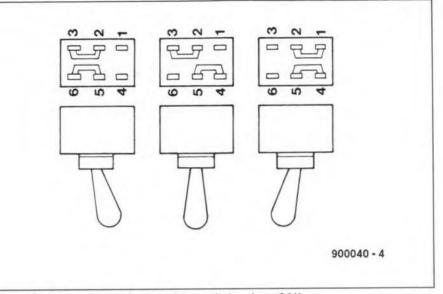

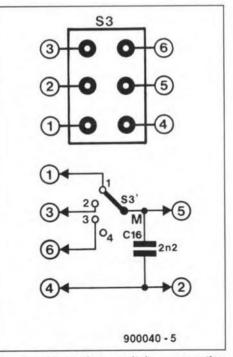

The circuit diagram in Fig. 5 shows five tuned circuits: L1–C1; L3–C2; L4–C3–C6; L6–C4; and L8–C5–C7. A 5-gang, 500 pF per section, variable capacitor is used for C1 to C5. The location of coils L2, L5 and L7, coupling the antenna to the receiver, is critical. All inductors are wound on ferrite rods.

The tuned circuits are adjusted simultaneously and cover different wavebands with small overlaps. The required band is selected automatically by the tuned input circuits in the receiver. There is no interaction between the five tuned circuits during normal operation.

The prototype has been evaluated and tested with several types of communications, domestic and vintage receiver. The wavebands covered by each of the five tuned circuits are:

L1-C1 — 125-450 kHz (2400-667 m) L3-C2 — 400-1900 kHz (750-158 m) L4-C3-C8 — 1000-4250 kHz (300-71 m) L6-C4 — 3500-9500 kHz (85.7-31.6 m) L8-C5-C7 — 8000-24000 kHz (37.5-12.5 m)

# Construction

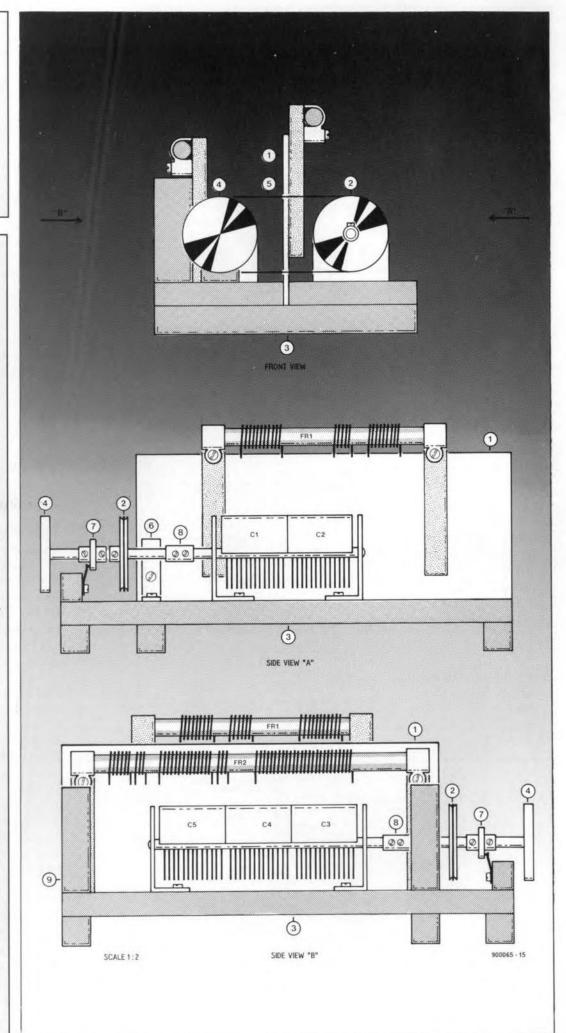

The baseboard assembly shown in Fig. 8 is made of two pieces of 18–22 mm thick (ply)wood. The vertically mounted copper-clad board is for direct common earthing connections and is trapped between the two halves of the baseboard and secured with two brass angle brackets. All wood parts should be given an application of teak colour wood dye.

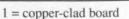

The LF-MF coil assembly—see Fig. 6 uses a 130×9.5 mm Grade F14 ferrite rod, cut down from a standard 140 mm long rod with a Junior hacksaw. Grade F14 is a nickel-zinc material that is usable up to 2 MHz, where performance just begins to fall off. The rod is clamped at either end in a plastic, round cable clip that is secured to a vertical bar of perspex (hardwood would do). The assembly is bolted to the vertical copper-clad board as shown in Fig. 9, side view 'A'.

Both L1 and L3 are proprietary inductors; each has a small coupling winding which should be ignored. The coupling coil to the receiver, L2, consists of 22 closewound turns of 32 SWG enamel copper wire on a small paxolin former. All three should be positioned in the exact positions shown in Fig. 6: deviations will change the overall frequency coverages.

The HF coil assembly—see Fig. 7—is also mounted on two vertical perspex (or

- 2 = 2 in. dia. cord drum

- 3 = wooden base

32

- 4 = knob (with cord drum and slow-motion drive behind)

- 5 = drive cord with tension spring

- 6 = brass angle bracket

- 7 = slow-motion drive

- 8 = shaft coupler

- 9 = feeder terminal block

# PARTS LIST

- FR1 = ferrite rod; Grade F14; 140×9.5 mm, cut to 130mm; Type FRA; stock no. 35-14147; Circkit Distribution Ltd FR2 = ferrite rod; Grade 61; 7.5×0.5 in; Type R61-050-750; Amidon Associates, 12033 Otsego St, Nth Hollywood, California 91607, USA L1 = antenna coil LWC1; stock no.35-00108: Cirkit Distribution Ltd L3 = antenna coil MWC2; stock no. 35-00268: Circkit Distribution Ltd C1, C2 = 2-gang  $\times$  500 pF large BC type variable capacitor; J. Birkett C3, C4, C5 = 3-gang × 500 pF large BC type variable capacitor; J. Birkett

- C6 = 470 pF, silver mica or ceramic

- C7 = 1000 pF, silver mica or ceramic

- slow-motion drive = code RX42V; Maplin

- shaft coupler (2 off) =0.25 in. shaft; J. Birkett

- dial cord drum (2 off) with spring; 54.5 mm dia.; code RX43W; Maplin

- copper-clad circuit board, undrilled; 200×90 mm

- cable clip, plastic (4 off) to fit ferrite rods

- wire (a) 32 SWG enamel insulated copper

(b) 1/0.6 mm singlestrand PVC covered,

1.2 mm outside diameter (NOT 1.0 mm O/D!)

hardwood) columns that are later screwed to the vertical coil support posts shown in Fig. 8. The ferrite rod is 7.5×0.5 inch (the US manufacturer specifies the dimensions only in inches). It is made of Grade 61 nickel-zinc material, specified for use up to 15 MHz, but which here, with special winding techniques, has been stretched to over 40 MHz.

The coils are closewound straight on to the rod from single-strand 1/0.6 mm PVC covered wire, 1.2 mm overall diameter. Similar wire exists with thinner insulation of about 1.0 mm overall diameter, but this MUST NOT be used. The direction of winding should be same for all five coils. They should be positioned exactly as shown in Fig. 7: deviations will result in incorrect frequency ranges and incorrect coupling. After the coils have been tested, they should be held in place with spots of adhesive at the ends. The number of turns for the coils is:

The 5-gang variable capacitor is made by coupling a 2-gang and a 3-gang capacitor together with the aid of two cord-drive drums, a length of dial cord and a spring for tension as shown in Fig. 9 and the photographs. A single epicyclic slow-motion drive operates the two variable capacitors simultaneously.

The variable capacitors are of the 'large broadcast' type that have the advantages of wide-spaced plates, ceramic insulation and a full 500 pF maximum capacitance, while their large size assists in keeping the leads to the coils short. Moreover, the minimum capacitance is smaller than that of most smaller compact types.

In view of possible variations in the dimensions of different makes of capacitor, the exact mounting positions are not shown.

The assembly should be fitted as shown with the aid of shaft couplers and lengths of 0.25 in. dia. rod to align the assembly and drive mechanism. On the prototype, the 2-gang variable capacitor was screwed vertically to the baseboard with the metal frame hardwired to the vertical copperclad board. The 3-gang was mounted upside down (to reduce lead lengths) and bolted to the copper-clad board.

All earth connections should be soldered direct to the copper-clad board by the shortest possible route.

Coupling coil L2 is connected to the

feeder terminal block—see Fig. 9, side view 'B'—by a short length of 300  $\Omega$  twin feeder. Coils L5 and L7 are connected in series and also connected to the terminal block via some 300  $\Omega$  twin feeder and then wired in series with the feeder from L3. This means that all three coils are in series, as shown in the circuit diagram.

The feeder to the receiver may be either the usual coaxial cable or  $300 \Omega$  flat twin feedline. This gives versatility of connection to all types of receiver input impedance.

It might be thought that the coupling coils should have dissimilar numbers of turns, depending on the feedline impedance. Practical experiments indicated that only a fraction of a turn difference would be necessary on L5 and L7, while L2 was not critical. Because of that, the numbers of coupling turns are a compromise that does not degrade the performance, however.

# Testing

The correct feeder should be connected between the feeder terminal block and the receiver. It will be found that the tuning of the antenna unit is quite sharp, thus improving the selectivity of the receiver. Whatever the selected waveband, the antenna tuning should be brought to resonance as indicated by a significant increase in signal. The antenna is directional, with maximum signal appearing on the 'flat' side of the rod and minimum signal at the ends of the rod. Rotation of the unit will, therefore, increase/decrease the strength of the received signal. If there is interference from other stations, local man-made noise, or static, the antenna should be rotated slightly to either side to reduce/eliminate that interference. In general, it will be noticed that the ambient noise level is far lower than with a long-wire antenna.

It will have been noted that the earlier quoted frequency ranges have small overlaps, so that the whole range of 125 kHz to 24 MHz is covered by five complete sweeps of the 5-gang capacitor to match any preselected receiver frequency range, whether LF, MF or HF. A preamplifier may be needed between the antenna and the receiver in the higher HF ranges if the receiver does not have a high RF gain.

The exact frequency ranges can be checked, if required, with a signal generator and appropriate receiver. If, as is probable, a signal generator is not available, but the receiver is dial calibrated, it is possible to check the ranges with an artificial noise signal. For this, a small battery-operated calculator is placed about 12-18 in. from the antenna. This generates a noise signal that can be resonated by the antenna-receiver combination. By manipulation of the calibrated receiver tuning and the antenna tuning, it is possible to check the frequency ranges of the five antenna ranges and, most importantly, to check that the ranges overlap somewhat to provide continuous frequency coverage.

# Conclusion

This compact antenna unit covers all those frequencies, HF, MF and LF, that one may like to receive below 24 MHz. It is directional for elimination or reduction of adjacent station interference, man-made electrical noises and static. It is far smaller than conventional antennas and picks up far less noise. It could be housed in a simple polished or painted wood enclosure or plastic (not metal!) case.

33

A series of projects for the not-so-experienced constructor. Although each article will describe in detail the operation, use, construction and, where relevant, the underlying theory of the project, constructors will, none the less, require an elementary knowledge of electronic engineering. Each project in the series will be based on inexpensive and commonly available parts.

# ACOUSTIC TEMPERATURE MONITOR

J. Ruffell

Electronic temperature monitoring need not be complex. This circuit gives an audible indication when a preset temperature is reached. It can be used as a thermal alarm on boilers and heating systems, as a bath water temperature indicator, or in an electronic whistle kettle.

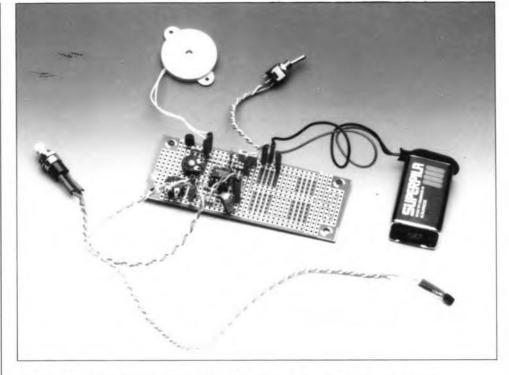

Basically, the temperature alarm consists of three parts: a temperature sensor, a small printed-circuit board which contains the measurement circuit, and a piezo-ceramic buzzer that functions as an indicator. The printed-circuit board and the buzzer are housed in a small ABS enclosure, together with the battery that powers the circuit. The sensor is connected to the circuit via two lengths of flexible wire so that it can be located as close as possible to the object whose temperature is to be measured.

### Temperature sensor

The temperature sensor is formed by an integrated circuit rather than the more conventional NTC (negative temperature coefficient) resistor. This choice was made to ensure a wide temperature range with acceptable accuracy. The sensor used is a Type LM235. This device, which looks like an ordinary transistor in a plastic enclosure, contains a fairly complex circuit that provides an output voltage that is a function of ambient temperature. The output voltage is linear over a wide range and accurately defined at 10 mV/K. Since the electrical behaviour of the LM235 is not unlike that of a temperature-sensitive zener diode, a similar circuit symbol is used. A third pin is drawn, however, to indicate that the LM235 has a calibration input (which is not used here).

The sensor is supplied in a number of versions for different temperature ranges. The LM135 is suitable for -55 °C to +150 °C, the LM235 for -40 °C to +125 °C, and the LM335 for -40 °C to +100 °C. In principle, all three may be used in this circuit: the choice depends on the application. Note, however, that the price of the devices rises with the temperature range.

### The circuit

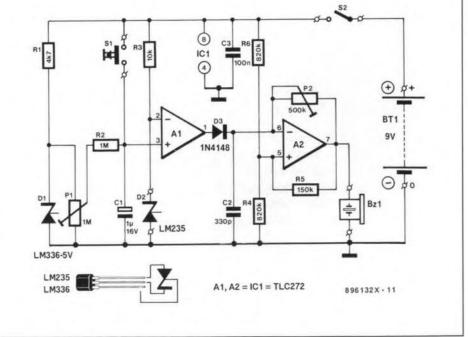

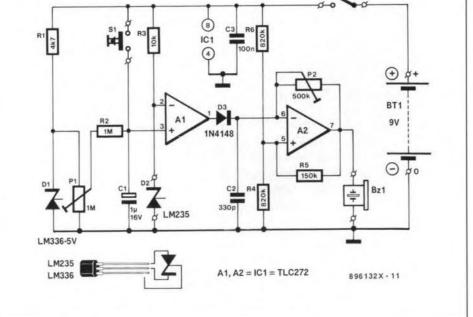

The circuit diagram is given in Fig. 1. Apart from the sensor, only one integrated circuit is used. This IC, a TLC272, contains two CMOS operational amplifiers, A1 and A2. The first is used for the temperature measurement, the second for the acoustic alarm.

Opamp A1 is wired as a comparator: it compares the voltage provided by the temperature sensor, D2, to that provided by an adjustable reference, D1. The LM336 in that position is a temperature-compensated 5-V zener diode. The reference voltage may be adjusted between 0 V and +5 V with the aid of preset P1 before it is applied to the +input of comparator A1.

As long as the temperature measured by D2 is relatively low, the voltage at the -input of A1 is lower than the reference voltage at the +input. As a result, the out-

Fig. 1. Circuit diagram of the acoustic temperature monitor.

Fig. 2. Suggested construction on universal prototyping board size-1.

#### COMPONENTS LIST

| Re | esistors:               |                |        |

|----|-------------------------|----------------|--------|

| 1  | 4k7                     | Rı             |        |

| 1  | 1M0                     | R <sub>2</sub> |        |

| 1  | 10k                     | R3             |        |

| 2  | 820k                    | R4;R6          |        |

| 1  | 150k                    | R <sub>5</sub> |        |

| 1  | 1M0 preset H            | P1             |        |

| 1  | 500k preset H           | P <sub>2</sub> |        |

| Ca | apacitors:              |                |        |

| 1  | 1µ0 16V                 | C1             |        |

| 1  | 330pF                   | C2             |        |

| 1  | 100nF                   | Сз             |        |

| Se | miconductors:           |                |        |

| 1  | LM336                   | D1             |        |

| 1  | LM235                   | D2             |        |

| 1  | 1N4148                  | D3             |        |

| 1  | TLC272                  | IC1            |        |

| Mi | scellaneous:            |                |        |

| 1  | push-to-make button     |                | S1     |

| 1  | miniature on/off switch |                | S2     |

| 1  | passive buzzer          |                | Bz1    |

| 1  | 9-V battery             |                | Bti    |

| 1  | printed-circuit board   |                | UPBS-1 |

|    |                         |                |        |

put of the comparator is high, i.e., virtually equal to the battery voltage. The oscillator, A<sub>2</sub>, is disabled because the junction of its frequency-determining components, P<sub>2</sub>-C<sub>2</sub>, is held at about +9 V via

Fig. 3. Completed printed-circuit board with external components connected.

diode D<sub>3</sub>. Hence, buzzer Bz<sub>1</sub> remains silent.

This condition is ended when the measured temperature rises above the set threshold. In electronic terms, this means that the voltage supplied by D<sub>2</sub> is higher than that at the +input, so that A<sub>1</sub> toggles and supplies a low output voltage. Diode D<sub>3</sub> blocks and decouples the output of A<sub>1</sub> from the oscillator, A<sub>2</sub>. Buzzer Bz<sub>1</sub> is actuated and supplies an acoustic signal of which the frequency is determined by P<sub>2</sub>.

Push-button S<sub>1</sub> allows the circuit to be reset following an alarm condition. When pressed, it causes C<sub>1</sub> to be charged to the supply voltage, so that the voltage at the +input of A<sub>1</sub> is higher than that at the -input, irrespective of the voltage supplied by D<sub>2</sub>. Pressing S<sub>1</sub> therefore disables the oscillator. Evidently, C<sub>1</sub> will be discharged slowly via P<sub>2</sub> and R<sub>1</sub>. This takes a while, however, because of the relatively high value of the components. The upshot is that D<sub>2</sub> will have cooled down to a temperature below the alarm level well before the voltage at the +input of A<sub>1</sub> has fallen below the reference voltage.

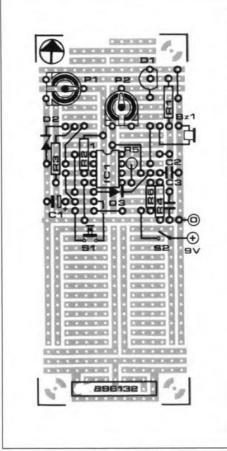

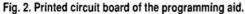

# Construction and adjustment

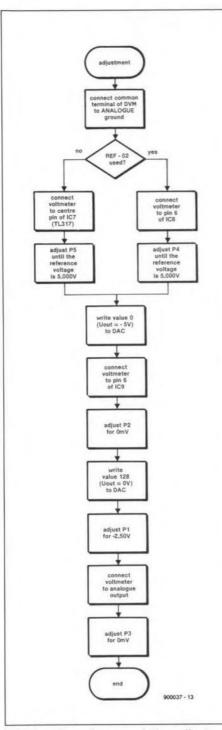

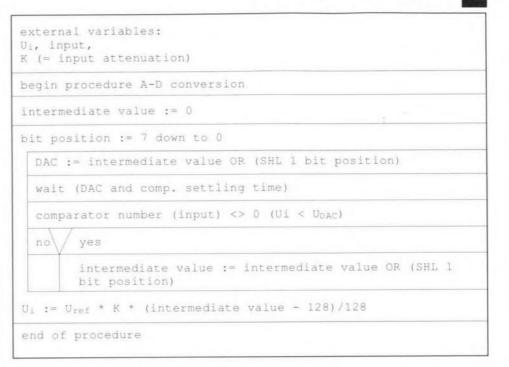

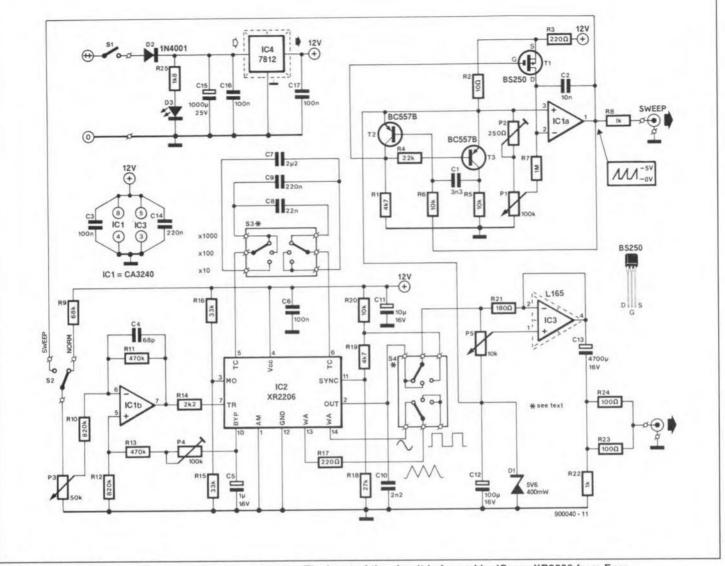

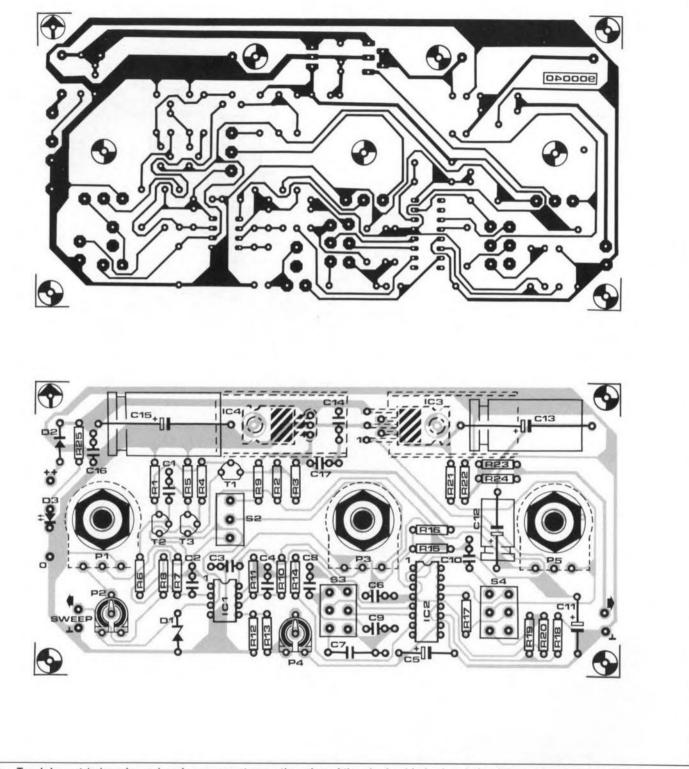

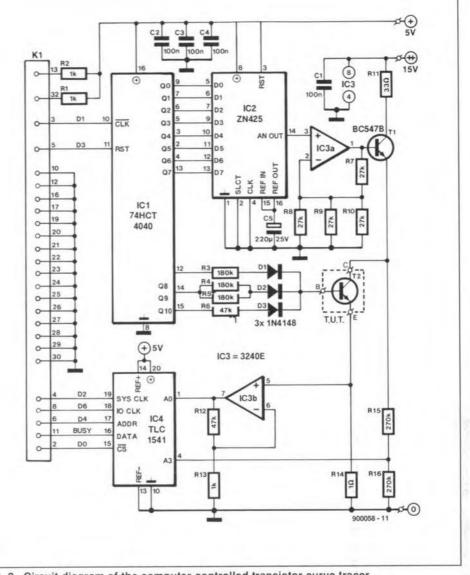

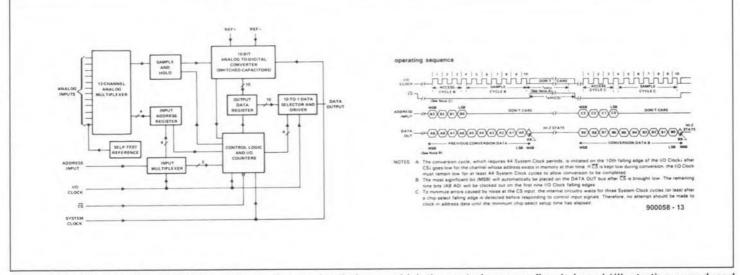

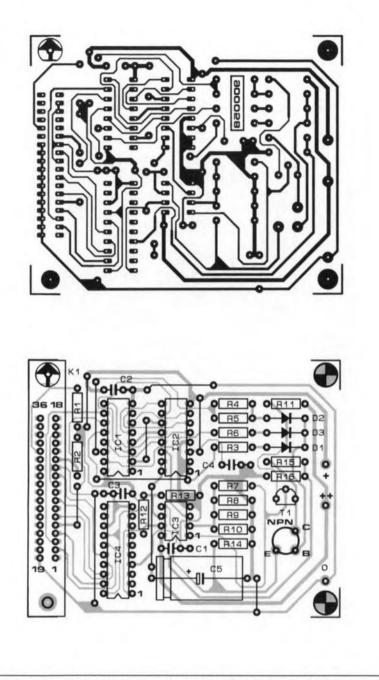

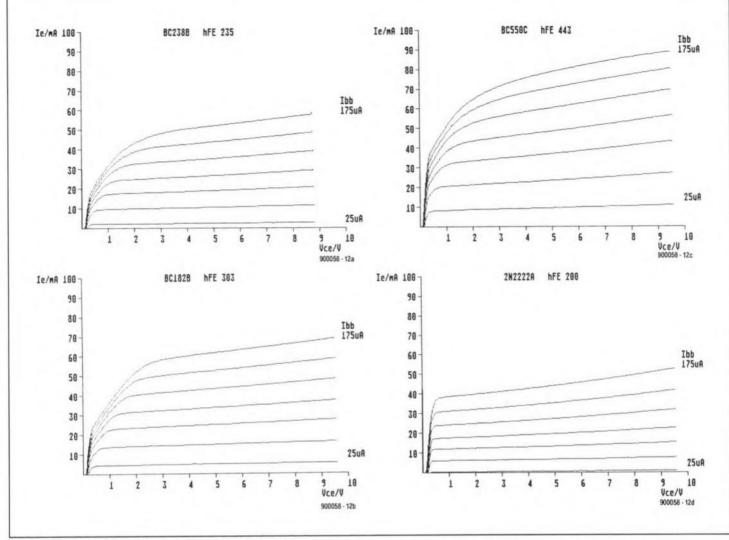

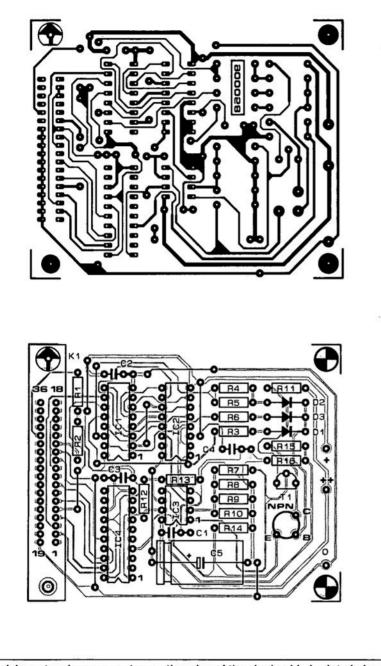

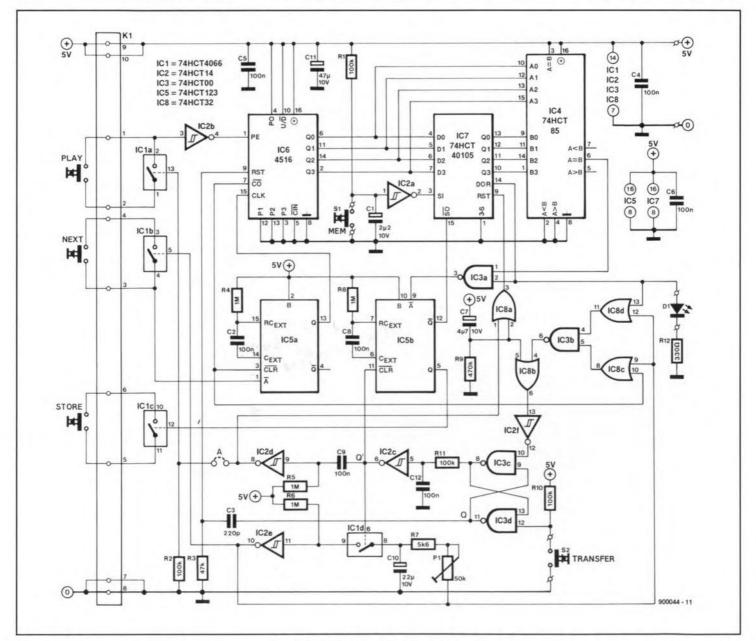

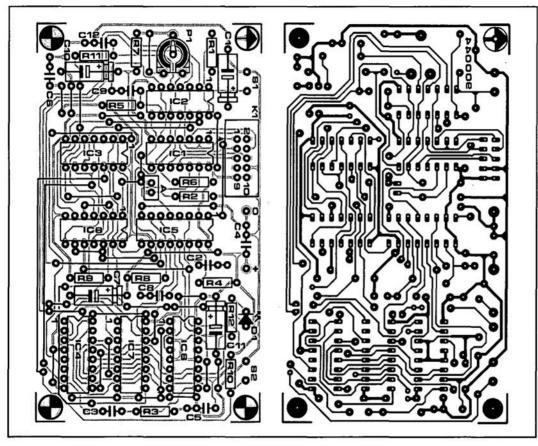

A suggested arrangement of the components on universal prototyping board size-1 (UPBS-1) is shown in Fig. 2. The population of this PCB should not present any problems. The buzzer, the temperature sensor, the battery and the two switches (reset and on/off) are external components, which are connected to the circuit via wires and solder terminals. In most cases, the alarm will be set for a fixed temperature, e.g., approximately 100 °C for boiling water. This allows a preset to be used as shown in the component mounting plan. If a variable temperature setting is required, P<sub>1</sub> is replaced by a potentiometer which is fitted on the front panel of the enclosure.