THE ELECTRONICS MAGAZINE WITH THE PRACTICAL APPROACHUK £1.70IR £2.62 (incl. VAT)January 1990

Video Mixer Mini EPROM Programmer Simple AC Millivoltmeter HC Oscillators 8052 modification CMOS Preamplifier (2) RS

### Theme of the month in February will be Audio & hi-fi

Also in the February issue:

- Dark room clock

- Video mixer (Part 2)

- Car theft deterrent

- Current sensors

- Feedback killer

- Capacitance meter

- PC radio

- Waveform modulation of the mains voltage

- Initialization aid for printers

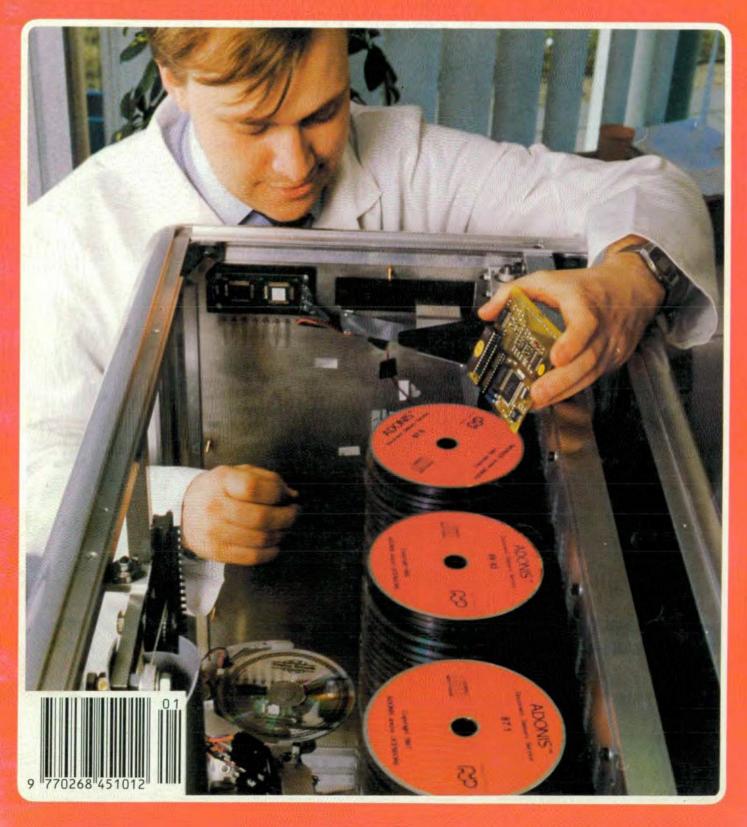

## Front cover

A software engineer inserts a microprocessor board into a Voyager CD-ROM jukebox disc library that has been designed and built by Next Technology Corporation of Cambridge.

Voyager is a floor-standing unit intended to slide under or stand alongside a desk and has a capacity for up to 270 compact discs and 8 CD-ROM drives.

Each CD can be used to hold large amounts of information, such as text, video or sound that can be retrieved quickly by a computer. In computer terms, it can hold over 175 Gigabytes of information. The British Library uses the system as part of the Adonis project, which stores over 200 biomedical journals on CD-ROM.

## CONTENTS

### LEADER

11

14

44

57

33

Radio makes a comeback

### **AUDIO & HI-FI**

27 PROJECT: All-solid-state preamplifier – Part 2 by T. Giffard

## COMMUNICATIONS

18 PROJECT: Telephone answering unit an ELV design

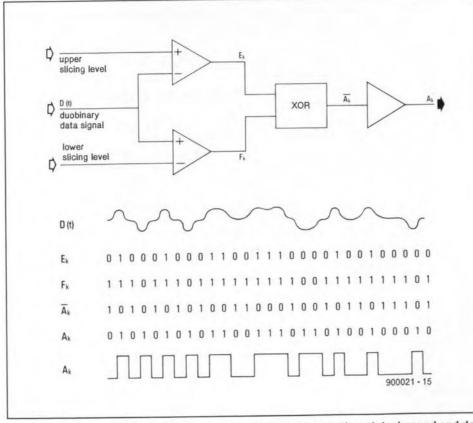

50 Introduction to duobinary encoding and decoding by J. Buiting

## COMPONENTS

62 HCMOS oscillators by J. Ruffell

### COMPUTERS

| PROJECT: EPROM programmer                  |

|--------------------------------------------|

| by J. Ruffell                              |

| PROJECT: CMOS RAM control for PC/AT        |

| from an idea by H. van den Bosch           |

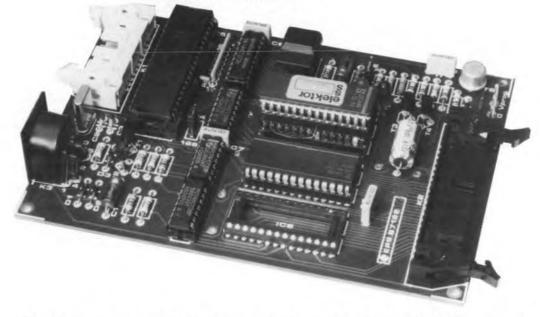

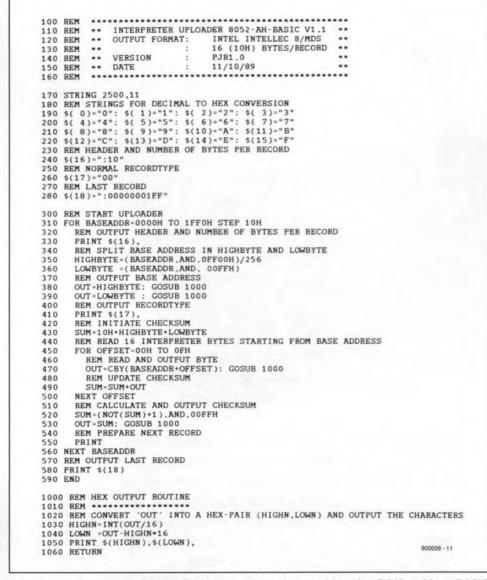

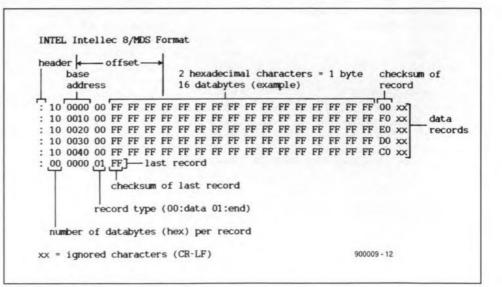

| PROJECT: CMOS replacement for 8052AH-BASIC |

| by J. Ruffell                              |

|                                            |

## GENERAL INTEREST

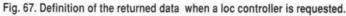

38 PROJECT: The digital model train - Part 10 by T. Wigmore

## INTERMEDIATE PROJECT

60 One-wire intercom by J. Bareford

### **RADIO & TELEVISION**

**PROJECT**: Video mixer – Part 1 by A. Rigby

## SCIENCE & TECHNOLOGY

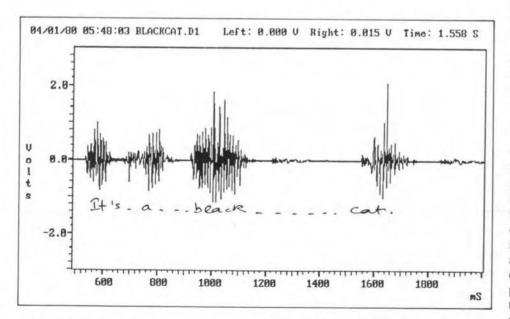

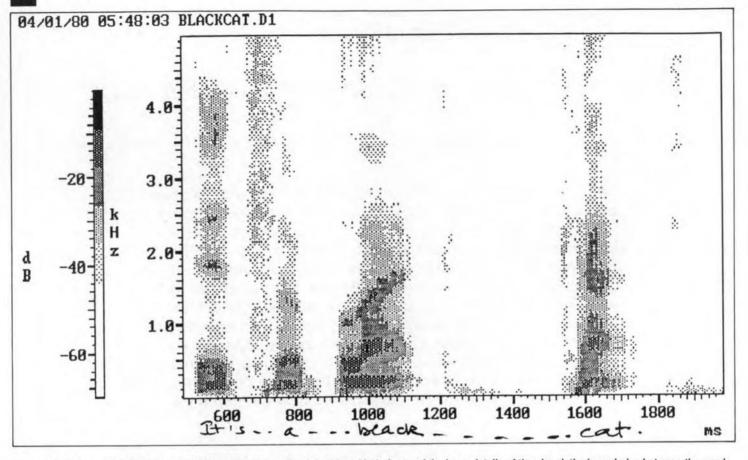

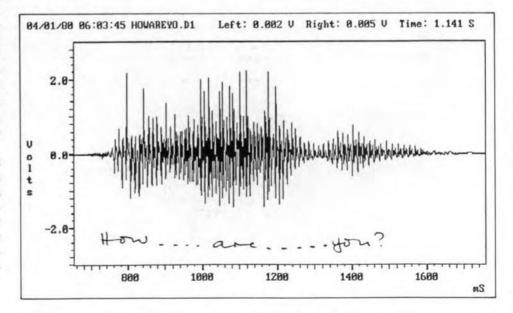

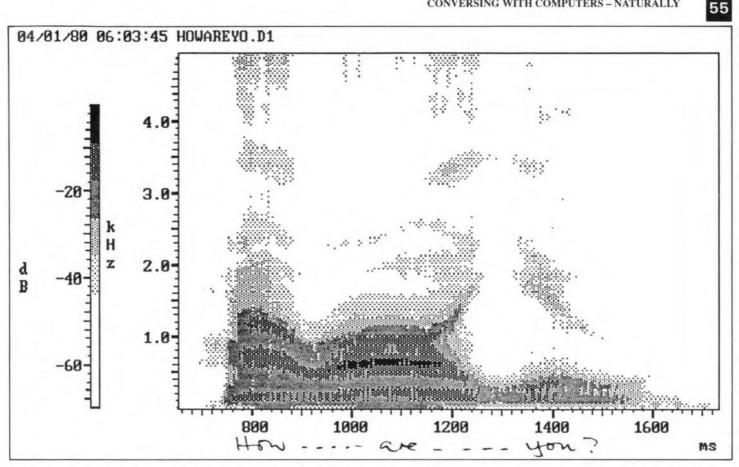

53 Conversing with computers – naturally by Professor Marcel Tatham

### **TEST & MEASUREMENT**

22 PROJECT: Simple AC millivoltmeter by T. Giffard

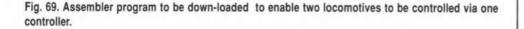

46 PROJECT: 1 GHz frequency meter card for PCs by H. Kolter

### INFORMATION

Electronics scene 13; New books 26; Events 43; Readers services 67

### **GUIDE LINES**

Switchboard 68; Buyers' guide 74; Classified ads 74; Index of advertisers 74

January 1990

Volume 16 Number 174

Simple AC millivoltmeter - p.22

3

# **MINI EPROM PROGRAMMER**

J. Ruffell

Many constructors have good reasons for preferring a low-cost EPROM programmer with manual data and address to a full-blown programmer operating under computer control. First, they may not have a computer; second, they do not mind spending some time on programming small amounts of data; and third, they object to the expenditure on an instrument that is only occasionally called upon.

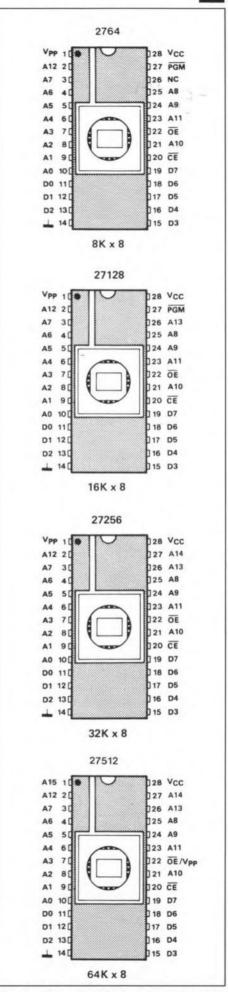

The programmer is definitely not intended for loading huge amounts of data into EPROMs. Even if you could manage to program bytes faultlessly at a rate of one per second, it would take more than 18 hours to load all 65,536 bytes (64 Kbytes) in a Type 27512 EPROM, the largest the present programmer can handle. Moreover, it is a common misunderstanding to associate EPROMs with microcomputer systems that require large amounts of data. As has been shown in a number of projects in this magazine over the past few months, there are quite a few occasions where no more than, say, 256 or 512 bytes are involved, such as where EPROMs function as programmable look-up or conversion tables.

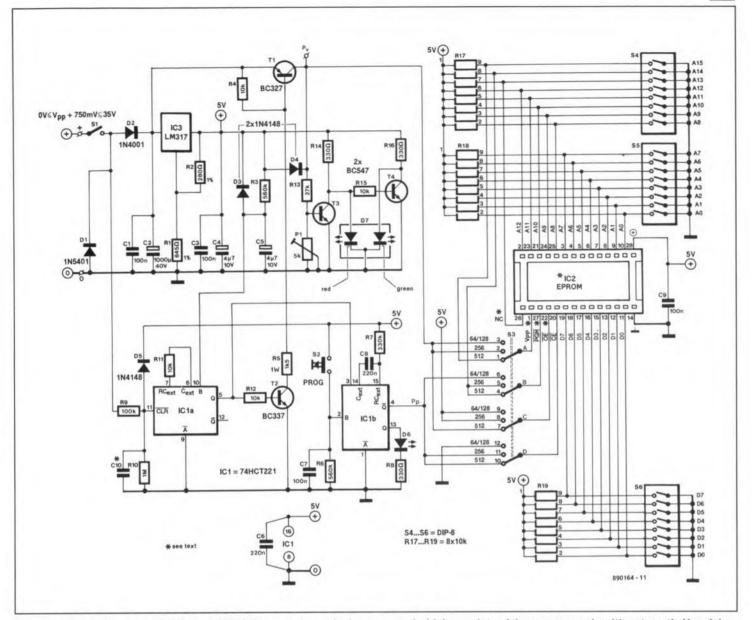

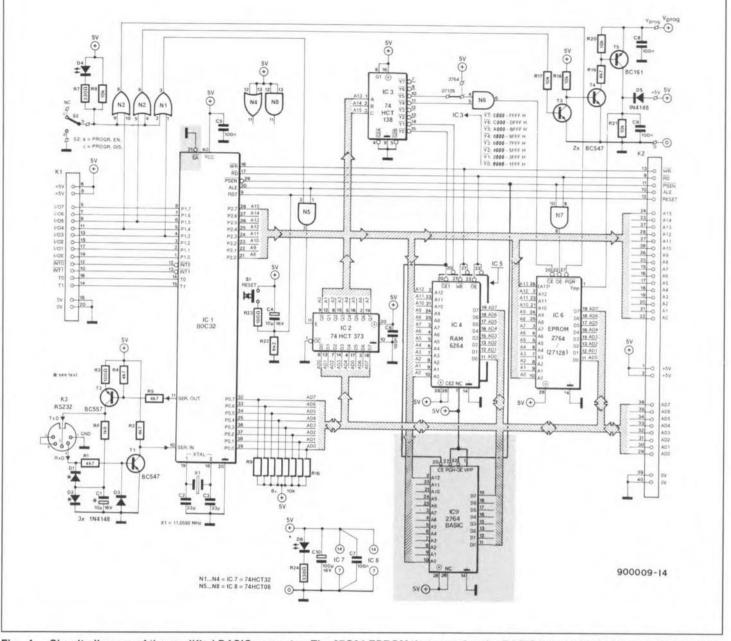

Although the circuit diagram of the mini EPROM programmer (Fig. 1) looks crowded, it should be noted that most components go into the power supply to ensure that the high programming voltage is not applied to the EPROM until the 5 V supply voltage is present — the reverse sequence would have disastrous consequences. Also note that an EPROM must

never be removed from the working programmer, because the order in which the programming voltage and the supply voltage are removed might just be wrong.

## How it works

Although the supply circuit already looks quite crowded in places, it is not complete without an external regulated power supply to furnish the programming voltage plus about 750 mV. The input voltage to the circuit may be adjusted by measuring the programming voltage at point Pv. The programming voltage is determined by the EPROM type and its manufacturer.

Regulator IC<sub>3</sub> reduces the programming voltage to 5 V which is used to power the EPROM and the programmer circuit. Transistor T<sub>1</sub> prevents the programming voltage being applied to the EPROM before the 5 V supply voltage. The transistor is controlled by a monostable multivibrator (MMV), IC<sub>1a</sub>. After this has been triggered, its Q output remains high until it is reset via its CLR input. This input is connected to the rest of the circuit in a manner to ensure that IC<sub>1a</sub> is reset if the +5 V supply voltage disappears, or when there is no supply voltage at all. The latter condition may appear superfluous, but the programming voltage is immediately

disconnected from the relevant EPROM pin when the programmer is switched off with S1. The 5 V supply voltage, however, remains present for a short while because the electrolytic capacitors take some time to discharge. Conversely, IC1a can not be set until the +5 V supply voltage is present. The SET input of the MMV is formed by trigger input B, which is connected to network R3-C5. The voltage on C5 takes a few seconds to rise to a level that enables IC1a to be set, and, consequently, the programming voltage to be applied to the EPROM. Capacitor C10 is required only if the CLR input of IC1a is erroneously actuated by input voltage fluctuations. The value of C10 should be between 100 pF and 10 nF and must be determined empirically. In general, the capacitor must be kept as small as possible.

Bi-colour LED  $D_7$  indicates the status of the EPROM programmer. The LED turns red (T<sub>3</sub> off; T<sub>4</sub> on) if the 5 V supply voltage is present, and green if both the 5 V and the programming voltage are present.

The circuit around IC<sub>1b</sub> (also a MMV) is a pro-

gramming pulse generator. When S<sub>2</sub> is actuated, a single 50-ms programming pulse is generated. An intelligent programming algorithm with variable programming pulse length is, of course, not feasible in a simple circuit like this. Even if it were available, the total programming time would not be reduced because the data and addresses are set manually, which takes much longer than 50 ms in any case.

The bulk of the signals in the programmer circuit emanates from DIP switches and associated pull-up resistors. Addresses are set with S4 and S5, data with S6. Switch S3 is used to select the EPROM type. The connections it makes are in ac-

Fig. 1. Circuit diagram of the budget EPROM programmer, the larger part of which consists of the power supply with automatic Vpp delay.

cordance with the EPROM data listed in Table 1.

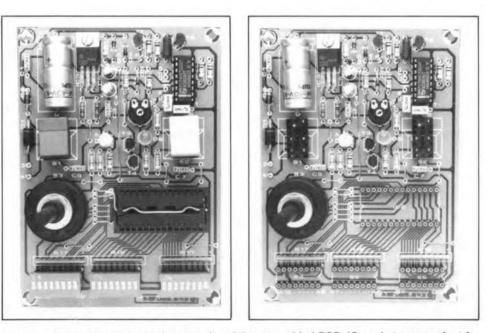

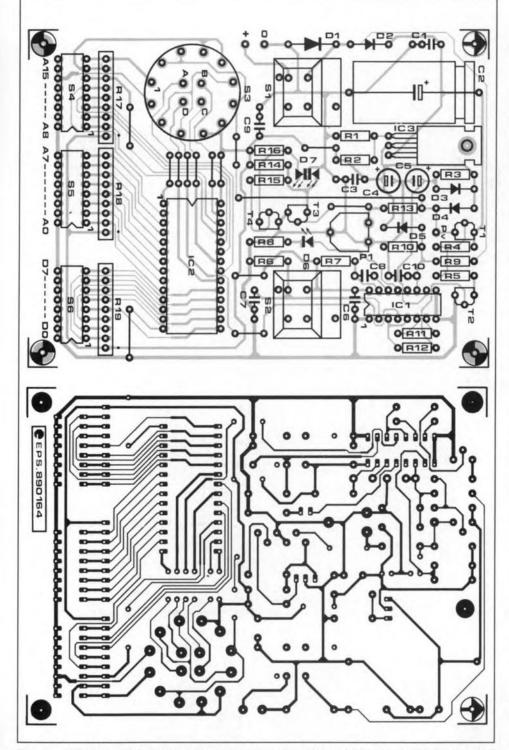

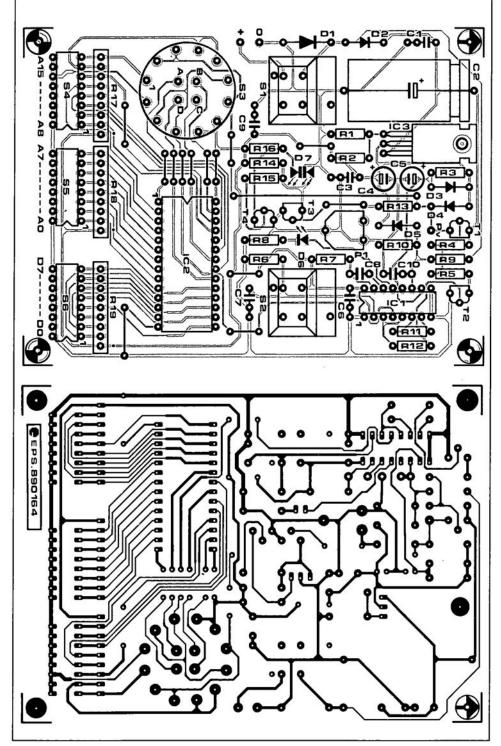

## Construction

The printed-circuit board for the programmer is shown in Fig. 3. Start the construction by fitting the wire links. Next, fit the resistors and capacitors. Each of the three single-in-line (SIL) resistor arrays may be replaced by eight vertically mounted, discrete resistors whose upper terminals are cut short and commoned by a horizontal wire that goes into the hole provided for the +5 V connection of the array.

The semiconductors are fitted next, with the exception of the LEDs. IC<sub>3</sub> does not need a heat-sink, and is bolted straight on to the PCB. Mount rotary switch S<sub>3</sub>, but do not cut its spindle as yet.

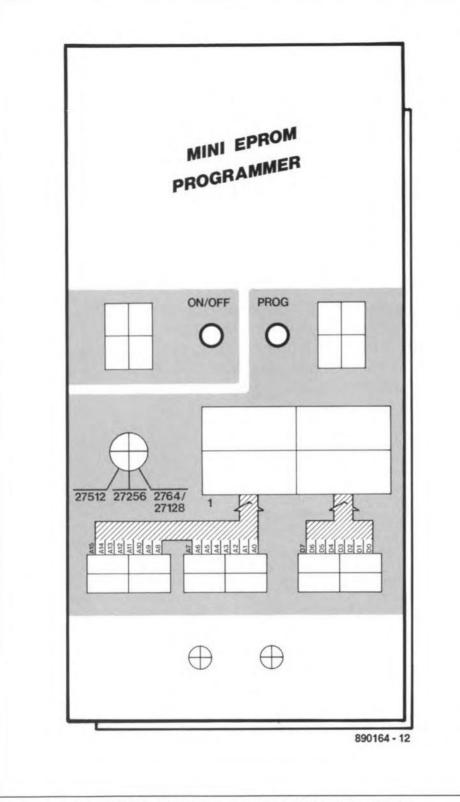

Be sure to mount the components that protrude from the front panel at the correct height above the board. This involves the LEDs, on/off switch S<sub>1</sub>, programming switch S<sub>2</sub>, the data/address DIP switches and the ZIF (zero-insertion force) socket

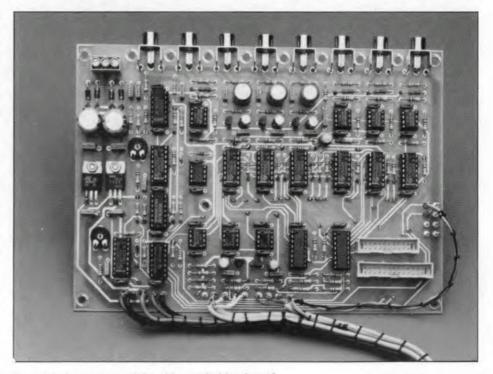

Fig. 2. As shown on these photographs of the assembled PCB, IC sockets are perfect for mounting the push-buttons and the DIP switch blocks. SIL strips are used for the ZIF socket. The height of the prototype enclosure did not require low-profile IC sockets to be stacked.

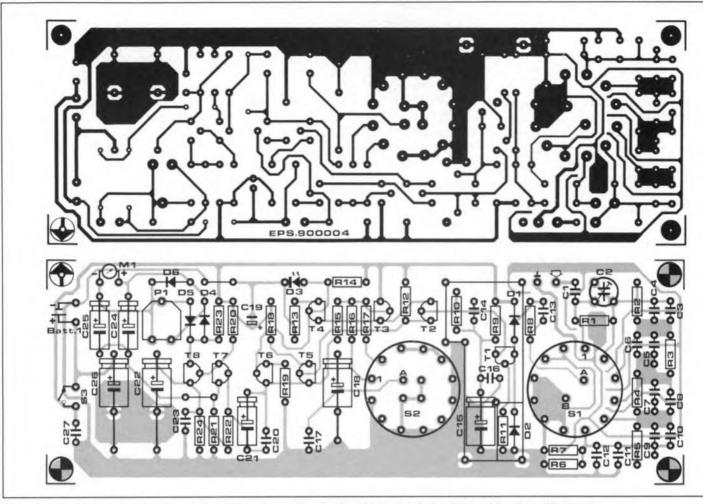

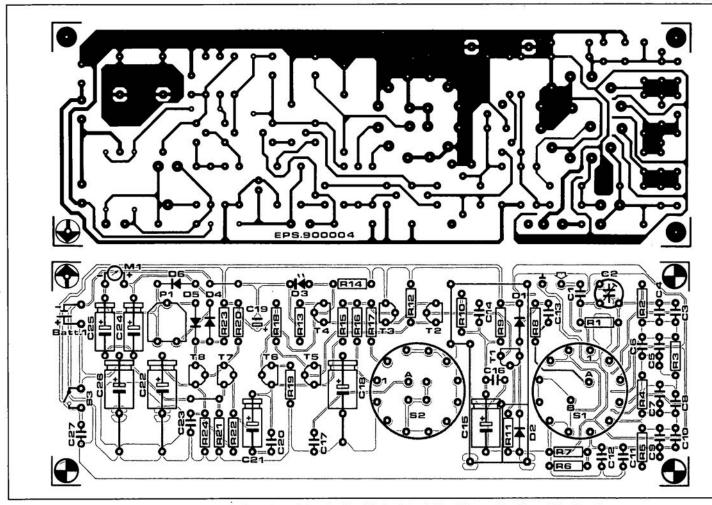

Fig. 3. Track layout and component mounting plan of the single-sided PCB for the mini EPROM programmer. Start the construction with fitting the wire links.

for the EPROM. A good way of achieving the correct height for the DIP switches is to use wire-wrap sockets or simply three or four stacked low-profile IC sockets (see Fig. 2). Much depends on the enclosure used.

Figure 4 shows a suggested lay-out for the front panel of the programmer. Make a photocopy of this drawing and use it as a template to cut and drill the metal or ABS front-panel of your enclosure.

## Setting up

Connect the external power supply and adjust it to an output that results in +10.0 V at point Pv (you may have to wait

| Pin | 2764 | 27128 | 27256 | 27512  |

|-----|------|-------|-------|--------|

| 1   | Vpp  | Vpp   | Vpp   | A15    |

| 22  | ŌĒ   | ŌE    | ŌĒ    | OE/Vpp |

| 26  | n.c. | A13   | A13   | A13    |

| 27  | PGM  | PGM   | A14   | A14    |

| Signal | 2764 | 27128 | 27256 | 27512 |

|--------|------|-------|-------|-------|

| ŌĒ     | н    | н     | н     |       |

| OE/Vpp |      |       |       | Pv    |

| Vpp    | Pv   | Pv    | Pv    |       |

| CE     | L    | Ĺ     | ĿF    | ĿF    |

| PGM    | LF   | LF    |       |       |

Table 1. EPROM programming data as set by the EPROM type switch on the front panel.

### Resistors:

$\begin{array}{l} R_1 = 845\Omega; \ 1\% \\ R_2 = 280\Omega; \ 1\% \\ R_3; R_6 = 560k \\ R_4; R_{11}; R_{12} = 10k \\ R_5 = 1k5; \ 1W \\ R_7 = 330k \\ R_8; R_{14}; R_{16} = 330\Omega \\ R_9 = 100k \\ R_{10} = 1M0 \\ R_{13} = 27k \\ R_{15} = 10k \\ R_{17}; R_{18}; R_{19} = 8 \text{-resistor}; 9 \text{-pin SIL} \\ resistor array 10k \\ P_1 = 5k \text{ preset H} \end{array}$

### Capacitors:

$\begin{array}{l} C_{1};C_{3};C_{7};C_{9}=100n\\ C_{2}=1000\mu;\,40\ V\\ C_{4};C_{5}=4\mu7;\,10\ V;\,radial\\ C_{6};C_{8}=220n \end{array}$

## Semiconductors:

$\begin{array}{l} D_1 = 1N5401 \\ D_2 = 1N4001 \\ D_3; D_4; D_5 = 1N4148 \\ D_6 = LED \\ D_7 = 3 \text{-terminal bi-colour LED} \\ T_1 = BC327 \\ T_2 = BC337 \\ T_3; T_4 = BC547 \\ IC_1 = 74HCT221 \\ IC_2 = EPROM \text{ to be programmed} \\ IC_3 = LM317 \end{array}$

### Miscellaneous:

S1 = self-locking push-button; ITW Type 61-20204000 +. S2 = momentary action push-button; ITW Type 61-10204000 +. S3 = PCB-mount 4-pole 3-way rotary switch. S4;S5;S6 = 8-way DIP switch block. 28-way IC socket (ZIF type preferred). PCB Type 890164 (see Readers Services page).

We regret that the front-panel foil for this project is not available ready-made.

ITW Switches • Division of ITW Ltd. • Norway Road • Hilsea • PORTSMOUTH PO3

5HT. Telephone: (0705) 694971.

17

Fig. 4. Suggested front-panel layout shown at true size for easy reproduction.

a second or two until T<sub>1</sub> is turned on). Adjust P<sub>1</sub> until the status LED changes colour. This completes the adjustment procedure.

## Do's and don'ts

There are a few basic rules to keep in mind when using the mini EPROM programmer:

Before inserting an EPROM, always check the programming voltage at point Pv and adjust your power supply to set the correct value for the device to be programmed. Next, set the EPROM type on S<sub>3</sub>.

- Never insert or remove an EPROM with the programmer switched on.

- And, finally, think before actuating the programming switch!

**ELEKTOR ELECTRONICS JANUARY 1990**

Fig. 3. Track layout and component mounting plan of the single-sided PCB for the mini EPROM programmer. Start the construction with fitting the wire links.

for the EPROM. A good way of achieving the correct height for the DIP switches is to use wire-wrap sockets or simply three or four stacked low-profile IC sockets (see Fig. 2). Much depends on the enclosure used.

Figure 4 shows a suggested lay-out for the front panel of the programmer. Make a photocopy of this drawing and use it as a template to cut and drill the metal or ABS front-panel of your enclosure.

## Setting up

Connect the external power supply and adjust it to an output that results in +10.0 V at point Pv (you may have to wait

| Pin | 2764 | 27128 | 27256 | 27512  |

|-----|------|-------|-------|--------|

| 1   | Vpp  | Vpp   | Vpp   | A15    |

| 22  | ŌĒ   | ŌĒ    | ŌE    | OE/Vpp |

| 26  | n.c. | A13   | A13   | A13    |

| 27  | PGM  | PGM   | A14   | A14    |

| Signal | 2764 | 27128 | 27256 | 27512 |

|--------|------|-------|-------|-------|

| ŌĒ     | н    | н     | н     |       |

| OE/Vpp |      |       |       | Pv    |

| Vpp    | Pv   | Pv    | Pv    |       |

| CE     | L    | L     | LF    | ЪЪ    |

| PGM    | LF   | 1.5   |       |       |

Table 1. EPROM programming data as set by the EPROM type switch on the front panel.

### Parts list

### **Resistors:**

R1 =  $845\Omega$ ; 1% R2 =  $280\Omega$ ; 1% R3;R6 = 560kR4;R11;R12 = 10kR5 = 1k5; 1 W R7 = 330kR8;R14;R16 =  $330\Omega$ R9 = 100kR10 = 1M0R13 = 27kR15 = 10kR17;R18;R19 = 8-resistor; 9-pin SIL resistor array 10kP1 = 5k preset H

### Capacitors:

C1;C3;C7;C9 = 100n C2 = 1000 $\mu$ ; 40 V · C4;C5 = 4 $\mu$ 7; 10 V; radial C6;C8 = 220n

### Semiconductors:

D1 = 1N5401 D2 = 1N4001 D3;D4;D5 = 1N4148 D6 = LED D7 = 3-terminal bi-colour LED T1 = BC327 T2 = BC337 T3;T4 = BC547 IC1 = 74HCT221 IC2 = EPROM to be programmed IC3 = LM317

### Miscellaneous:

S1 = self-locking push-button; ITW Type 61-20204000 +. S2 = momentary action push-button; ITW Type 61-10204000 +. S3 = PCB-mount 4-pole 3-way rotary switch. S4;S5;S6 = 8-way DIP switch block. 28-way IC socket (ZIF type preferred). PCB Type 890164 (see Readers Services page).

We regret that the front-panel foil for this project is not available ready-made.

+ ITW Switches • Division of ITW Ltd. • Norway Road • Hilsea • PORTSMOUTH PO3 5HT. Telephone: (0705) 694971.

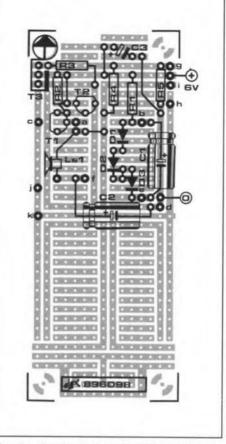

This automatical telephone answering unit, designed by ELV GmbH, uses a 256-Kbit voice recording circuit to store and replay your spoken message of up to 15 seconds. Noteworthy features are that it is available as a complete kit, provides a battery back-up facility, and does not require alignment. No provision is made, however, to record incoming calls.

From the onset, it should be made clear that the telephone answering unit is not type-approved by British Telecom, and may not be connected to the public switched telephone network (PSTN). This limits its use to domestic and office telephone exchanges. In countries other than the UK, the relevant PTT authorities should be contacted for information on type approval.

A digital sound processing circuit in the telephone answering unit does away with the need of the more usual cassette or tape recorder to replay the recorded message. Apart from its four front-panel mounted controls, the unit has no parts or controls subject to mechanical wear and tear.

The unit is of the direct-coupled type, i.e., it does not use a costly transformer that complicates the line interface circuit and limits the speech bandwidth.

## Simple to connect and operate

The telephone answering unit is simply connected in parallel with the line terminals inside an existing telephone set. In most European countries, the telephone line connections are marked 'a' and 'b', or 'LA' and 'LB'. Although terminals 'a' and 'b' have the corresponding indications on the printed-circuit board, the connections between the line and the telephone answering unit may be reversed without causing damage because the input of the circuit uses a bridge rectifier.

The unit is powered by an inexpensive mains adaptor with an unregulated output voltage of 12 VDC at 100 mA.

The on/off switches and the associated indicator LED are located at the left of the

front panel. The unit is switched on and off by briefly pressing the relevant button. The LED lights at normal intensity if

the unregulated input voltage supplied by the mains adaptor is between 12 V and 15 V. A 9 V rechargeable battery inside the enclosure ensures that the answering unit remains operative during mains voltage interruptions. The 'on' LED lights at reduced intensity if the unit is batterypowered. An internal voltage monitor ensures that the unit is automatically switched off when the battery voltage drops below 7.5 V. When the mains voltage is switched on again, the battery is recharged, but the answering unit is not switched on automatically because the speech content of its internal RAM is erased or corrupted. The unit can be taken into operation again only by switching it on with the front panel control.

To record a message, press the RECORD button briefly. The associated LED lights. Wait one or two seconds before delivering the message via the built-in condenser microphone located between the RECORD key and the LED. Speak at a distance of about 20 cm to 50 cm from the microphone. An internal amplifier with leveldependent gain ensures the best drive margin for the speech digitizer.

There is no technical reason for the short pause before the message, but callers may be unable to hear the first two or three words of the message because of the connection noise that is often heard immediately after a call is answered.

The telephone answering unit has an outgoing message length of 15 seconds. This may appear relatively short, but in reality allows a message of reasonable duration to be recorded without having to speak too quickly.

The LED at the centre of the front panel lights when the recorded message is transmitted. This happens automatically when the unit answers the call, or manually when the START button is pressed. Although the message can be heard by picking up the receiver of the parallel-connected telephone set, the line driver circuit in the answering unit can not be overridden by the normal speech signal. The line circuit eliminates virtually any external signal that resembles line unbalance or noise. This means that you can not hear the calling party, while the calling party hears the answer message only.

The recorded message may be interrupted while it is transmitted by pressing the OFF key. It should be noted, however, that this also clears the message.

A new message may be recorded as often as required by pressing the RECORD key. The previous message is automatically cleared to make the practical use of the answering unit as simple as possible.

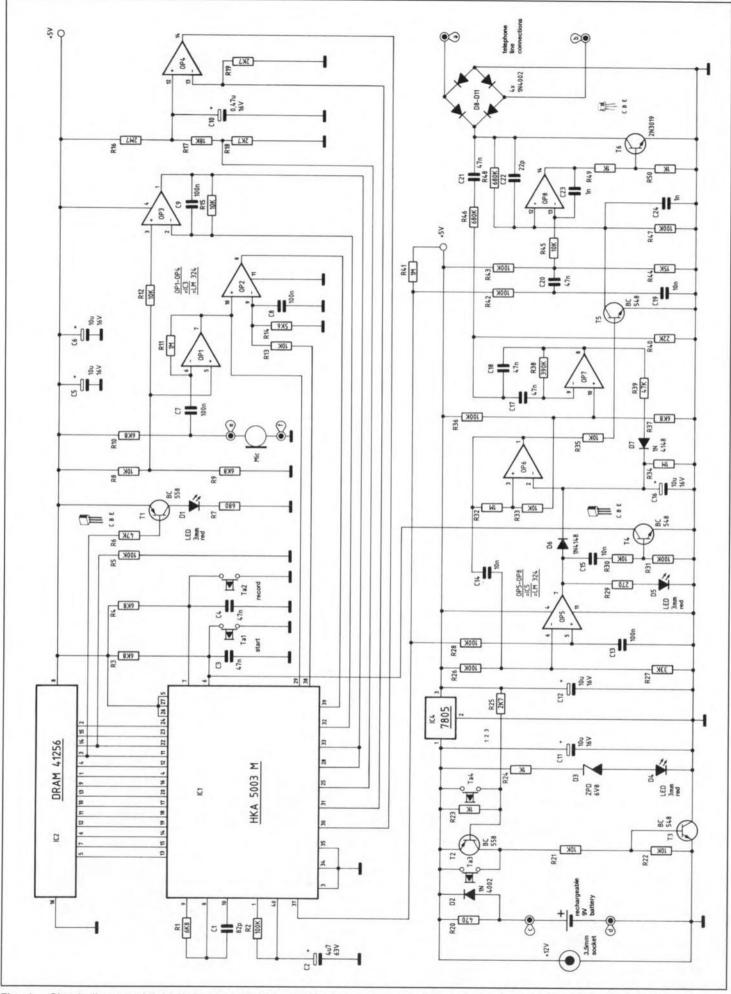

## **Circuit description**

The circuit diagram in Fig. 1 shows that the AF signal supplied by the electret microphone is applied to the –input (pin 6) of opamp OP1 via coupling capacitor C7. The gain of the opamp is determined by feedback resistor R11. The amplified microphone signal at pin 7 is applied to the comparator input, pin 29, of the voice recorder chip, IC1.

The signal conversion and storage circuit works on the basis of adaptive delta modulation (ADM). In this process, a comparator is used to determine whether the instantaneous level of an analogue input signal is above or below that of the reference level established by summation

889504

Fig. 1. Circuit diagram of the telephone answering unit. The answer message is recorded and stored digitally in 256-kbit RAM chip IC2.

**ELEKTOR ELECTRONICS JANUARY 1990**

COMMUNICATIONS

of previously taken samples. The result of the comparison is a 0 or a 1 which is stored into the memory. The next step involves a further comparison between the current input level and the new (*adaptively* established) reference level. The result is another 0 or 1 which goes into the memory.

The digital-to-analogue conversion is essentially the reverse process, and is based on current-controlled integration of the digital memory data. The content of the memory is fed out sequentially. Any 1 or 0 causes the current output amplitude to become greater or smaller respectively.

The Type HKA5003M integrated circuit requires only four external opamps and a handful of passive components to handle the D-A and A-D conversions, as well as the memory addressing. Unfortunately, the scope of this article does not allow a closer analysis of the internal operation of the HKA5003M to be given, so that it has to be treated like a black box.

Random-access memory (RAM) chip IC2 has capacity for storing up to 262,144 bits (0s or 1s). At a maximum speech recording time of 15 s, this results in a data rate of 17,476 bits per second, which corresponds to 'almost' six bits for an AF input frequency of 3,000 Hz. Since this 'digital resolution' is too low to ensure acceptable quality of the digitized speech signal, the dynamic response of IC1 is boosted. This is achieved with an internal current source which is composed of quantization stages, and controlled by a 4-bit shift register. The quantization level of the current source is incremented when the shift register contains only 0s or 1s, and is reduced to almost nought at small input signal levels and low frequencies to eliminate background noise. The operation of the quantization stages is not unlike that of a compander, and ensures acceptable playback quality for signals up to 3,000 Hz, i.e, for most components in the frequency spectrum of speech.

### Answer circuit

The speech processor chip has an onboard refresh controller which allows an inexpensive dynamic RAM to be used. All 262,144 bits are read sequentially to transmit the 15-s message. The serial signal at pin 37 of IC1 is applied to integrator C19 via R42. Coupling capacitor C20 feeds the filtered signal to the output driver formed by OPs, T6 and associated parts. Output pin 14 of OPs is connected to the base of T6 via R29 and R50. This causes the collector voltage of T6 to take a value that results in equal voltages at the inverting (-) and non-inverting (+) inputs of opamp OPs. The -input is held at a reference voltage of about +0.6 V by potential divider R43-R44. With the amplification of the opamp determined by R47-R48, a voltage of about 5 V is obtained at the collector of T<sub>6</sub>, but only when the unit is actuated, i.e., effectively connected to the telephone line.

The reference voltage at junction R43-R44-R45-C20 is modulated with the digitized speech signal. As a result, this is superimposed on to the collector voltage of T<sub>6</sub>, and from there, on to the telephone line.

The above situation applies to the 'playback' mode only, i.e., when the unit is answering a call. Otherwise,  $T_5$  is turned on, so that the +input of OPs is at a lower potential than the -input. As a result, opamp output pin 8 is at virtually 0 V, keeping T<sub>6</sub> disabled. The telephone line terminals (a and b) are at 50 V to 60 V.

### **Receive** circuit

When the extension is called, components C21 and R46 feed ring signals on the line to a bandfilter around OP7. The alternating output voltage of OP7 is rectified by R39-D7 and applied to combination C16-R34. After a few ring pulses, the voltage on C16 exceeds that at the +input of OP6, which consequently toggles. The resultant low level at the output of the opamp causes T5 to be turned off via R35. This, in turn, causes the output stage to be enabled via pin 12 of OPs. The output transistor, T6, is driven to a level where its collector is at about 5 V. This enables the telephone exchange to detect that the call is being answered.

Next, C14 causes OP5 to toggle and supply a high level at its output. The resultant pulse from C15-R30 is applied to the base of T4, whose collector voltage drops briefly. The START input of IC1, pin 6, is taken low. The output voltage at pin 37 of the speech synthesizer rises from 0.5 V to about 2.0 V when the answer message is being transmitted. This level enables the state of comparator OP5 to be frozen via R28 while the message lasts (approx. 15 s). Capacitor C16 is also charged, so that T5 is kept off in the absence of a ring signal.

When the recorded message is finished, the voltage at pin 37 of IC1 reverts to 0.5 V, so that the output of OP5 goes low, and C16 is slowly discharged. When the voltage on C16 drops below the reference voltage of OP6, the opamp toggles and supplies a high level at its output. As a result, T5 is turned on, and T6 is turned off via OP8 so that the answering unit is disconnected from the telephone exchange. It is connected back again by ring pulses as explained above.

### Power supply

In most cases, the mains adaptor is only lightly loaded, so that its output voltage is between 13 V and 15 V. The 9 V battery in the answering unit is charged via R<sub>2</sub>.

Power indicator D4 passes the current through series resistor R24 and zener diode D3, and lights at its nominal intensity.

When button Ta<sub>3</sub> (ON) is pressed, the circuit is powered by T<sub>3</sub>, which is turned on via R<sub>21</sub>. The voltage across regulator IC<sub>4</sub> is about 9 V (14 – 5), which switches on T<sub>2</sub> via potential divider R<sub>23</sub>-R<sub>25</sub>. When Ta<sub>3</sub> is released, the circuit remains on by virtue of R<sub>23</sub> which feeds a base current into T<sub>3</sub>.

Voltage regulator IC4 provides the 5 V supply voltage for the entire circuit. When the mains voltage disappears, D<sub>2</sub> con-

### Parts list

**Resistors:**  $R_{29} = 270\Omega$  $R_{20} = 470\Omega$  $R_7 = 680\Omega$ R23;R24;R49;R50 = 1k0 R18;R19;R25 = 2k7  $R_{14} = 5k6$ R1:R3:R4;R9:R10;R37 = 6k8 Rs;R12;R13;R15;R21;R22;R30;R33; R35:R45 = 10k  $R_{44} = 15k$ R17 = 18k  $R_{40} = 22k$  $R_{27} = 33k$ R6;R39 = 47k R2;R5;R26;R28;R31;R36;R42;R43;  $R_{47} = 100k$  $R_{38} = 390k$ R46;R48 = 680k R11;R32;R34;R41 = 1M0  $R_{16} = 2M7$

### Capacitors:

$\begin{array}{l} C_{22} = 22p\\ C_1 = 82p\\ C_{23}; C_{24} = 1n0\\ C_{14}; C_{15}; C_{19} = 10n\\ C_{3}; C_{4}; C_{17}; C_{18}; C_{20}; C_{21} = 47n\\ C_{7}; C_{8}; C_{9}; C_{13} = 100n\\ C_{10} = 0.47\mu; \ 16 \ V\\ C_{2} = 4.7\mu; \ 63 \ V\\ C_{5}; C_{6}; C_{11}; C_{12}; C_{16} = 10\mu; \ 16 \ V \end{array}$

### Semiconductors:

$\begin{array}{l} \text{IC3;IC5} = \text{LM324} \\ \text{IC1} = \text{HKA5003M} \\ \text{IC4} = 7805 \\ \text{IC2} = 41256 \\ \text{T3;T4;T5} = \text{BC547B} \\ \text{T1;T2} = \text{BC558} \\ \text{T6} = 2\text{N3019} \\ \text{D8} - \text{D11} = 1\text{N4002} \\ \text{D2;D6;D7} = 1\text{N4148} \\ \text{D3} = ZPD6V8 \\ \text{D1;D4;D5} = \text{LED; 3 mm; red} \end{array}$

### Miscellaneous:

Ta1 – Ta4 = PCB-mount push-button.Qty 1:Condenser microphone.Qty 1:PP3 battery clip.QTY 1:3.5 mm dia. supply socket.Qty 6:solder pin.10 cm light-duty wire.20 cm 2-way flexible cable.

ducts, so that the 9 V battery takes over the supply. Although the input voltage of the regulator drops to about 8 V, the circuit remains on because T<sub>2</sub> conducts. LED D4 lights at reduced intensity to indicate that the unit is powered by the battery.

When the battery voltage drops below 8 V, the voltage difference between the input and the output of IC4 also drops to a level at which T2 is turned off. Consequently, T3 is turned off, and the circuit is no longer powered. The power indication LED goes out.

The battery is charged again as soon as the mains voltage is restored, but the telephone answering unit remains off until

**ELEKTOR ELECTRONICS JANUARY 1990**

20

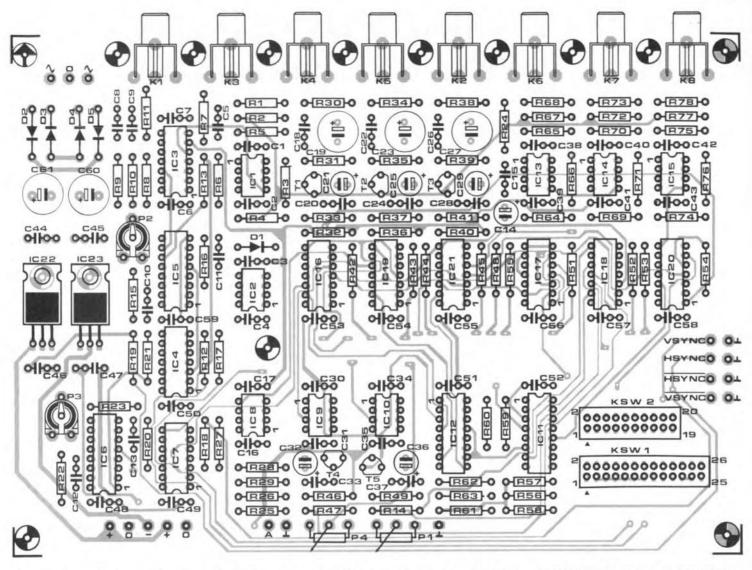

Fig. 2. Top views and component mounting plans of the keyboard PCB and the main PCB.

21

Ta<sub>3</sub> (ON) is actuated. In most cases, a new message must be recorded only if the answering unit has completely run out of battery power at some time. Fortunately, this should not be required too often since the capacity of the 9 V battery supplied with the kit is such that most power cuts can be coped with.

## Length of the message

It will be clear that the time available for the message is inversely related to the rate at which it is recorded and reproduced. The output frequency of the clock oscillator on board IC1 may be changed to individual requirements to achieve a message duration other than 15 seconds as determined by parts R1 and C1. The resistor may be changed within a range of 3.3 k $\Omega$ to 15 k $\Omega$ , with the lower value resulting in improved speech quality at a short message duration.

## Construction

The printed-circuit boards for the telephone answering unit are shown in Fig. 2. Start the construction by fitting the 17 wire links and all the passive parts. Next, fit the semiconductors. The size and dimensions of the boards are geared to the ABS enclosure supplied with the kit.

On their completion, the boards are carefully examined with reference to the parts list and the component overlay. Next, position the keyboard PCB vertically against the front edge of the main PCB. The lower edge of the keyboard PCB must protrude at about 1.5 mm below the track side of the main PCB. Align facing solder tracks and join each pair which a little solder, taking good care not to cause short-circuits.

Fit the 3.5 mm power supply socket into a hole in the rear panel and connect the two light-duty supply wires to the relevant terminals on the PCB. The connection to the telephone line is made direct via a short length of 2-way flexible cable.

The telephone answering unit requires no alignment, and is ready for use as soon as the PCBs and the batteries have been fitted into the case.

A complete kit of parts for the telephone answering unit is available from the designers' exclusive worldwide distributors (regrettably not in the USA and Canada):

ELV France B.P. 40 F-57480 Sierck-les-Bains FRANCE Telephone: +33 82837213 Fax: +33 82838180

Fig. 2. Top views and component mounting plans of the keyboard PCB and the main PCB.

It will be clear that the time available for the message is inversely related to the rate at which it is recorded and reproduced. The output frequency of the clock oscillator on board IC1 may be changed to individual requirements to achieve a message duration other than 15 seconds as determined by parts R1 and C1. The resistor may be changed within a range of 3.3 k $\Omega$ to 15 k $\Omega$ , with the lower value resulting in improved speech quality at a short message duration.

## Construction

can be coped with.

Length of the message

The printed-circuit boards for the telephone answering unit are shown in Fig. 2. Start the construction by fitting the 17 wire links and all the passive parts. Next, fit the semiconductors. The size and dimensions of the boards are geared to the ABS enclosure supplied with the kit.

On their completion, the boards are carefully examined with reference to the parts list and the component overlay. Next, position the keyboard PCB vertically against the front edge of the main PCB. The lower edge of the keyboard PCB must protrude at about 1.5 mm below the track side of the main PCB. Align facing solder tracks and join each pair which a little solder, taking good care not to cause short-circuits.

Fit the 3.5 mm power supply socket into a hole in the rear panel and connect the two light-duty supply wires to the relevant terminals on the PCB. The connection to the telephone line is made direct via a short length of 2-way flexible cable.

The telephone answering unit requires no alignment, and is ready for use as soon as the PCBs and the batteries have been fitted into the case.

A complete kit of parts for the telephone answering unit is available from the designers' exclusive worldwide distributors (regrettably not in the USA and Canada):

**ELV France** B.P. 40 F-57480 Sierck-les-Bains FRANCE Telephone: +33 82837213 Fax: +33 82838180

message must be recorded only if the answering unit has completely run out of battery power at some time. Fortunately, this should not be required too often since the capacity of the 9 V battery supplied with the kit is such that most power cuts

Ta3 (ON) is actuated. In most cases, a new

## SIMPLE AC MILLIVOLTMETER

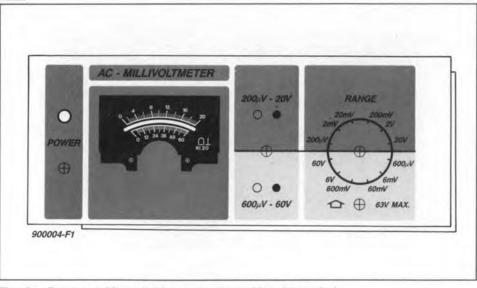

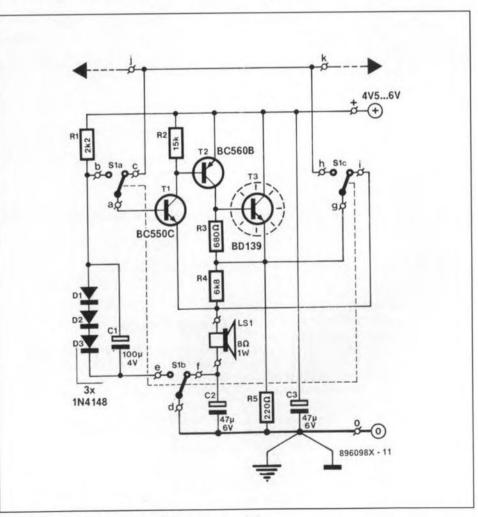

The third instrument in our series on budget test equipment is a wideband millivoltmeter with no fewer than twelve ranges, quite reasonable accuracy, a sensitivity of 200  $\mu$ V and a frequency range from 20 Hz to over 2 MHz.

A sensitive AC millivoltmeter is a useful instrument even if an oscilloscope is already available in your electronics workshop. This is mainly because signal levels are easier read from a meter scale than from an oscilloscope screen, which requires counting graticule divisions, multiplication by the set sensitivity, and conversion from the peak-to-peak value to the rms (root-mean-square) value. The AC millivoltmeter is also smaller and more sensitive than the average oscilloscope, and in addition may be powered by batteries. Compared to the digital multimeter, the AC millivoltmeter offers a much greater bandwidth. Although hard to beat for DC measurements, most DMMs have a frequency range of just 400 Hz which makes them really unsuitable even for signal tracing and frequency response measurements in AF amplifiers. By contrast, the AC millivoltmeter has a bandwidth of 20 Hz to 2 MHz.

The test instrument described here has no fewer than 12 measurement ranges from 0.2 mV to 60 V, and a high input impedance of 1 M $\Omega$ . The highest range, 60 V, allows output voltages of powerful AF amplifiers to be measured, while the most sensitive range, 0.2 mV, is suitable for direct signal level measurements on microphones and pick-up cartridges.

The choice of the enclosure and the design of the front-panel of the AC millivoltmeter are in line with the two earlier described instruments.

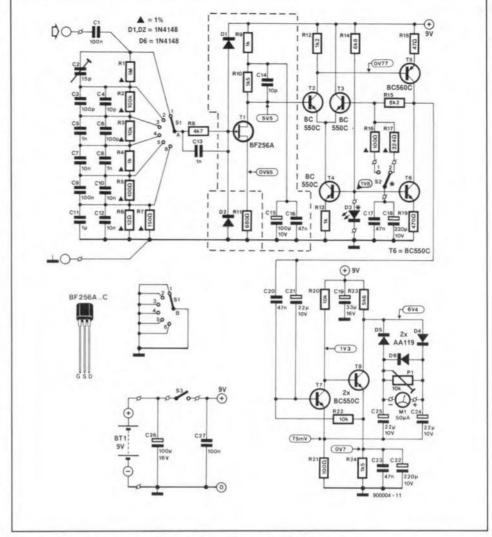

## **Circuit description**

Since the instrument measures AC voltage only, off-set and drift are not normally

### T. Giffard

problems in the amplifier stages. This means that integrated differential amplifiers in the form of operational amplifiers are not needed, and may be replaced by a circuit based on discrete transistors. The final version of this circuit was found to offer good stability at a reasonable bandwidth by virtue of the accurately compen-

### SIMPLE AC MILLIVOLTMETER

### AV measurement ranges:

0.2 mV; 2 mV; 20 mV; 200 mV; 2 V; 20 V 0.6 mV; 6 mV; 60 mV; 600 mV; 6 V; 60 V

### Accuracy:

- approx. 5% at 2 MHz with selected compensation capacitors in input attenuator; approx 3% at 100 kHz (depending on meter error).

- approx. 2% at 15 kHz; 10% above 15 kHz with non-selected standard MKT capacitors in input attenuator.

### Bandwidth (0.5 dB): 17 Hz to 2 MHz

17 HZ 10 2 MHZ

### Input impedance: 1 MΩ//10 pF

1 Mischio be

minimum:

| Battery vol | tage: |  |

|-------------|-------|--|

| nominal:    |       |  |

| maximum.    |       |  |

9 VDC

10 VDC

7.5 VDC

| Cu | rre | nt | con | sum | otio | 1: |

|----|-----|----|-----|-----|------|----|

7.5 mA typ. at 9 V.

sated voltage divider at the input, and a PCB design that prevents problems with wiring capacitance by accommodating the range switch on the printed-circuit board.

### Voltage divider

The circuit diagram in Fig. 1 shows frequency compensation capacitors fitted in parallel with every resistor in the input attenuator around rotary switch S1. These capacitors linearize the frequency response above 500 kHz. Ceramic capacitors are connected in parallel with larger MKT (metallized multi-layer theraphtelate) types as a fine correction to the compensation at relatively high frequencies. If possible, the ceramic capacitors are selected to give a time constant of 11 µs for each of the *R*-*C* combinations in the voltage divider.

### Input amplifier

Depending on the position of S2 in the measurement amplifier, the AC voltage at the gate of FET T1 that results in full-scale deflection of the meter is either 0.2 mV or 0.6 mV. The gate of the FET forms a very high impedance so that the voltage divider is hardly loaded. Components D1-D2 and R8 protect the gate against overvoltage. Diodes D1 and D2 conduct at gate voltages of about +9.6 V and -0.6 V respectively and afford protection to about 50 V in the 0.2 mV range. Capacitor C13 prevents Rs and its associated stray capacitance (the FET, the diodes and the relevant PCB tracks) forming a low-pass filter that would limit the bandwidth of the millivoltmeter. It should be noted, however, that the reactance of C13 drops with increasing frequency, which reduces the

ELEKTOR ELECTRONICS JANUARY 1990

protective effect of the diodes at frequencies above 40 kHz or so. The values of Rs and C13 are, therefore, a compromise between bandwidth and protection over a reasonable frequency range.

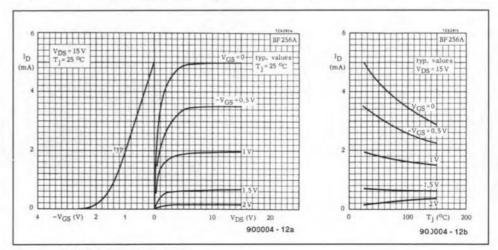

FET T1 is not included in the feedback circuit of the measurement amplifier that follows it. It has its own feedback resistor, R11, to give an amplification of about 1.5 times. R9 functions as a drain resistor for direct voltage only. For alternating voltages, it is decoupled by C15 and C16. These parts decouple the supply voltage and so help to stabilize the sensitive input stage. The DC setting of the FET is determined by the source resistor: since the gate is effectively grounded by the resistor ladder network, the voltage drop across the source resistor creates a negative gate voltage (UGs), which determines the current through the drain- and the source resistors. The resultant bias setting can be deduced from the curves in Fig. 2. For a drain voltage of about +5.5 V,  $R_{11} = 680\Omega$ to set a drain current of about 1.5 mA at  $U_{\rm CS} = 1$  V. It should be noted, however, that FETs in the same *I*DSS-*U*<sub>P</sub> group (here, the A-type of the BF256 is used) are subject to a certain production tolerance. Fortunately, this is of little consequence in this case because of the low drive level (below 1 mV).

### Measurement amplifier

This consists of a differential amplifier, T<sub>2</sub>-T<sub>3</sub>, followed by a class-A output amplifier. The emitter current of the differential amplifier is sunk by current source T<sub>4</sub>, which uses a LED, D<sub>3</sub>, to supply a reference voltage of 1.8 V. A normal red LED has a typical voltage drop of about 1.5 V and can not be used in this application. The LED required is either a high-efficiency or an amber type which drops typically 1.8 V.

With  $R_{13} = 1 k\Omega$ , T4 sinks a constant current of 1.2 mA. The output stage also uses a constant current source, T6. This current source forms a high AC resistance at the collector of T5. Compared to a single collector resistor, the current source allows a much higher gain to be achieved. The previously mentioned reference voltage source, D3, is also used for this second current source to give a constant current of about 2.5 mA (1.2 V/R<sub>19</sub>).

The input FET is DC-coupled to the measurement amplifier and thus determines the bias setting by means of its drain voltage of between 4 V and 5 V. The inverting input of the 'discrete opamp', T2–T6, is formed by the base of T3. This is DC-coupled to the output of the measurement amplifier by feedback resistor R15, so that the differential amplifier regulates the direct voltage at the output (collectors of T5-T6) to the value that exists at the non-inverting opamp input, the base of T2.

The overall gain for alternating voltages is either 83 times or 26 times as determined by switch S<sub>2</sub>, which selects feedback resistors R<sub>15</sub>-R<sub>16</sub> or R<sub>15</sub>-R<sub>17</sub> in series with a parallel combination of capacitors, C<sub>17</sub>-C<sub>18</sub>. This simple switch ar-ELEKTOR ELECTRONICS JANUARY 1990

Fig. 1. Circuit diagram of the wideband millivoltmeter.

rangement results in two sets of measurement ranges.

Fortunately, the transistors offer stable operation at relatively high frequencies, so that frequency compensation with a small ceramic capacitor is not needed in the AC feedback network. In practice, C14 alone does the job adequately.

### Active rectifier

The signal rectifier is capacitively coupled to the measurement amplifier by C20 and

C21. The active part consists of a two-stage amplifier around T7-T8, which uses the rectifier and the moving-coil meter as part of its feedback network to achieve linear operation. The result is a high sensitivity of about 21 mV at the input of the rectifier for full-scale deflection (f.s.d.) of the moving-coil meter. The double meter scale is virtually linear, as shown on the frontpanel layout in Fig. 3.

The high as well as stable amplification of the instrument results in a measure-

Fig. 2. BF256A FET design data.

Fig. 3. Front-panel lay-out (shown at approx. 60% of true size).

ment range of  $200 \ \mu V$  f.s.d., in which the lowest signal level that can be measured reliably is determined by the noise levels that exist in the discrete opamp and, of course, in the power supply. Consequently, the meter will not normally indicate '0' in the 200  $\mu V$  range. Capacitors C<sub>26</sub> and C<sub>27</sub> reduce the noise on the supply voltage lines and compensate the negative effect of the rising internal resistance of the battery as this is slowly discharged.

Preset P1 determines the form factor, i.e., it allows the meter indication to be reduced from the peak-to-peak value to the corresponding rms value. Note, however, that the set form factor is only valid for sine-wave voltages: the AC millivoltmeter does not contain a true-rms converter.

The signal rectifier consists of germanium diodes D<sub>4</sub>-D<sub>5</sub>. Silicon diode D<sub>6</sub> protects the coil in the meter against overloading.

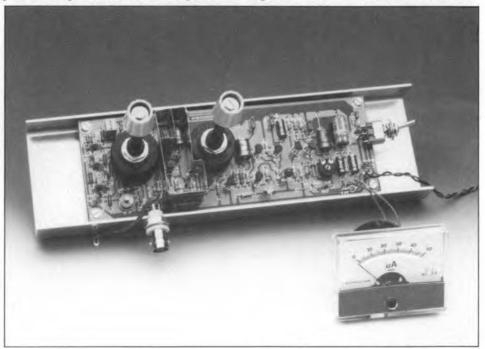

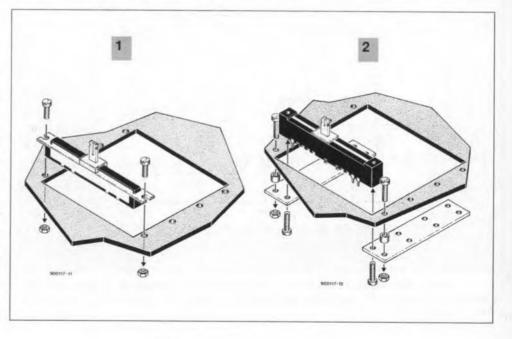

## Construction and alignment

As with the previous two instruments in this series, the construction depends entirely on the combination of the printedcircuit board (Fig. 4), the metal enclosure and the front-panel layout (Fig. 3). Together, these give a compact instrument that is simple to build because the wiring is kept to a minimum.

The two rotary switches are 6-way types with a special ring to set the number of positions. Set the ring to two positions on S<sub>2</sub>. The same ring may be omitted or set to six positions in the case of the range selector, S<sub>1</sub>. Select two suitable collet knobs for the switches and provide them with an additional pointer arrow opposite the one already printed on the plastic collar.

The population of the single-sided printed-circuit board should not present problems. Be sure to fit all components as close as possible to the board, i.e., keep all component terminals as short as possible. Check your work every now and then to prevent a long fault-finding session later. Fit solder pins at the locations shown between the rotary switches. Next, bend a 20-mm high piece of tin plate to form the screening as shown on the photographs of the prototype board.

Cut and drill a suitable aluminium support plate that can be bolted on to the side panels of the LC-850 enclosure. The completed PCB is fitted on to this support plate with the aid of four 10-mm high threaded PCB spacers.

Use the front-panel foil as a template to cut and drill the aluminium front panel of the enclosure. Fit the power LED, the on/off switch, the moving-coil meter and the BNC socket. Connect wires to the LED, the switch and the meter, and a short length of screened cable to the BNC socket.

Remove the rear panel of the enclosure, and insert the support plate with the PCB on it vertically between the side brackets of the enclosure. Move the assembly towards the front of the enclosure until the PCB is at about 50 mm from the front panel. This position allows enough room for the body of the moving-coil meter. Mark the holes in the side brackets to be used for securing the support panel. Cut the rotary switch spindles at the required distance from the front panel. Check if the two collet knobs fit, and remove them again.

The enclosure has ample room behind the vertically fitted support plate for a 9-V battery or a battery pack made up of six penlight types. Rechargeable batteries may also be used, in which case it is necessary to fit a charge socket on the rear panel of the enclosure. The AC millivoltmeter must never be powered by a mains adapter without an internal 9 V regulator.

## Setting up

The instrument is aligned before it is reassembled and fitted into the enclosure. Connect the meter, the on/off switch, the LED, the BNC socket and a 9-V battery. Fit the knobs provisionally on the switch spindles.

Switch on, and check that the current consumption is 7–8 mA. Use a digital multimeter to measure the voltage at the anode of D<sub>3</sub> (+1.8 V) and the positive terminal of C<sub>21</sub> (between +5 V and +6 V). The latter voltage must be virtually equal to that at the drain of T<sub>1</sub>. If this is not the case, replace the FET, or adapt R<sub>11</sub>. Check that the collector of T<sub>8</sub> is at about +6.4 V.

Set the instrument to the 60 V range and adjust the mechanical meter setting to an indication of 0. Connect a sine-wave generator to a digital multimeter set to alternating voltage measurement. Set the generator to a frequency between 100 Hz and 200 Hz. Connect a 1000:1 voltage divider between the input of the DMM and the input of the AC millivoltmeter. This voltage divider consists of a 10 k $\Omega$ and a 10  $\Omega$  resistor (both at 1% tolerance). Set the millivoltmeter to the 0.6 V range and the DMM to the 1 V or 3 V range. Adjust preset P<sub>1</sub> for corresponding readings on the DMM and the AC millivolt-

**ELEKTOR ELECTRONICS JANUARY 1990**

Fig. 4. Track layout and component mounting plan of the single-sided printed-circuit board for the millivoltmeter.

meter — i.e., disregard the multipliers 1 (V) and 0.001 (mV) — and check the adjustment for a couple of amplitude settings on the generator.

Check the indications on the millivoltmeter against those on the DMM. If the meter scale deviates considerably, try fitting another pair of diodes in positions D4 and D5 (Types BAT85 may be used if the stated germanium diodes are hard to obtain).

Since 1%-tolerance resistors are used in the input attenuator, the indications in the other ranges follow the results of the above alignment to within 1%.

Trimmer C<sub>2</sub> is adjusted for optimum compensation at an input frequency of 200 kHz. An oscilloscope and a sine-wave oscillator are required for this calibration to compare the indicated levels in the 200 mV ranges. If these instruments are not available, set C<sub>2</sub> to about two-thirds of its range to give a capacitance of 10–12 pF.

The prototype shown in the photographs has a 1-dB bandwidth of over 4 MHz, and an indication error smaller than 5% at 2 MHz.

Previously featured test equipment in this series:

RF inductance meter. *Elektor Electronics* October 1989.

LF/HF signal tracer. *Elektor Electronics* December 1989.

ELEKTOR ELECTRONICS JANUARY 1990

### Parts list

**Resistors:**  $R_1 = 1M0:1\%$ R2 = 100k; 1% R3 = 10k: 1%  $R_4 = 1k0; 1\%$  $R_5;R_{16} = 100\Omega; 1\%$ Re = 120; 1%  $R_7 = 150\Omega; 1\%$ Rs = 4k7R9;R13 = 1k0  $R_{10}$ ; $R_{24} = 1k5$  $R_{11} = 680\Omega$  $R_{12} = 1k2$  $R_{14} = 6k8$ R15 = 8k2 R17 = 342Ω; 1%  $R_{18} = 47\Omega$  $R_{19} = 470\Omega$ R20;R22 = 10k  $R_{21} = 100\Omega$  $R_{23} = 5k6$ P1 = 10k preset H

### Capacitors:

$C_{1};C_{27} = 100n \text{ ceramic}$   $C_{2} = 15p \text{ trimmer}$   $C_{3} = 100p \text{ polystyrene (styroflex)}$   $C_{4};C_{14} = 10p$   $C_{5} = 1n0$   $C_{7} = 10n$   $C_{6} = 100p$   $C_{8};C_{13} = 1n0 \text{ ceramic}$

### C9 = 100n

C10;C12 = 10n ceramic C11 = 1 $\mu$ 0 C15 = 100 $\mu$ ; 10 V C16;C17;C20;C23 = 47n ceramic C18;C22 = 220 $\mu$ ; 10 V C19 = 33 $\mu$ ; 16 V tantalum bead C21;C24;C25 = 22 $\mu$ ; 10 V C26 = 100 $\mu$ ; 16 V

### Semiconductors:

$\begin{array}{l} D_1; D_2; D_6 = 1N4148\\ D_3 = amber \ or \ high-intensity \ LED\\ (Ur = 1.8 \ V; \ see \ text)\\ D_4; D_5 = AA119\\ T_1 = BF256A\\ T_2; T_3; T_4; T_6; T_7; T_8 = BC550C\\ T_5 = BC560C \end{array}$

#### Miscellaneous:

S1;S2 = 2-pole 6-way rotary switch for PCB mounting. S3 = miniature SPDT switch. BT1 = 9-V battery with clip. M1 = 50 μA moving-coil meter e.g., Monacor Type PM2. Metal enclosure: H=80 mm; W=200 mm; D=180 mm. E.g., Telet LC-850 (C-I Electronics, P.O. Box 22089, 6360 AB Nuth, Holland). PCB Type 900004 (see Readers Services page). Front-panel foil 900004-F (see Readers Services page).

Fig. 4. Track layout and component mounting plan of the single-sided printed-circuit board for the millivoltmeter.

Parts list

meter — i.e., disregard the multipliers 1 (V) and 0.001 (mV) — and check the adjustment for a couple of amplitude settings on the generator.

Check the indications on the millivoltmeter against those on the DMM. If the meter scale deviates considerably, try fitting another pair of diodes in positions D4 and D5 (Types BAT85 may be used if the stated germanium diodes are hard to obtain).

Since 1%-tolerance resistors are used in the input attenuator, the indications in the other ranges follow the results of the above alignment to within 1%.

Trimmer C<sub>2</sub> is adjusted for optimum compensation at an input frequency of 200 kHz. An oscilloscope and a sine-wave oscillator are required for this calibration to compare the indicated levels in the 200 mV ranges. If these instruments are not available, set C<sub>2</sub> to about two-thirds of its range to give a capacitance of 10–12 pF.

The prototype shown in the photographs has a 1-dB bandwidth of over 4 MHz, and an indication error smaller than 5% at 2 MHz.

Previously featured test equipment in this series:

RF inductance meter. *Elektor Electronics* October 1989.

LF/HF signal tracer. *Elektor Electronics* December 1989.

**ELEKTOR ELECTRONICS JANUARY 1990**

**Resistors:** R1 = 1M0; 1% R2 = 100k; 1% R3 = 10k; 1% R4 = 1k0; 1% R5;R16 = 100Ω; 1%  $R_6 = 12\Omega; 1\%$ R7 = 150Ω; 1% Rs = 4k7R9;R13 = 1k0  $R_{10};R_{24} = 1k5$  $R_{11} = 680\Omega$  $R_{12} = 1k2$  $R_{14} = 6k8$ R15 = 8k2 R17 = 342Ω; 1%  $R_{18} = 47\Omega$  $R_{19} = 470\Omega$ R20;R22 = 10k  $R_{21} = 100\Omega$ R23 = 5k6 Pi = 10k preset H Capacitors:

$G_1;C_27 = 100n \text{ ceramic}$   $G_2 = 15p \text{ trimmer}$   $G_3 = 100p \text{ polystyrene (styroflex)}$   $G_4;C_{14} = 10p$   $G_5 = 1n0$   $G_7 = 10n$   $G_6 = 100p$   $G_8;C_{13} = 1n0 \text{ ceramic}$

$\begin{array}{l} C_9 = 100n \\ C_{10}; C_{12} = 10n \ ceramic \\ C_{11} = 1\mu 0 \\ C_{15} = 100\mu; \ 10 \ V \\ C_{16}; C_{17}; C_{20}; C_{23} = 47n \ ceramic \\ C_{18}; C_{22} = 220\mu; \ 10 \ V \\ C_{19} = 33\mu; \ 16 \ V \ tantalum \ bead \\ C_{21}; C_{24}; C_{25} = 22\mu; \ 10 \ V \\ C_{26} = 100\mu; \ 16 \ V \end{array}$

$\begin{array}{l} \textbf{Semiconductors:} \\ D_1;D_2;D_6 = 1N4148 \\ D_3 = amber or high-intensity LED \\ (Ur = 1.8 V; see text) \\ D_4;D_5 = AA119 \\ T_1 = BF256A \\ T_2;T_3;T_4;T_6;T_7;T_8 = BC550C \end{array}$

T2:T3:T4:T6:T7:T8 = BC550C T5 = BC560C Miscellaneous:

S1;S2 = 2-pole 6-way rotary switch for PCB mounting. S3 = miniature SPDT switch. BT1 = 9-V battery with clip. M1 = 50 μA moving-coil meter e.g., Monacor Type PM2. Metal enclosure: H=80 mm; W=200 mm; D=180 mm. E.g., Telet LC-850 (C-I Electronics, P.O. Box 22089, 6360 AB Nuth, Holland). PCB Type 900004 (see Readers Services page). Front-panel foil 900004-F (see Readers Services page).

## **DC-AC** converter

### July/August 1989, p. 49-51

Only when used in conjunction with the external timebase circuit, the 4047 in the converter supplies an output signal with a duty factor other than 0.5. This causes the primary transformer winding to become saturated, and the dissipation in the power transistors to rise to uncontrollable levels. To prevent this happening, fit wire links 2–3 and 4–5 to keep the 4047 operating in the astable mode. Connect pin 2 of the timebase circuit (100 Hz signal) to pin 3 of the 4047 via a 10 k $\Omega$  resistor. Remove R<sub>1</sub> and C<sub>1</sub> from the main converter board.

Attention: none of the above changes applies to the free-running version of the power converter.

## CORRECTIONS

## Simple AC millivolt meter

### January 1990, p. 22-25

In the circuit diagram, Fig. 1, the voltage shown at the base of T<sub>5</sub> is measured with respect to the positive supply rail.

## Dark-room clock

### February 1990, p. 62-66

The value of R<sub>17</sub> (1 k $\Omega$ ) is best increased to 10 k $\Omega$  to prevent T<sub>6</sub> overloading the Q13 output of IC<sub>1</sub>, which may cause erroneous clocking of IC<sub>1</sub>.

In Fig. 4, pin 9 of IC1 should also be circled to indicate that a through-contact

wire must be fitted in the relevant PCB hole.

## Vocal eliminator

July/August 1989, supplement p. 5-6

Pins 5 (+input) and pin 6 (-input) of opamp A<sub>2</sub> must be transposed in the circuit diagram.

## Voice recorder from Texas Instruments

### June 1989, p. 43-45

The supply voltage pin numbers of IC<sub>2</sub>, IC<sub>3</sub> and IC<sub>4</sub> are given incorrectly in the circuit diagram in Fig 6.

Pins 18 of IC2 and IC3, and pin 4 of IC4, must be connected to ground. Pins 9 of IC2 and IC3, and pin 8 of IC4, must be connected to +5 V.

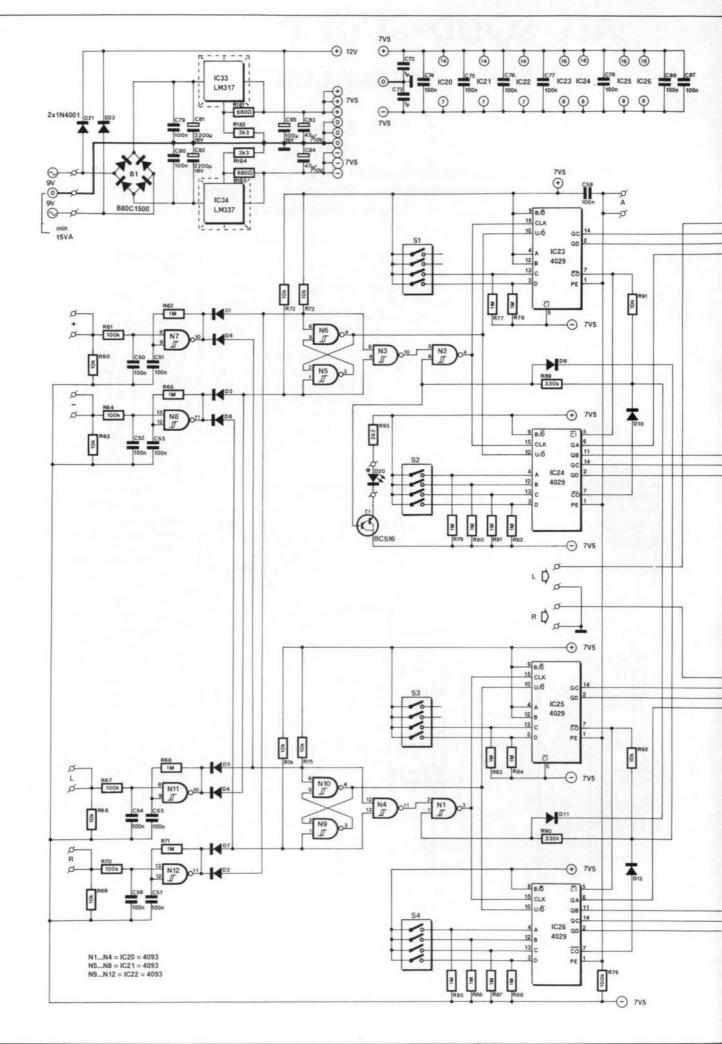

## ALL-SOLID-STATE PREAMPLIFIER 890170-14

## PART 2 – VOLUME CONTROL STAGES

by T. Giffard

## In this second and final part of the article we describe the volume and balance control stages, followed by the construction of the complete preamplifier.

Like the CMOS switches described in Part 1, the volume control switches are connected in an amplifier circuit in such a way that they have no potential drop across them. This results in very low distortion, so that the preamplifier can be used in topquality stereo installations.

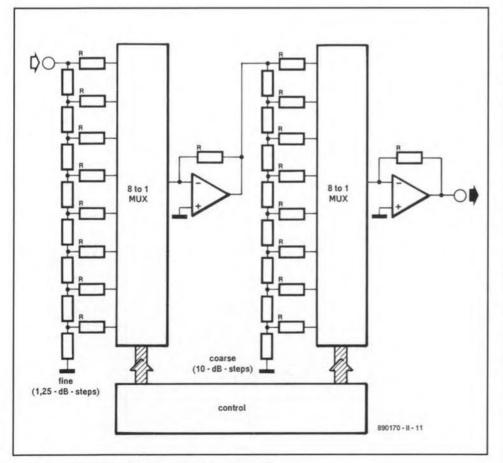

The basic principle of the volume control circuit is illustrated in Fig. 9. Since it is not easy to design an electronic switch with, say, fifty positions, two cascaded attenuation networks, each consisting of eight voltage dividers, are used.

Each network is switched in steps of 1.25 dB and the second (coarse) in steps of 10 dB. When the 'fine' attenuator reaches maximum attenuation ( $8 \times 1.25 = 10 \text{ dB}$ ). the 'coarse' one is switched by one step (= 10 dB). A total attenuation of 78.75 dB in  $8 \times 8 = 64$  steps is therefore provided. This number of steps could not be provided by a standard rotary switch.

Each attenuator section is resistively coupled to the input of an 8-to-1 multiplexer. The output of each multiplexer is applied to the inverting input of an opamp, so that there is no voltage drop across the multiplexers.

A control circuit ensures that the multiplexers are switched correctly and that the attenuators for the left- and right-hand channels can be used independently with the aid of balance switches.

A preset key makes it possible for the volume to be set to a predetermined position.

## Circuit description

In the circuit diagram of Fig. 10, the bufferred signals from the input circuits are fed to the 'fine' attenuator (R94 -R101 for

Fig. 9. Fundamental set-up of the volume control circuit.

## **Calculation of voltage dividers**

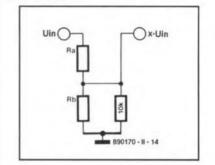

Each of the voltage dividers in the attenuators of Fig. 9 is basically configured as shown below.

Each voltage divider is formed by resistors Ra and Rb, the ratio of whose values depends on which branch of the divider they are located in. The 10 k $\Omega$  resistor is connected via the multiplexer to the inverting input of the opamp (virtual earth), so that, as far as the potential divider is concerned, it is connected to earth.

The voltage at the junction of the resistors is *xU*in, where *x* is the attenuation factor (no attenuation: x = 1; maximum attenuation: r = 0)

In the computation, the value of Ra + Rbis taken as 10 k $\Omega$ , which gives a value for x of:

$$x = \frac{R b // 10 k\Omega}{R b // 10 k\Omega + R a}$$

and for  $R_a$  of  $(10 \text{ k}\Omega - R_b)$ . Substituting these values and rearranging the formula for *x*, gives a value (in  $k\Omega$ ) for Rb of:

$$R b = \frac{10 - \frac{10}{x} + \sqrt{\left(\frac{10}{x} - 10\right)^2 + 400}}{2}$$

If it is desired to change the value of the steps, x must be replaced by  $10^{y/20}$ , where y is the desired attenuation in dB per step. Remember that from the result for each step the result of the previous step must be deducted. Resistance values so calculated must, where necessary, be rounded to the nearest standard value.

the left-hand channel and R110–R117 for the right-hand channel). Each branch of the attenuator is connected via a 10 k $\Omega$  resistor to the first multiplexer (IC27 and IC29 for the left-hand and right-hand channels respectively. The output of the 'fine' attenuators is applied to the 'coarse' attenuators, R102–R109 and R118–R125, via buffers A20 and A22 respectively. The output of the 'coarse' attenuators is applied to a second multiplexer, IC28 and IC30 respectively, each of which is followed by a buffer, A19 and A21.

29

Buffers A19 and A21 are configured rather differently from A20 and A22, in that they have an additional, complementary pair of transistors, T2-T3 and T5-T6.

The three diodes between the bases of these transistors ensure an adequate quiescent current.

The output impedance of these circuits is very low, so that long leads to the power amplifiers will not cause any problems.

The 22  $\Omega$  resistors, R174 and R179, provide short-circuit protection. The outputs may be connected direct to 600  $\Omega$  headphones.

The relay contacts at the outputs connect the outputs to earth to obviate audible clicks when the mains is switched on or off. It was not possible to replace the relay by an electronic device. Fortunately, the contacts are not in the signal path, so that the sound quality can never be affected by them.

The multiplexers are switched by Type 4029 preset up/down counters: IC23-IC24 for the left-hand channel and IC25-IC26 for the right-hand channel. DIP switches allow the volume to be preset to individual taste. Each time the preamplifier is switched on or when the reset key is pressed, the preset counter positions are assumed.

The carry-out pins of the counters are interconnected in a manner to ensure that the gates which provide the clock pulses, N2 for IC23-IC24 and N1 for IC25-IC26, are both blocked the moment one of the counters reaches nought or maximum. This arrangement ensures that the balance setting is maintained when the volume is adjusted to nought or maximum.

The plus and minus volume keys are connected to start/stop oscillators N7 and N8 respectively. A momentary depression of a key causes a single pulse at the output of the associated gate, while a sustained depression causes a pulse train. If the speed of this control is found to be too low, it may be increased by lowering the value of C51 and C53, and possibly also of C55 and C57.

The pulses associated with the +key are fed to N3 via D1 and to N4 via D6. The ensuing signals are taken to the clock inputs of the counters via

AUDIO & HI-FI

N2 and N1 respectively.

30

When the -key is pressed, the generated pulses are passed to the clock inputs of the counters via D3-N3-N2 and D8-N4-N1 respectively.

Two bistables, N5-N6 for the left-hand channel and N9-N10 for the right-hand channel, provide a signal that drives the up/down inputs of the counters. The level of this signal depends on which key is pressed.

The circuit of the balance control is virtually identical with that of the volume control. An exception is that the bistables are configured in a way that causes the left-hand counter to receive an 'up' signal when the right-hand counter gets a 'down' signal. Thus, if the left-hand balance key is pressed, the left-hand counter counts up and the right-hand counter counts down. Pressing the reset key returns the circuits to the position set by S1–S4. That position need not be the same for the two channels. This is useful where, for instance, there is a small difference in balance between the two speakers.

The power supply provides a separate voltage for energizing the output relay. Because of the (relatively) low value of C85, the relay is deenergized immediately the mains is switched off. On power-up, there is a delay provided by R180-C71-T4.

The remainder of the preamplifier is powered by the regulated, symmetrical voltage provided by IC33 and IC34.

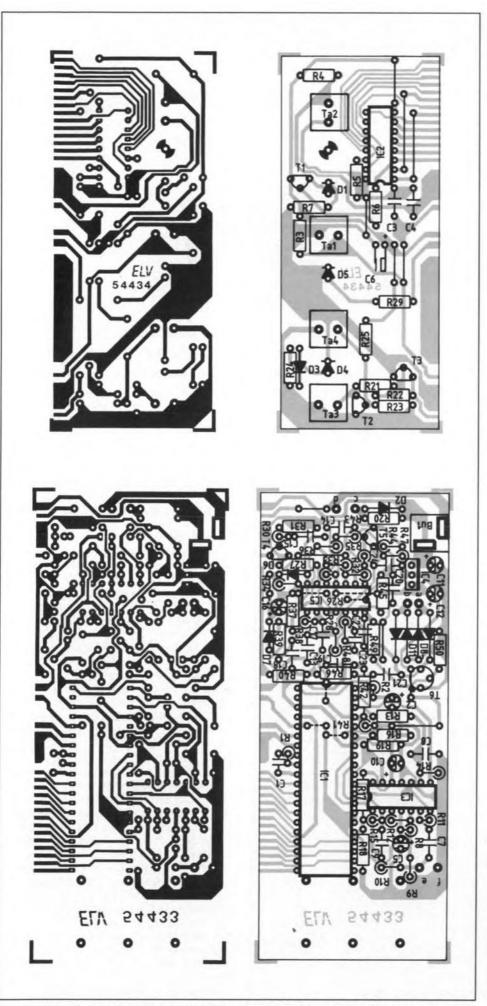

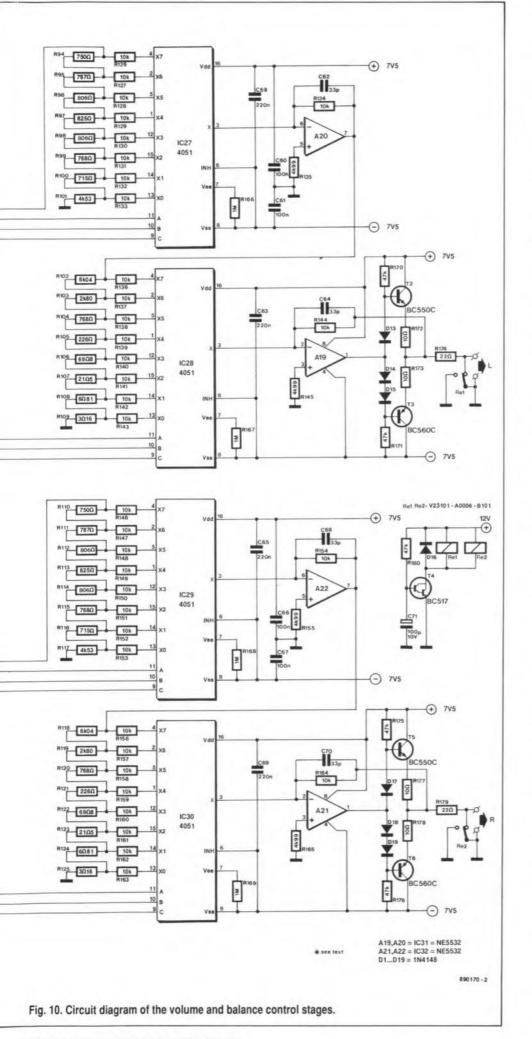

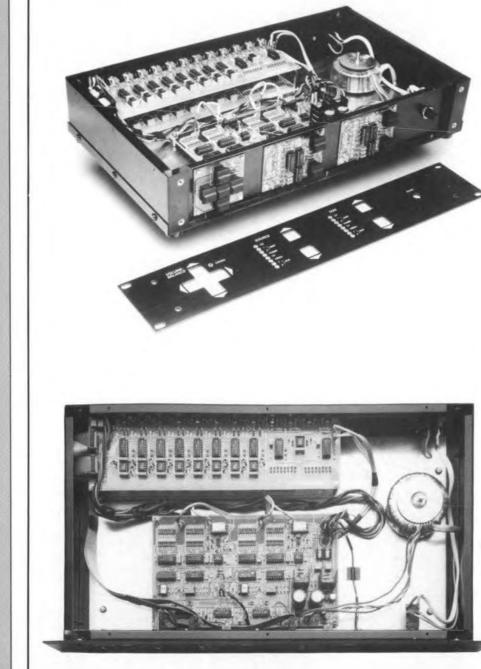

### Construction

Populating the PCB shown in Fig. 11 should not present any problems. All ICs and DIL switches may be mounted in sockets, but this is not obligatory.

The two electrolytic capacitors in the power supply are types that should be mounted upright. Each of the regulator ICs should be fitted on a heat sink.

It is convenient to provide all connexion points with a solder pin. Not, by the way, that for each control signal two solder pins may be fitted: this will facilitate the possible extension with remote control at a later date.

It is advisable to set all DIP switches to zero before the board is installed in the enclosure. The counters are then at nought at first power-up and that is a safe starting point.

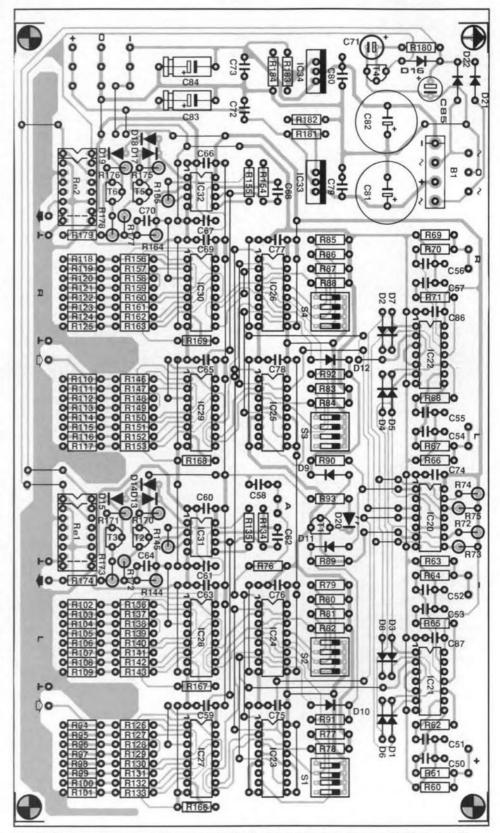

The preamplifier may be installed in a 19-inch, 2-unit (88 mm) high, enclosure. The enclosure used for the prototypes – see Fig. 12 – has a double front panel. Rectangular holes are cut in the back of this panel over which the control boards are screwed. If an enclosure with a single front panel is used, the three control boards may be fitted direct to the rear of the panel with the aid of small metal brackets.

The LED located on the board with the volume and balance controls should be bent sideways by a few millimetres so that it comes directly behind the relevant opening in the front panel.

Note that self-adhesive foils for the

front and rear panels of the enclosure are available through the Readers' service (see Fig. 13).

The boards for the input and system control stages dealt with in Part 1 should be fitted near the left-hand side of the rear panel.

The board for the volume and balance control stages should be fitted at the lefthand centre of the enclosure in such a way that the relays are located nearest the input boards. The mains transformer, the mains on-off switch and the mains cable entry should be fitted at the extreme right-hand rear of the enclosure, as far away as possible from the printed-circuit boards.

Note that the mains earth should be connected only to the appropriate terminal on the volume control board.

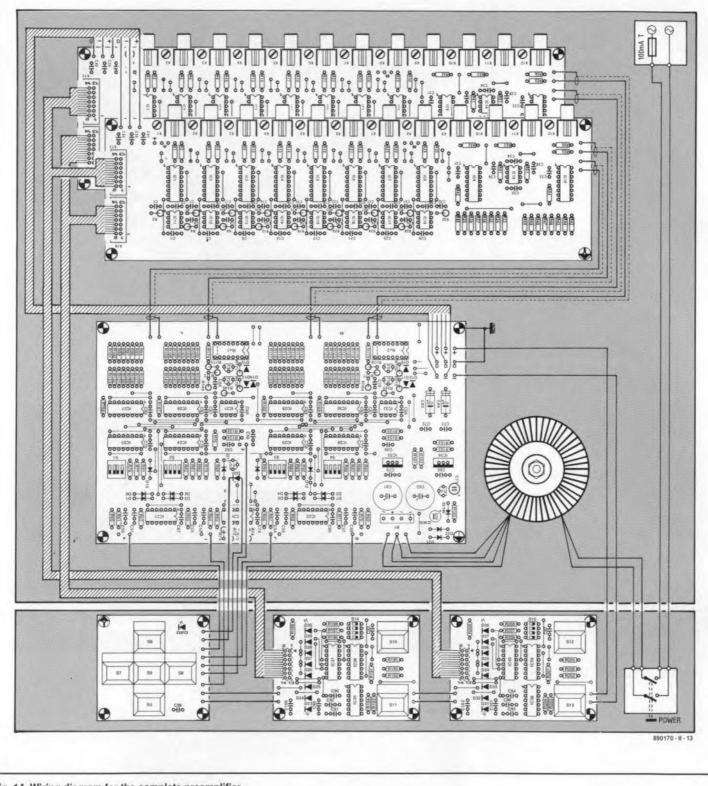

A wiring diagram for the complete preamplifier is shown in Fig. 14. For all analogue signals suitable screened cable should be used; all other connexions may be made in standard insulated circuit wire.

Fig. 11. Component mounting side of the printed-circuit board for the volume and balance control.

### Parts list

**Resistors:** R60;R63;R66;R69;R72 - R75;R91;R92 = 10k R61;R64;R67;R70;R76 = 100k R62; R65; R68; R71; R77 - R88; R166 - R169 = 1M0 R89;R90 = 330k  $R_{93} = 2k2$ R94;R110 =  $750\Omega$ ; 1% R95;R111 = 787Ω; 1% R96;R98;R112;R114 = 806Ω; 1% R97;R113 = 825Ω; 1% R99;R104;R115;R120 = 768Ω; 1% R100;R116 = 715Ω; 1% R101;R117 = 4k53; 1% R102;R118 = 6k04; 1% R103;R119 = 2k80; 1% R105;R121 = 226Ω; 1% R106; R122 = 69Ω8; 1% R107; R123 = 21 Ω5; 1% R108; R124 = 6Ω81; 1% R109;R125 = 3Ω16; 1% R126 - R134; R146 - R154; R156 - R164 = 10k; 1% R135;R145;R155;R165 = 4k99; 1% R170;R171;R175;R176;R180 = 47k R172;R173;R177;R178 = 10Ω; 0.6 W R174:R179 = 222: 0.6 W R181;R183 = 680Ω R182;R184 = 3k3

### Capacitors:

C50 - C58;C60;C61;C66;C67;C74 - C80;  $C_{86};C_{87} = 100n$ C59;C63;C65;C69 = 220n C62:C64:C68:C70 = 33p C71 = 100µ; 16 V; radial C72;C73 = 1µ0; MKT Ca1;Ca2 = 2200µ; 16 V; radial C83;C84 = 47µ: 10 V C85 = 100µ; 16 V; radial

### Semiconductors:

$D_1 - D_{19} = 1N4148$ D20 = LED; red; 3 mm D21;D22 = 1N4001 B1 = B80C1500  $T_1 = BC516$  $T_2;T_5 = BC550C$ T3;T6 = BC560C  $T_4 = BC517$  $IC_{20} - IC_{22} = 4093$  $IC_{23} - IC_{26} = 4029$  $IC_{27} - IC_{30} = 4051$ IC31;IC32 = NE5532 IC33 = LM317 IC34 = LM337

### Miscellaneous:

S1 - S4 = 4-way DIP switch block. Re1;Re2 = PCB-mount 12-V relay: e.g. Siemens V23101-A0006-B101. Qty 2: heatsink (for IC33 and IC34). Tr1 = toroidal transformer 2×9 V @15 VA: e.g. Type 03011 (240 V mains; Jaytee Electronic Services) or Type 01011 (220 V mains). Enclosure: 25 or 30 cm deep: e.g. ESM Type ER48/09. Fused chassis plug for mains cord: e.g. ElectroMail stock no. 481-639. Fuse: 100 mA slow. PCB Type 890170-2 (see Readers Services

page). Front and rear panel foils Types 890170-F1 and -F2 (see Readers Services page).

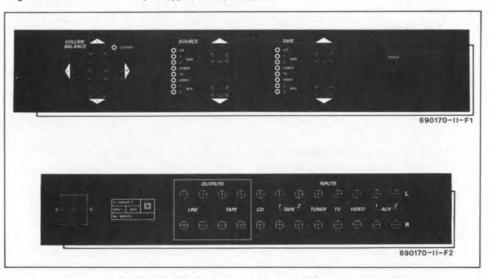

Fig. 12. General views of the prototype of the preamplifier

Fig. 13. Self-adhesive foils are available for the front and rear panels.

Fig. 14. Wiring diagram for the complete preamplifier.

Some ribbon cables were already described in Part 1 and these may now be shortened where necessary. If the connectors are dismantled carefully, they may be refitted to the (shortened) cable without any problems.

After all the boards are fitted and interconnected, a few simple checks can be carried out. Make sure that DIP switches S2 and S4 are OFF, otherwise there is the likelihood of a deafening sound from the loudspeakers when the preamplifier is connected into the audio system.

After the mains has been switched on, it should be possible to select all the inputs for tape-out and line-out. The volume and balance controls may also be tested: the LED should light when the minimum and maximum positions are reached. Briefly pressing the reset key should bring the volume back to the preset value.

Finally, you will have noticed that the preamplifier is DC-coupled throughout and normally this should not create any problems. However, if the input of your power amplifier has no capacitors, it may be advisable to connect a couple of good-quality capacitors (for instance, 4.7–10 µF metallized polypropylene or polystyrene types) in the line outputs.

## VIDEO MIXER

## PART 1: VIDEO SWITCHING BOARD

A. Rigby

Recent developments in consumer electronics have boosted the popularity of video recorders, portable cameras and camcorders to such an extent that the film camera has become a thing of the past. Video enthusiasts who want to edit and mix recorded material from various video sources, and in addition require special fade-in and fade-out effects, will delight in building and using the advanced mixing desk presented here.

Not so long ago, a small fortune would buy a bulky video recorder offering mono sound, a primitive programming facility and just acceptable picture quality if the tracking control was re-adjusted from time to time. Today's camcorders (camera-recorders) cost less than these old VCRs, but offer significantly improved sound and picture quality. Stereo sound, Super-VHS and all-digital recording techniques are already available but will take some time to become established in the consumer markets.

In spite of all its technological benefits, the camcorder has one disadvantage when compared to, say, an 8-mm film camera: editing recordings requires a mixer, of which there appear to be few around that can be purchased ready-made at a reasonable price.

The video mixer/effects unit described here allows a up to three video signals to be combined into one video output signal. The mixer also offers a number of special effects which result in attractive fade-in, fade-out and superimpose effects.

An important proviso must be mentioned at the outset: depending on the number of video sources connected to the mixer, at least one (two sources) or two (three sources) must have an external synchronization input. One video source always serves as the master sync source, the other (one or two) are externally synchronized.

The mixer always mixes two signals, even when three signals are applied. It does not allow three signals to be shown simultaneously. The mixing options are:

- video 1 with video 2

- video 1 with video 3

- video 2 with video 3

Again remember that video sources that lack an external synchronization input can not be mixed. The reason for this is probably familiar to those who have experience working with video signals, but may be less obvious to many other readers. Mixing video signals is essentially alternate switching between lines of two TV pictures. To maintain phase synchronism between the two pictures, their picture line content must start at the same instant. The synchronization pulses in the video signal serve to time this instant. The sync pulse frequencies of the two video sources will not be equal if the syncs are derived from free-running clock circuits

as used in most portable cameras. Hence, a single synchronization source is required to prevent the two pictures 'floating' with respect to one another in the mixed image.

87304-I

It would not be fair to say that the video mixer is a simple-to-build project. The final design is relatively complex, and construction is only recommended to readers who have experience in working with video signals, and who are confident of their soldering skills.

Lozenge-insertion: one of the many picture mixing effects.

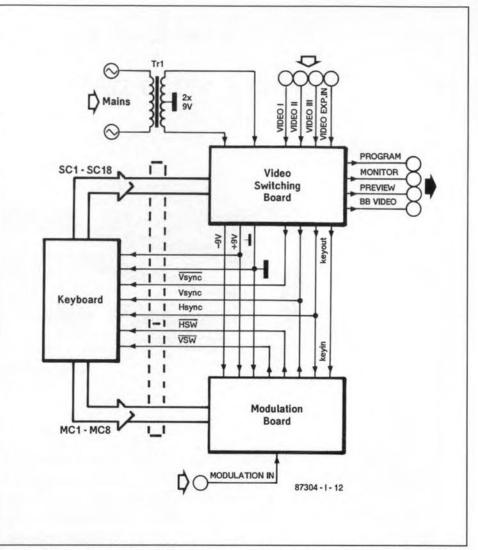

## Two block diagrams

34

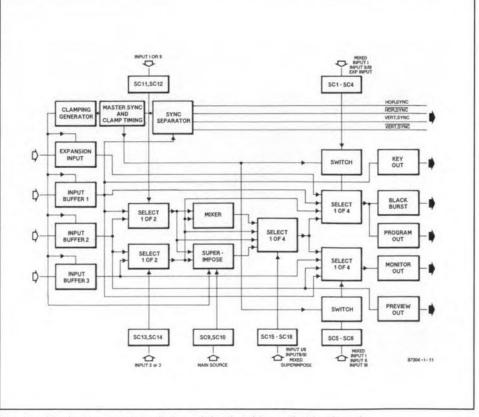

The basic operation of the video mixer is best understood by looking at the block diagram in Fig. 1. The three blocks shown in the drawing represent the three circuits that make up the video mixer. Each circuit is constructed on a separate printed-circuit board. This first instalment of a fourpart article deals with the video switching board. Part 2 discusses the modulation board, and Part 3 the keyboard. Part 4, finally, addresses matters related to the adjustment and practical use of the video mixer.

The block diagram shows four inputs, VIDEO I, VIDEO II, VIDEO III and VIDEO EXP. The first three accept the video signals that are to be mixed. Input VIDEO I takes the master signal that ensures the central synchronization. The video source connected to this input does not require an external synchronization input, and must always be present to provide the master sync signals for the other video source(s). The other two inputs, VIDEO II and VIDEO III, are identical, and take signals from sources synchronized with VIDEO I.

The fourth mixer input, VIDEO EXP (expansion input), takes an additional signal that may be routed to the monitor when none of the other inputs is being used. This 'stand-by' signal may be supplied by a test chart generator or logomat. It can not be mixed with the other channels.

The video mixer has four outputs. The BLACK-BURST (BB-video) output supplies the composite synchronization signal for the video sources. Outputs PROGRAM and MONITOR are electrically identical and supply the mixed video output signal. The PREVIEW output, finally, allows the video-1, video-2, video-3, or the mixed video signal to be viewed independently of the other outputs.

The video switching board divides the synchronization signal recovered from video-1 between the sub-circuits. The control signals for the modulation and the switching board emanate from the keyboard circuit (to be discussed in Part 3). The function of these control signals, marked SCxx, will be reverted to in due course.

Figure 2 shows the block diagram of the video switching board. The input buffers are at the left, the outputs at the right. Electronic switches at a number of locations select the required signals. The control blocks at the top of the diagram are used to generate the sync signals and enable the colour burst in the master signal to be inserted at the right instant into the output signal. In the mixer circuit, the horizontal and vertical sync signals are available separately in true as well as inverted form. The KEYOUT output allows a kind of picture-in-picture effect to be achieved: one particular colour is removed from the picture on one channel, to be filled in by corresponding areas in the picture on the other channel. This effect is often used in TV news broadcasts to create a background for (apparently large)

Fig. 2 Block diagram of the first module, the video switching board.

35

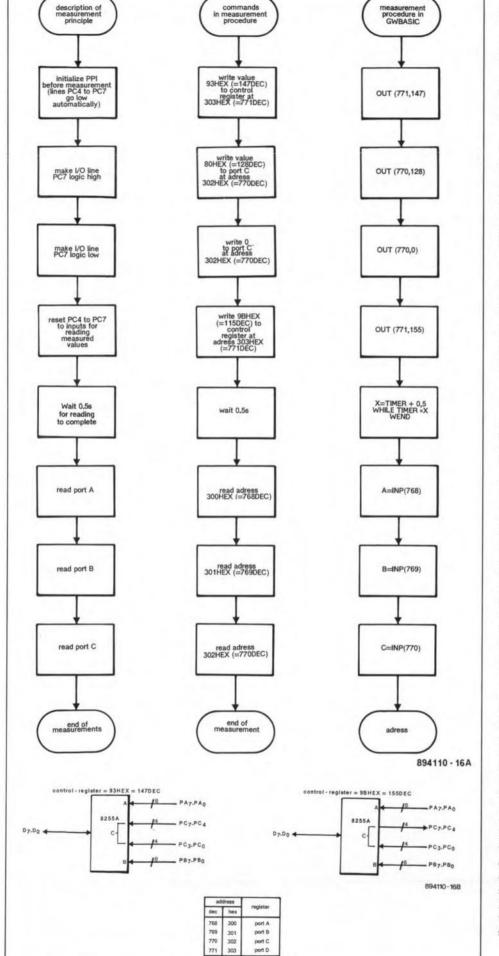

weather maps.

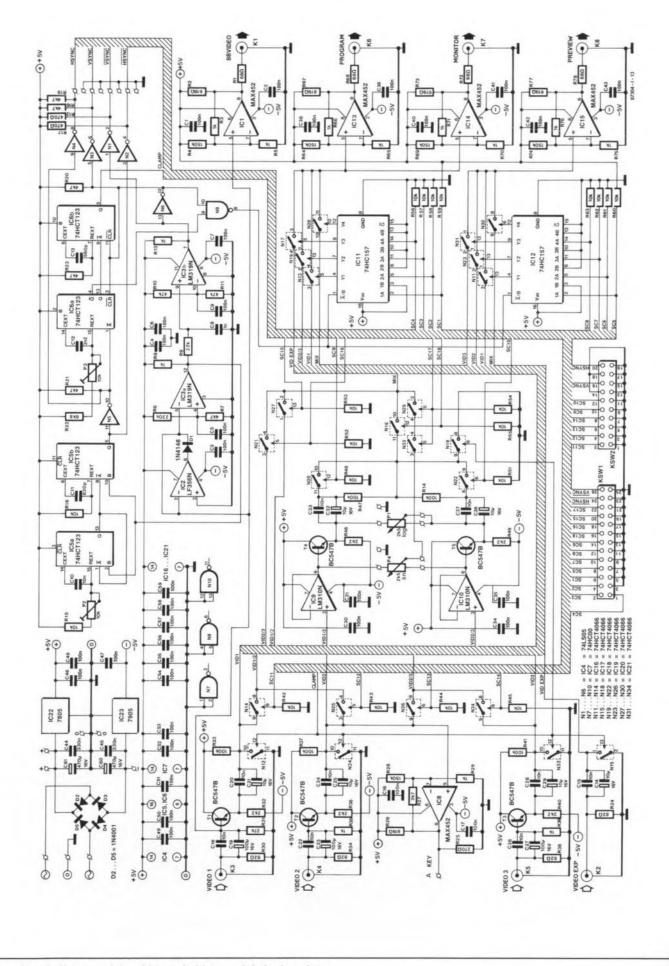

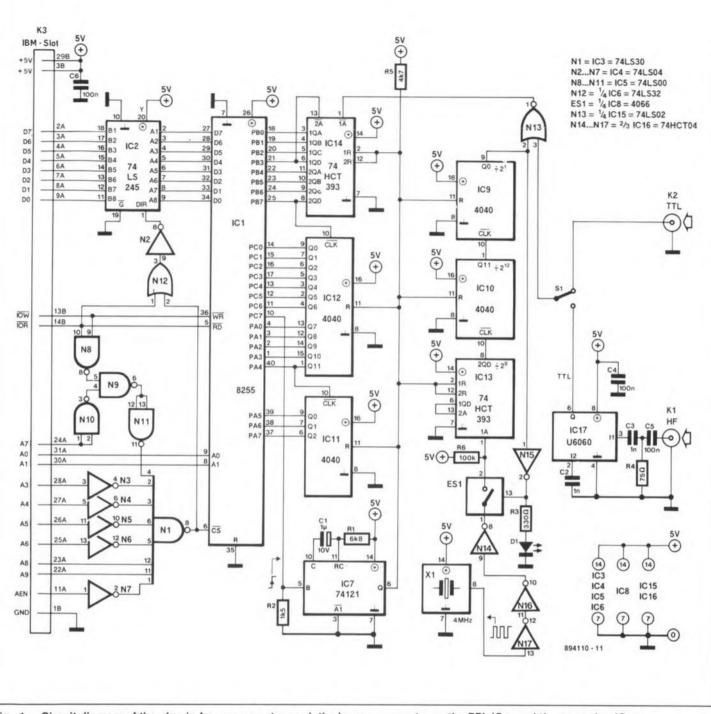

## Switching unit: the practical circuit

Although the circuit is fairly complex, the diagram in Fig. 3 gives a good insight into the operation of the video switching board.

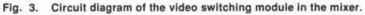

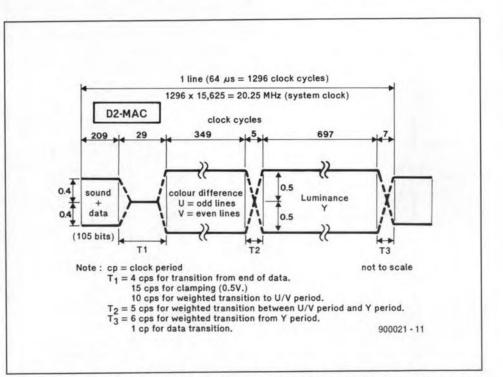

The video signal applied to the VIDEO I input, socket K3, serves to synchronize all other sources. Opamps IC2, IC3a and IC3b form a synchronization separator. Circuit IC2 clamps the input signal, while IC3a and the associated filter recover the line sync pulses. These trigger IC5a, a monostable multivibrator (MMV), whose output pulses have a fixed length of 60 µs. These pulses keep a second MMV, IC5b, from being started by interference during the picture line time, and ensure that a 4 µs horizontal sync pulse is generated by IC5b at the end of the line only. This gives a total time of 64 µs for the line content and the sync pulse, as shown in Fig. 4. The first picture information appears in the line 12 µs after the start of the line sync pulse. The third MMV, IC6a, ensures that the line sync pulse and the colour burst recovered from video 1 are applied to all other video signals. This is achieved by NAND gate N9 switching multiplexers IC11 and IC12 in a way that video-1 signals present during an 11 µs interval around the line sync pulse are passed to the output (by pre-selection on the  $\overline{A}/B$  input).

Circuit IC<sub>6b</sub> generates a clamp pulse of approximately 1 µs before the start of the picture line content. The clamp pulse serves to define the absolute black level as a direct-voltage reference in the video signal.

The analogue circuitry on the video switching board starts at the left of the circuit diagram with three input buffers around transistors  $T_1$ ,  $T_2$  and  $T_3$ . These ensure that the video sources are terminated into the correct impedance, and further ensure sufficient drive for use at various points in the circuit. The inputs asa well as the outputs of the buffers are in series with parallel combinations of a solid (MKM) and an electrolytic capacitor to ensure a low reactance over a wide frequency range, which ensures that both the vertical and the horizontal sync pulses are passed undistorted. Each buffer output can be short-circuited by an electronic switch to give the required reference black level. The electronic switches are controlled by the clamping pulse.

There is a fair number of electronic switches between the buffers and the output. These switches are controlled from the keyboard circuit and select the two video signals that are to be mixed. The selected signals are first buffered for the benefit of two mixing effects.

First, the opamps used allow the signals to be mixed by potentiometer P4. The mixed video signal at the wiper is passed through a series of electronic switches before it arrives at the output buffers, IC13, IC14 and IC15.

Second, the amplifier that follows the mixer stage is used for the superimpose effect. Although the circuit around potentiometer P1 looks similar to the mixer stage, it works altogether differently. Transistors T4 and T5 ensure sufficient buffering between the mixer and the superimpose stage, while potentiometer P1 forms an adjustable short-circuit between the two video signals, which are mixed in a way that ensures that their brightest picture areas are passed to the output. Effectively, a relatively dark area in one picture is covered by a brighter one at the same location in the other picture. Switches N20 and N22 determine the video channel selection if the superimpose function is not used (P1 set to maximum).

Circuits IC11 and IC12 have a number of functions related to the control of the video switching board. These functions will be reverted to in Part 2. For now, it is sufficient to say that control lines SC1 through SC8 are connected to switches that select the video signal that is to be fed to the output.

As will be seen in Part 2 of this article, the pattern generator on the modulation board controls lines SC15 through SC18 to enable two pictures to be mixed via an intermediate effect.

The circuit around opamp ICs raises the video signal at the VIDEO II input to a level suitable for driving the keying input on the modulation board.

The power supply is quite simple. Every board has its own regulator, which takes the unregulated supply voltage from the central power supply. The video switching board has two local regulators, IC22 and IC23 to provide the symmetrical, regulated supply voltages of +5 V and – 5 V.

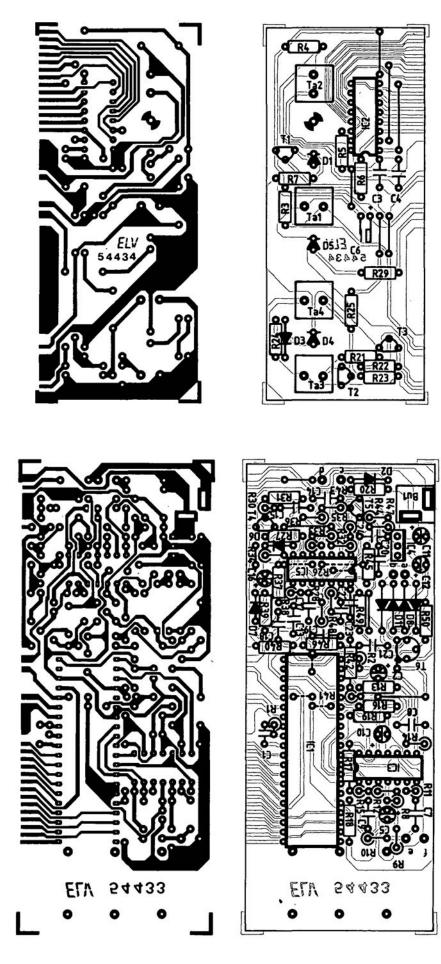

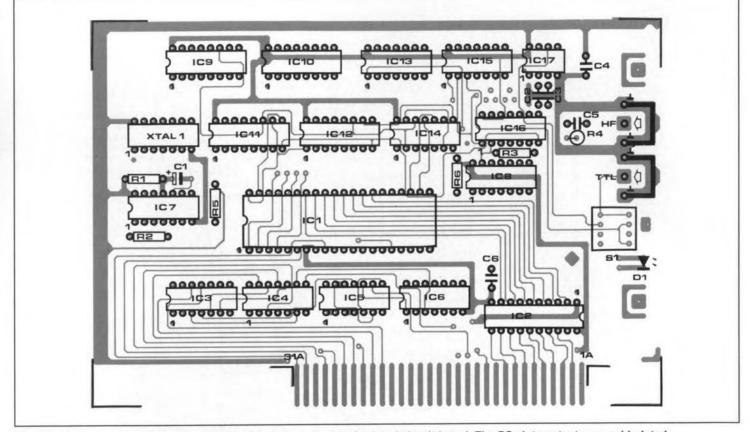

## Construction

The printed-circuit board for this part of the project is a relatively large, doublesided and through-plated type, which is available ready-made. The component overlay shows that the board is fairly densely populated.

Use PCB-mount phono sockets for the video inputs and outputs as indicated on the component mounting plan. The synchronization signals, the supply voltage and the potentiometers are connected via solder pins. PCB headers KSW1 and KSW2 mate with IDC sockets fitted on short flat-cables that connect the video switching board to the keyboard unit and the modulator board.

Start the construction with fitting all connectors, solder pins and phono sockets. Then follow the passive components. Ample decoupling is provided by inex-

Completed prototype of the video switching board.

37

Fig. 5. Component mounting plan of the video switching board. The input and output cables are connected to PCB-mount phono sockets.

Parts list

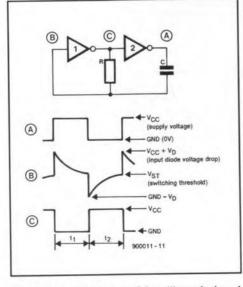

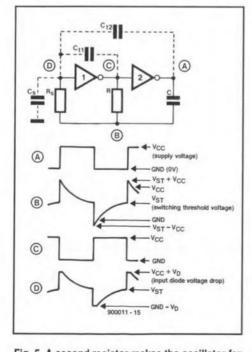

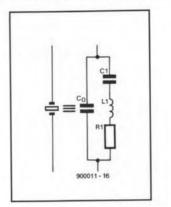

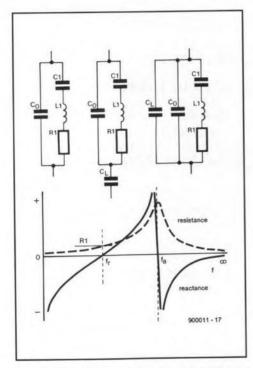

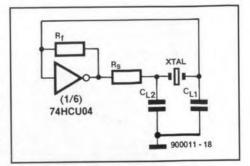

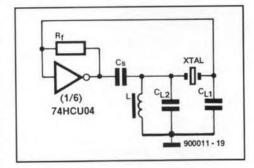

### **Resistors:**