# A Baker's Dozen Real Analog Solutions for Digital Designers

A Baker's Dozen

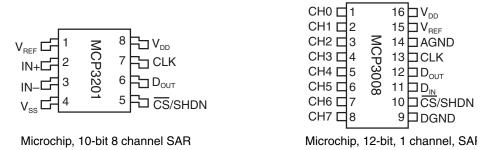

## A Baker's Dozen

Real Analog Solutions for Digital Designers

by Bonnie Baker

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2005, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

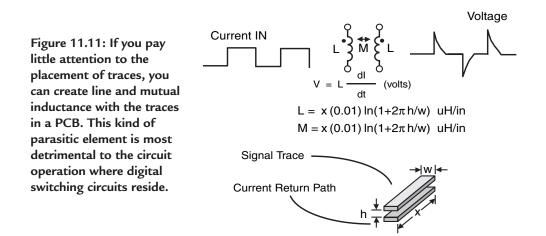

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

#### Library of Congress Cataloging-in-Publication Data

Baker, Bonnie.

A Baker's dozen : real-world analog solutions for digital designers / by Bonnie Baker. p. cm. ISBN 0-7506-7819-4

1. Digital integrated circuits--Design and construction. 2. Logic design. I. Title.

TK7874.B343 2005 621.3815--dc22

2005040558

*British Library Cataloguing-in-Publication Data* A catalogue record for this book is available from the British Library.

For information on all Newnes publications visit our Web site at www.books.elsevier.com

$05 \ 06 \ 07 \ 08 \ 09 \quad 10 \ 9 \ 8 \ 7 \ 6 \ 5 \ 4 \ 3 \ 2 \ 1$

Printed in the United States of America

## Contents

| Preface                                                                      | ix   |

|------------------------------------------------------------------------------|------|

| Acknowledgments                                                              | xi   |

| About the Author                                                             | xiii |

| Chapter 1: Bridging the Gap Between Analog and Digital                       |      |

| Try to Measure Temperature Digitally                                         | 6    |

| Road Blocks Abound                                                           | 8    |

| The Ultimate Key to Analog Success                                           | 14   |

| How Analog and Digital Design Differ                                         | 15   |

| Time and Its Inversion                                                       |      |

| Organizing Your Toolbox                                                      | 21   |

| Set Your Foundation and Move On, Out of the Box                              |      |

| Chapter 1 References                                                         | 23   |

| Chapter 2: The Basics Behind Analog-to-Digital Converters                    | 25   |

| The Key Specifications of Your ADC                                           |      |

| Successive Approximation Register (SAR) Converters                           |      |

| Sigma-Delta ( $\Sigma$ - $\Delta$ ) Converters                               |      |

| Conclusion                                                                   |      |

| Chapter 2 References                                                         | 60   |

| Chapter 3: The Right ADC for the Right Application                           | 63   |

| Classes of Input Signals                                                     |      |

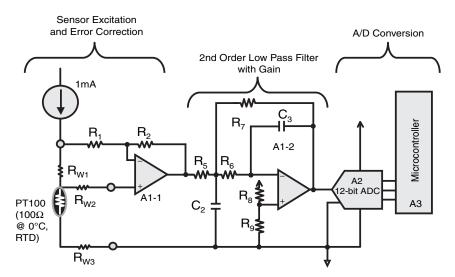

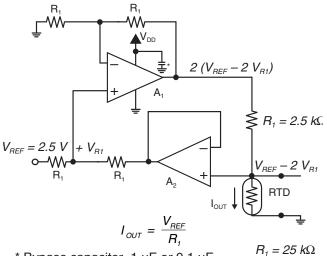

| Using an RTD for Temperature Sensing: SAR Converter or Sigma-Delta Solution? | 72   |

| RTD Signal Conditioning Path Using the Sigma-Delta ADC                       | 76   |

| Measuring Pressure: SAR Converter or Sigma-Delta Solution?                   | 77   |

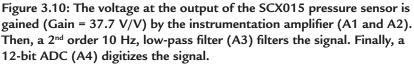

| The Pressure Sensor Signal Conditioning Path Using a SAR ADC                 |      |

| Pressure Sensor Signal Conditioning Path Using a Sigma-Delta ADC             |      |

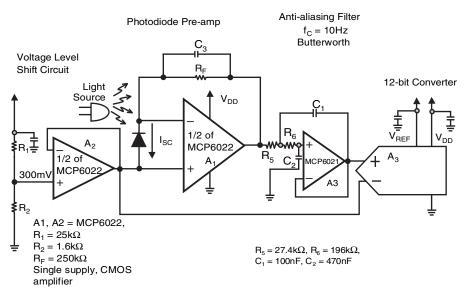

| Photodiode Applications                                                      |      |

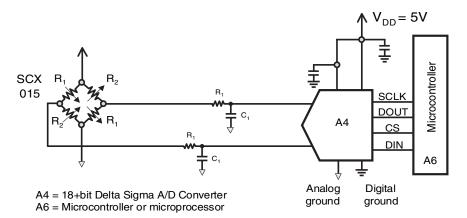

| Photosensing Signal Conditioning Path Using a SAR ADC                        |      |

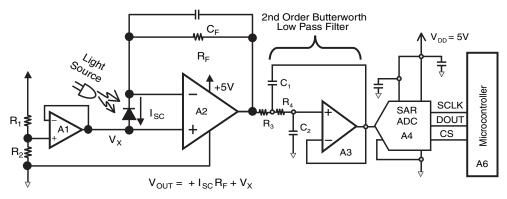

| Photosensing Signal Conditioning Path Using a Sigma-Delta ADC                |      |

| Motor Control Solutions                                                      |      |

#### Contents

| Conclusion                                                         |    |

|--------------------------------------------------------------------|----|

| Chapter 3 References                                               |    |

| Chapter 4: Do I Filter Now, Later or Never?                        | 91 |

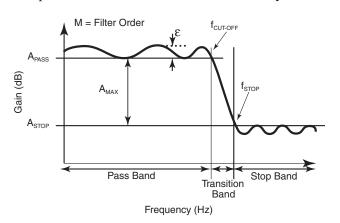

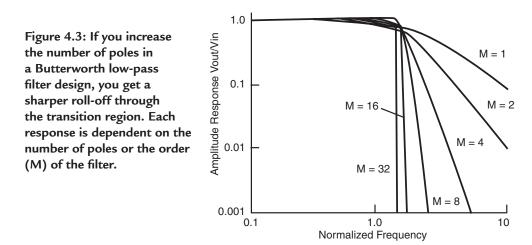

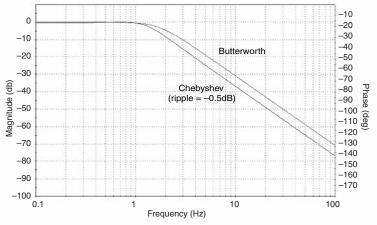

| Key Low-Pass Analog Filter Design Parameters                       |    |

| Anti-Aliasing Filter Theory                                        |    |

| Analog Filter Realization                                          |    |

| How to Pick Your Operational Amplifier                             |    |

| Anti-Aliasing Filters for Near DC Analog Signals                   |    |

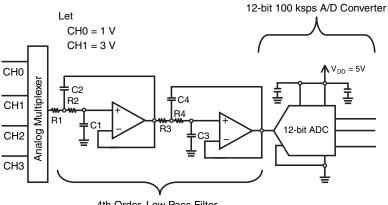

| Multiplexed Systems                                                |    |

| Continuous Analog Signals                                          |    |

| Matching the Anti-Aliasing Filter to the System                    |    |

| Chapter 4 References                                               |    |

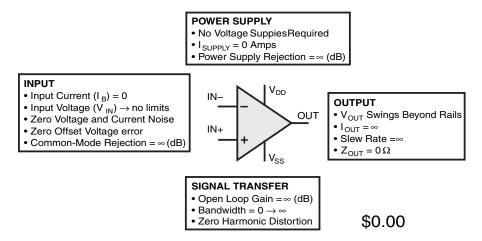

| Chapter 5: Finding the Perfect Op Amp for Your Perfect Circuit     |    |

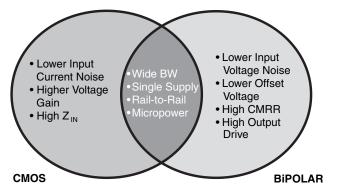

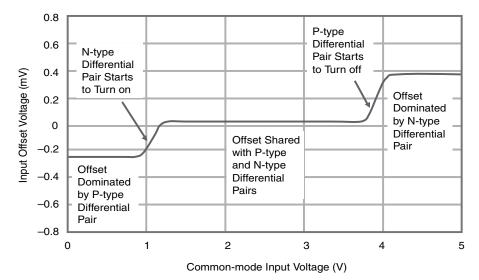

| Choose the Technology Wisely                                       |    |

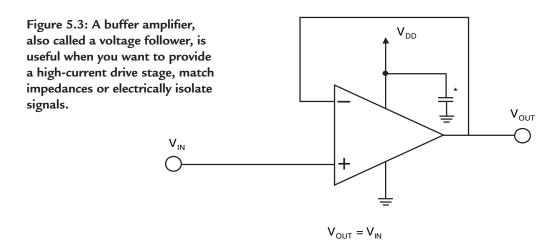

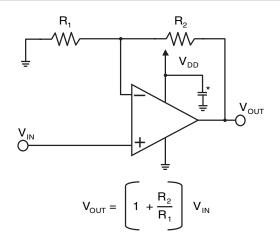

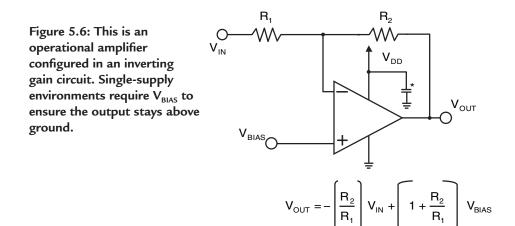

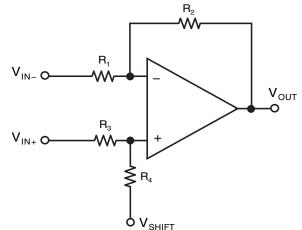

| Fundamental Operational Amplifier Circuits                         |    |

| Using these Fundamentals                                           |    |

| Amplifier Design Pitfalls                                          |    |

| Chapter 5 References                                               |    |

| Chapter 6: Putting the Amp Into a Linear System                    |    |

| The Basics of Amplifier DC Operation                               |    |

| Every Amplifier is Waiting to Oscillate, and Every Oscillator is   |    |

| Waiting to Amplify                                                 |    |

| Determining System Stability                                       |    |

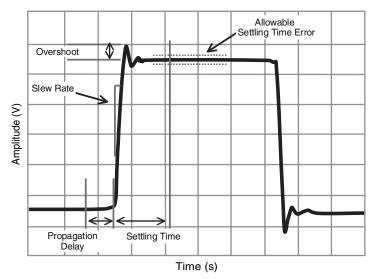

| Time Domain Performance                                            |    |

| Go Forth                                                           |    |

| Chapter 6 References                                               |    |

| Chapter 7: SPICE of Life                                           |    |

| The Old Pencil and Paper Design Process                            |    |

| Is Your Simulation Fundamentally Valid?                            |    |

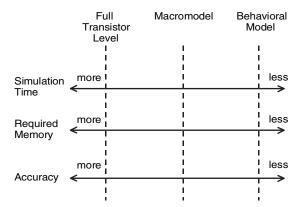

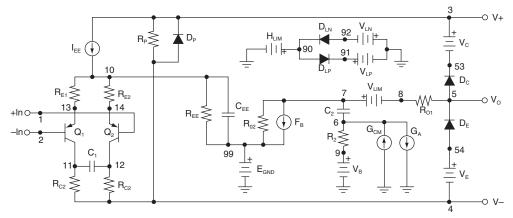

| Macromodels: What Can They Do?                                     |    |

| Concluding Remarks                                                 |    |

| Chapter 7 References                                               |    |

| Chapter 8: Working the Analog Problem From the Digital Domain .    |    |

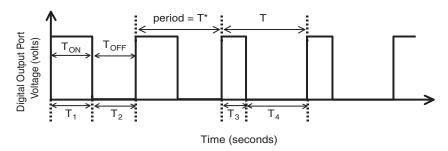

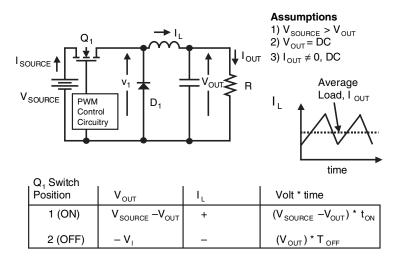

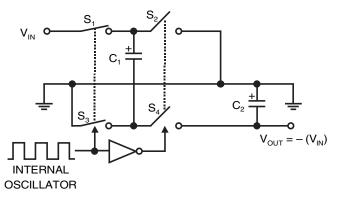

| Pulse Width Modulators (PWM) Used as a Digital-to-Analog Converter |    |

| Using the Comparator for Analog Conversions                        |    |

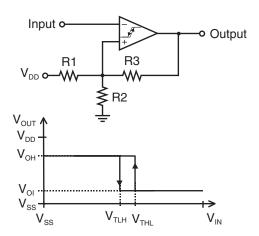

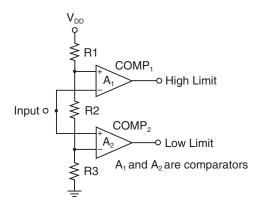

| Window Comparator                                                       | 196   |

|-------------------------------------------------------------------------|-------|

| Combining the Comparator with a Timer                                   | 197   |

| Using the Timer and Comparator to Build a Sigma-Delta A/D Converter     |       |

| Conclusion                                                              | 207   |

| Chapter 8 References                                                    | 208   |

| Chapter 9: Systems Where Analog and Digital Work Together               | 209   |

| Selecting the Right Battery Chemistry for Your Application              |       |

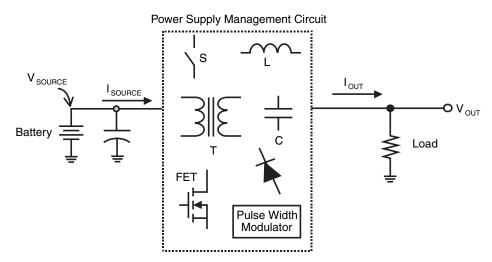

| Taking the Battery Voltage to a Useful System Voltage                   |       |

| Defining Power Supply Efficiency                                        |       |

| Comparing The Three Power Devices                                       |       |

| What is the Best Solution for Battery-Operated Systems?                 | 221   |

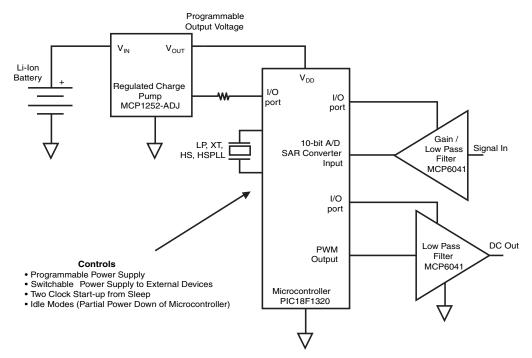

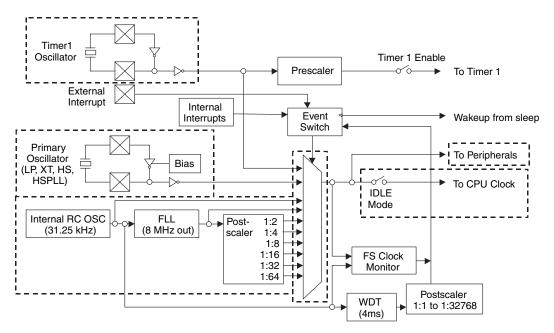

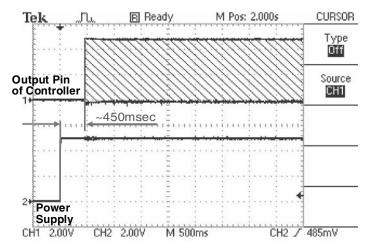

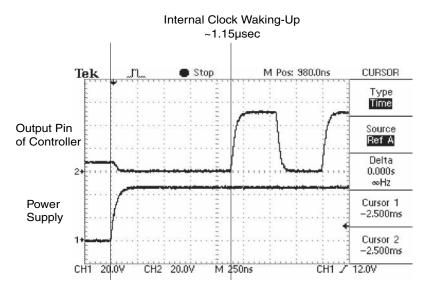

| Designing Low-Power Microcontroller Systems is a State of Mind          | 222   |

| Conclusion                                                              |       |

| Chapter 9 References                                                    | 229   |

| Chapter 10: Noise – The Three Categories: Device, Conducted and Emitted | d 231 |

| Definitions of Noise Specifications and Terms                           |       |

| Device Noise                                                            |       |

| Conducted Noise                                                         |       |

| Chapter 10 References                                                   |       |

| Chapter 11: Layout/Grounding (Precision, High Speed and Digital)        | 261   |

| The Similarities of Analog and Digital Layout Practices                 |       |

| Where the Domains Differ – Ground Planes Can Be a Problem               |       |

| Where the Board and Component Parasitics Can Do the Most Damage         |       |

| Layout Techniques That Improve ADC Accuracy and Resolution              |       |

| The Art of Laying Out Two-Layer Boards                                  |       |

| Current Return Paths With or Without a Ground Plane                     |       |

| Layout Tricks for a 12-Bit Sensing System                               |       |

| General Layout Guidelines – Device Placement                            |       |

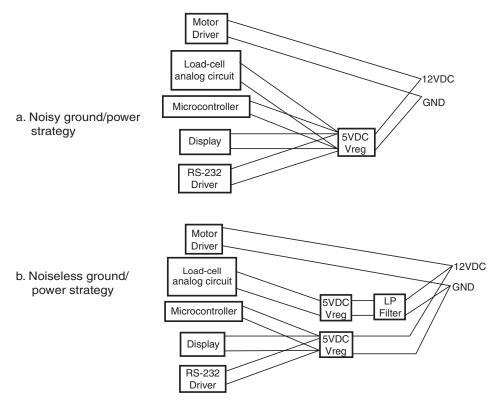

| General Layout Guidelines – Ground and Power Supply Strategy            |       |

| Signal Traces                                                           |       |

| Did I Say Bypass and Use an Anti-Aliasing Filter?                       |       |

| Bypass Capacitors                                                       |       |

| Anti-Aliasing Filters                                                   |       |

| PCB Design Checklist                                                    |       |

| 0                                                                       |       |

| Contents | ; |

|----------|---|

|----------|---|

| Chapter 12: The Trouble With Troubleshooting Your Mixed-Signal De  | signs  |

|--------------------------------------------------------------------|--------|

| Without the Right Tools                                            | -      |

| The Basic Tools for Your Troubleshooting Arsenal                   |        |

| You ask, "Does my Circuit A/D Converter Work?"                     |        |

| Power Supply Noise                                                 |        |

| Improper Use of Amplifiers                                         |        |

| Don't Miss the Details                                             |        |

| Conclusion                                                         |        |

| Chapter 12 References                                              |        |

| Chapter 13: Combining Digital and Analog in the Same Engineer, and | on the |

| Same Board                                                         | 307    |

| The Signal Chain to the Real World                                 |        |

| Tools of the Trade                                                 |        |

| Throwing the Digital In With the Analog                            |        |

| Conclusion                                                         |        |

| Appendix A: Analog-to-Digital Converter Specification Definitions  |        |

| and Formulas                                                       | 319    |

| Appendix B: Reading FFTs                                           | 329    |

| Reading the FFT Plot                                               |        |

| Appendix C: Op Amp Specification Definitions and Formulas          | 337    |

| Index                                                              | 343    |

## Preface

I went to an analog university where the core courses were, of course, all analog. Then I started my career at a high-quality, premier, analog house; Burr-Brown. Mind you, my objective was not to work at an analog house, my objective was to have a job. Nonetheless, there I rubbed shoulders with the best analog engineers in industry. After thirteen years, I decided to expand my horizons and work for a digital company. For me, thirteen was a lucky number because this is when my real education began.

What did I learn? I learned that you design your circuit so that it works in the application, not so that you have the most elegant solution in industry. I also learned that you can use digital circuits as well as analog circuits to get the job done. Moreover, I learned that sometimes ignorance is bliss. Many of the digital engineers that I have worked with don't know that some tasks are impossible. For instance, at Burr-Brown we trimmed our precision analog circuits with the high technology of Nicrome. This trim process is very specific to analog silicon circuits and is accurate. I told the engineers that they could not have precision products without a Nicrome process. Boy was I wrong. Microchip trims in analog circuit precision with their digital Flash process.

I have always been a "died in the wool" analog engineer, but I am starting to change. I haven't made a total transition to the "dark (digital) side," but digital is looking more attractive all the time. This attraction is enhanced by the fact that I am very familiar with analog and have a diverse set of analog, and now digital, tools to solve my circuit problems. This book is for you so that you can also have the same set of tools and can become more competitive in your design endeavors.

Digital circuitry and software is encroaching into the analog hardware domain. Analog will never disappear at the sensor conditioning circuit, power supply, or layout strategies. I know the digital engineer will continue to be challenged by analog issues, even if they deny that they exist.

Now let's add to the complexity of the digital engineer's challenges. The advances in microcontroller and microprocessor chip designs are growing in every direction. Increased speed and memory is just one example of the direction that these devices are taking. However, the most interesting change is the addition of peripherals, including analog and interface circuitry. Not only is the engineer required to know the details of the implementation of these peripherals, but also know the basics of layout strategies. Today, the digital engineer needs an added dimension of knowledge in order to solve problems beyond the firmware design challenges.

Going forward, the digital engineer needs some basic tools in their toolbox. I wrote this book for practicing digital engineers, students, educators and hands-on managers who are looking for the analog foundation that they need to handle their daily engineering problems. It will serve as a valuable reference for the nuts-and-bolts of system analog design in a digital word. The target audience for this book is the embedded design engineer that has the good fortune to wander into the analog domain.

## Acknowledgments

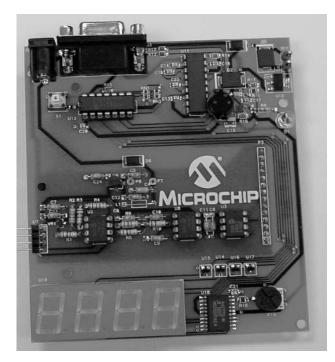

I'd like to thank all of the engineers who gave their time to review the material in the volume. A primary reviewer, Kumen Blake (Microchip Technology engineer) was meticulous and always provided excellent, relevant feedback. Paul McGoldrick (AnalogZone, editor-in-chief) gave significant time to ensure that sections of this book were accurate and concisely written. Numerous engineers at Microchip Technology, Texas Instruments and Burr-Brown also reviewed the material for technical accuracy.

Thanks also to Newnes acquisition editor Harry Helms and Kelly Johnson of Borrego Publishing. Harry pestered me for over a year to just sit down and write. I then said to him it would take two years to finish this book, and he said it would take one year. It actually took ten months from start to finish only because of Harry's enthusiastic encouragement at the beginning. Kelly did an outstanding job of editing my final-author's copy.

And especially, thanks to my support system in Tucson, Arizona. They were my cheerleaders in this solitary endeavor. And together, we finished it!

## About the Author

Bonnie Baker writes the monthly "Baker's Best" for *EDN* magazine. She has been involved with analog and digital designs and systems for nearly 20 years. Bonnie started as a manufacturing product engineer supporting analog products at Burr-Brown. From there, Bonnie moved up to IC design, analog division strategic marketer, and then corporate applications engineering manager. In 1998, she joined Microchip Technology and has served as their analog division analog/mixed-signal applications engineering manager and staff architect engineer for one of their PICmicro divisions. This has expanded her background to not only include analog applications, but microcontroller solutions as well.

Bonnie holds a Masters of Science in Electrical Engineering from the University of Arizona (Tucson, AZ) and a bachelor's degree in music education from Northern Arizona University (Flagstaff, AZ). In addition to her fascination with analog design, Bonnie has a drive to share her knowledge and experience and has written over 200 articles, design notes, and application notes and she is a frequent presenter at technical conferences and shows.

### CHAPTER

## 1

Bridging the Gap Between Analog and Digital

## CHAPTER 1

## Bridging the Gap Between Analog and Digital

A few years ago, I was approached by a new graduate, engineering applicant at the Embedded Systems Conference (ESC), 2001 in San Francisco. When he found out that I was a manager, he explained that he was looking for a job. He said he knew of Microchip Technology, Inc. and wanted to work for them if he could. He immediately produced his resume. I gave him a few more details about my role at Microchip. At the time, I managed the mixed signal/linear applications group. My department's roles were product definition, technical writing, customer training, and traveling all over the world visiting customers. At the conclusion of this "sales" pitch, he proudly told me that it sounded like a great job. I reemphasized that I was in the Analog arm at Microchip. He obviously thought that he did his homework because he told me that analog is dying and digital will eventually take over. Anyone who knew anything about Microchip would agree! Wow, I had a live one.

I was there, doing my obligatory Microchip booth duty for the afternoon. There was a lot of action on the floor, and the room was full of exhibits. The lights were on, the sound of conversations were projecting across the room. The heating and cooling system was doing a splendid job of keeping us comfortable. Exhibitors in the booths were (believe it or not) demonstrating the operation of sensors, power devices, passive devices, RF products, and so forth. There must have been several hundred booths, all of which were trying to promote their engineering merchandise.

Figure 1.1: The Embedded Systems Conference exhibit hall in 2001 had hundreds of booths, many of which were already showing signs of interest in analog systems. This was done even though the emphasis of the conference was digital.

#### Chapter 1

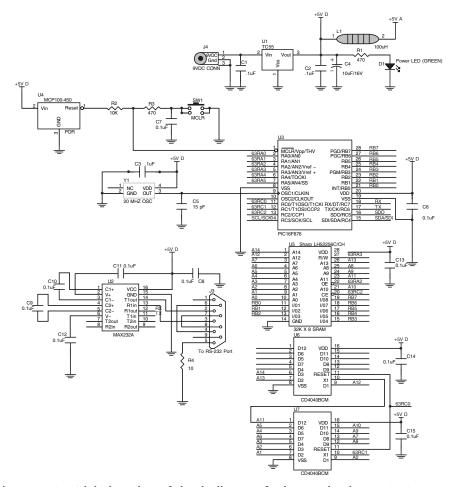

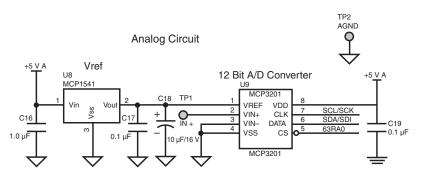

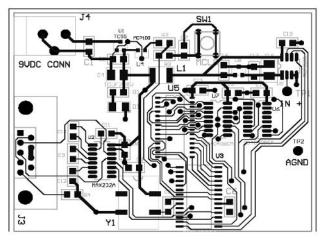

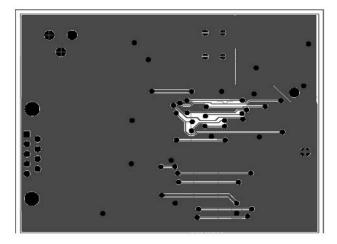

Some of the vendor exhibits had analog signal conditioning demonstrations. As a matter of fact, right in front of us, Microchip had a temperature sensor connected to a computer through the parallel port. The temperature sensor board would self-heat, and the sensor would measure this change and show the results on the PC screen. Once the temperature reached a threshold of 85°C, the heating element was turned off. You could then watch the temperature go down on the PC until it reached 40°C, at which point the heating element would be turned-on again.

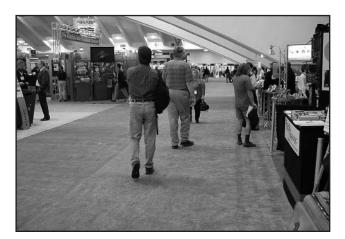

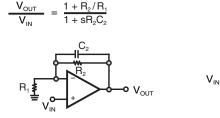

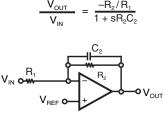

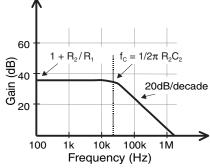

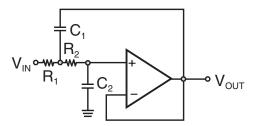

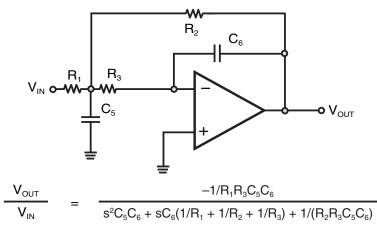

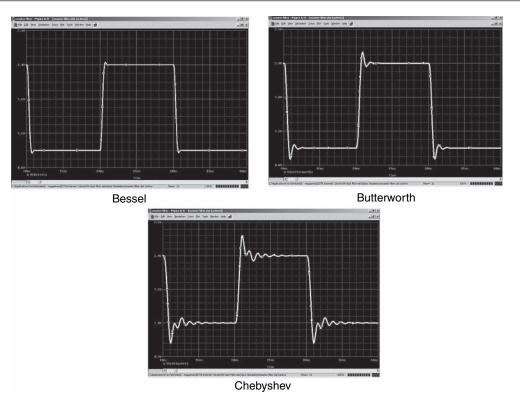

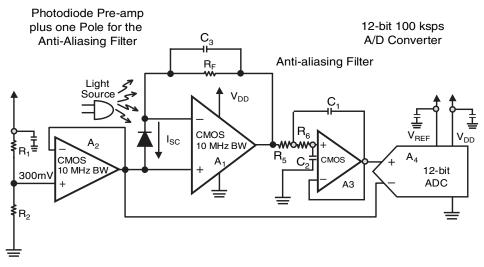

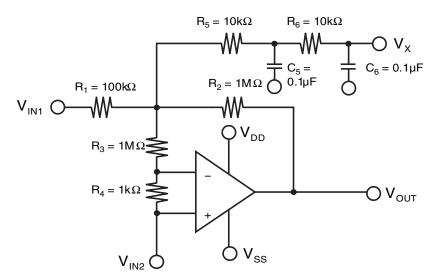

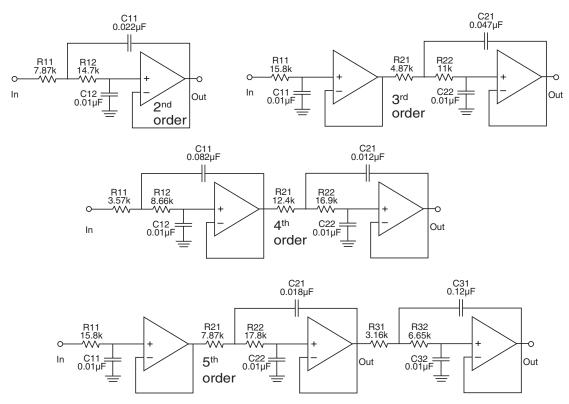

At a second counter, we also had a computer running the new FilterLab® analog filter design program. With this tool, you can specify an analog filter in terms of the number of poles, cutoff frequency and approximation type (Butterworth, Bessel and Chebyshev). Once you type in your information, the software spits out a filter circuit diagram, such as the filter circuit shown in Figure 1.2. You can theoretically build the circuit and take it to the lab for testing and verification. There was a customer at the counter, playing around with the filter software.

Figure 1.2: One of the views of the FilterLab program from Microchip provided analog filter circuit diagrams. This particular circuit is a 5<sup>th</sup> order, low-pass Butterworth filter with a cut-off frequency of 1 kHz. The FilterLab program from Microchip is just one example of a filter program from a semiconductor supplier. Texas Instruments, Linear Technology, and Analog Devices have similar programs available on the World Wide Web.

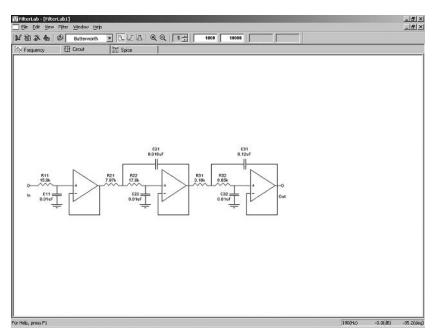

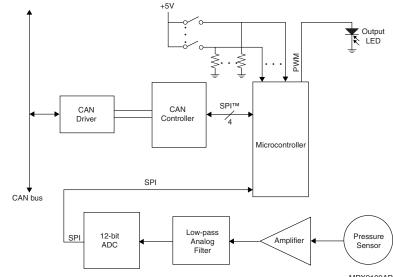

At exhibit counter number three, there was a CANbus demonstration with temperature sensing, pressure sensing and DC motor nodes. CANbus networks have been around for over 15 years. Initially, this bus was used in automotive applications requiring predictable, error-free

communications. Recent falling prices of controller area network (CAN) system technologies have made it a commodity item. The CANbus network has expanded past automotive applications. It is now migrating into systems like industrial networks, medical equipment, railway signaling and controlling building services (to name a few). These applications are using the CANbus network, not only because of the lower cost, but because the communication with this network is robust, at a bit rate of up to 1 Mbits/sec.

A CANbus network features a multimaster system that broadcasts transmissions to all of the nodes in the system. In this type of network, each node filters out unwanted messages. An advantage from this topology is that nodes can easily be added or removed with minimal software impact. The CAN network requires intelligence on each node, but the level of intelligence can be tailored to the task at that node. As a result, these individual controllers are usually simpler, with lower pin counts. The CAN network also has higher reliability by using distributed intelligence and fewer wires.

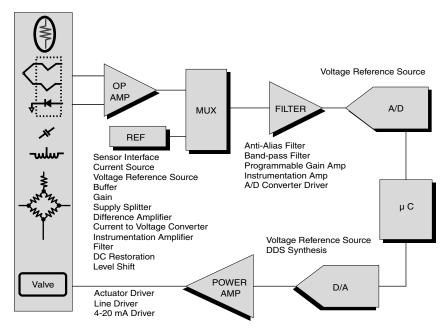

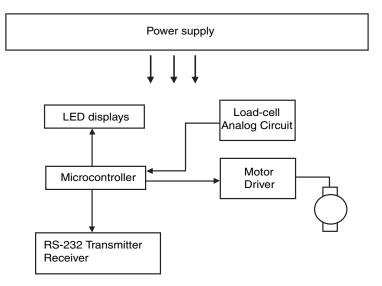

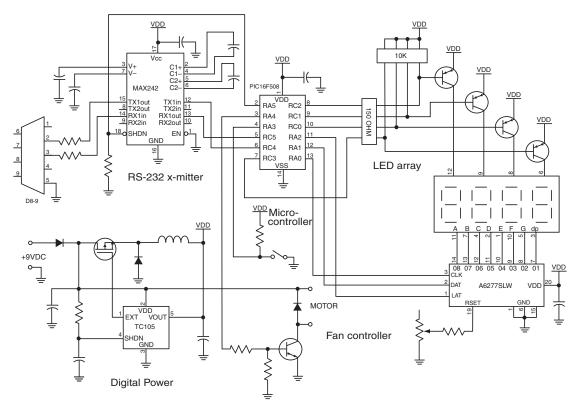

You might say, "What does this have to do with analog circuits?" And the answer is *every-thing*. The communication channel is important only because you are shipping digitized analog information from one node to another. With this ESC exhibit, three CANbus nodes communicated through the bus to each other. One node measured temperature. The temperature value was used to calibrate the pressure sensor on the second node. You could apply pressure to the pressure-sensing node by manually squeezing a balloon. (This type of demonstration was put together to get the observer more involved.) The sensor circuitry digitized the level pressure applied and sent that data through the CANbus network to a DC motor. The DC motor was configured so that increased pressure would increase the revolution per minute (RPM) of the motor. Figure 1.3 shows a basic block diagram containing the pressure-sensing node.

Figure 1.3: The CANbus system at the 2001 Embedded Systems Conference has three different analog function nodes. The node illustrated in this figure measured the pressure applied to a balloon and sent the data across the CANbus network to a DC motor (not illustrated here).

MPX2100AP

Then to finish out the Microchip displays in the booth, there were three counters that had microcontroller demos.

I asked the engineering applicant, giving him a chance to redeem himself, "Out of curiosity, do you see anything analog-ish like in this room?" He looked around the convention room thoughtfully. I was amused when he sympathetically looked at me and answered, "No, not really." I think that he thought I was a bit old-fashioned, behind the times. No regrets from him. He was confident that he gave me an insightful, informed answer.

You guessed it. His resume went into the circular file.

#### Try to Measure Temperature Digitally

No, this is not a book about interview techniques. This book is neither about how to win points and climb the corporate ladder. This is a book about the analog design opportunities that surround us every day, all day long, and how we can solve them in a single-supply environment. Reflecting on the applicant's answer, I think that he was partially right. Digital solutions are encroaching into the analog hardware in a majority of applications.

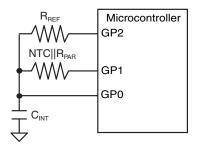

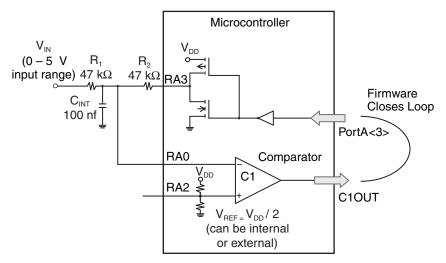

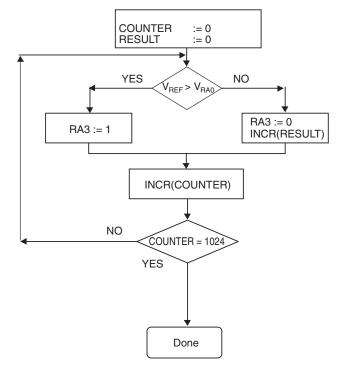

So let's try to measure temperature digitally. The simple, low resolution analog-to-digital (A/D) converter can easily be replaced with a resistor/capacitor (R/C) pair connected to a microcontroller I/O pin. The R/C pair would supply a signal that operates with a single-pole,

rise-time function. The controller counts milliseconds, with its oscillator/timer combination measures the input signal. Why would you want to do this? Maybe you are measuring temperature with a sensor that changes its resistance value with changes in temperature.

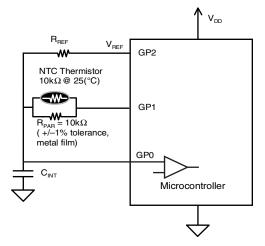

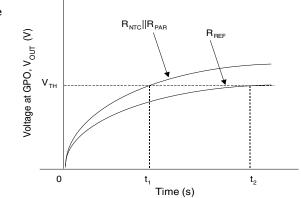

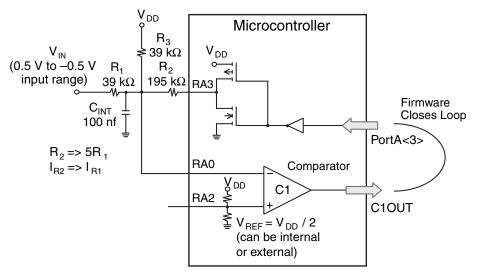

The temperature sensing circuit in Figure 1.4 is implemented by setting GP1 and GP2 of the microcontroller as inputs. Additionally, GP0 is set low to discharge the capacitor,  $C_{INT}$  As the voltage on  $C_{INT}$  discharges, the configuration of GP0 is changed to an input and GP1 is set to a high output. An internal timer counts the amount of time (t<sub>1</sub> in Figure 1.5) before the voltage at GP0 reaches the threshold (V<sub>TH</sub>), which changes the recognized input from 0 to 1. In this case,  $R_{NTC}$ (a negative temperature coefficient thermistor) is placed in parallel with  $R_{PAR}$  or  $R_{NTC} || R_{PAR}$ . This parallel combination interacts with  $C_{INT}$ . After this happens, GP1 and GP2 are again set as inputs and

Figure 1.4: This circuit switches the voltage reference on and off at GP1 and GP2. In this manner, the time constant of the NTC thermistor in parallel with a standard resistor (RNTC || RPAR) and integrating capacitor ( $C_{INT}$ ) is compared to the time constant of the reference resistor ( $R_{REF}$ ) and integrating capacitor.

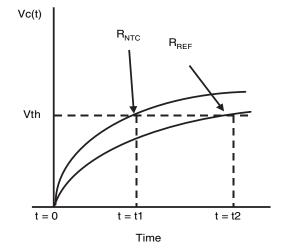

Figure 1.5: The R/C time response of the circuit shown in Figure 1.4 allows for the microcontroller counter to be used to determine the relative resistance of the negative temperature coefficient (NTC) thermistor element.

GP0 as an output low. Once the integrating capacitor  $C_{INT}$  has time to discharge, GP2 is set to a high output and GP0 as an input. A timer counts the amount of time before GP0 changes to 1 again, but this provides the timed amount of  $t_2$ , per Figure 1.5. In this case,  $R_{REF}$  is the component interacting with  $C_{INT}$ .

The integration time of this circuit can be calculated using:

$$V_{OUT} = V_{REF} (1 - e^{-t/RC}) \text{ or}$$

$$t = RC \ln (1 - V_{TH} / V_{REF})$$

where  $V_{OUT}$  is the voltage at the I/O pin, GPO,

V<sub>REF</sub> is the output, logic-high voltage of the I/O pin, GP1 or GP2;

$V_{TH}$  is the input voltage to GP0 that causes a logic 1 to trigger in the microcontroller.

If the ratio of  $V_{TH}$ :  $V_{REF}$  is kept constant, the unknown resistance of the  $R_{NTC} \parallel R_{PAR}$  can be determined with:

$$\mathbf{R}_{\mathrm{NTC}} \| \mathbf{R}_{\mathrm{PAR}} = \mathbf{R}_{\mathrm{REF}} (t_2/t_1)$$

Notice that in this configuration, the resistance calculation of the parallel combination of  $R_{\text{NTC}} \parallel R_{\text{PAR}}$  is independent of  $C_{\text{INT}}$  but the absolute accuracy of the measurement is dependent on the accuracy of your resistors.

Oops, did I say you can use a linear resistor and a charging device like a capacitor to replace an A/D converter in a temperature measurement system? I guess my applicant at the ESC show was also wrong. Analog will never disappear and the digital engineer will continue to be challenged to delve into these types of issues. The analog solution is many times more efficient and usually more accurate. For instance, the previous R/C example is only as accurate as the number of bits in the timer, the speed of the oscillator, and how accurately you know the value of your resistors.

#### Road Blocks Abound

I have worked with a wide spectrum of analog and digital designers. Each one of them has their own quirks and reasons why they can't do everything, but here are some statements that I have received from my digital clientele concerning their analog challenges.

#### Not My Job!

This statement came about with surprising frankness. "People in my department are avoiding analog circuitry in their design as much as possible, no matter how important it is. Many of them have had experiences where analog circuit performance was hard to predict. Therefore, almost every engineer will find an existing analog circuit and use that as a point of reference. If they have the misfortune of being asked to design part or all of the analog circuit from scratch, they will try to use facts that they remember from their school days. And in their school days they studied mostly digital."

Good luck. It seems from this statement that the died-in-the-wool digital designer has no interest in how to get from A to B, but more interest in what the cookbook suggests.

It turns out that the designers who operate in this mode are like a carpenter with a hammer looking for a nail. The designer has a circuit solution and tries to make it fit their application. A good example of applying the cookbook solution to a place where it won't fit is to try to use

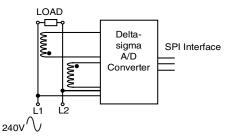

a standard 12-bit successive approximation register (SAR) in a power sensing application. This type of application actually requires a sigma-delta converter. As you will find later in this book (Chapter 3), the sigma-delta ( $\Sigma$ - $\Delta$ ) converter can reach a resolution level in the sub-nano volt region. This is an advantage because you not only eliminate the input, analog-gain stage, but you reduce the noise in the bandpass region of your signal. Figure 1.6 shows this power meter solution.

In this circuit, the current through the power line is sensed using an inductor on the low-side of the load. As a result, the voltage drop across this sensing element must be low.

#### Show Me the Beef

Figure 1.6: A power meter application requires <12-bit resolution in the system. This may imply that a simple 12-bit SAR converter can do the job, but the required LSB size is much smaller than the SAR converter can provide. Consequently, a sigma-delta converter is often used.

One day, a digital engineer said to me, "Thank god, I have finally found the key to working with analog and now I can go back about my digital business. Thank you for that one, insightful tip."

The tip I gave him was not that earthshaking. As a matter of fact, it provided the two primary operational amplifier specifications that an engineer uses when designing an analog low-pass filter. See Gain Bandwidth Product and Slew Rate (Chapter 4).

The gain bandwidth product (GBWP) is a multiplication factor that helps you predict the closed-loop bandwidth of an operational amplifier. You can easily find this parameter by looking at the specification table of the amplifier. You can quickly find this specification out of the 30 or 40 items in the table by looking at the "units" column. That column is usually on the right side of the table. When you are trying to find the gain bandwidth product specification, look for frequency units in Hz, kHz or MHz. Once you find these abbreviated units, verify that you have found the right item by looking to the left for the specification definition. Now, double-check and ensure you understand the test conditions for this specification by reading the conditions column and the general conditions that are summarized at the top of the table. All of these areas on a typical data sheet are pointed out in Figure 1.7.

| Electrical Characteristics: Unless of $V_{OUT} = V_{DD}/2$ , $R_L = 10 \text{ k}\Omega$ to $V_{DD}/2$ , and |                 | ted, $T_A = -$ | -25°C, V | <sub>DD</sub> = +1.8 | to 5.5V, V <sub>s</sub> | $_{\rm s} = {\rm GND}, V_{\rm CM} = V_{\rm DD}/2$ |

|-------------------------------------------------------------------------------------------------------------|-----------------|----------------|----------|----------------------|-------------------------|---------------------------------------------------|

| Parameters                                                                                                  | Sym             | Min            | Тур      | Max                  | Units                   | Conditions                                        |

| AC Response                                                                                                 |                 |                |          |                      |                         |                                                   |

| Gain Bandwidth Product                                                                                      | GBWP            |                | 1.0      | _                    | MHz ┥                   |                                                   |

| Phase Margin                                                                                                | PM              | _              | 90       | -                    | 0                       | G = +1                                            |

| Slew Rate                                                                                                   | SR              | _              | 0.6      | _                    | V/µs                    |                                                   |

| Noise                                                                                                       |                 |                |          |                      |                         |                                                   |

| Input Noise Voltage                                                                                         | E <sub>ni</sub> | _              | 6.1      | _                    | µVp-p                   | f = 0.1 Hz to 10 Hz                               |

| Input Noise Voltage Density                                                                                 | e <sub>ni</sub> | _              | 28       | _                    | nV/√Hz                  | f = 1 kHz                                         |

| Input Noise Current Density                                                                                 | i <sub>ni</sub> | _              | 0.6      |                      | fA/√Hz                  | f = 1 kHz                                         |

Figure 1.7: A typical electrical specification table for an operational amplifier has seven columns. When searching for a particular specification, the units-column is the easiest one to start with.

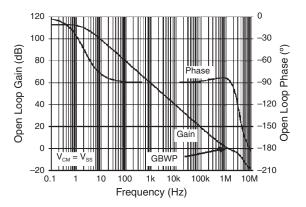

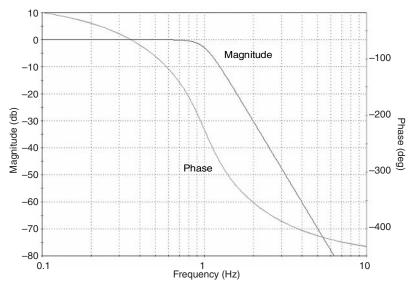

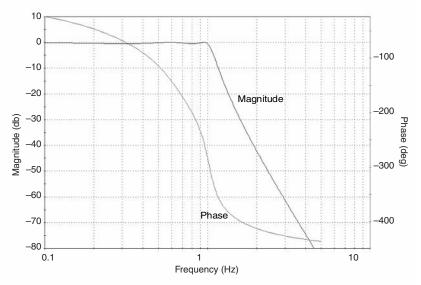

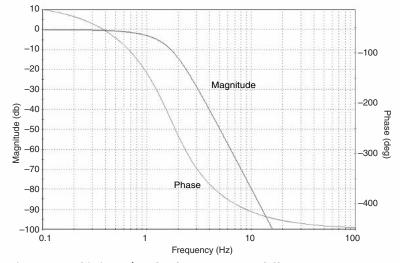

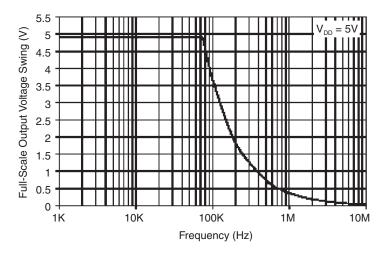

A second place where this specification can be found is in the characteristic performance graphs later on in the data sheet (see Figure 1.8). *Open-loop gain versus frequency* is the usual label for this curve. Sometimes the open-loop phase is included in this graph. You will find that the 0dB crossing of the gain curve will usually match the gain bandwidth product in the specification table.

Figure 1.8: These typical performance curves show many of the parameters in the specification table of the data sheet of an amplifier. This graph illustrates the typical open-loop gain, phase vs. frequency response. The arrow in this figure points to the gain bandwidth product for this unity-gain-stable amplifier.

1

#### Chapter 1

The gain bandwidth product (GBWP) will tell you the highest small-signal frequency (~  $\pm 100 \text{ mV}$ ) that you can send through your amplifier circuit without distortion. It also tells you the frequency where a pole is introduced to your closed-loop amplifier circuit. This is particularly critical to know when you design low-pass filters. In this type of circuit, you deliberately put poles in the transfer function by putting resistors and capacitors around the amplifier, as shown in Figure 1.2. If the amplifier adds a pole, your circuit could oscillate. Consequently, the closed-loop bandwidth of the amplifier must be at least 100 times higher than the cutoff frequency ( $f_{CUT-OFF}$ ) of the filter. Another way of stating this is that the gain bandwidth product of your amplifier should be equal to or greater than 100 ×  $f_{CUT-OFF}$  (this assumes the filter has a gain of +1 V/V). If you don't take these precautions, you might erroneously be inclined to investigate your filter equations only to find out that the amplifier is not well-suited for your design.

You might ask, "How important is this specification in other amplifier application circuits?" Generally, you will need an amplifier with good bandwidth performance for your signal, but probably won't see instability because of your amplifier selection. Or in another application, you may be more concerned about the quiescent current of the amplifier or power supply capability instead of the bandwidth because you are designing a battery-powered circuit that operates at DC.

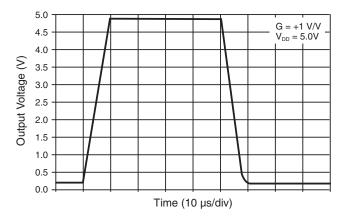

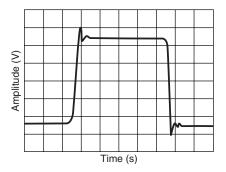

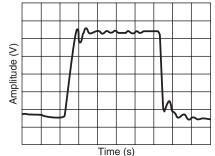

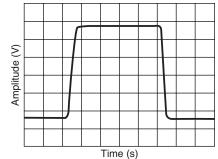

The second specification that I mentioned previously is slew rate. The slew rate of an amplifier is determined by putting a square wave signal at the input of the amplifier and looking to see how fast the signal changes on the output. The units of this specification are generally V/sec, V/msec, or V/ $\mu$ sec. You can find this specification in the table in the same way we found the gain bandwidth product. There is also a characteristic curve in most amplifier data sheets that gives a good look at how a typical part will perform. You'll find that the label of this graph is usually "Large signal, noninverting pulse response" (Figure 1.9).

Figure 1.9: This graph illustrates the typical time domain response of the output voltage vs. time of an amplifier.

With the filter circuit, this specification will tell you the maximum frequency of the large signals going through your circuit. If you don't pay attention to this specification, you may find that the amplifier distorts your larger, higher frequency signals. A good rule of thumb for this design parameter is: slew rate  $\geq (2\pi V_{OUT P-P} \times f_{CUT-OFF})$  where  $V_{OUT P-P}$  is the expected peak-to-peak output voltage swing below  $f_{CUT-OFF}$  of your filter.

Once again, you may ask, is this specification critical in all applications? The answer is again, no. You will find that the operational amplifier applications are very diverse. As a result, op amp manufacturers average 30 to 40 specifications in the tables and 15 to 25 characteristic curves. This is done to cater to as many users as they can. It is useful to note that the gain bandwidth product and slew rate were primary specifications for this one type of circuit. Meeting these specification requirements is critical if you are designing a low-pass filter, but this is not the case with other operational amplifier applications.

#### Don't Bother Me With the Small Stuff—Just Give Me the Data

One of the more common statements as said to me by the ambitious, digital engineer is, "Just give me the data. I will fix it in my processor. I know we can design a digital filter with the classical FIR or IIR filters, or better yet implement an FFT response. I can also calibrate the signal if need be. I'm confident that I will be able to get rid of those undesirable, messy analog signals."

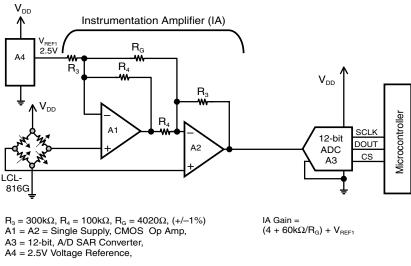

This comment always brings a smile to my face. See the case in point with the circuit in Figure 1.10.

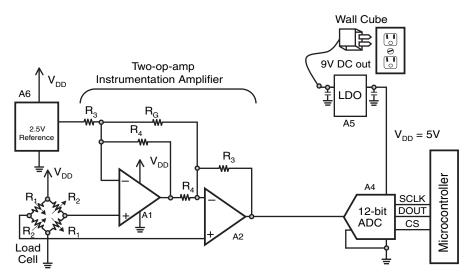

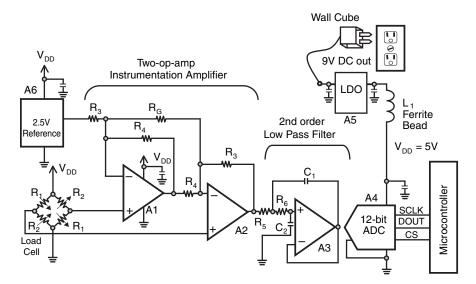

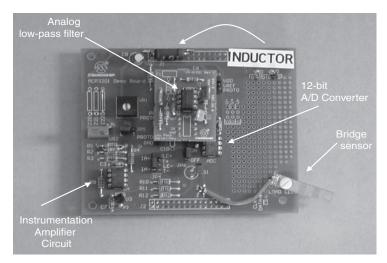

Figure 1.10: The circuit in this diagram uses a 12-bit A/D converter in combination with an instrumentation amplifier to convert the low-signal, output of a Wheatstone bridge sensor to usable digital codes.

#### Chapter 1

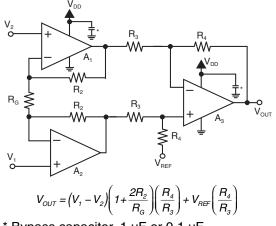

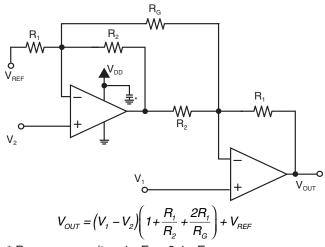

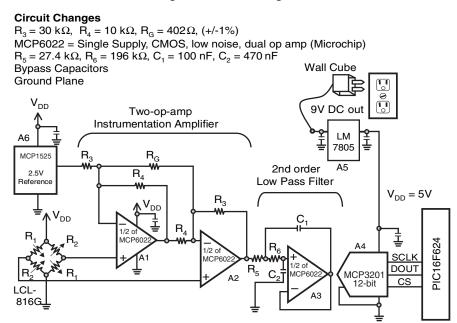

The analog portion of this circuit has a load cell, a dual-operational amplifier configured as an instrumentation amplifier, a SAR A/D converter, a microcontroller and voltage references for the IA and A/D converter. The sensor is a 1.2 k $\Omega$ , 2 mV/V load cell with a full-scale load range of ±32 ounces. In this 5 V system, the electrical full-scale output range of the load cell is ±10 mV. The instrumentation amplifier, consisting of two operational amplifiers (A1 and A2) and five resistors, is configured with a gain of 153 V/V. This gain matches the full-scale output swing of the instrumentation amplifier block to the full-scale input range of the A/D converter. The SAR A/D converter has an internal input sampling mechanism. With this function, a single sample is taken for each conversion. The microcontroller acquires the data from the SAR A/D converter. The controller can also execute calibration and translate the data into a usable format for tasks such as displays or actuator feedback signals.

The transfer function, from sensor to the output of the A/D converter is:

$D_{OUT} = ((LC_P - LC_N)(Gain) + V_{REF1})(2^{12}/V_{REF2})$ with  $LC_P = V_{DD} (R_2 / (R_1 + R_2))$

with  $LC_N = V_{DD} (R_1 / (R_1 + R_2))$

with GAIN =  $(1 + R_3 / R_4 + 2R_3 / R_G)$

where  $LC_P$  and  $LC_N$  are the positive and negative sensor outputs,

*GAIN* is the gain of the instrumentation amplifier circuit. The instrumentation amplifier is configured using A1 and A2. The gain is adjusted with  $R_G$ ,

$V_{REFI}$  is a 2.5 V reference which level shifts the instrumentation amplifier output

$V_{REF2}$  is the 4.096 V reference, which determines the A/D converter input range and LSB size;

$V_{DD}$  is the power supply voltage and sensor excitation voltage;

$D_{OUT}$  is a decimal representation of the 12-bit digital output code of the A/D converter (rounded to the nearest integer).

If the design of this system is poorly implemented, it could be an excellent candidate for noise problems. The symptom of a poor implementation is an intolerable level of uncertainty with the digital output results from the A/D converter. It is easy to assume that this type of symptom indicates that the last device in the signal chain generates the noise problem. But, in fact, the root cause of poor conversion results could originate with other active devices or passive components in the signal chain, the PCB layout or even extraneous sources.

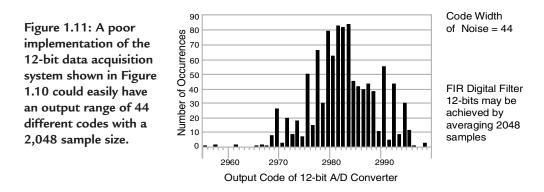

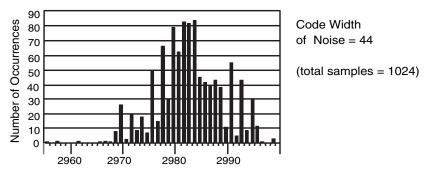

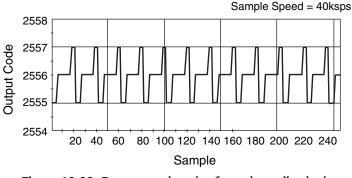

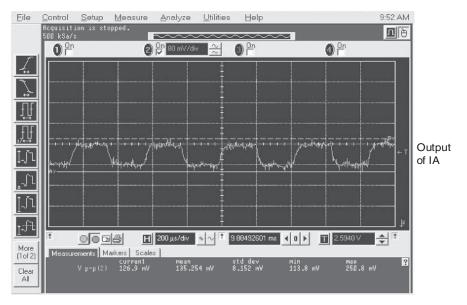

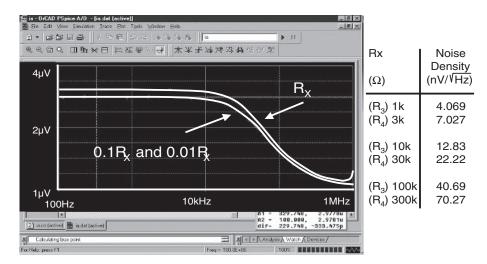

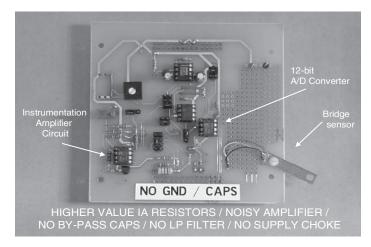

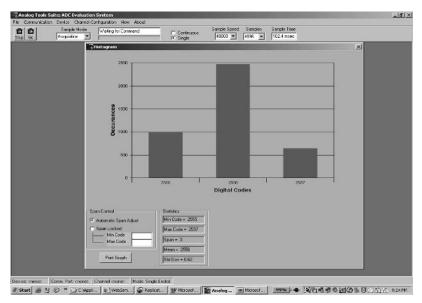

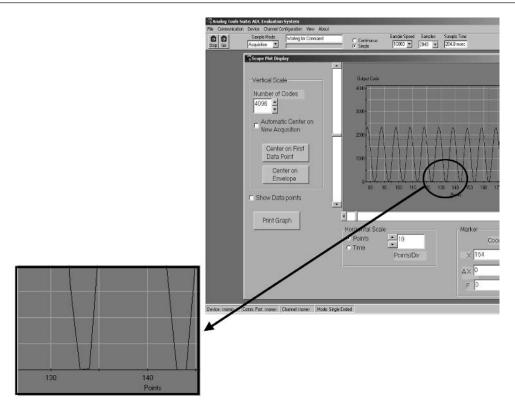

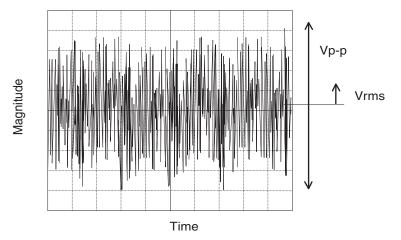

In this circuit, noise can be reduced within the analog channel hardware. But, with the first prototype of this circuit, these low noise precautions were not used. Therefore, the data output of the A/D converter illustrated in Figure 1.11 indicates that this was a noisy system. It is fine

to design a proto with this level of noise. In addition, it is truly divine to understand the noise and remove it in hardware wherever possible.

But, let's assume that you take the digital route to perform the filtering. On a perfect day, you will need to collect at least 2,048, 12-bit data points and calculate the average. I said on *a perfect day* because when I look at this data there seems to be more going on than just white noise. There are small occurrences in the lower 20 codes of the data, and the major portion of the data does not form a "normal distribution" type of curve. It seems to have troughs and there is nothing normal about this data at all.

A common, bad scenario is that the problem is never solved through the lifetime of your application circuit. These unknown noise problems are fixed with digital tricks. That overly confident statement ignores the trade-offs inherent in taking the all-digital route. One of the major consequences is time. A digital filter needs to collect several hundreds of samples in order to compete with the analog solution. On top of that, the already digitized signal has been contaminated by aliased (this is explained in Chapter 4), high-frequency signals, which you will never be able to tell your original signal from the contaminants. These tricks may or may not work over time.

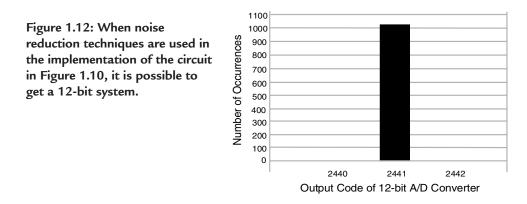

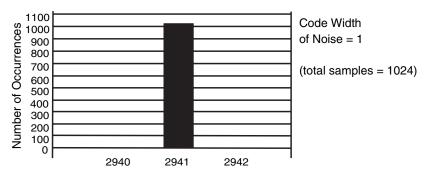

On the other hand, the analog solution is simple and final. The data loses its erratic behavior and you can get the same converted number every time! What do you do?

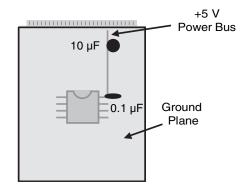

- 1. Put bypass capacitors across the power supply pin to ground with every active device. (See Chapter 10.)

- 2. Use a ground plane. This will usually require at least a two-layer board. (See Chapter 11.)

- 3. Reduce the resistor values in the instrumentation amplifier. When you reduce these resistors (without changing the throughput gain), the noise in the signal chain will also reduce. (See Chapter 10.)

- 4. Use low noise amplifiers. (See Chapter 12.)

- 5. Insert a low-pass filter before the A/D converter. This filter will remove higher frequency noise as well as eliminate aliasing problems. (See Chapter 4.)

- 6. Choke the power supply switching noise to the analog portion of the board with an inductor. (See Chapter 12.)

These are all simple solutions to a seemingly impossible, noisy circuit problem. Figure 1.12 shows the results of these actions.

Calibration can be another sticky point when you go to the digital environment. Once you loose your dynamic range in the analog domain, it is impossible to recover it digitally. For instance, if you use amplifiers in this circuit that do not give you good rail-to-rail performance, the outer limits of the signal is lost forever. Another situation, not related to Figure 1.10, could be if your signal is logarithmic instead of linear. If this is the case, digital manipulation will not take you very far. This type of data can only be fixed in the analog domain.

#### The Ultimate Key to Analog Success

News alert! The ultimate analog key does not exist. And I don't mind turning this around to tell analog engineers that digital engineering is a little more than ones and zeros. The analog mountains that can be climbed are analogous to your digital challenges. Following are three examples.

For the first example, in the sprit of designing a robust design, the digital designer architects the software to identify unforeseen, catastrophic errors. The watchdog timer (WDT) can be used for this purpose. The function of a watchdog timer is easy enough. It counts down using the system clock from an initial value to zero. During implementation, if your firmware does not reset this timer soon enough, the watchdog timer resets or interrupts the system without human intervention when the counter reaches zero. Alternatively, the analog domain protection circuitry is used to minimize the effects of unforeseen errors or transients. In analog disciplines this be can implemented with over-range notifications or protection devices at

sensitive nodes, such as zener diodes, metal oxide varistors (MOV), transzorbes, or Schottky diodes. With these types of additions to the hardware, "bad" signals are identified and eliminated before they become part of the signal path.

The second example would be to work on your digital design low-power strategies by effectively using clocking algorithms. Low power should be thought of as a "state of mind" (see Chapter 9). With a low-power mindset, you can throttle down your controller to near inactivity if you really want to save battery power. The hardware approach would be to reduce clock source rate or power supply voltage. An equally effective approach is to operate with a partial or complete controller/processor shutdown mode. Combining these techniques with execution time and a little intelligence, you can easily tackle your most challenging power conservation problems. In your analog design, you will choose the lower power devices and utilize device shutdown features. In this environment, the designer needs to research the market for the best solution, whether it is a similar lower power device, or an alternative silicon topology that runs more efficiently.

A third example would be where you savor and protect your programming tricks from your competition. You can do this by making the code unreadable in the finished product in the same way the analog engineer buries traces inside boards, blacks out device part numbers, or asks vendors to give him proprietary part numbers.

The list goes on. But the thing to remember and understand is that each of us, in our own disciplines, tries to take technology to its limit. So what do you do when your manager says in his one-sided conversational way, "You're an engineer (aren't you)? Good. Since we are understaffed, I need you to do the entire (hardware/software) design. What? You don't know anything about analog. Hmmm, maybe I need to find someone else? I knew you would rise to the occasion. Have your development schedule on my desk by the end of the day so I can set up a deadline schedule."

#### How Analog and Digital Design Differ

The basic difference between the analog mindset and digital mindset are embedded in the definitions of precision (calculated risk versus right every time), hardware versus software, and time (or the inverse of). The basic concepts behind analog and digital disciplines are easy to find. In terms of this book, I will describe analog design from a practical standpoint. You will find that the in-depth lists and details about product specifications will be a little thin, but there is a detailed discussion about key specifications as they relate to basic analog systems.

#### Precision

What is precise enough in an analog circuit? There are three ways to answer this question. A first aspect is, "as precise as it needs to be." You will find that some of your circuits will only require accuracy to one or two millivolts. Others will require accuracy to the submicrovolts.

#### Chapter 1

This difference in system requirements will encourage you to settle for "close enough" in some systems, and "What else can I squeeze out of this circuit?" in other systems.

A second aspect of accuracy involves really understanding the components and devices you are working with. In terms of the components, you should know that a 1 k $\Omega$  resistor or a 20 pF capacitor is not equal to those absolute values all the time. For instance, temperature can have a dramatic effect of these components. Also, there are variations from device-to-device out of your bin in the lab. The combination of these two major issues can change the performance of your circuit dramatically if you don't take them into consideration.

In terms of devices, you will find product data sheets have maximum guaranteed values and typical values. The maximum guaranteed values are self-explanatory in that you should expect that your devices will not over-range the specifications as stated provided the devices are not overstressed with higher voltages or temperatures. The typical values are another manner. There are a variety of ways to determine what these typical values should be, and you will find that each manufacturer will have their own way to calculate these values along with their justification. Some manufacturers take the average of a large sample of devices prior to the initial product release. Other manufacturers define their typical values as being equal to one standard deviation plus the average. I have also heard of manufacturers using their SPICE simulation as a guide for these numbers. Sometimes the Spice simulation is justified because it is impossible to test a particular specification.

The third aspect of accuracy is noise. When you take this issue into consideration, you need to have some understanding of statistical calculations with large samples. I am going to cover this issue in more detail later in Chapter 10.

#### Hardware versus Software

This discussion seems to simplify the problem a bit, but I have a solution for those embarking on the ownership of analog. Think of it in terms of learning the fundamentals about your components, knowing the general behavior of basics building block devices, and running through a high level evaluation of your circuits first.

#### 1. Learn the fundamentals about your components.

For instance, the fundamentals at the very bottom of the barrel include resistors, capacitors and inductors. You were probably exposed to the devices early in your career, but what do you really need to know as an analog design engineer?

Resistors are simple devices. There are several perspectives that you have to consider when you use this type of component in your design. The first, and most easy way of thinking about a resistor is that it influences voltage and current in your design. This is defined through the infamous Thevenin equation:

V / RI = 1

Where V is voltage

R is resistance in ohms

I is current in amperes

I always remember this formula from my elementary school geography lessons. <u>Vermont is</u> always over <u>**R**</u>hode <u>I</u>sland.

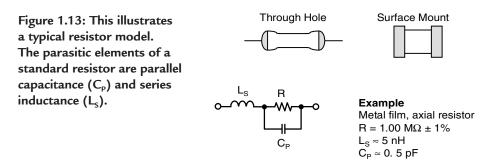

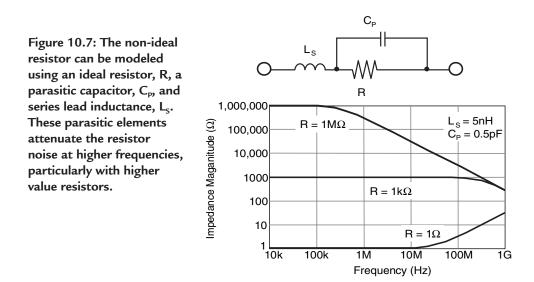

But this is the part of resistors in your circuit. For practical purposes, this is a DC equation, not AC. Moving past this formula, you need to be concerned about the parasitic characteristics. Namely, there is a parasitic capacitor in parallel with the resistive element and a parasitic inductor in series. These components are artifacts of the physical device. There is a diagram of the resistor with these parasitics in Figure 1.13.

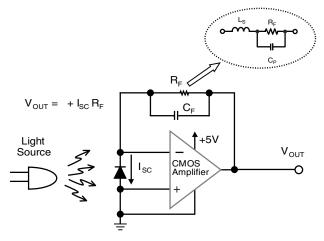

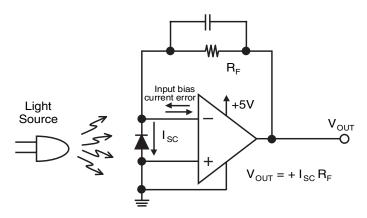

The fact is, I never worry about the parasitic capacitance until I started designing transimpedance, optical, photodiode-sensing circuits. An example of this type of circuit is shown in Figure 1.14. If blindly built (without concern for the parasitic capacitance), this photosensing circuit can mysteriously sing like a bird (oscillate) without too much effort. This oscillation is usually caused by an inappropriate choice of  $C_F$ , but it can also be caused by that phantom capacitor,  $C_{P}$ . These capacitors, in combination with the photodiode parasitic capacitance and the amplifier's

Figure 1.14: If you don't consider the parasitic capacitance of the feedback resistor, a transimpedance photosensing circuit can be unstable.

input capacitance interact to establish stability, or not (see Chapter 6). This is one example, but you can extrapolate this to other circuits if you are using small value discrete capacitors in parallel or series with discrete resistors.

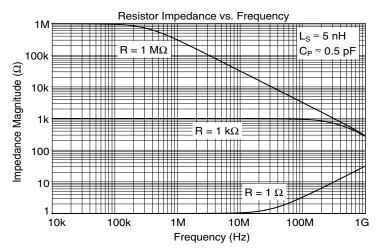

The parasitic inductance of the resistor (also see Figure 1.15) can affect higher speed systems where lower value resistors are the norm. This inductance can affect the behavior of the current sensing resistor used in switched-mode power supplies.

Generally speaking, the impedance of higher value resistors is more affected by the parasitic capacitance, and low value resistors is affected by the parasitic inductance. Figure 1.15 illustrates this point.

Figure 1.15: The impedance of a resistor changes from the defined DC resistance value to other values over frequency. The parasitic capacitance and impedance influence these changes.

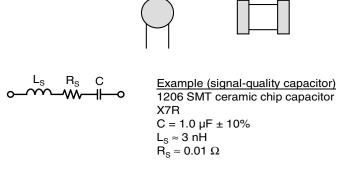

Capacitors, on the other hand, should be considered in the frequency domain when you are designing. There is one formula for the capacitor that I used frequently in my design. This formula is:

$I = C * \delta V / \delta t$

Where C is capacitance in farads

$\delta V$  is change in voltage in volts

$\delta t$  is change in time is seconds

Capacitors are very useful for power supplies, stability, loading low dropout regulators and loading voltage references. But, in all cases, you use capacitors to modify frequencies, not DC signals.

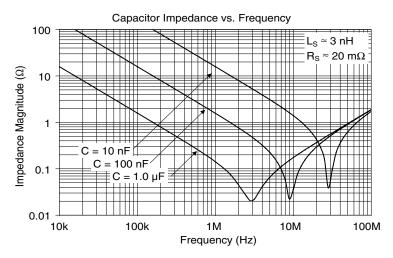

Figure 1.16: This illustrates a typical ceramic capacitor model. The parasitic elements of a standard capacitor is parallel resistance ( $R_s$ ), also know as effective series resistance (ESR), and series inductance ( $L_s$ ), also know as effective series impedance.

Figure 1.17: The frequency response of a capacitor varies at lower frequencies due to the series resistance and higher frequencies due to the series inductor.

- 2. *Know the general behavior of basic building blocks.* Consider these basic circuit cells as instruction codes. Start by using them in their most common circuit configurations or the classical approach. In analog, your basic building blocks are:

- Analog-to-digital converters (Chapters 2 and 3)

- Operational amplifiers (Chapters 5 and 6)

- 3. *Higher level thinking*. Are you afraid of math? Don't dwell on it at first. Concentrate on the practical side of analog applications. Learn the rules of thumb for analog. For

instance, many of us, being indoctrinated in the school system background, sharpen our pencils, pull out the old calculator and grind through the trees before we have a thought about what the forest looks like. Once you step back and think about it, you will find that your detailed analysis can be way off. If your analysis is correct, it probably is only part of the picture. Here is a perfect example of what I mean.

Problem:

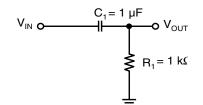

What is the corner frequency of the single-pole, low-pass R|C filter shown in Figure 1.18?

Answer:

*"Hand wave" solution:* Wait a minute. This isn't a lowpass filter. This is a high-pass filter. (You probably knew this right away but you would be amazed at how many

would overlook this simple conclusion!) But if I assumed that the author made a mistake and reversed the placement of the resistor and capacitor, the corner frequency would be about  $1/(2 \pi R \times C)$  or 160 Hz. How did I get there? Isn't  $1/2\pi$  equal to about 0.16? As a first pass, I think I can accept that error because the capacitor device-to-device error is probably  $\pm 10$  or 20% accurate.

Calculated solution (with blinders on):

$$\begin{split} (V_{OUT} - V_{IN}) \,/\, (1/sC_1) &= V_{OUT} \,/\, R_1 \\ V_{OUT} \,(\, sC_1 + 1/R_1) &= V_{IN} \,/\, (1/sC_1) \\ V_{OUT} \,/\, V_{IN} &= (sR_1 \times C_1 + 1)/(sR_1 \times C_1) \end{split}$$

From this calculation, there is a pole at DC and a zero at 159.1549 Hz.

These two solutions don't agree! And I bet a SPICE simulation would match your calculated solution. The moral to this story is "hand wave," or think yourself through the problem first. SPICE does not mean "don't think," it means "verification of your analysis." With this type of analysis, you should keep in mind the accuracy (or lack there of) of the various components and devices in your system. After, and only after, you know generally how the circuit works and how the system responds, give your mathematical and SPICE skills a try (see Chapter 7).

#### Time and Its Inversion

In the digital domain, particularly with real time operating system (RTOS), you will find that you are counting minutes, seconds, milliseconds, and nanoseconds. This is also done with analog circuits, but more importantly, the inverse of seconds is counted. Taking the inverse of seconds helps you think in terms of frequency instead of time. Frequency information is much more critical here.

4. *This could be a good career decision*. The universities are graduating less and less engineers knowledgeable in analog, but as we all know, analog will not be going away any time soon.

#### **Organizing Your Toolbox**

You need to decide what is important and what is not for your future analog design work. An effective way to do this is to arm yourself with basic, key tools of the trade. You should concentrate as you collect your ammunition on six topics.

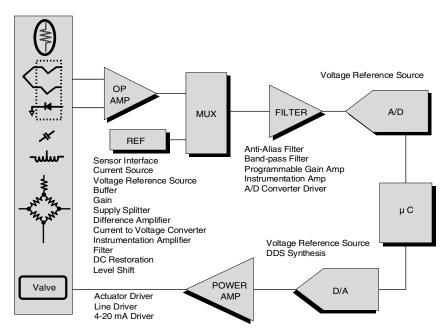

Figure 1.19: This signal chain is somewhat universal in that it deals with the analog signal coming in, conditions it through the amplification system and digitizes it in preparation for the microcontroller or processor.

First, know how to get data in and out of the digital domain. When this is mastered you will know the different topologies, important specifications, and the art of matching the converter to the application.

Then, sit back and ask yourself, "Where does my data in the controller really come from?" You will usually find some sort of sensor at the origin of the signal path. Further back from the A/D converter is the amplification system. In this system, the signal can either be enhanced through amplification or corrupted because of noise or linearity errors. The key player in the amplification system is the operational amplifier. Volumes of books have been written on this seemingly simple part, but not enough written about the single-supply operational amplifier applied in a simple manner. We will cover that in this book and take it one step further, into the battery-powered environment.

Now go back to your strength. Revisit the digital with analog in mind. Can you exploit your digital engine easily with a few analog tricks?

Go out on a limb. Bring the "art" of some of the essential analog disciplines into your toolbox. In particular, learn about noise sources and noise filters. Think about your layout and how it affects your circuit solution. Then go to the lab with confidence.

## Set Your Foundation and Move On, Out of the Box

Drop your inhibition. Have fun. Work outside your box. Learning a new craft takes persistence, time and a learning attitude. Analog design is a matter of sitting down and doing it, whether it is right or wrong. Then on the next day tweak it, and the next day, and the next day, until the circuit is finally refined. No magic formulas here, just some common sense, and problem solving techniques. First, define the problem. Then identify tools and strategies that can be used to work the problem. Third, work the problem to a solution. Finally, reread your definition of the problem and determine if your solution seems reasonable. Analog only demands good, honest, consistent and persistent work. Sound familiar?

#### **Chapter 1 References**

- "FilterPro<sup>™</sup> .MFB and Sallen-Key Low-Pass Filter Design Program," Bishop, Trump, Stitt, SBFA001A, Texas Instruments.

- FilterLab®2.0 User's Guide, DS51419A, Microchip Technology.

- "CANbus Networks Break Into Mainstream Use", Marsh, David, EDN, Aug. 22, 2002

- "Making the CANbus a "can-do" Bus," Warner, Will, EDN, Aug. 21, 2003.

- "Implementing Ohmmeter/Temperature Sensor," Cox, Doug, AN512, Microchip Technology.

- "Resistance and Capacitance Meter Using a PIC16C622," Richey, Rodger, AN611, Microchip Technology.

# CHAPTER

# 2

# The Basics Behind Analog-to-Digital Converters

# CHAPTER 2

# The Basics Behind Analog-to-Digital Converters

The analog-to-digital converter (ADC) is always in the back seat of the station wagon, looking at the analog signal through the rear window. In a way, I am soft on this device because this is where I was in my family's station wagon throughout my childhood, being one of six children. The controller, in the front seat, can see the results of the converter's labor, but the question is, can those results be counted on? If the ADC reports the system data incorrectly, the controller is blind to errors that have been introduced by the converter and signal chain. This is true unless you are willing to allocate a lot of code to try to unscramble the mess (with no guarantee of success). But why not go to the source of the problem. Believe me when I say the ADC can cause you a great deal of heartache if you don't understand the nuances. Your misunderstanding of how to use the ADC can leave the controller or processor struggling with erroneous or inaccurate data.

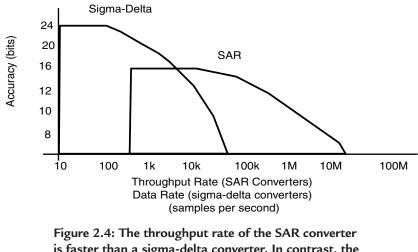

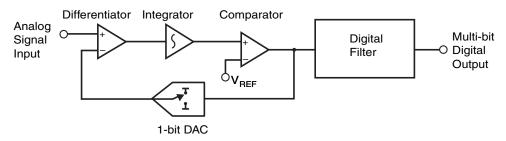

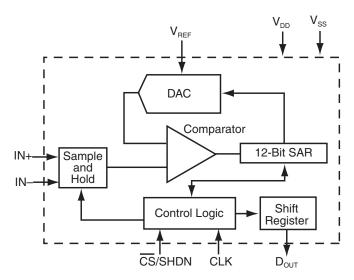

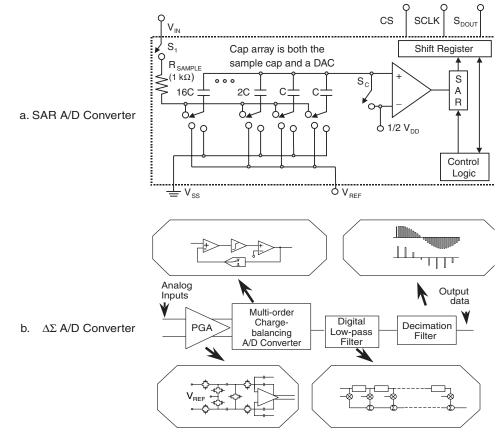

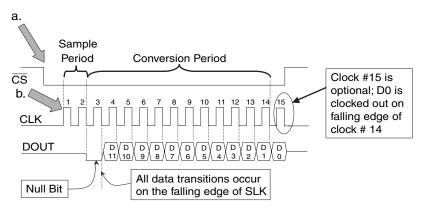

In this chapter, we are going to discuss the key specifications for ADCs and how they can impact your expected results from your converter. This list of specifications generally applies to all classes of converters. Then we will delve into the particulars of the successive approximation register (SAR) ADC. This part of the discussion will start with an explanation about how the SAR converter works. The issues discussed will give you insight on how to use this type of converter effectively, the first time. There will be more performance specifications and characteristics discussed here with emphasis on how to design with or around some of the converter's shortcomings. This is followed with a user-friendly version of how a sigma-delta ( $\Sigma$ – $\Delta$ ) ADC works. The  $\Sigma$ – $\Delta$  topics will follow the same line of discussion as with the SAR converter. First, we will talk about the topology and in particular how it impacts your signal chain. Following this brief discussion, the performance specifications that are particular to the  $\Sigma$ – $\Delta$  converter will be discussed, with solutions on how to work with or work around the  $\Sigma$ – $\Delta$  converter limitations.

The primary ADC specifications are summarized in Appendix A and B, so if you forget about the particulars of a specification, this is a great place to look. Appendix A contains a glossary of common converter specifications. In Appendix B, you will find out what fast Fourier transform (FFT) is and how it relates to the performance of your converter.

There are numerous other converters that you can use for your application circuits, like the Pipeline, FLASH, and voltage-to-frequency (V/F) converters, but these topologies are beyond the scope of this book.

## The Key Specifications of Your ADC

#### Input Range of the ADC

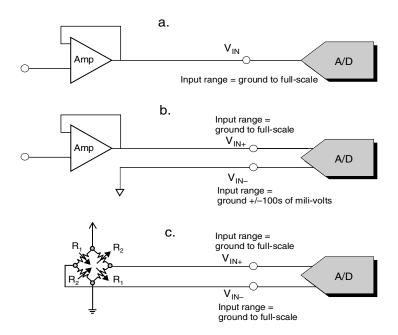

The input range of the ADC can be a bit tricky. You will find variations of single-ended, differential, pseudo-differential, while the input range is determined by the voltage reference  $(V_{REF})$  of the converter.

An example of the configuration of an ADC with a single-ended input is shown in Figure 2.1a. This type of converter input is easy to use because there is no question of what to do with that pin. The input voltage range is equal to the full-scale range (FSR) of the converter. Additionally, the digital code at the output of this configuration is straight binary (see the Straight Binary Section in this chapter).

Figure 2.1: The input(s) of ADCs can be configured in one of three ways. The single-ended input (A) is configured for one input voltage referenced to ground. Another type of input stage has two inputs configured as a "pseudo-differential" stage (B) where the signal input is the noninverting input, and the inverting input is used to reject small-signal system noise. The third type of input stage is the differential input (C) where the two inputs to the converter range from ground to the full-scale input voltage.

In Figure 2.1b, the input of the converter is configured as a pseudo-differential input. This simply means that the input to the converter is differential, but one of the input pins has a range that is limited to a few hundred millivolts from ground. This has the same output digital

coding as the single-ended input device. The digital code at the output is straight binary. You might ask what this configuration would do for you? True to the spirit of differential input stages, this type of device will reject small common-mode noise. In simple terms, if a small-signal, like 50 Hz or 60 Hz, is an undesirable part of the signal you are trying to convert, this common-mode signal will be rejected or eliminated. This is a nice feature as long as you understand that you have to connect it properly to ground.

A third type of input for ADCs is the fully differential input stage. With this configuration both inputs can be brought from ground to the converter's FSR. This is nice, because not only can you reject small common-mode signals but you also can convert a positive or negative analog signal to a digital output. You guessed it, the output code is in the format of two's complement (see the Two's Complement section in this chapter).

So why is this important? There are some signal sources that are differential. One example is the signal from a Wheatstone bridge in Figure 2.1c. You will find that if one of the inputs goes positive, the other will go negative. This action will give you a gain of 2 V/V in the analog domain. It will also couple the noise in the environment on both lines. The ADC will then be able to filter that noise and convert the signal of interest from the bridge.

With this type of input, the FSR is double what you might expect. If you think about it, if the noninverting input goes to its full range and the inverting input is referenced to ground, the difference in this signal is  $(V_{IN+} - V_{IN-}) = +V_{FS}$ . Now if the input signal changes so that the noninverting input is referenced to ground, and the inverting input is taken to full-scale, the difference in the input signal is  $(V_{IN+} - V_{IN-}) = -V_{FS}$ . So the actual FSR of this type of device is  $+V_{FS} - (-V_{FS})$  or  $2 \times V_{FS}$ , where  $V_{FS}$  is the full-scale input voltage range.

## Digital Coding of the Analog Signal

An analog-to-digital converter translates an analog input signal into a discrete digital code. This digital representation of the *real-world* signal can be manipulated in the digital domain for the purposes of information processing, computing, data transmission, or control system implementation. In any application where a converter is used, it is advantageous to have the code structure complement the microcontroller or processor's operands.

We are going to talk about the most common code schemes: Straight binary and binary two's complement code. For simplicity, all of the following code examples are for a 4-bit converter. The median analog voltages in the tables are the equivalent analog voltages that are at the center of the digital code.

These codes are mathematically described using the full-scale (FS) input range of the converter. Usually the full-scale input range of an ADC is equal to or twice as much as the voltage reference applied to the device. And in some instances, the voltage reference connect is tied internally in the device to the power supply. In all of these configurations, you will need to refer to the product's data sheet for specifics.

#### Chapter 2

The basic differences between these two types of code is:

- 1. The least significant bit (LSB) size of the two's complement code is twice as large as the LSB size of the straight binary code. This does not increase the number of codes that the converter can create. With the two's complement code, the positive and negative voltage inputs to the converter are represented with the same amount of codes that the straight binary represents, only the positive voltage input voltage with code.

- 2. The analog FSR of the straight binary code is a positive voltage from ground to  $V_{REF}$ . The analog FSR of the two's complement code is equal to the positive FSR, plus the unsigned negative FSR.

- 3. The digital output code of the two's complement code is easier when running arithmetic calculations, such as subtraction.

#### Straight Binary Code

The straight binary code is more accurately called unipolar straight binary. This digital format for an analog-to-digital conversion is the simplest to understand. As the name implies, this coding scheme is used only when positive voltages are converted. This is a good output code for converters that are configured with a signal input, as shown in Figures 2.1a and 2.1b. An example of this type of coding is shown in Table 2.1.

Table 2.1: The Unipolar Straight Binary Code representation of zero volts is equal to a digital 0000. The analog fullscale minus one LSB digital representation is equal to 1111. With this code there is no digital representation for analog full-scale.

| Median analog voltage (V)                     | Digital code |

|-----------------------------------------------|--------------|

| 0.9375 FS ( <sup>15</sup> / <sub>16</sub> FS) | 1111         |

| 0.875 FS ( <sup>14</sup> / <sub>16</sub> FS)  | 1110         |

| 0.8125 FS ( <sup>13</sup> / <sub>16</sub> FS) | 1101         |

| 0.75 FS ( <sup>12</sup> / <sub>16</sub> FS)   | 1100         |

| 0.6875 FS ( <sup>11</sup> / <sub>16</sub> FS) | 1011         |

| 0.625 FS ( <sup>10</sup> / <sub>16</sub> FS)  | 1010         |

| 0.5625 FS ( <sup>9</sup> / <sub>16</sub> FS)  | 1001         |

| 0.5 FS ( <sup>8</sup> / <sub>16</sub> FS)     | 1000         |

| 0.4375 FS ( <sup>7</sup> / <sub>16</sub> FS)  | 0111         |

| 0.375 FS ( <sup>6</sup> / <sub>16</sub> FS)   | 0110         |

| 0.3125 FS ( <sup>5</sup> / <sub>16</sub> FS)  | 0101         |

| 0.25 FS ( <sup>4</sup> / <sub>16</sub> FS)    | 0100         |

| 0.75 FS ( <sup>3</sup> / <sub>16</sub> FS)    | 0011         |

| 0.1875 FS ( <sup>2</sup> / <sub>16</sub> FS)  | 0010         |

| 0.0625 FS ( <sup>1</sup> / <sub>16</sub> FS)  | 0001         |

| 0                                             | 0000         |

When this scheme is used to represent a positive analog signal range, the digital code for zero volts is equal to zero (0000 per Table 2.1). The definition of a positive voltage is the amplitude between the ADC ground or the inverting input and the noninverting input of the ADC. Given

an ideal converter with no offset, gain, integral nonlinearity (INL), differential nonlinearity (DNL) error or noise, the code transition from 0000 to 0001 occurs at the analog value of:

First Code Transition =  $(0 + \frac{1}{2} \text{ LSB})$ Second Code Transition =  $(1 \text{ LSB } + \frac{1}{2} \text{ LSB})$ where  $\text{LSB} = +\text{FS} / 2^n$ Where LSB is equal to the least significant bit n is equal to the number of converter bits and +FS is equal to the analog FSR.

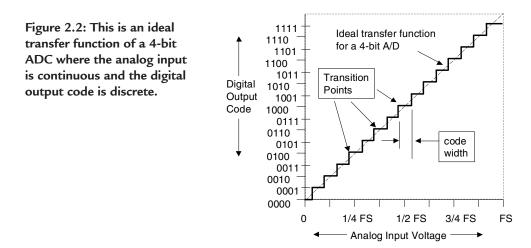

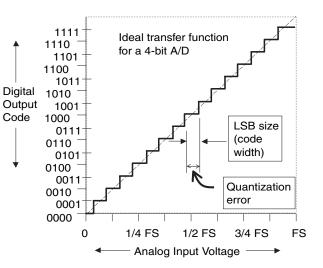

The digital output code versus analog input voltage is mapped in Figure 2.2. In this figure, the analog input voltage of 0 V is converted to a digital code of 0000. If the analog input voltage is changed at the input of the ADC to approximately 0.25 FS voltage, the ADC will produce a digital code of 0100. At approximately midpoint between the codes specified in Table 2.1, the converter will transition from a lower digital code to a higher digital code. A code width as defined in Figure 2.2 is equal to one least significant bit (LSB).

#### Binary Two's Complement Code

In some applications, the unipolar ADC converts negative and positive values. This can only happen when the ADC has differential analog inputs, as shown in Figure 2.1c. These types of devices will output digital code in the binary two's complement format. Binary two's complement arithmetic is widely used in microcontrollers, calculators and computers because simple subtractions and additions require less code. The additional operation of two binary numbers

in two's complement is straightforward, in that the two numbers are added together. The subtraction operation of numbers in two's complement is done by adding the two numbers together to get the subtracted solution.

For example:

| Decimal | Two's      | Decimal | Two's      | Decimal | Two's      |

|---------|------------|---------|------------|---------|------------|

|         | Complement |         | Complement |         | Complement |

| +7      | 0111       | +7      | 0111       | +5      | 0101       |

| +5      | 0101       | -5      | 1011       | -7      | 1001       |

|         |            |         |            |         |            |

| +12     | 1100       | +2      | 0010       | -2      | 1100       |

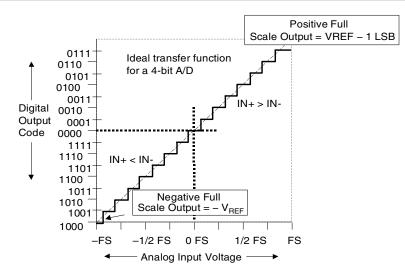

Binary two's complement coding is not as straightforward as straight binary. The codes are not continuous from one end to the other due to the discontinuity that occurs at the analog bipolar zero. The two's complement representation of a positive binary number is generated by logically complementing all the digits, which then converts it to the negative binary number counterpart as shown in Table 2.2 and Figure 2.3. With this code scheme, the most significant bit (MSB) is a sign indicator. A positive value is indicated with an MSB logic 0. An MSB value of logic 1 indicates that the output number is a negative value.

Table 2.2: The binary two's complement representation of zero volts is also equal to a digital 0000. The analog positive FS minus one LSB digital representation is equal to 0111, and the analog negative FS representation is 1000.

| Median Voltage (V)                           | Code |

|----------------------------------------------|------|

| 0.875 FS ( <sup>7</sup> / <sub>8</sub> FS)   | 0111 |

| 0.75 FS ( <sup>6</sup> / <sub>8</sub> FS)    | 0110 |

| 0.625 FS ( <sup>5</sup> / <sub>8</sub> FS)   | 0101 |

| 0.5 FS ( <sup>4</sup> / <sub>8</sub> FS)     | 0100 |

| 0.375 FS ( <sup>3</sup> / <sub>8</sub> FS)   | 0011 |

| 0.25 FS ( <sup>2</sup> / <sub>8</sub> FS)    | 0010 |

| 0.125 FS ( <sup>1</sup> / <sub>8</sub> FS)   | 0001 |

| 0                                            | 0000 |

| -0.125 FS (- <sup>1</sup> / <sub>8</sub> FS) | 1111 |

| -0.25 FS (- <sup>2</sup> / <sub>8</sub> FS)  | 1110 |

| -0.375 FS (- <sup>3</sup> / <sub>8</sub> FS) | 1101 |

| $-0.5 \text{ FS} (-4/_8 \text{ FS})$         | 1100 |

| -0.625 FS (- <sup>5</sup> / <sub>8</sub> FS) | 1011 |

| -0.75 FS (- <sup>6</sup> / <sub>8</sub> FS)  | 1010 |

| -0.875 FS (- <sup>7</sup> / <sub>8</sub> FS) | 1001 |

| -1 FS                                        | 1000 |

Figure 2.3: The transfer function of a 4-bit ADC bipolar analog input will produce a two's complement code as a digital output.

This system has an odd number of codes and only one zero state. Differential input ADCs (Figure 2.1c) are devices that can be operated in a single-ended, positive voltage input mode or a full-differential input mode. In the full-differential mode, the FSR of the device is equal to:

$$FSR = \{+IN_{MAX} - (-IN_{MIN})\} + \{-IN_{MAX} - (+IN_{MIN})\}$$

And the ADC's input voltage range is equal to:

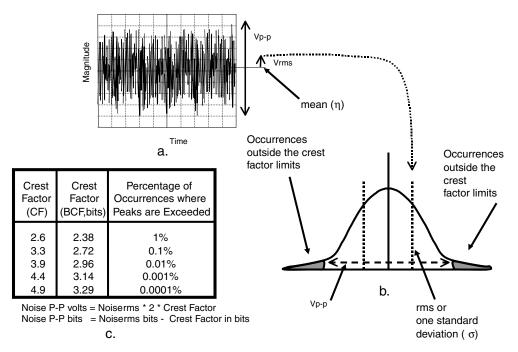

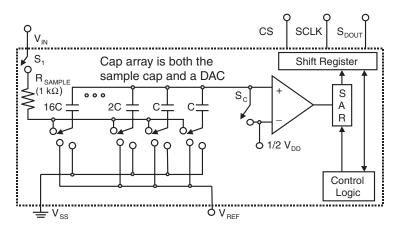

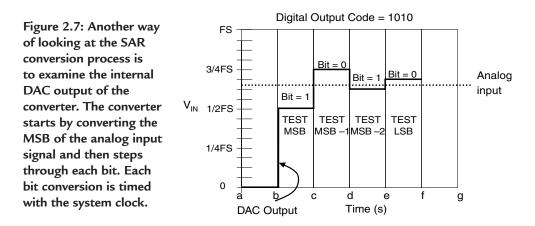

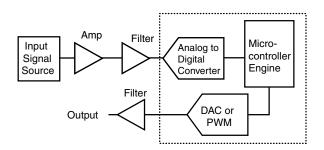

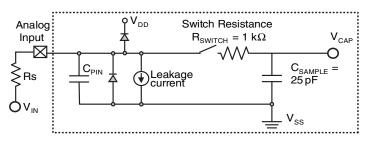

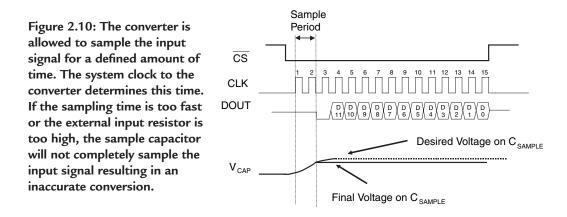

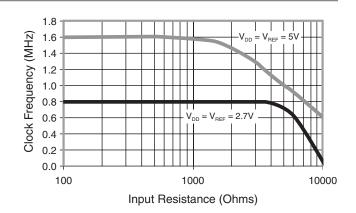

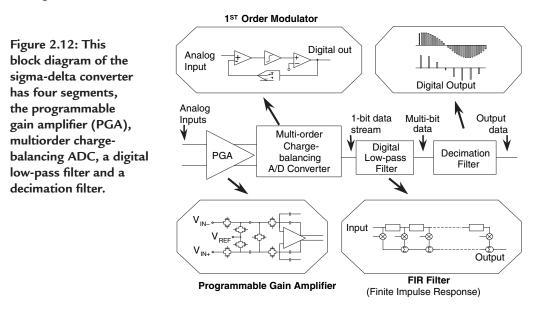

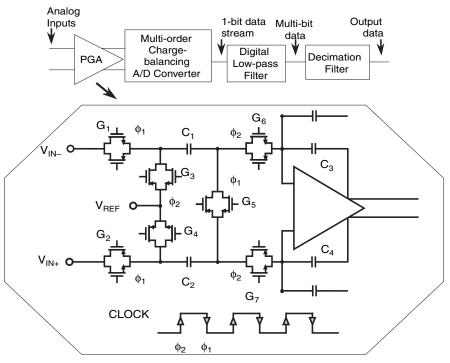

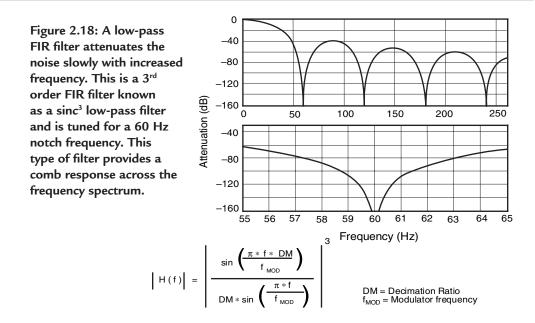

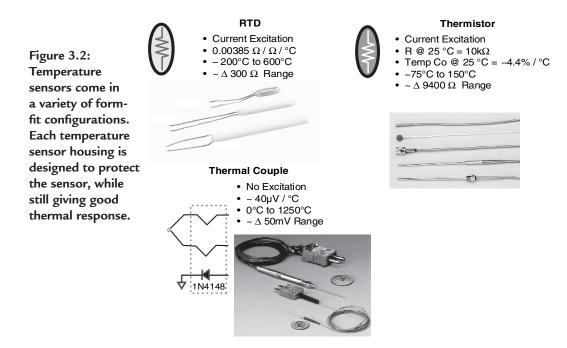

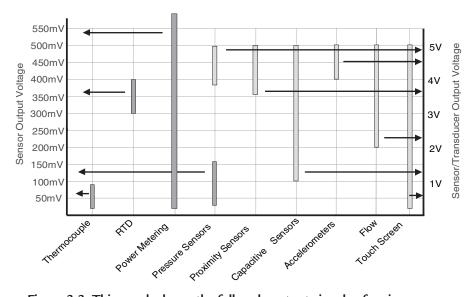

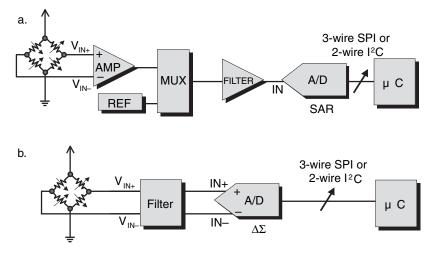

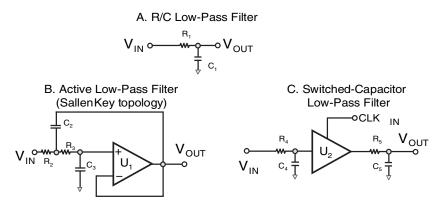

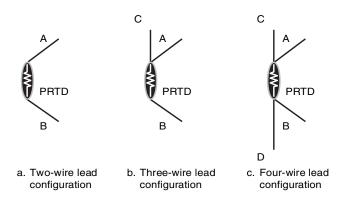

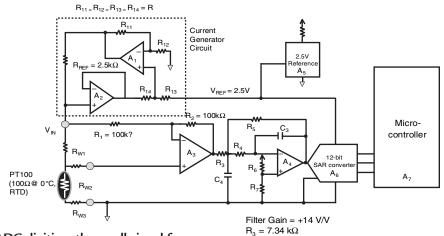

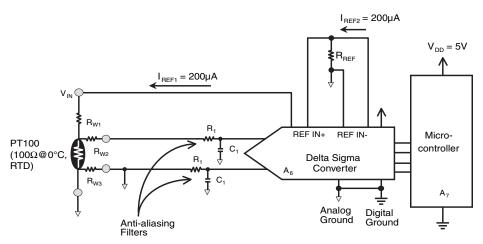

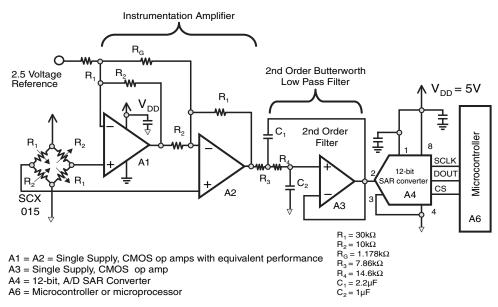

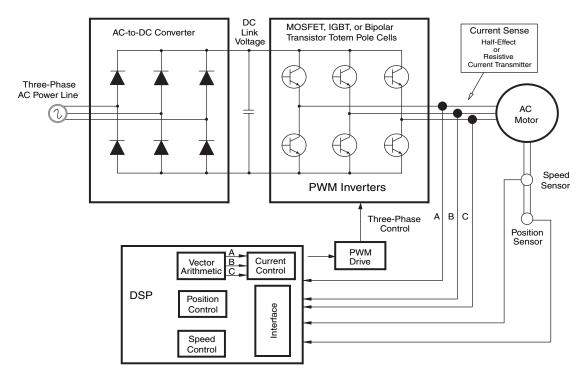

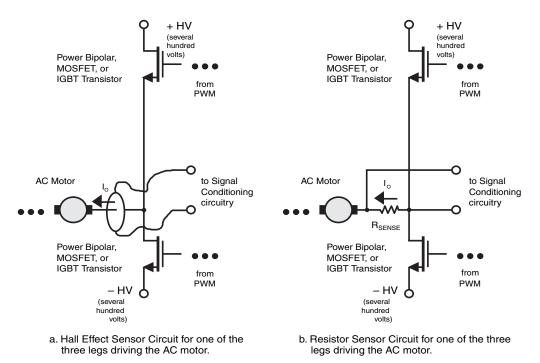

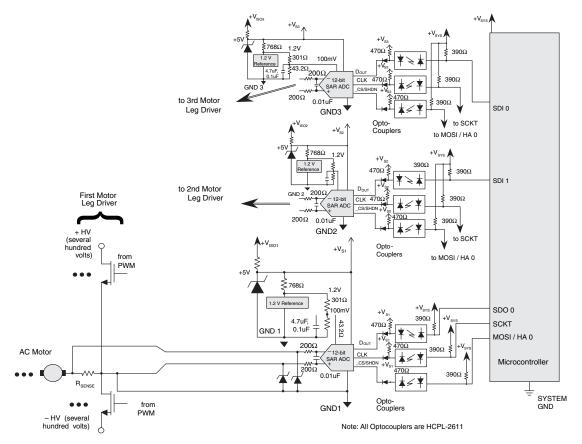

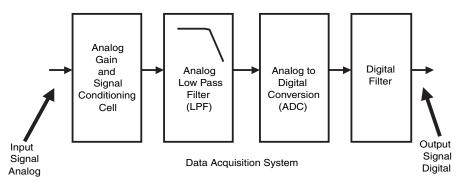

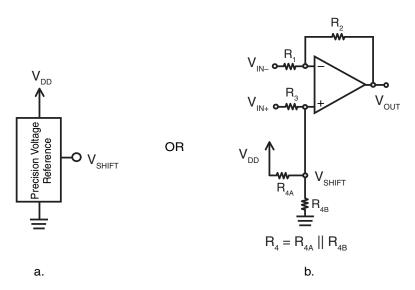

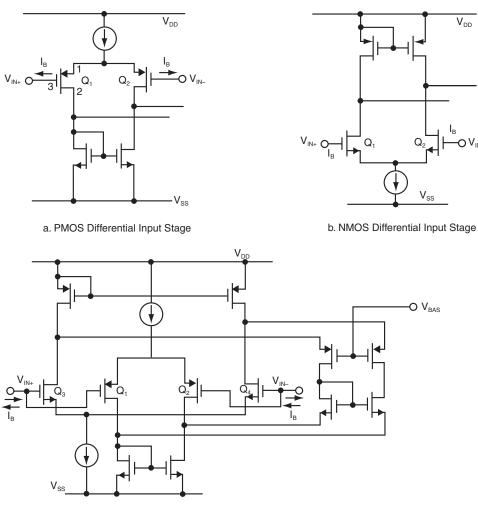

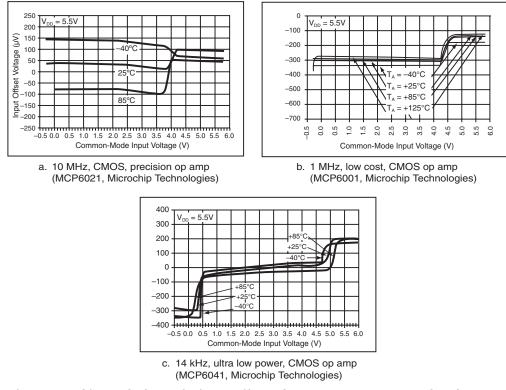

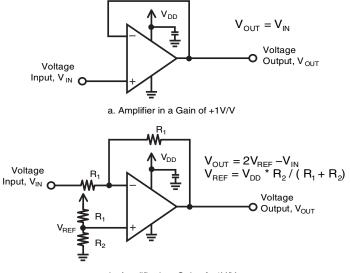

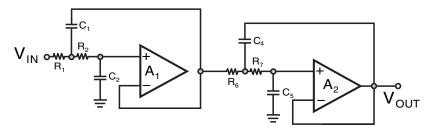

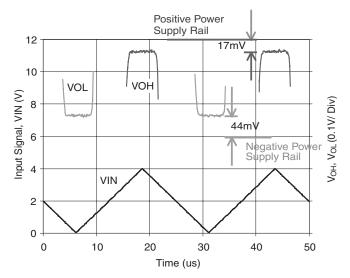

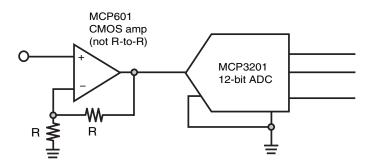

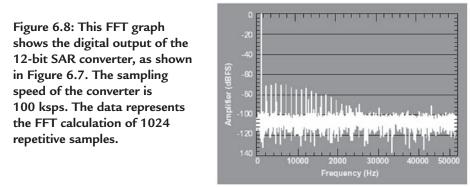

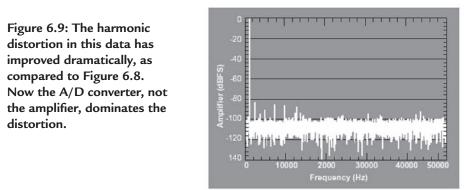

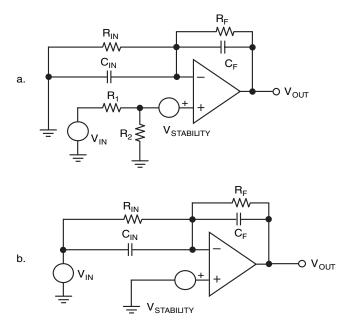

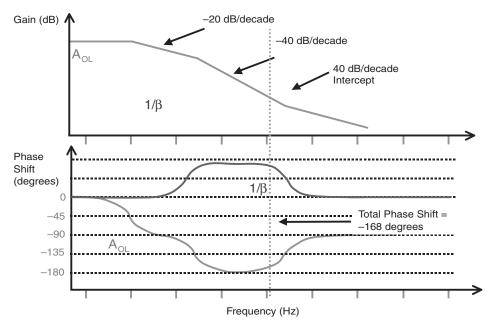

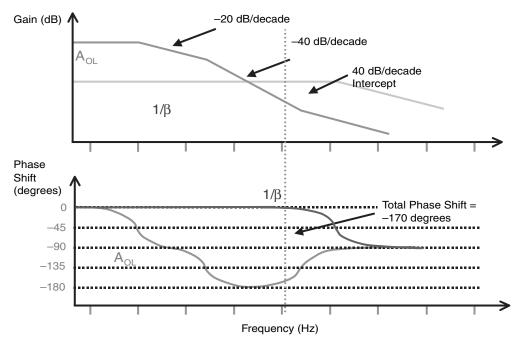

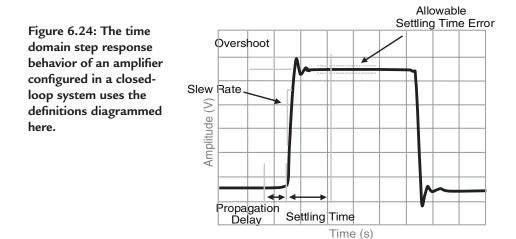

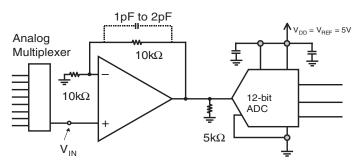

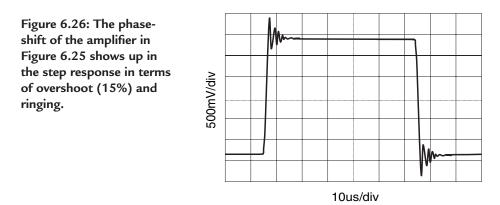

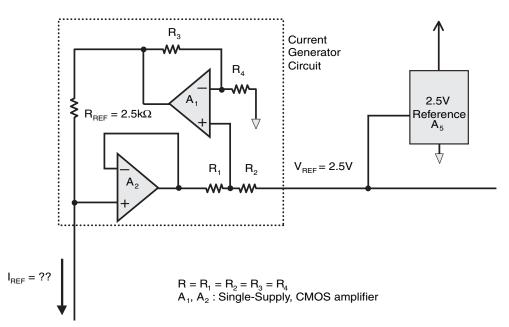

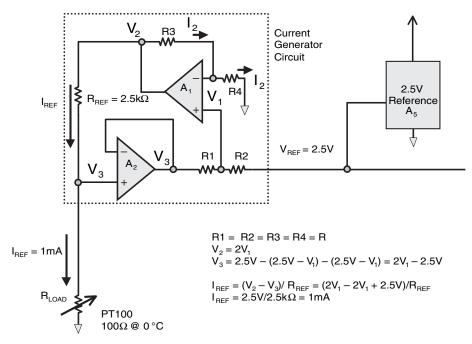

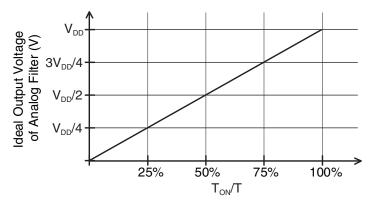

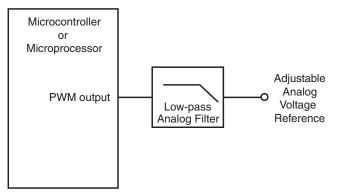

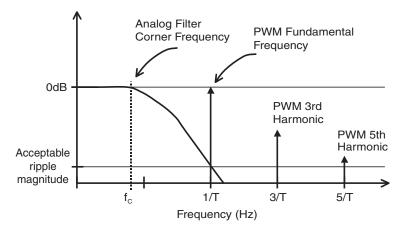

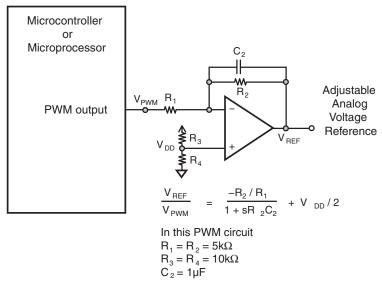

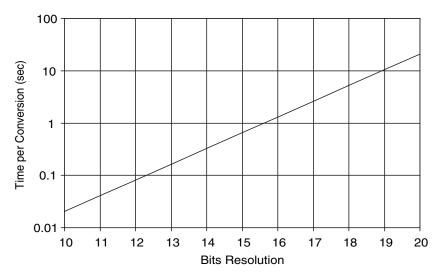

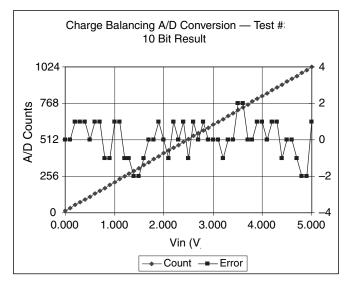

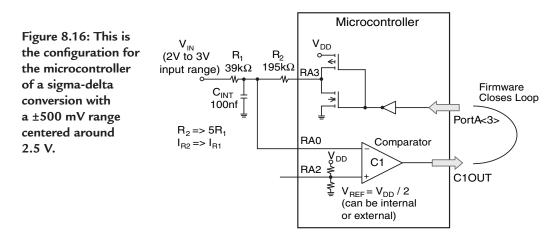

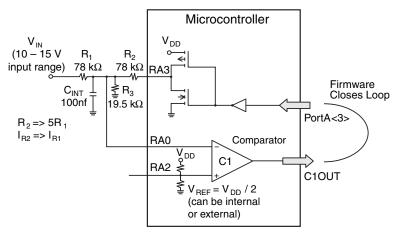

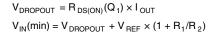

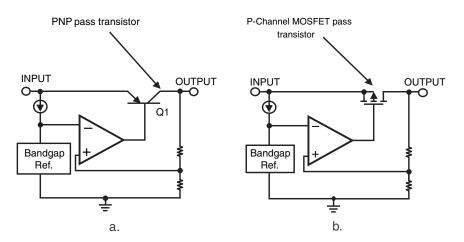

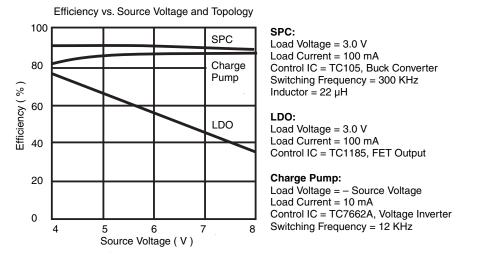

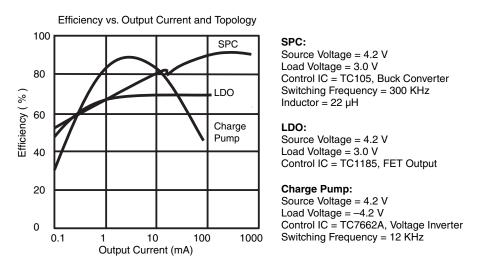

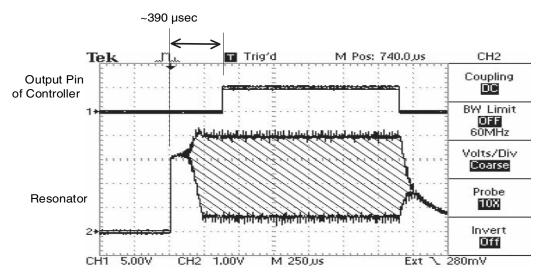

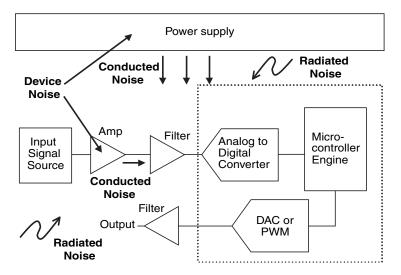

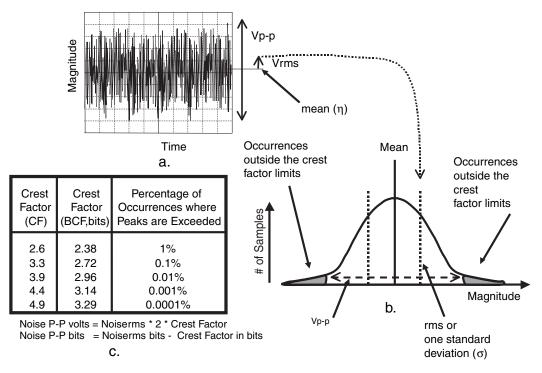

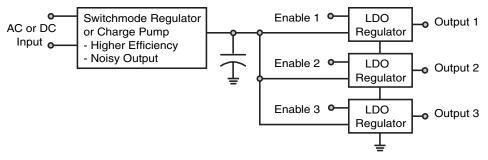

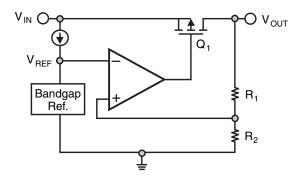

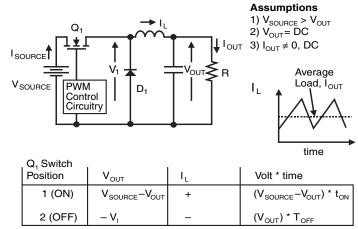

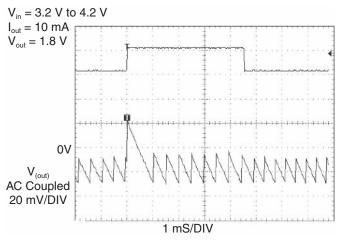

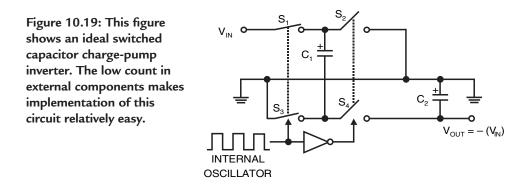

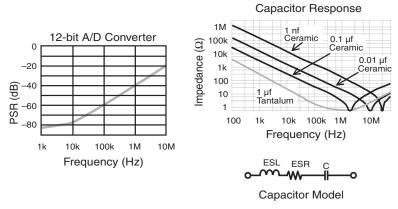

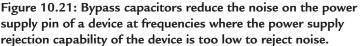

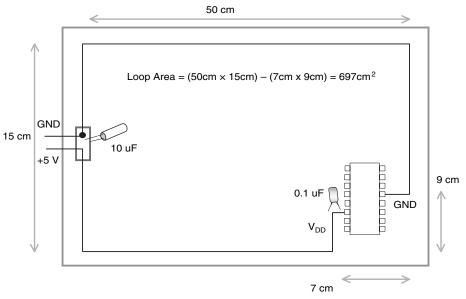

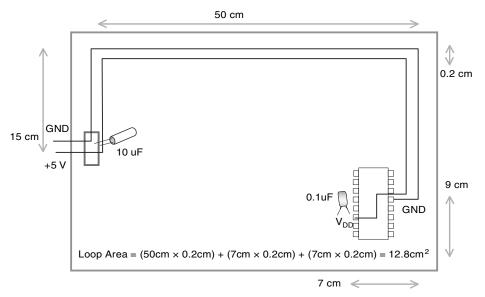

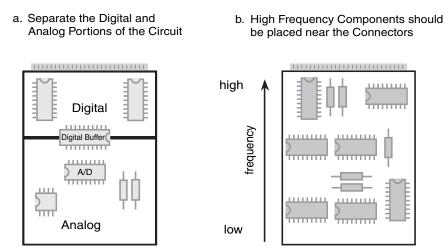

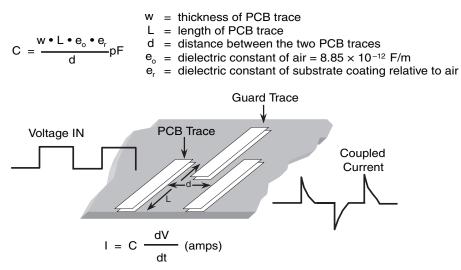

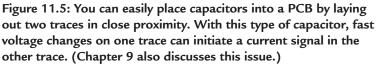

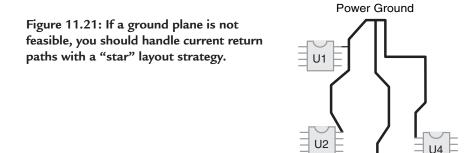

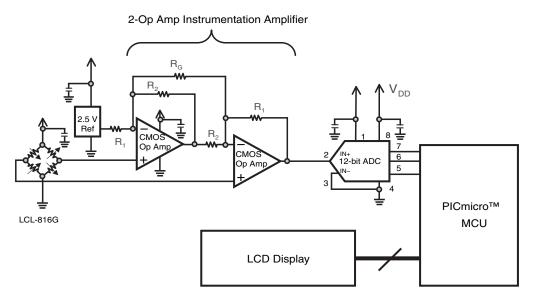

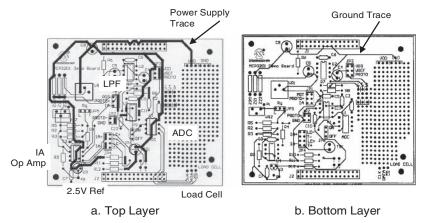

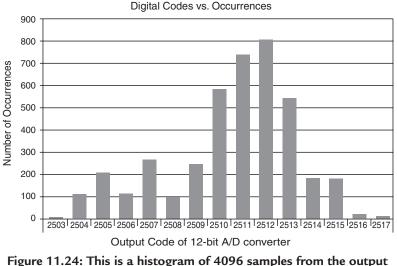

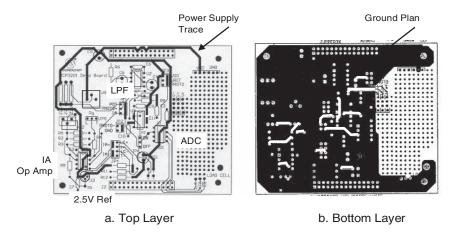

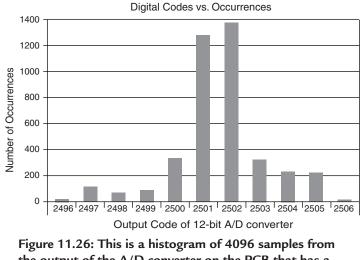

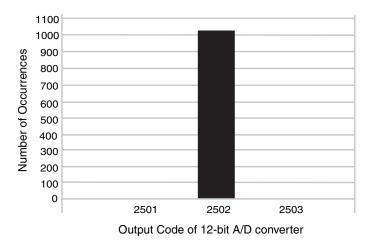

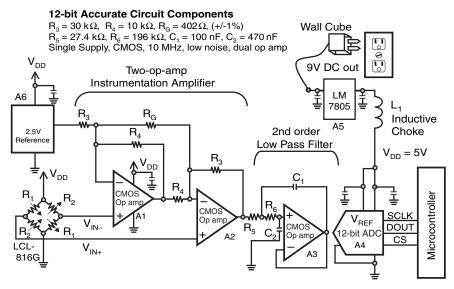

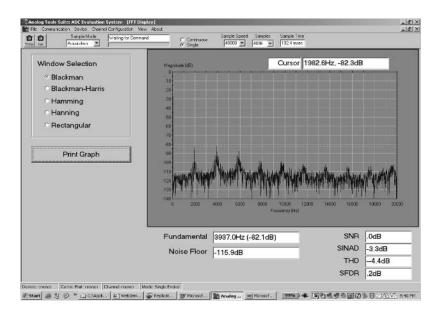

$$A_{IN} = (+IN - (-IN))$$